TPD4E001-Q1

ZHCSB23E - MARCH 2013 - REVISED JUNE 2017

# TPD4E001-Q1 具有 1.5pF I/O 电容的 4 通道 ESD 保护阵列

## 特性

- 具有符合 AEC-Q100 标准的下列结果:

- 器件温度等级 1: -40°C 至 +125°C 运行环境温 度范围

- 器件人体模型 (HBM) 静电放电 (ESD) 分类等级

- HBM 电平 15kV

- 器件带电器件模型 (CDM) ESD 分类等级 C5

- IEC 61000-4-2 4 级 ESD 保护

- ±8kV 接触放电

- ±15kV 气隙放电

- IEC 61000-4-5 浪涌保护

- 5.5A (8/20µs)

- 输入电容低至 1.5pF

- 最大泄漏电流低至 10nA

- 电源电压范围: 0.9V 至 5.5V

#### 2 应用

- 终端设备

- 汽车音响主机

- 汽车后座娱乐系统

- 汽车后置摄像头系统

- 接口

- USB 2.0

- 以太网

- 精密模拟接口

## 3 说明

TPD4E001-Q1 器件是一款低电容 TVS 二极管阵列, 设计用于为通信线路中连接的敏感电子元件提供 ESD 保护。每个通道包含一对将 ESD 脉冲引导至 Vcc 或者 GND 的瞬态电压抑制二极管。根据 IEC 61000-4-2 国 际标准规定, TPD4E001-Q1 可防止接触放电电压高达 ±8kV 和气隙放电高达电压 ±15kV 的 ESD 事件发生。 该器件每通道的电容低至 1.5pF, 因此非常适用于高速 数据接口。低泄露电流(最大 10nA)确保了系统的最 低功耗和模块接口的高精度。

此外, 此器件还适用于为使用 USB 2.0、以太网或高 精度模拟接口的汽车音响主机、后座娱乐系统以及后座 摄像机系统提供保护。

## 器件信息(1)

| 器件型号        | 封装         | 封装尺寸 (标称值)      |

|-------------|------------|-----------------|

| TPD4E001-Q1 | SOT-23 (6) | 2.90mm x 1.60mm |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

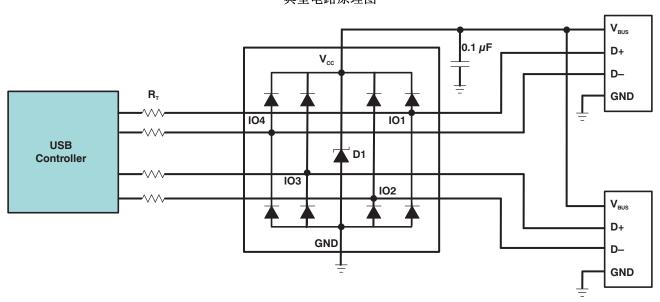

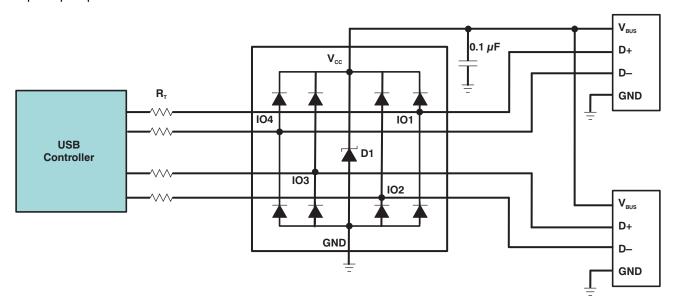

## 典型电路原理图

|          |                                                                                                             | 目录                               |      |                                |      |

|----------|-------------------------------------------------------------------------------------------------------------|----------------------------------|------|--------------------------------|------|

| 1        | 特性                                                                                                          | 1                                |      | 7.4 Device Functional Modes    | 8    |

| 2        | · · · · · · · · · · · · · · · · · · ·                                                                       |                                  | 8    | Application and Implementation | 9    |

| 3        | · · · · · · · · · · · · · · · · · · ·                                                                       |                                  |      | 8.1 Application Information    |      |

| 4        | 修订历史记录                                                                                                      |                                  |      | 8.2 Typical Application        |      |

| 5        | Pin Configuration and Functions                                                                             |                                  | 9    | Power Supply Recommendations   | 11   |

| 6        | Specifications                                                                                              |                                  | 10   | Layout                         | 12   |

| ·        | 6.1 Absolute Maximum Ratings                                                                                |                                  |      | 10.1 Layout Guidelines         | 12   |

|          | 6.2 ESD Ratings—AEC Specification                                                                           |                                  |      | 10.2 Layout Example            | 12   |

|          | 6.3 ESD Ratings—IEC Specification                                                                           |                                  | 11   | 器件和文档支持                        | 13   |

|          | 6.4 Recommended Operating Conditions                                                                        |                                  |      | 11.1 文档支持                      | 13   |

|          | 6.5 Thermal Information                                                                                     |                                  |      | 11.2 接收文档更新通知                  | 13   |

|          | 6.6 Electrical Characteristics                                                                              |                                  |      | 11.3 社区资源                      | 13   |

|          | 6.7 Typical Characteristics                                                                                 |                                  |      | 11.4 商标                        | 13   |

| 7        | Detailed Description                                                                                        |                                  |      | 11.5 静电放电警告                    | 13   |

| •        | 7.1 Overview                                                                                                |                                  |      | 11.6 Glossary                  | 13   |

|          | 7.2 Functional Block Diagram                                                                                |                                  | 12   | 机械、封装和可订购信息                    | 13   |

|          | 7.3 Feature Description                                                                                     |                                  |      |                                |      |

|          | 之前版本的页码可能与当前版本有所不同。<br>nges from Revision D (March 2015) to Revision                                        | n E                              |      |                                | Page |

| • U      | pdated Typical Application Schematic                                                                        |                                  |      |                                | 9    |

| Char     | ges from Revision C (June 2013) to Revision                                                                 | D                                |      |                                | Page |

| . –      |                                                                                                             |                                  |      |                                |      |

|          | L添加 引脚配置和功能部分,ESD 额定值表,特性<br>h,布局部分,器件和文档支持部分以及机械、封                                                         |                                  |      |                                |      |

| 5.       |                                                                                                             | 装和可订购信                           | 言息部分 | 分                              | 1    |

| ケ<br>• E | ,布局部分,器件和文档支持部分以及机械、封建<br>是更改 器件 CDM ESD 分类等级,从 C4B 改为 C5                                                   | 装和可订购信<br>5                      | 言息部分 | 分                              | 1    |

| ケ<br>• E | <b>)</b> ,布局部分,器件和文档支持部分以及机械、封                                                                              | 装和可订购信<br>5                      | 言息部分 | 分                              | 1    |

| • E      | ,布局部分,器件和文档支持部分以及机械、封建<br>是更改 器件 CDM ESD 分类等级,从 C4B 改为 C5                                                   | 装和可订购信5sion C                    | 意息部分 | <del>分</del>                   | 1    |

| • E      | h,布局部分,器件和文档支持部分以及机械、封建<br>是更改 器件 CDM ESD 分类等级,从 C4B 改为 C5<br>nges from Revision B (February 2012) to Revis | 裝和可订购信<br>5sion C<br>Characteris | 意息部分 | <del>分</del>                   | 1    |

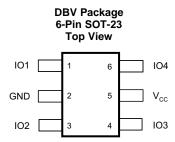

# **5 Pin Configuration and Functions**

## **Pin Functions**

| PIN             |     | TVDE | DESCRIPTION                                                                       |  |  |  |  |

|-----------------|-----|------|-----------------------------------------------------------------------------------|--|--|--|--|

| NAME            | NO. | TYPE | DESCRIPTION                                                                       |  |  |  |  |

| GND             | 2   | GND  | Ground                                                                            |  |  |  |  |

| IO1             | 1   |      |                                                                                   |  |  |  |  |

| IO2             | 3   | 1/0  | FOR anythetical above of                                                          |  |  |  |  |

| IO3             | 4   | I/O  | ESD-protected channel                                                             |  |  |  |  |

| IO4             | 6   |      |                                                                                   |  |  |  |  |

| V <sub>CC</sub> | 5   | I    | Power-supply input. Bypass V <sub>CC</sub> to GND with a 0.1-μF ceramic capacitor |  |  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                  | MIN  | MAX            | UNIT |

|------------------|--------------------------------------------------|------|----------------|------|

| $V_{CC}$         | Supply voltage                                   | -0.3 | 7              | V    |

| $V_{IO}$         | I/O voltage tolerance                            | -0.3 | $V_{CC} + 0.3$ | V    |

| I <sub>PP</sub>  | Peak pulse current (Tp = 8/20 µs) <sup>(2)</sup> |      | 5.5            | Α    |

| P <sub>PP</sub>  | Peak pulse power (Tp = 8/20 μs) <sup>(2)</sup>   |      | 100            | W    |

| $T_A$            | Free air operating temperature                   | -40  | 125            | °C   |

| $T_{J}$          | Junction temperature                             |      | 150            | °C   |

| T <sub>stg</sub> | Storage temperature                              | -65  | 150            | °C   |

<sup>(1)</sup> SStresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings—AEC Specification

|                    |               |                                                         | VALUE  | UNIT     |

|--------------------|---------------|---------------------------------------------------------|--------|----------|

| V                  | Electrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±15000 | V        |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per AEC Q100-011            | ±750   | <b>v</b> |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 ESD Ratings—IEC Specification

|                                            |                                 |                                 | VALUE | UNIT |

|--------------------------------------------|---------------------------------|---------------------------------|-------|------|

| M                                          | Clastrostatic discharge         | IEC 61000-4-2 contact discharge | ±8000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | IEC 61000-4-2 air-gap discharge | ±15000                          | V     |      |

<sup>(2)</sup> Non-repetitive current pulse 8/20 µs exponentially decaying waveform according to IEC 61000-4-5.

## 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                            |                                | MIN | MAX             | UNIT |

|----------------------------|--------------------------------|-----|-----------------|------|

| T <sub>A</sub>             | Free air operating temperature | -40 | 125             | °C   |

| V <sub>CC</sub> pin        | Operating voltage              | 0.9 | 5.5             | V    |

| IO1, IO2, IO3,<br>IO4 pins | Operating voltage              | 0   | V <sub>CC</sub> | V    |

## 6.5 Thermal Information

|                      |                                              | TPD4E001-Q1  |      |

|----------------------|----------------------------------------------|--------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DBV (SOT-23) | UNIT |

|                      |                                              | 6 PINS       |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 202.1        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 146.2        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 47.1         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 37.6         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 46.7         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

#### 6.6 Electrical Characteristics

$V_{CC}$  = 5 V ± 10%, over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                 | TEST CONDITION                                                                                         | MIN                 | TYP <sup>(1)</sup> | MAX | UNIT |    |

|--------------------|---------------------------|--------------------------------------------------------------------------------------------------------|---------------------|--------------------|-----|------|----|

| I <sub>CC</sub>    | Supply current            |                                                                                                        |                     |                    | 1   | 200  | nA |

| $V_{F}$            | Diode forward voltage     | I <sub>F</sub> = 10 mA                                                                                 |                     | 0.65               |     | 0.95 | V  |

| $V_{BR}$           | Breakdown voltage         | I <sub>BR</sub> = 10 mA                                                                                | 11                  |                    |     | V    |    |

| V <sub>CLAMP</sub> | Clamping voltage          | Surge strike $^{(2)}$ on IO pin, GND pin grounded, $V_{CC} = 5.5 \text{ V}$ , $I_{PP} = 5.5 \text{ A}$ | Positive transients |                    | 16  |      | V  |

| $V_{RWM}$          | Reverse standoff voltage  | IO pin to GND pin                                                                                      |                     |                    |     | 5.5  | V  |

| I <sub>IO</sub>    | Channel leakage current   | $V_{IO}$ = GND to $V_{CC}$                                                                             |                     |                    |     | ±10  | nA |

| C <sub>IO</sub>    | Channel input capacitance | $V_{CC} = 5 \text{ V}$ , bias of $V_{CC}/2$ , f = 10 MHz                                               |                     |                    | 1.5 |      | pF |

<sup>(1)</sup> Typical values are at  $V_{CC}$  = 5 V and  $T_A$  = 25°C. (2) Non-repetitive current pulse 8/20  $\mu$ s exponentially decaying waveform according to IEC 61000-4-5.

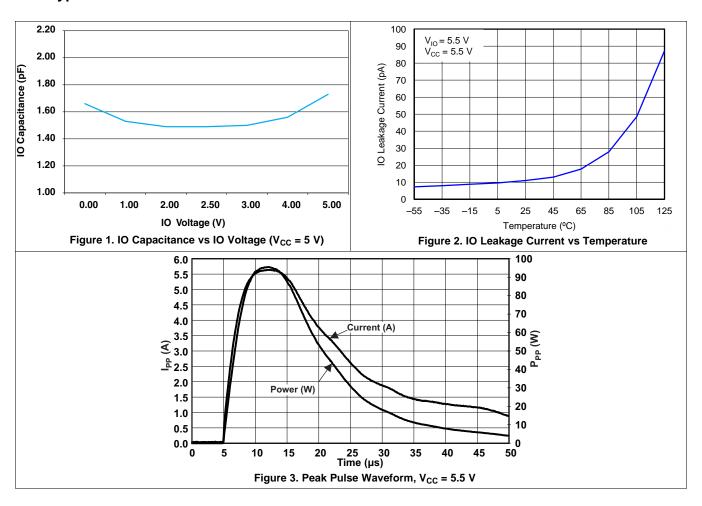

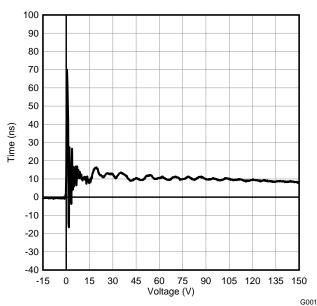

## 6.7 Typical Characteristics

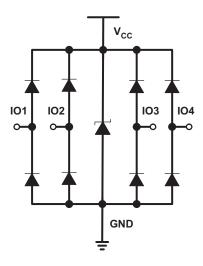

## 7 Detailed Description

#### 7.1 Overview

The TPD4E001-Q1 device is a low-capacitance, TVS diode array designed for ESD protection in sensitive electronics connected to communication lines. Each channel consists of a pair of transient voltage suppression diodes that steer ESD pulses to  $V_{CC}$  or GND. The TPD4E001-Q1 device protects against ESD events up to  $\pm 8$ -kV contact discharge and  $\pm 15$ -kV air-gap discharge, as specified in IEC 61000-4-2 international standard. This device has a low capacitance of 1.5-pF per channel making it ideal for use in high-speed data interfaces. The low-leakage current (10 nA maximum) ensures minimum power consumption for the system and high accuracy for analog interfaces.

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 AEC-Q100 Qualified

This device is qualified according to the AEC-Q100 standard. The device temperature rating is Grade 1 (-40°C to +125°C). The HBM Classification Level passed is 3B (> 8 kV). The CDM Classification Level passed is C5 (all pins 750 V to <1000 V).

#### 7.3.2 IEC 61000-4-2 Level 4 ESD Protection

The device is specified at ±8-kV contact discharge and ±15-kV air gap discharge.

#### 7.3.3 IEC 61000-4-5 Surge Protection

This device is rated to pass at least 5.5-A of peak pulse current according to the IEC 61000-4-5 (8/20-µs pulse) standard.

#### 7.3.4 Low 1.5-pF Input Capacitance

This device has a typical capacitance of 1.5-pF on each of the four IO pins. This allows for high speed signals on the IO pins in excess of 1 Gbps.

#### 7.3.5 Low 10-nA (Maximum) Leakage Current

This device is rated to have a maximum leakage current of 10-nA on each of the four IO pins.

#### 7.3.6 0.9-V to 5.5-V Supply Voltage Range

This device is specified to operate with a supply voltage (on  $V_{CC}$ ) between 0.9-V and 5.5-V to ensure sufficient signal integrity.

#### 7.4 Device Functional Modes

The TPD4E001-Q1 device is a passive integrated circuit that triggers when voltages are above  $V_{BR}$  or below the lower diodes  $V_F$  (-0.6 V). During ESD events, voltages as high as  $\pm 8$  kV (contact) can be directed to ground via the internal diode network. Once the voltages on the protected line fall below the trigger levels of TPD4E001-Q1 (usually within 10s of nano-seconds) the device reverts back to its high-impedance state.

## 8 Application and Implementation

#### **NOTE**

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The TPD4E001-Q1 device is a TVS diode array which is typically used to provide a path to ground for dissipating ESD events on high-speed signal lines between a human interface connector and a system. As the current from ESD passes through the TVS, only a small voltage drop is present across the diode. This is the voltage presented to the protected IC. The triggered TVS holds this voltage,  $V_{CLAMP}$ , to a safe level for the protected IC.

## 8.2 Typical Application

For this design example, one TPD4E001-Q1 device is being used in a dual USB 2.0 application. This provides a complete port protection scheme.

Figure 4. Typical Application Schematic

### **Typical Application (continued)**

#### 8.2.1 Design Requirements

For this design example, a single TPD4E001-Q1 device is used to protect all the pins on two USB2.0 connectors. Given the USB application, known parameters are listed in the Table 1.

**Table 1. Design Parameters**

| DESIGN PARAMETER                             | VALUE         |

|----------------------------------------------|---------------|

| Signal range on IO1, IO2, IO3, or IO4        | 0 V to 3.6 V  |

| Voltage range on V <sub>CC</sub>             | 0 V to 5.25 V |

| Operating Frequency on IO1, IO2, IO3, or IO4 | 240 MHz       |

#### 8.2.2 Detailed Design Procedure

To begin the design process, some parameters must be decided upon; the designer needs to know the following:

- · Signal range on all protected lines

- Operating frequency on all protected lines

#### 8.2.2.1 Signal Range on IO1 Through IO4

The TPD4E001-Q1 device has 4 identical protection channels for signal lines. The symmetry of the device provides flexibility when selecting which of the 4 IO channels protects which signal lines. Any IO supports a signal range of 0 to  $(V_{CC} + 0.3)$  V. Therefore, this device supports the USB 2.0 signal swing assuming  $V_{CC}$  is set appropriately.

## 8.2.2.2 Voltage Range on V<sub>CC</sub>

The V<sub>CC</sub> pin can be connected in one of two ways:

- If the V<sub>CC</sub> pin connects to the system power supply, the TPD4E001-Q1 device works as a transient suppressor for any signal swing above V<sub>CC</sub> + V<sub>F</sub>. TI recommends a 0.1-μF capacitor on the device V<sub>CC</sub> pin for ESD bypass.

- If the V<sub>CC</sub> pin does not connect to the system power supply, the TPD4E001-Q1 device can tolerate higher signal swing in the range up to 10 V. Note that TI still recommends a 0.1-μF capacitor at the V<sub>CC</sub> pin for ESD bypass.

If this pin is connected to the USB 2.0  $V_{BUS}$  supply or left floating, the allowable signal swing is enough for a USB 2.0 application.

#### 8.2.2.3 Bandwidth on IO1 Through IO4

Each IO pin on the TPD4E001-Q1 device has a typical capacitance of 1.5 pF. This capacitance is low enough to easily support USB 2.0 data rates.

## 8.2.3 Application Curve

Figure 5. IEC 61000-4-2 Voltage Clamp Waveform 8-kV Contact

# 9 Power Supply Recommendations

This device is a passive ESD protection device so there is no need to power it. Do not violate the maximum voltage specifications for each pin.

## 10 Layout

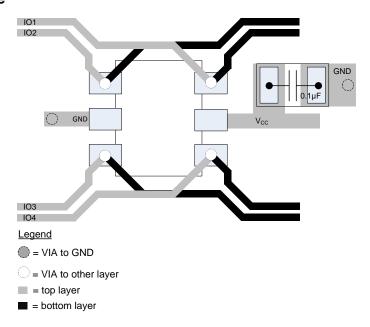

## 10.1 Layout Guidelines

When placed near the connector, the TPD4E001-Q1 device's ESD solution offers little or no signal distortion during normal operation due to low IO capacitance and ultra-low leakage-current specifications. The TPD4E001-Q1 device ensures that the core circuitry is protected and the system is functioning properly in the event of an ESD strike. For proper operation, observe the following layout and design guidelines:

- Place the TPD4E001-Q1 device solution close to the connector. This allows the device to take away the energy associated with ESD strike before it reaches the internal circuitry of the system board.

- Place a 0.1-μF capacitor very close to the V<sub>CC</sub> pin. This limits any momentary voltage surge at the IO pin during the ESD strike event.

- Ensure that there is enough metallization for the V<sub>CC</sub> and GND loop. During normal operation, the TPD4E001-Q1 device consumes nA leakage current. But during the ESD event, V<sub>CC</sub> and GND may see 15 A to 30 A of current, depending on the ESD level. Sufficient current path enables safe discharge of all the energy associated with the ESD strike.

- · Leave the unused IO pins floating.

- One can connect the V<sub>CC</sub> pin in two different ways:

- a. If the  $V_{CC}$  pin connects to the system power supply, the TPD4E001-Q1 works as a transient suppressor for any signal swing above  $V_{CC}$  +  $V_F$ . TI recommends a 0.1- $\mu$ F capacitor on the device  $V_{CC}$  pin for ESD bypass.

- b. If the  $V_{CC}$  pin does not connect to the system power supply, the TPD4E001-Q1 can tolerate higher signal swing in the range up to 10 V. Note that TI still recommends a 0.1- $\mu$ F capacitor at the  $V_{CC}$  pin for ESD bypass.

- The optimum placement is as close to the connector as possible.

- EMI during an ESD event can couple from the trace being struck to other nearby unprotected traces, resulting in early system failures.

- The PCB designer needs to minimize the possibility of EMI coupling by keeping any unprotected traces away from the protected traces which are between the TVS and the connector.

- · Route the protected traces as straight as possible.

- Eliminate any sharp corners on the protected traces between the TVS and the connector by using rounded corners with the largest radii possible.

- Electric fields tend to build up on corners, increasing EMI coupling.

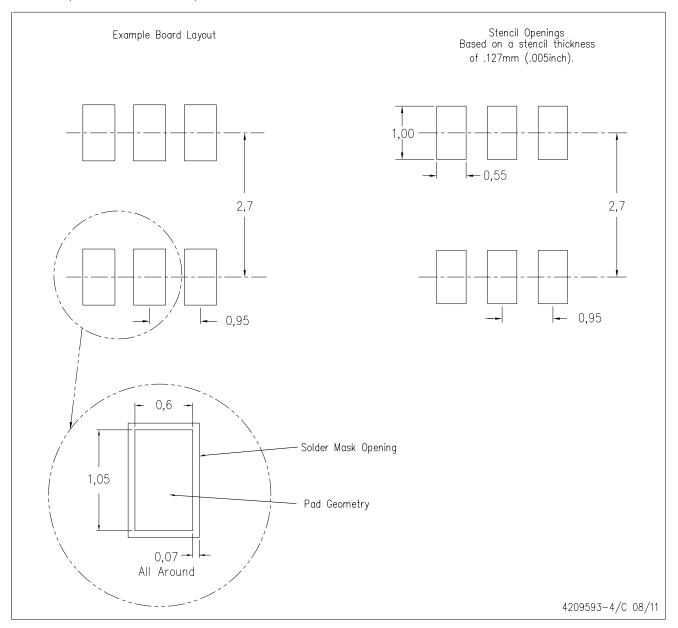

#### 10.2 Layout Example

### 11 器件和文档支持

#### 11.1 文档支持

#### 11.1.1 相关文档

请参阅如下相关文档:

- 阅读和理解 ESD 保护数据表

- 《ESD 布局指南》

### 11.2 接收文档更新通知

如需接收文档更新通知,请访问 ti.com 上的器件产品文件夹。请单击右上角的通知我进行注册,即可收到任意产品信息更改每周摘要。有关更改的详细信息,请查看任意已修订文档中包含的修订历史记录。

#### 11.3 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

#### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 12 机械、封装和可订购信息

以下页面包括机械、封装和可订购信息。这些信息是指定器件的最新可用数据。这些数据发生变化时,我们可能不会另行通知或修订此文档。如欲获取此产品说明书的浏览器版本,请参见左侧的导航栏。

## PACKAGE OPTION ADDENDUM

5-Jul-2017

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|----------------------|---------|

| TPD4E001QDBVRQ1  | ACTIVE | SOT-23       | DBV                | 6    | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 125   | AAXQ                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPD4E001-Q1:

# **PACKAGE OPTION ADDENDUM**

5-Jul-2017

www.ti.com

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

PACKAGE MATERIALS INFORMATION

www.ti.com 5-Jul-2017

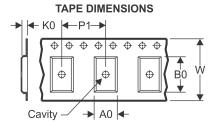

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

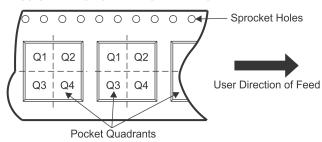

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPD4E001QDBVRQ1 | SOT-23          | DBV                | 6 | 3000 | 178.0                    | 9.0                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

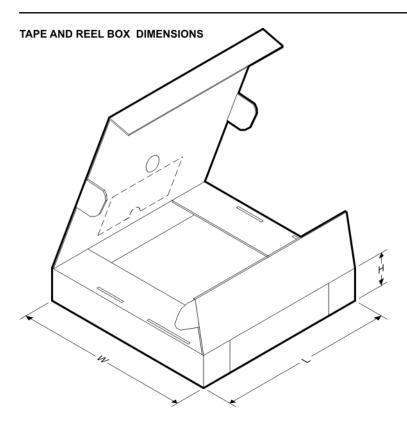

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Jul-2017

#### \*All dimensions are nominal

| Device          | Device Package Type |     | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-----------------|---------------------|-----|------|------|-------------|------------|-------------|--|

| TPD4E001QDBVRQ1 | SOT-23              | DBV | 6    | 3000 | 180.0       | 180.0      | 18.0        |  |

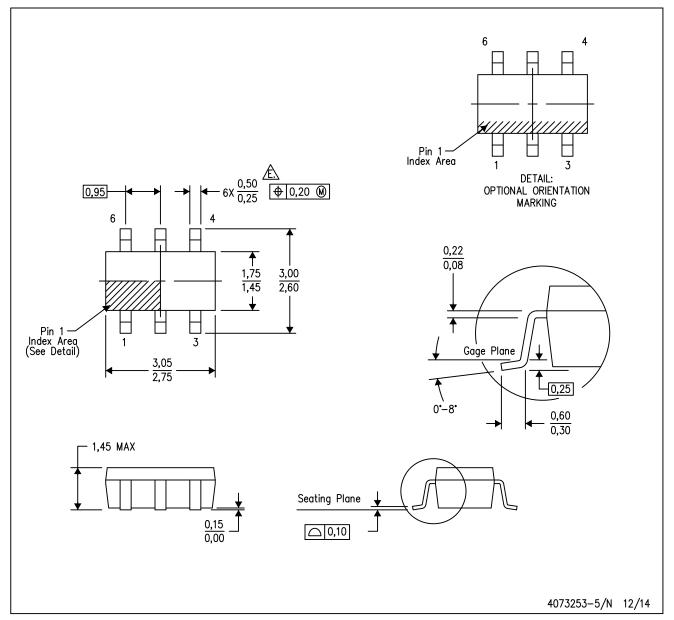

# DBV (R-PDSO-G6)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation.

- Falls within JEDEC MO-178 Variation AB, except minimum lead width.

# DBV (R-PDSO-G6)

# PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

#### 重要声明

德州仪器 (TI) 公司有权按照最新发布的 JESD46 对其半导体产品和服务进行纠正、增强、改进和其他修改,并不再按最新发布的 JESD48 提供任何产品和服务。买方在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。

TI 公布的半导体产品销售条款 (http://www.ti.com/sc/docs/stdterms.htm) 适用于 TI 己认证和批准上市的已封装集成电路产品的销售。另有其他条款可能适用于其他类型 TI 产品及服务的使用或销售。

复制 TI 数据表上 TI 信息的重要部分时,不得变更该等信息,且必须随附所有相关保证、条件、限制和通知,否则不得复制。TI 对该等复制文件不承担任何责任。第三方信息可能受到其它限制条件的制约。在转售 TI 产品或服务时,如果存在对产品或服务参数的虚假陈述,则会失去相关 TI 产品或服务的明示或暗示保证,且构成不公平的、欺诈性商业行为。TI 对此类虚假陈述不承担任何责任。

买方和在系统中整合 TI 产品的其他开发人员(总称"设计人员")理解并同意,设计人员在设计应用时应自行实施独立的分析、评价和判断,且应全权负责并确保应用的安全性,及设计人员的应用(包括应用中使用的所有 TI 产品)应符合所有适用的法律法规及其他相关要求。设计人员就自己设计的应用声明,其具备制订和实施下列保障措施所需的一切必要专业知识,能够(1)预见故障的危险后果,(2)监视故障及其后果,以及(3)降低可能导致危险的故障几率并采取适当措施。设计人员同意,在使用或分发包含 TI 产品的任何应用前,将彻底测试该等应用和该等应用中所用 TI 产品的功能。

TI 提供技术、应用或其他设计建议、质量特点、可靠性数据或其他服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI资源"),旨在帮助设计人员开发整合了 TI 产品的 应用, 如果设计人员(个人,或如果是代表公司,则为设计人员的公司)以任何方式下载、访问或使用任何特定的 TI资源,即表示其同意仅为该等目标,按照本通知的条款使用任何特定 TI资源。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

设计人员只有在开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为或对设计人员进行辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

除 TI 己明确指出特定产品已达到特定行业标准(例如 ISO/TS 16949 和 ISO 26262)的要求外,TI 不对未达到任何该等行业标准要求而承担任何责任。

如果 TI 明确宣称产品有助于功能安全或符合行业功能安全标准,则该等产品旨在帮助客户设计和创作自己的 符合 相关功能安全标准和要求的应用。在应用内使用产品的行为本身不会 配有 任何安全特性。设计人员必须确保遵守适用于其应用的相关安全要求和 标准。设计人员不可将任何 TI 产品用于关乎性命的医疗设备,除非己由各方获得授权的管理人员签署专门的合同对此类应用专门作出规定。关乎性命的医疗设备是指出现故障会导致严重身体伤害或死亡的医疗设备(例如生命保障设备、心脏起搏器、心脏除颤器、人工心脏泵、神经刺激器以及植入设备)。此类设备包括但不限于,美国食品药品监督管理局认定为 III 类设备的设备,以及在美国以外的其他国家或地区认定为同等类别设备的所有医疗设备。

TI 可能明确指定某些产品具备某些特定资格(例如 Q100、军用级或增强型产品)。设计人员同意,其具备一切必要专业知识,可以为自己的应用选择适合的 产品, 并且正确选择产品的风险由设计人员承担。设计人员单方面负责遵守与该等选择有关的所有法律或监管要求。

设计人员同意向 TI 及其代表全额赔偿因其不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2017 德州仪器半导体技术(上海)有限公司