PGA450-Q1

Reference

Design

ZHCS861B - APRIL 2012 - REVISED JUNE 2015

Ħ

# PGA450-Q1 超声波传感器信号调节器

Technical

Documents

#### 特性 1

- 双 N-通道金属氧化物半导体 (NMOS) 低侧驱动器

- 可配置突发信号生成器

- 低噪声放大器

- 12 位逐次逼近寄存器 (SAR) 模数转换器 (ADC)

- 可配置数字带通滤波器

- 数字信号包迹检测

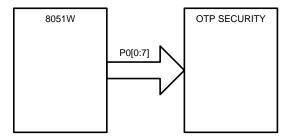

- 片载8位微处理器

- LIN 2.1 物理接口和协议

- 安全装置定时器

- 用于测试和编程的四线串行外设接口 (SPI) 接口

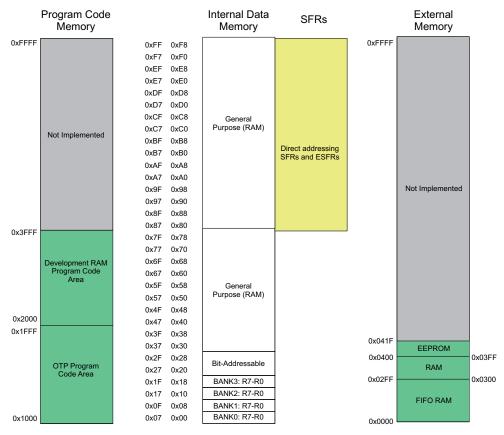

- 8K 字节的一次性可编程 (OTP) 存储器

- 768 字节的先进先出 (FIFO) RAM

- 256 字节的暂存 RAM

- 8K 字节开发 RAM

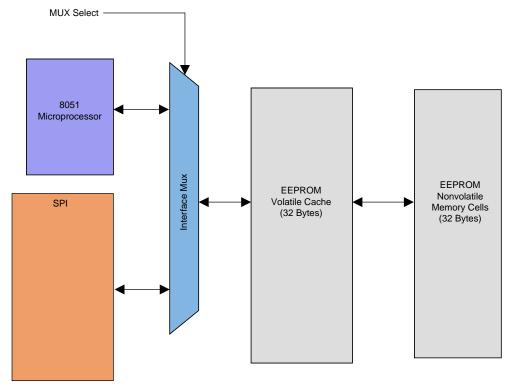

- 针对应用的 32 字节 EEPROM

## 2 应用

- 停车辅助系统

- 盲点检测

- 物体检测应用

## 3 说明

Tools &

Software

PGA450-Q1 是一款针对停车辅助系统或物体检测应用 中的超声波传感器的全集成接口器件。 该器件包括以 下系统模块:稳压器、12 位逐次逼近寄存器 (SAR) 模 数转换器 (ADC)、8 位微控制器、数字带通滤波器、数 模转换器 (DAC)、双通道 NMOS 低侧驱动器、低噪声 放大器、振荡器、LIN 2.1 物理接口及相关协议。

Support &

Community

22

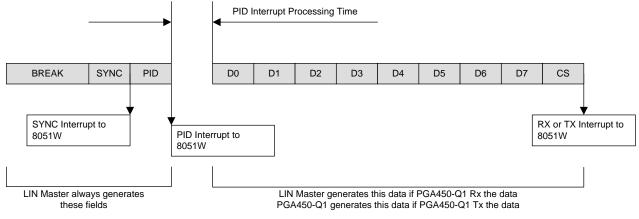

PGA450-Q1 配有 8 位微控制器和 OTP 程序存储器, 用于处理回声信号以及计算传感器与物体间的距离。 这个数据通过 LIN 2.1 通信协议传送。 LIN 2.1 物理层 只作为从器件并且不执行 LIN 唤醒特性。 所有其他 LIN 2.1 功能均可在软件中实现。

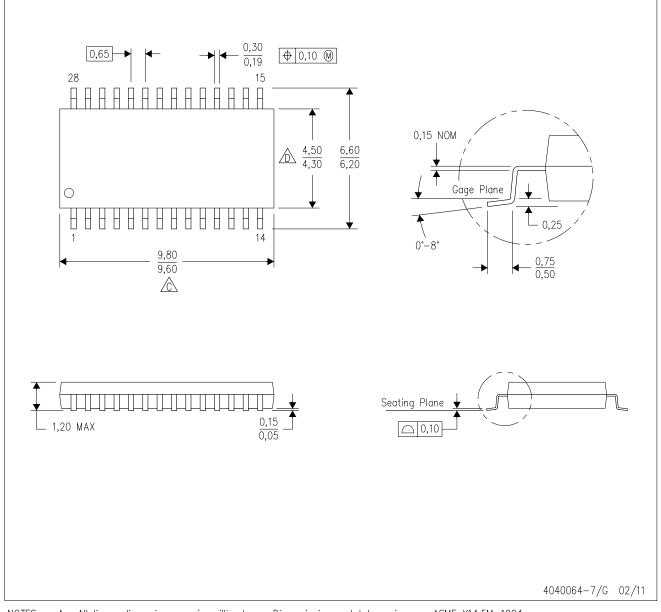

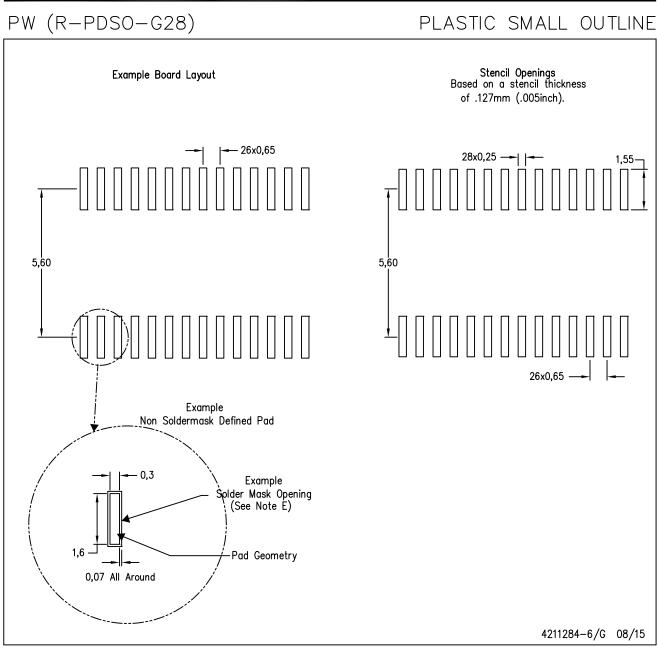

## 器件信息(1)

| 器件型号      | 封装         | 封装尺寸(标称值)       |

|-----------|------------|-----------------|

| PGA450-Q1 | TSSOP (28) | 9.70mm x 4.40mm |

|           |            |                 |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

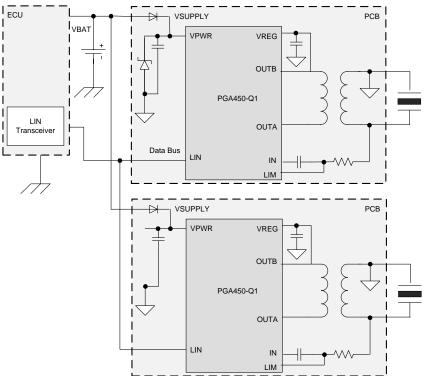

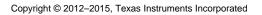

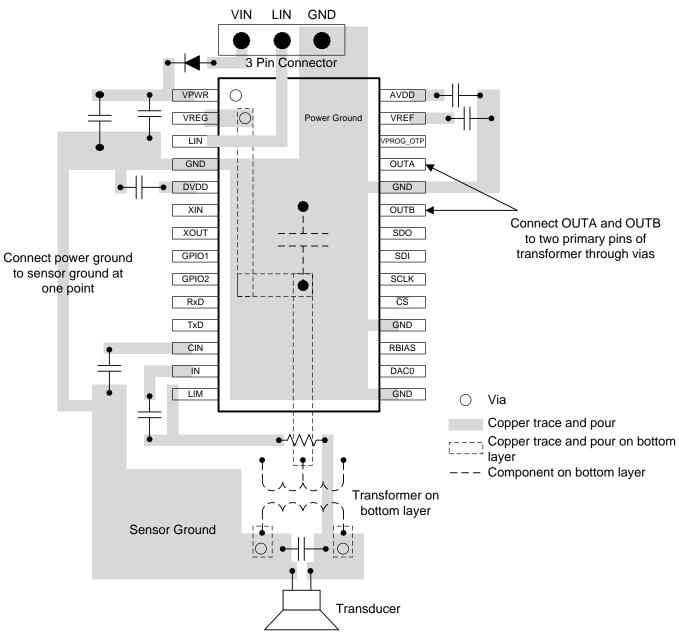

## 典型应用图

## 目录

| 1 | 特性   |                                                             |

|---|------|-------------------------------------------------------------|

| 2 | 应用   |                                                             |

| 3 | 说明   |                                                             |

| 4 | 修订   | 历史记录                                                        |

| 5 |      | Configuration and Functions 4                               |

| 6 | Spe  | cifications5                                                |

|   | 6.1  | Absolute Maximum Ratings 5                                  |

|   | 6.2  | ESD Ratings 5                                               |

|   | 6.3  | Recommended Operating Conditions 5                          |

|   | 6.4  | Thermal Information 6                                       |

|   | 6.5  | Electrical Characteristics 6                                |

|   | 6.6  | Electrical Characteristics — LIN 2.1 Slave and Buffered SCI |

|   | 6.7  | Electrical Characteristics — SPI Interface                  |

|   | 6.8  | Timing Requirements 8                                       |

|   | 6.9  | Timing Requirements — LIN 2.1 Slave and Buffered SCI        |

|   | 6.10 | Timing Requirements — SPI Interface 10                      |

|   | 6.11 | Switching Characteristics 10                                |

|   | 6.12 | 9                                                           |

|   | 6.13 | Typical Characteristics 13                                  |

| 7  | Deta | ailed Description           | 14  |

|----|------|-----------------------------|-----|

|    | 7.1  | Overview                    | 14  |

|    | 7.2  | Functional Block Diagram    | 14  |

|    | 7.3  | Feature Description         |     |

|    | 7.4  | Device Functional Modes     | 54  |

|    | 7.5  | Programming                 | 56  |

|    | 7.6  | Register Maps               |     |

| 8  | Арр  | lication and Implementation | 116 |

|    | 8.1  | Application Information     | 116 |

|    | 8.2  | Typical Application         | 116 |

| 9  | Pow  | ver Supply Recommendations  | 121 |

| 10 | Lay  | out                         | 121 |

|    | 10.1 | Layout Guidelines           | 121 |

|    | 10.2 | Layout Example              | 122 |

| 11 | 器件   | 年和文档支持                      | 123 |

|    | 11.1 | 文档支持                        | 123 |

|    | 11.2 | 2 社区资源                      | 123 |

|    | 11.3 | 商标                          | 123 |

|    | 11.4 | 静电放电警告                      | 123 |

|    | 11.5 | 术语表                         | 123 |

| 12 | 机械   | 载、封装和可订购信息                  | 123 |

|    |      |                             |     |

## 4 修订历史记录

2

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision A (April 2012) to Revision B

| • | 已将停车距离更改为停车辅助系统(应用和说明部分)                                                                                                                                                                                                                                                                                                                          | 1  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | 已添加 ESD 额定值表,特性描述部分,器件功能模式,应用和实施部分,电源相关建议部分,布局部分,器件和文档<br>支持部分以及机械、封装和可订购信息部分。                                                                                                                                                                                                                                                                    | 1  |

| • | Added the external crystal parameter to the Timing Requirements table                                                                                                                                                                                                                                                                             | 8  |

| • | Changed active bit to ACTIVE_EN bit and added VREG_EN; updated <i>Power-Up Waveforms</i> figure in the <i>Power</i><br>Supply Block section.                                                                                                                                                                                                      | 16 |

| • | Removed ; this field can be updated by the 8051W from the last paragraph in the Clock Synchronizer Using the SYNC Field in the LIN Bus section                                                                                                                                                                                                    | 18 |

| • | Updated the Burst Generator figure                                                                                                                                                                                                                                                                                                                | 20 |

| • | Changed all instances of LS in to Low-side in <i>Description</i> column of <i>Low-Side MOSFET Gate Drive Modes ITEM</i><br>DESCRIPTION table                                                                                                                                                                                                      | 20 |

| • | Changed register names in the description column of the <i>Low-Side MOSFET Gate Drive Modes ITEM</i><br><i>DESCRIPTION</i> table: ENABLE CONTROL to EN_CTRL, PULSE COUNT A to PULSE_CNTA, PULSE COUNT B to<br>PULSE_CNTB, BURST_ONA to ON_A, BURST_OFFA to OFF_A, BURST_ONB to ON_B, BURST_OFFB to<br>OFF_B. Removed Set by SFR from Description. | 20 |

| • | Changed For TI Use Only to Reserved.                                                                                                                                                                                                                                                                                                              | 21 |

| • | Updated the Digital Data Path figure                                                                                                                                                                                                                                                                                                              | 23 |

| • | Changed MODE bits to mode bits, changed FIFO CONTROL register to FIFO control register and added (FIFO_CTRL) to Datapath Output Format Control section                                                                                                                                                                                            | 35 |

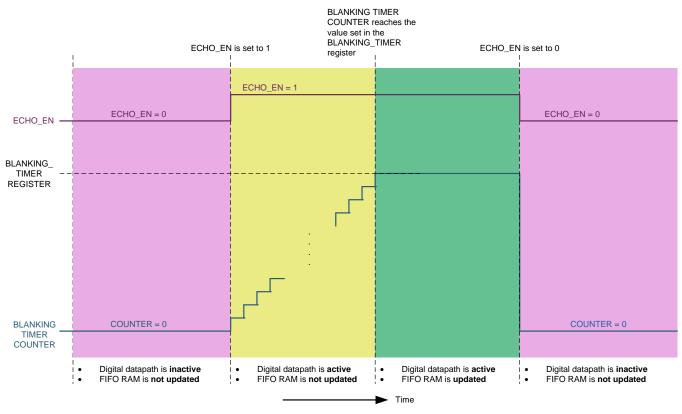

| • | Added (EN_CTRL) and changed ENABLE CONTROL register to enable control register in the Datapath Activation and Blanking Timer.                                                                                                                                                                                                                     | 36 |

| • | Updated the States of Digital Datapath figure                                                                                                                                                                                                                                                                                                     |    |

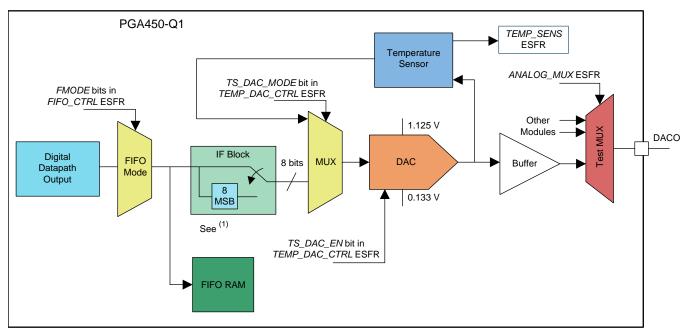

| • | Changed ANALOG MUX ESFR to ANALOG_MUX ESFR, removed all caps for temperature sensor and digital datapath, changed TEMP_CTRL to TEMP_DAC_CTRL in the Digital Datapath Output Mode section.                                                                                                                                                         |    |

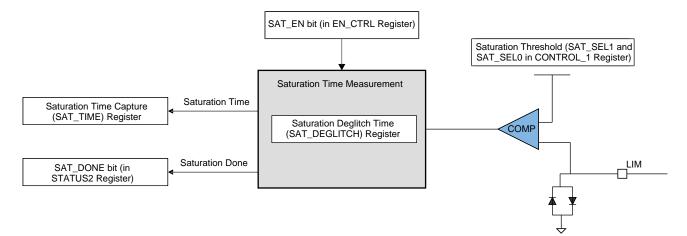

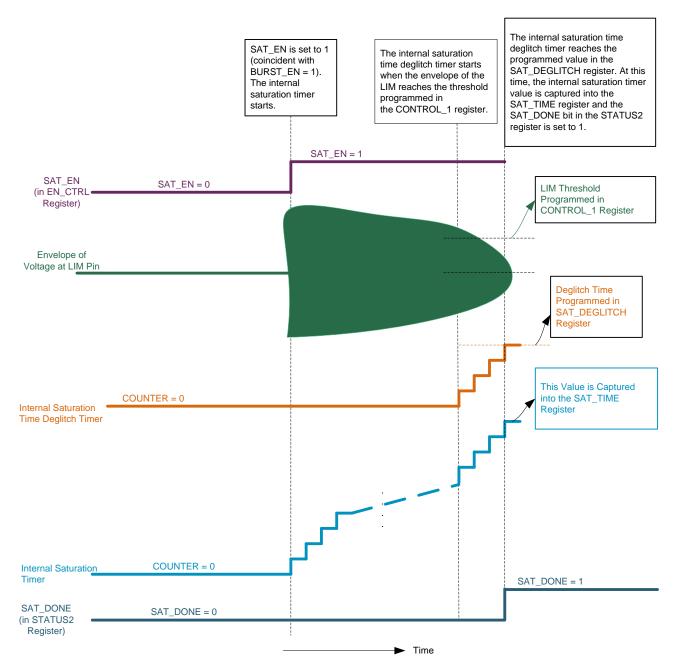

| • | Added (EN_CTRL), (SAT_DEGLITCH), and (SAT_TIME) register name definitions, changed uppercase register                                                                                                                                                                                                                                             |    |

www.ti.com.cn

Page

## TEXAS INSTRUMENTS

www.ti.com.cn

## 修订历史记录 (接下页)

|   | names to lower case, changed second bullet from: SATURATION THRESHOLD register to: Saturation threshold is set by the SAT_SEL1 and SAT_SEL0 bits in CONTROL_1 register in <i>Transducer Saturation Time</i> section                                                                                                                                                   | . 37 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Updated the Transducer Saturation-Time Measurement Block figure                                                                                                                                                                                                                                                                                                       | 37   |

| • | Changed ENABLE CONTROL register to EN_CTRL, changed SATURATION DEGLITCH TIME register to SAT_DEGLITCH register, changed SATURATION TIME CAPTURE register to SAT_TIME register, changed sentence from: When this voltage goes below the programmed threshold in the SATURATION THRESHOLD register to: When this voltage goes below the programmed saturation threshold | . 38 |

| • | Changed room temperature to 30°C; changed Temperature = 0.75 to Temperature = 1.75 in <i>Temperature Sensor</i> section.                                                                                                                                                                                                                                              | 39   |

| • | Updated the Timing Diagram Showing the Measurement of Transducer Saturation Time figure                                                                                                                                                                                                                                                                               | . 39 |

| • | Changed FREE RUNNING TIMER to free-running timer, added (FRT) coin, changed register to ESFR, changed CAP_FR_TMR to CAP_FR_TIMER.                                                                                                                                                                                                                                     | . 40 |

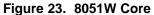

| • | Added: which is stored in the FIFO_POINTER register to FIFO Memory for Digital Datapath Output section.                                                                                                                                                                                                                                                               | . 41 |

| • | Deleted unless the entire OTP is erased by a UV-light EPROM eraser from the following sentence: After an address is programmed, it cannot be programmed again. in the OTP Programming section.                                                                                                                                                                        | . 43 |

| • | Removed: Use MOVX commands to place data in external memory addresses 0x0400 through 0x041F                                                                                                                                                                                                                                                                           | . 45 |

| • | Updated the LIN Registers figure                                                                                                                                                                                                                                                                                                                                      | 47   |

| • | Switched 1 and 0 under HOLD in LIN Frame-Control Configuration section.                                                                                                                                                                                                                                                                                               | . 48 |

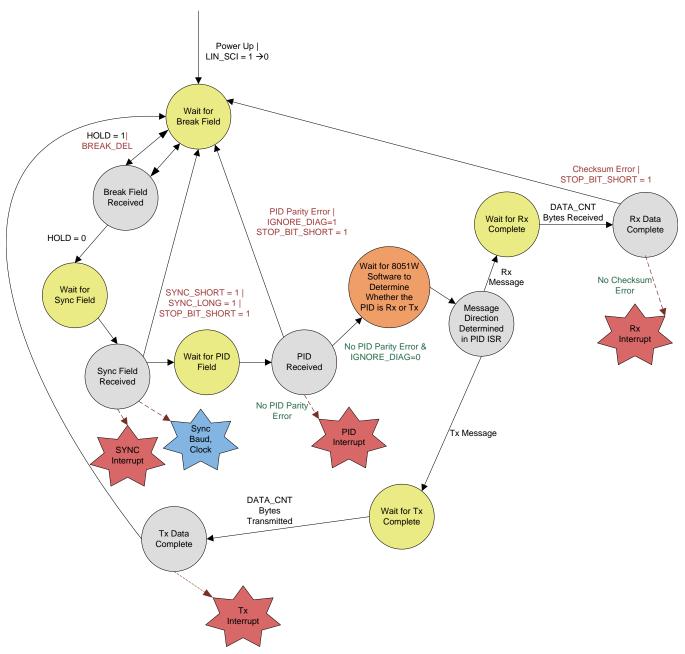

| • | Changed If there is a parity error to: If there is no parity error in LIN Slave-Protocol State Machine                                                                                                                                                                                                                                                                | . 49 |

| • | Updated the LIN Controller State Machine figure                                                                                                                                                                                                                                                                                                                       | 51   |

| • | Changed Rx to receive in LIN Slave Protocol Rx section.                                                                                                                                                                                                                                                                                                               | 51   |

| • | Changed receive to transmit and TX to transmit in the LIN Slave Protocol Tx section.                                                                                                                                                                                                                                                                                  | . 51 |

| • | Removed: of the PID field under STOP_BIT_VAL in the LIN Slave Framing Error Status section.                                                                                                                                                                                                                                                                           | . 51 |

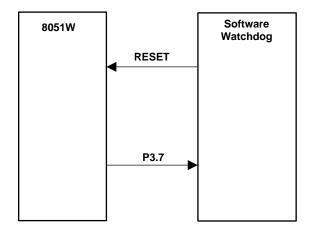

| • | Changed CPU_WD_EN to SW_WD_EN                                                                                                                                                                                                                                                                                                                                         | 62   |

Texas Instruments

www.ti.com.cn

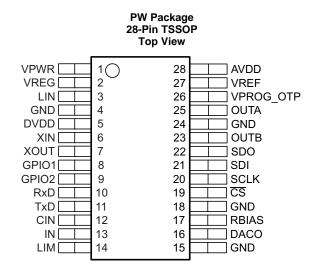

## 5 Pin Configuration and Functions

### **Pin Functions**

| PIN |           | 1/0 | DESCRIPTION                              |  |  |  |  |

|-----|-----------|-----|------------------------------------------|--|--|--|--|

| NO. | NAME      | 20  | DESCRIPTION                              |  |  |  |  |

| 1   | VPWR      | Ι   | Supply voltage                           |  |  |  |  |

| 2   | VREG      | 0   | Regulated voltage for transducer         |  |  |  |  |

| 3   | LIN       | I/O | LIN communication bus                    |  |  |  |  |

| 4   |           |     |                                          |  |  |  |  |

| 15  | GND       |     | Ground                                   |  |  |  |  |

| 18  | GND       | _   | Ground                                   |  |  |  |  |

| 24  |           |     |                                          |  |  |  |  |

| 5   | DVDD      | 0   | Regulated voltage for digital core       |  |  |  |  |

| 6   | XIN       | Ι   | Crystal input                            |  |  |  |  |

| 7   | XOUT      | 0   | Crystal out                              |  |  |  |  |

| 8   | GPIO1     | I/O | Constal surpose I/O 1 and 2              |  |  |  |  |

| 9   | GPIO2     | 20  | General-purpose I/O 1 and 2              |  |  |  |  |

| 10  | RxD       | Ι   | 8051W UART Rx (Port 3_0)                 |  |  |  |  |

| 11  | TxD       | 0   | 8051W UART Tx (Port 3_1)                 |  |  |  |  |

| 12  | CIN       | Ι   | Input capacitor                          |  |  |  |  |

| 13  | IN        | Ι   | Transducer receive input                 |  |  |  |  |

| 14  | LIM       | Ι   | Transducer receive limit                 |  |  |  |  |

| 16  | DACO      | 0   | DAC output                               |  |  |  |  |

| 17  | RBIAS     | Ι   | Bias resistor (100 k $\Omega$ to ground) |  |  |  |  |

| 19  | CS        | Ι   | SPI chip select                          |  |  |  |  |

| 20  | SCLK      | Ι   | SPI clock                                |  |  |  |  |

| 21  | SDI       | Ι   | SPI slave data in                        |  |  |  |  |

| 22  | SDO       | 0   | SPI slave data out                       |  |  |  |  |

| 23  | OUTB      | 0   | Transducer drive output B                |  |  |  |  |

| 25  | OUTA      | 0   | Transducer drive output A                |  |  |  |  |

| 26  | VPROG_OTP | Ι   | OTP programming voltage                  |  |  |  |  |

| 27  | VREF      | 0   | Reference voltage for ADC                |  |  |  |  |

| 28  | AVDD      | 0   | Regulated voltage for analog             |  |  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                           |                     | MIN  | MAX            | UNIT |

|-----------------------------------------------------------|---------------------|------|----------------|------|

| Power-supply voltage                                      | VPWR                | -0.3 | 40             | V    |

|                                                           | VREG, VPROG_OTP pin | -0.3 | 10             | V    |

|                                                           | LIN                 | -27  | 40             | V    |

| Valessa                                                   | RBIAS, CIN, IN      | -0.3 | 3              | V    |

| Voltage                                                   | DVDD, XIN, XOUT     | -0.3 | 40<br>10<br>40 | V    |

|                                                           | OUTA, OUTB          | -0.3 | 40             | V    |

|                                                           | LIM                 | -1.5 | 1.5            | V    |

| Voltage on all other pins, VMAX                           |                     | -0.3 | 6              | V    |

| Low-side FET current, IFET                                |                     |      | 1.5            | Α    |

| Maximum operating junction temperature, T <sub>Jmax</sub> |                     | -40  | 150            | °C   |

| Storage temperature, T <sub>stg</sub>                     |                     | -40  | 125            | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions are not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                              |                                 | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------|---------------------------------|-------|------|

|                    |                         | Human body model (HBM), per AEC Q10          | 0-002 <sup>(1)</sup>            | ±2000 |      |

|                    |                         | IEC61000-4-2 <sup>(2)</sup>                  | LIN pin                         | ±8000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per AEC Q100-011 | Corner pins (1, 14, 15, and 28) | ±750  | V    |

|                    |                         | 0100-011                                     | Other pins                      | ±500  |      |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

(2) Per IEC61000-4-2:1995 specification, contact with no external capacitor.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                             |                                                                                  | MIN | NOM | MAX | UNIT |

|-------------------|---------------------------------------------|----------------------------------------------------------------------------------|-----|-----|-----|------|

| VPWR              | Power-supply voltage                        |                                                                                  | 7   |     | 18  | V    |

|                   |                                             | Power up, $T_A = 105^{\circ}C$                                                   |     |     | 50  | mA   |

| IPWR              | Power-supply current                        | Active mode <sup>(1)</sup> temperature sensor off, $T_A$<br>= 105°C, VPWR = 18 V |     |     | 15  | mA   |

|                   |                                             | Quiet mode <sup>(1)</sup> , $T_A = 105^{\circ}C$ , VPWR = 18 V                   |     |     | 7.5 | mA   |

| <b>IPWR</b> AVG   | Average power-supply current <sup>(1)</sup> |                                                                                  |     |     | 10  | mA   |

| T <sub>A</sub>    | Operating ambient temperature               |                                                                                  | -40 |     | 105 | °C   |

| C <sub>VREG</sub> | Capacitance on VREG pin                     |                                                                                  | 10  |     | 470 | μF   |

| C <sub>VPWR</sub> | Capacitance on VPWR pin <sup>(2)</sup>      |                                                                                  | 47  |     | 100 | μF   |

| C <sub>ESR</sub>  | ESR of capacitor on VREG pin                |                                                                                  |     | 2   |     | Ω    |

(1) The average current is defined as: I<sub>pwr</sub>(Average) = 0.3I<sub>active</sub> + 0.7I<sub>quiet</sub> Active Mode: The entire device is active.

Quiet Mode: LNA, A/D, digital datapath, and OUTA/B are OFF. Microprocessor and LIN are still active. Add 100 mA to these currents if capacitor on VREG is charging

(2) The average current site and VDMD to be at most 4 V/me.

(2) The capacitor value must allow a discharge rate on VPWR to be at most 1 V/ms.

### PGA450-Q1

ZHCS861B-APRIL 2012-REVISED JUNE 2015

www.ti.com.cn

NSTRUMENTS

**EXAS**

## 6.4 Thermal Information

|                 |                                           | PGA450-Q1   |      |

|-----------------|-------------------------------------------|-------------|------|

|                 | THERMAL METRIC <sup>(1)</sup>             | PWP (TSSOP) | UNIT |

|                 |                                           | 28 PINS     |      |

| $R_{\thetaJA}$  | Junction-to-ambient thermal resistance    | 68.7        | °C/W |

| $R_{\thetaJC}$  | Junction-to-case (top) thermal resistance | 11.6        | °C/W |

| $R_{\theta JB}$ | Junction-to-board thermal resistance      | 27.6        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

|                        | PARAMETER                                  | TES                                            | ST CONDITIONS                                                | MIN  | TYP         | MAX  | UNIT  |

|------------------------|--------------------------------------------|------------------------------------------------|--------------------------------------------------------------|------|-------------|------|-------|

| POWER SUPP             | PLY                                        |                                                |                                                              |      |             |      |       |

| VPWR <sub>POR</sub>    | VPWR voltage for POR to occur              | POR is deas                                    | serted                                                       | 3    |             | 4.2  | V     |

| V <sub>AVDD</sub>      | AVDD pin voltage                           | IAVDD = 5 m                                    | AVDD = 5 mA                                                  |      | 5           | 5.25 | V     |

| I <sub>AVDD</sub>      | AVDD pin load current                      |                                                |                                                              |      |             | 5    | mA    |

| V <sub>DVDD</sub>      | DVDD pin voltage                           |                                                |                                                              |      | 1.8         |      | V     |

| VREF                   | VREF pin voltage                           |                                                |                                                              |      | 3           |      | V     |

| VREG                   |                                            |                                                |                                                              |      |             |      |       |

| VREC                   | Transducer primary voltage tolerance       | IREG = 100                                     | VPWR = 7 V<br>VREG_SEL = 0_XXX for<br>4.7 V-5.4 V            |      | ±100        |      | mV    |

| VREG <sub>TOL</sub>    | Transuccer primary voltage tolerance       | μA                                             | VPWR = 10 V<br>VREG_SEL = 1_XXX for<br>7.7 V-8.4 V           |      | ±150        |      | IIIV  |

| VREG <sub>CHARGE</sub> | Transducer voltage droop while<br>charging | IREG = 100<br>setting                          | mA, below VREG_SEL                                           |      | 500         |      | mV    |

| VREG <sub>READY</sub>  | VREG_READY threshold                       | Below VREG_SEL setting                         |                                                              |      | 250         |      |       |

| hana                   | VREG output current                        | VPWR > VR                                      | EG_SEL + 2.5 V                                               | 90   | 100         | 110  | mA    |

| I <sub>VREG</sub>      | WEG bulpat carrent                         | VPWR > VR                                      | VPWR > VREG_SEL + 2 V                                        |      |             |      | μA    |

| VREG <sub>I_S2G</sub>  | VREG short-to-ground protection<br>current | VPWR = 16 V, T <sub>A</sub> = 105 °C, no burst |                                                              |      |             | 110  | mA    |

| LOW-SIDE DR            | RIVE MOSFETS                               |                                                |                                                              |      |             |      |       |

| r <sub>ds(on)</sub>    | FET ON resistance                          | $I_{load} = 500 \text{ m}$                     | A, T <sub>A</sub> = 105 °C                                   |      |             | 1.2  | Ω     |

| I <sub>PULSE</sub>     | Drain pulse current                        | 50 kHz                                         |                                                              |      |             | 1.5  | Α     |

|                        | Drive clamping voltage                     | $Vgs = 0 V, I_d$                               | <sub>d</sub> = 10 mA                                         | 40   |             |      | V     |

|                        | Leakage current                            |                                                |                                                              |      |             | 5    | μA    |

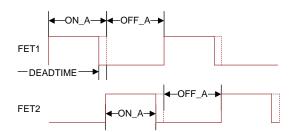

| LOW NOISE A            | MPLIFIER                                   |                                                |                                                              |      |             |      |       |

|                        |                                            | LNA_GAIN s                                     | etting = 0b00                                                | 1680 | 1750        | 1820 |       |

| Δ                      | Gain                                       | LNA_GAIN s                                     | etting = 0b01                                                | 892  | 892 930 968 |      | V/V   |

| A <sub>V</sub>         | Gain                                       | LNA_GAIN Setting = 0b10                        |                                                              | 496  | 517         | 538  | V/V   |

|                        |                                            | LNA_GAIN Setting = 0b11                        |                                                              | 99   | 104         | 109  |       |

| R <sub>IN</sub>        | Input impedance                            | 40 kHz                                         |                                                              | 100  |             |      | kΩ    |

|                        | Clamp voltage                              |                                                |                                                              | -1.5 |             | 1.5  | V     |

| I <sub>LIM</sub>       | Input current limit                        |                                                |                                                              |      |             | 200  | mA    |

|                        | Noise (input-referred of the signal chain) | IN pin = GNI<br>frequency =<br>kHz             | D, T <sub>A</sub> = 105 °C, center<br>40 kHz, Bandwidth = 10 |      | 0.7         |      | µVrms |

|                        | Input-referred PSRR                        | VPWR = 7 V                                     | , LNA gain setting = 0b00                                    |      | 93          |      | dB    |

| 12-BIT ADC             |                                            |                                                |                                                              |      |             |      |       |

| V <sub>ADCREF</sub>    | Input voltage range                        |                                                |                                                              | 0    |             | 3    | V     |

|                        | DNL                                        | 20% to 80%                                     | input range                                                  |      | 2.5         |      | LSB   |

## **Electrical Characteristics (continued)**

|                      | PARAMETER                              | TEST CONDITIONS                                                    | MIN   | TYP   | MAX   | UNIT    |

|----------------------|----------------------------------------|--------------------------------------------------------------------|-------|-------|-------|---------|

|                      | INL                                    | 20% to 80% input range, best-fit curve                             |       | 4     |       | LSB     |

|                      | Gain                                   | Best-fit curve                                                     | 1373  | 1378  | 1383  | LSB/V   |

|                      | Offset                                 | Best-fit curve                                                     |       | -15   |       | LSB     |

| 8-BIT DAC            |                                        |                                                                    |       |       |       |         |

| V <sub>DAC_MAX</sub> | Output range                           |                                                                    | 0.133 |       | 1.125 | V       |

|                      | Gain                                   |                                                                    |       | 3.9   |       | mV/Code |

|                      | Offset voltage                         | Output when DAC code is 000h at $R_{load}$ = 100 k $\Omega$ to GND |       | 0.133 |       | V       |

|                      | Full-scale voltage                     | Output when DAC code is $0xFF R_{load}$<br>= 100 k $\Omega$ to GND |       | 1.125 |       | V       |

| I <sub>DAC</sub>     | Output current                         | DAC Code = 0x00<br>DAC Code = 0xFF, $R_{load}$ = 100 k $\Omega$    |       |       | 12.5  | μA      |

|                      | INL                                    |                                                                    | -2    |       | 2     | LSB     |

|                      | DNL                                    |                                                                    | -1    |       | 1     | LSB     |

|                      | Capacitance load                       |                                                                    |       | 10    |       | pF      |

| TRANSDUCE            | R SATURATION TIME                      | · · · · · · · · · · · · · · · · · · ·                              |       |       |       |         |

|                      |                                        | SAT_SEL = 200 mV                                                   |       | 200   |       | mV      |

| .,                   |                                        | SAT_SEL = 300 mV                                                   |       | 300   |       | mV      |

| V <sub>SAT_TH</sub>  | Saturation threshold                   | SAT_SEL = 400 mV                                                   |       | 400   |       | mV      |

|                      |                                        | SAT_SEL = 600 mV                                                   |       | 600   |       | mV      |

| TEMPERATU            | IRE SENSOR                             | · · · · · ·                                                        |       |       |       |         |

|                      | Temperature sensor range               |                                                                    | -40   |       | 140   | °C      |

|                      | Temperature accuracy                   | –40°C to 105°C                                                     | -5    |       | 5     | °C      |

|                      | Temperature sensor code                | 30°C                                                               |       | 0     |       | LSB     |

|                      | Temperature sensor LSB                 |                                                                    |       | 1.75  |       | °C/LSB  |

| GPIOS, 8051          | UART Tx AND Rx                         | łł                                                                 |       |       |       |         |

| VIH                  | GPIO input mode, high, Rx,             | R <sub>load</sub> > 10 kΩ                                          | 3.5   |       | 5.3   | V       |

| VIL                  | GPIO input mode, low, Rx               |                                                                    | -0.3  |       | 1.5   | V       |

| R <sub>PULLUP</sub>  | Internal pullup on input               | Pullup is to AVDD                                                  |       | 100   |       | KΩ      |

| VOH                  | GPIO strong-mode output, high, Tx      | I <sub>OH</sub> = 5 mA                                             | 4     |       |       | V       |

| VOL                  | GPIO strong-mode output, low, Tx       | $I_{OL} = 5 \text{ mA}$                                            |       |       | 0.8   | V       |

|                      | Total current on GPIO1 + GPIO2 +Tx pin | No load on AVDD pin                                                |       |       | 5     | mA      |

| MEMORY               |                                        | · ·                                                                |       |       |       |         |

|                      | OTP programming voltage                |                                                                    | 7.5   | 8     | 8.5   | V       |

|                      | OTP programming current                |                                                                    | 2     |       | 5     | mA      |

| DIAGNOSTIC           |                                        | · /                                                                |       |       |       |         |

| VPWR_OV              | VPWR overvoltage level                 |                                                                    | 25    | 28    | 32    | V       |

| AVDD_UV              | VPWR for AVDD undervoltage             |                                                                    |       | 5.6   |       | V       |

| AVDD_OC              | AVDD Overcurrent                       |                                                                    | 45    | 55    | 65    | mA      |

| RBIAS_OC             | RBIAS Overcurrent                      |                                                                    | 65    | 80    | 90    | μA      |

|                      | Low-side driver A/B drain monitor      |                                                                    | 2.2   | 2.5   | 2.8   | V       |

|                      | Low-side driver A/B monitor            |                                                                    | 2.2   | 2.5   | 2.8   | V       |

|                      | Over temperature shut-off protection   |                                                                    | 150   |       | 200   | °C      |

|                      | 1                                      |                                                                    |       |       |       | -       |

### PGA450-Q1 ZHCS861B-APRIL 2012-REVISED JUNE 2015

www.ti.com.cn

STRUMENTS

EXAS

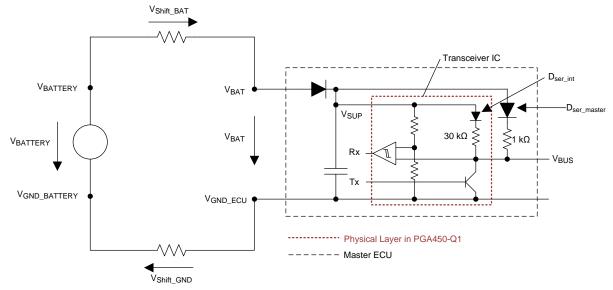

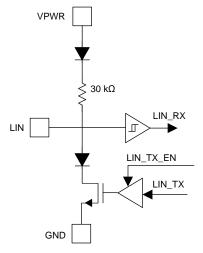

## 6.6 Electrical Characteristics — LIN 2.1 Slave and Buffered SCI<sup>(1)(2)</sup>

| PARAMETER                | TEST CONDITIONS                                                                                               | MIN   | ТҮР | MAX   | UNIT             |

|--------------------------|---------------------------------------------------------------------------------------------------------------|-------|-----|-------|------------------|

| I <sub>BUS_LIM</sub>     | V <sub>BUS</sub> = 18 V                                                                                       | 40    |     | 200   | mA               |

| I <sub>BUS_PAS_dom</sub> | Driver off, V <sub>BUS</sub> = 0V, V <sub>PWR</sub> = 12 V                                                    | -1    |     |       | mA               |

| I <sub>BUS_PAS_rec</sub> | Driver off, 7 V < V <sub>PWR</sub> < 18 V, 8 V < V <sub>BUS</sub> < 18 V, V <sub>BUS</sub> > V <sub>PWR</sub> |       |     | 20    | μA               |

| I <sub>BUS_NO_GND</sub>  | $GND_{Device} = V_{PWR}, 0 < V_{BUS} < 18 V, V_{PWR} = 12 V$                                                  | -1    |     | 1     | mA               |

| I <sub>BUS_NO_BAT</sub>  | V <sub>PWR</sub> = GND, 0 < V <sub>BUS</sub> < 18 V                                                           |       |     | 100   | μA               |

| V <sub>BUSdom</sub>      | Receiver dominant state                                                                                       |       |     | 0.4   | V <sub>PWR</sub> |

| V <sub>BUSrec</sub>      | Receiver recessive state                                                                                      | 0.6   |     |       | V <sub>PWR</sub> |

| V <sub>BUS_CNT</sub>     | $V_{BUS\_CNT} = (V_{th\_dom} + V_{th\_rec})/2$                                                                | 0.475 | 0.5 | 0.525 | V <sub>PWR</sub> |

| V <sub>HYS</sub>         | $V_{HYS} = V_{th_rec} - V_{th_dom}$                                                                           |       |     | 0.175 | V <sub>PWR</sub> |

| R <sub>Slave</sub>       | Serial resistor                                                                                               | 20    | 30  | 60    | KΩ               |

| C <sub>IN</sub>          | Input capacitance on LIN pin                                                                                  |       | 60  |       | pF               |

(1) LIN Mode:

LIN 2.1 physical layer and LIN protocol (Section 2.1 of LIN 2.1) specification

Exceptions: No wake-up (Section 2.6.2 of LIN 2.1) No transport layer in digital logic (Section 3 of LIN 2.1) No node configuration and identification services in digital (Section 4 of LIN 2.1)

No diagnostic layer in digital logic (Section 5 of LIN 2.1) The device is not certified for LIN compliance. Communication baud rate is fixed at 19.2 kBPS.

(2) SCI Mode: None

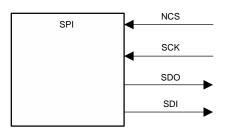

## 6.7 Electrical Characteristics — SPI Interface

|                     | PARAMETER                                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------|------------------------------------------|-----------------|-----|-----|-----|------|

|                     | High-level voltage (CS, SCK, SDI, SDO)   |                 | 3.5 |     |     | V    |

|                     | Low-level voltage (CS, SCK, SDI,<br>SDO) |                 |     |     | 1.5 | V    |

| C <sub>L(SDO)</sub> | Capacitive load for data output (SDO)    |                 |     | 10  |     | pF   |

## 6.8 Timing Requirements

|                   |                                                        |                                                                                                                     | MIN   | NOM | MAX  | UNIT |

|-------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| POWER SUP         | PPLY                                                   |                                                                                                                     |       |     |      |      |

| t <sub>PU</sub>   | Power-up time – AVDD and DVDD reach regulation levels. | VPWR = 7 V to 18 V, VREG is not in regulation                                                                       |       |     | 10   | ms   |

| CLOCK             |                                                        |                                                                                                                     |       |     |      |      |

|                   | External crystal                                       |                                                                                                                     |       | 16  |      | MHz  |

| F <sub>OSC</sub>  | Internal oscillator frequency                          | 25°C                                                                                                                | 15.8  | 16  | 16.2 | MHz  |

| F <sub>DUTY</sub> | Internal oscillator duty cycle                         |                                                                                                                     |       | 50% |      |      |

|                   | Internal oscillator frequency                          | Before LIN sync                                                                                                     | -4%   |     | 4%   |      |

|                   | accuracy                                               | LIN baud rate = 19.2 kBPS, after LIN sync                                                                           | -0.5% |     | 0.5% |      |

| 8-bit DAC         |                                                        |                                                                                                                     |       |     |      |      |

|                   | Settling time                                          | Code 0x00 to 0xFF step. Output is 90% of full scale. $R_{load} = k\Omega$ to GND. $C_{load} = 10 \text{ pF}$ to GND |       |     | 20   | μs   |

| DIAGNOSTIC        | cs                                                     |                                                                                                                     |       |     |      |      |

|                   | Low-side driver A/B fault                              | LS_FAULT_TIMER_2 = 1 µs setting                                                                                     |       | 1   |      | μs   |

|                   | deglitch time                                          | LS_FAULT_TIMER_2 = 2 µs setting                                                                                     |       | 2   |      | μs   |

|                   | Software watchdog time-out                             |                                                                                                                     |       | 250 |      | ms   |

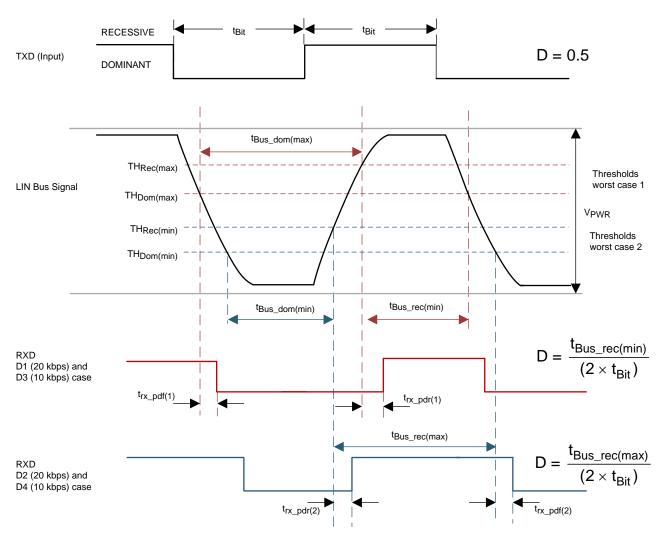

## 6.9 Timing Requirements — LIN 2.1 Slave and Buffered SCI<sup>(1)(2)</sup>

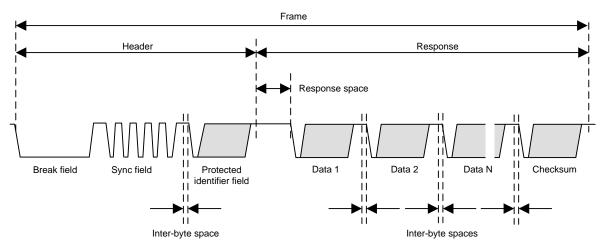

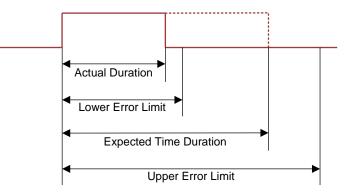

Figure 1 shows the LIN timing details.

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                         | MIN   | NOM | MAX   | UNIT |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| D1                  | $\begin{array}{l} TH_{Rec(max)} = 0.744 \times V_{PWR}; \ TH_{Dom(max)} = 0.581 \times V_{PWR}; \\ V_{PWR} = 7 \ V_{18} \ V; \ t_{Bit} = 50 \ \mu s; \ D1 = t_{Bus\_rec(min)} / \ (2 \times t_{Bit}) \ Load_1; \\ C_{BUS} = 1 \ nF; \ R_{BUS} = 1 \ K\Omega \ Load_2; \\ C_{BUS} = 6.8 \ nF; \ R_{BUS} = 660 \ \Omega \ Load_3; \ C_{BUS} = 10 \ nF; \ R_{BUS} = 500 \ \Omega, \ see \ Figure \ 1. \end{array}$         | 0.396 |     |       |      |

| D2                  | $\begin{array}{l} TH_{Rec(min)} = 0.522 \times V_{PWR}; \ TH_{Dom(min)} = 0.284 \times V_{PWR}; \\ V_{PWR} = 7.6 \ V18 \ V; \ t_{Bit} = 50 \ \mu s; \ D2 = t_{Bus\_rec(max)}/\ (2 \times t_{Bit}) \ Load_1; \\ C_{BUS} = 1 \ nF; \ R_{BUS} = 1 \ k\Omega \ Load_2; \\ C_{BUS} = 6.8 \ nF; \ R_{BUS} = 660 \ \Omega \ Load_3; \ C_{BUS} = 10 \ nF; \ R_{BUS} = 500 \ \Omega, \ see \ Figure \ 1. \end{array}$            |       |     | 0.581 |      |

| D3                  | $\begin{array}{l} TH_{Rec(max)} = 0.778 \times V_{PWR}; \ TH_{Dom(max)} = 0.616 \times V_{PWR}; \ V_{PWR} = 7 \ V \ to \ 18 \ V; \\ t_{Bit} = 96 \ \mu s; \ D4 = t_{Bus\_rec(min)} \ / \ (2 \times t_{Bit}) \ Load_1; \ C_{BUS} = 1 \ nF; \ R_{BUS} = 1 \ k\Omega \ Load_2; \\ C_{BUS} = 6.8 \ nF; \ R_{BUS} = 660 \ \Omega \ Load_3; \ C_{BUS} = 10 \ nF; \ R_{BUS} = 500 \ \Omega, \ see \ Figure \ 1. \end{array}$   | 0.417 |     |       |      |

| D4                  | $\begin{array}{l} TH_{Rec(min)} = 0.389 \times V_{PWR}; \ TH_{Dom(min)} = 0.251 \times V_{PWR}; \ V_{PWR} = 7.6 \ V \ to \ 18 \ V; \\ t_{Bit} = 96 \ \mu s; \ D4 = t_{Bus\_rec(max)} \ / \ (2 \times t \ Bit) \ Load_1; \ C_{BUS} = 1 \ nF; \ R_{BUS} = 1 \ k\Omega \ Load_2; \\ C_{BUS} = 6.8 \ nF; \ R_{BUS} = 660 \ \Omega \ Load_3; \ C_{BUS} = 10 \ nF; \ R_{BUS} = 500 \ \Omega, \ see \ Figure \ 1. \end{array}$ |       |     | 0.590 |      |

| t <sub>rx_pd</sub>  | Propagation delay of receiver<br>$R_{RXD} = 2.4 \text{ k}\Omega$ ; $C_{RXD} = 20 \text{ pF}$                                                                                                                                                                                                                                                                                                                            |       |     | 6     | μs   |

| t <sub>rx_sym</sub> | Symmetry of receiver propagation delay rising edge with respect to falling edge $R_{RXD}$ = 2.4 k $\Omega$ ; C $_{RXD}$ = 20 pF                                                                                                                                                                                                                                                                                         | -2    |     | 2     | μs   |

(1) LIN Mode:

LIN 2.1 physical layer and LIN protocol (Section 2.1 of LIN 2.1) specification Exceptions: No wake-up (Section 2.6.2 of LIN 2.1) No transport layer in digital logic (Section 3 of LIN 2.1)

No node configuration and identification services in digital (Section 4 of LIN 2.1) No diagnostic layer in digital logic (Section 5 of LIN 2.1)

The device is not certified for LIN compliance. Communication baud rate is fixed at 19.2 kBPS.

(2) SCI Mode: None

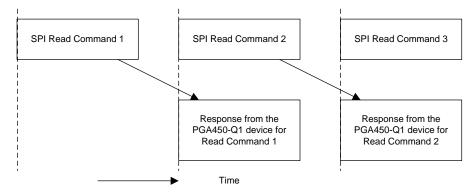

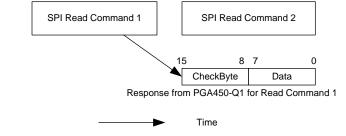

## 6.10 Timing Requirements — SPI Interface

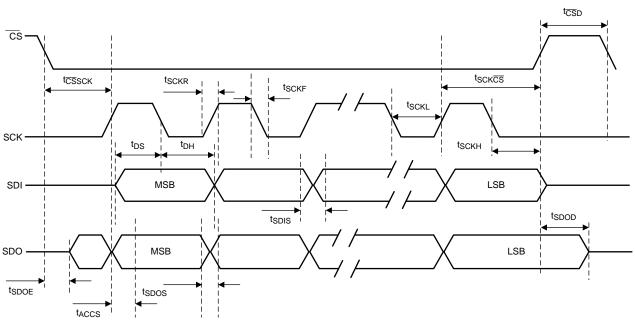

Figure 2 shows the SPI clocking details.

|                     |                                                            |                                           | MIN  | NOM | MAX | UNIT |

|---------------------|------------------------------------------------------------|-------------------------------------------|------|-----|-----|------|

| f <sub>SCK</sub>    | SPI frequency                                              |                                           |      |     | 8   | MHz  |

| t <sub>CSSCK</sub>  | CS low to first SCK rising edge                            |                                           | 125  |     |     | ns   |

| t <sub>SCK</sub> CS | Last SCK rising edge to $\overline{\text{CS}}$ rising edge |                                           | 125  |     |     | ns   |

| t <sub>CSD</sub>    | CS disable time                                            |                                           | 375  |     |     | ns   |

| t <sub>DS</sub>     | SDI setup time                                             |                                           | 25   |     |     | ns   |

| t <sub>DH</sub>     | SDI hold time                                              |                                           | 25   |     |     | ns   |

| t <sub>SDIS</sub>   | SDI fall/rise time                                         |                                           |      |     | 25  | ns   |

| t <sub>SCKR</sub>   | SCK rise time                                              | See Figure 2.                             |      |     | 7   | ns   |

| t <sub>SCKF</sub>   | SCK fall time                                              |                                           |      |     | 7   | ns   |

| t <sub>SCKH</sub>   | SCK high time                                              |                                           | 62.5 |     |     | ns   |

| t <sub>SCKL</sub>   | SCK low time                                               |                                           | 62.5 |     |     | ns   |

| t <sub>SDO</sub>    | SDO enable time                                            |                                           |      |     | 25  | ns   |

| t <sub>ACCS</sub>   | SCK rising edge to SDO data valid                          |                                           |      |     | 25  | ns   |

| t <sub>SDOD</sub>   | SDO disable time                                           |                                           |      |     | 25  | ns   |

| t <sub>SDOS</sub>   | SDO rise/fall time                                         | $C_{SDO} = 10 \text{ pF}$ , see Figure 2. | 1    |     | 15  | ns   |

## 6.11 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                            | TEST CONDITIONS | MIN | TYP MAX | UNIT       |

|-----------------------|--------------------------------------|-----------------|-----|---------|------------|

| 12-BIT ADO            | 5                                    |                 |     |         |            |

|                       | Conversion time                      |                 |     | 1       | μs         |

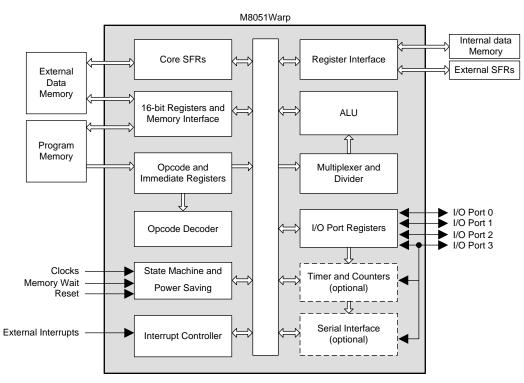

| 8051W WA              | RP CORE                              | •               | •   |         | -          |

| F <sub>CORE_CLK</sub> | Core frequency                       |                 |     | 16      | MHz        |

|                       | Memory interface                     |                 |     | 1       | Wait State |

| MEMORY                |                                      |                 |     |         |            |

|                       | OTP programming time                 | 1 byte          | 100 |         | μs         |

|                       | OTP data retention years             | 105 °C          |     | 10      | Years      |

|                       | EEPROM R/W cycles                    |                 |     | 1000    | Cycles     |

|                       | EEPROM data retention                | 105 °C          |     | 10      | Years      |

|                       | EEPROM programming time              | 32 Bytes        |     | 70      | ms         |

| DIAGNOST              | TICS                                 |                 |     |         |            |

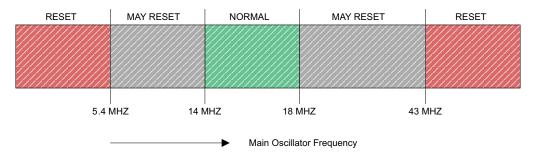

|                       | Main oscillator underfrequency fault |                 |     | 14      | MHz        |

|                       | Main oscillator overfrequency fault  |                 | 18  |         | MHz        |

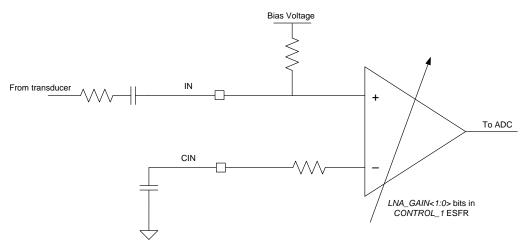

## 6.12 Digital Datapath Filter Switching Characteristics

| PARAMETER                                               | TEST CONDITIONS | MIN | TYP | MAX | UNIT    |

|---------------------------------------------------------|-----------------|-----|-----|-----|---------|

| BAND-PASS FILTER<br>FILTER TYPE: SECOND-ORDER BUTTERWOR | TH FILTER       |     |     |     |         |

| Band-pass center frequency                              |                 | 40  |     | 70  | kHz     |

| Band-pass center-frequency step size                    |                 |     | 0.5 |     | kHz     |

| Bandpass filter bandwidth                               |                 | 4   |     | 7   | kHz     |

| Bandpass filter bandwidth step size                     |                 |     | 0.5 |     | kHz     |

| BPF gain                                                |                 |     | 0   |     | dB      |

| DOWNSAMPLE                                              |                 |     |     |     |         |

| Downsample rate                                         |                 | 25  |     | 50  | Samples |

| Downsample-rate step size                               |                 |     | 1   |     |         |

## **Digital Datapath Filter Switching Characteristics (continued)**

| PARAMETER                                                 | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------------------------------------------------|-----------------|-----|-----|-----|------|

| LOW-PASS FILTER<br>FILTER TYPE: FIRST-ORDER BUTTERWORTH I | FILTER          |     |     |     |      |

| LPF cutoff frequency                                      |                 | 0.5 |     | 4   | kHz  |

| LPF cutoff frequency step size                            |                 |     | 0.5 |     | kHz  |

| LPF gain                                                  |                 |     | 0   |     | dB   |

Figure 1. LIN Timing Diagram

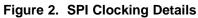

## 6.13 Typical Characteristics

VPWR = 12 V,  $T_A = 25^{\circ}C$

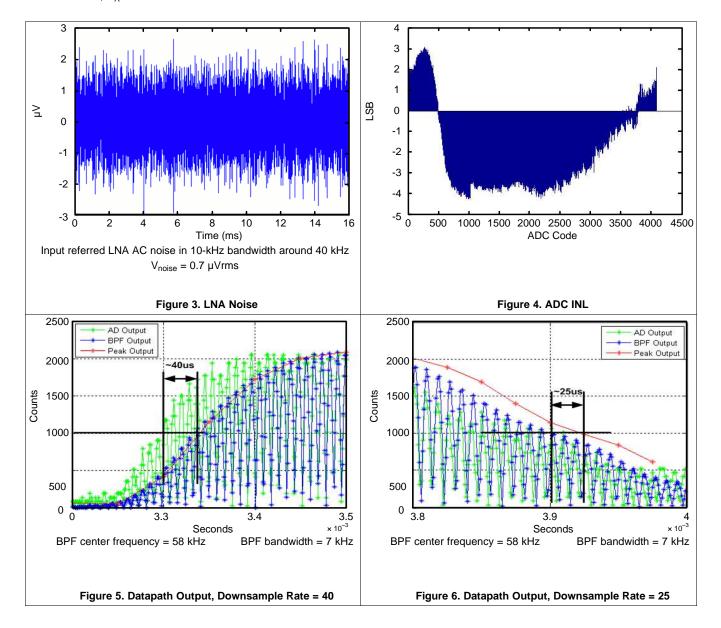

## 7 Detailed Description

## 7.1 Overview

The PGA450-Q1 integrates power management, low-side drivers, analog front-end, digital datapath, and interface functions to form a full ultrasonic-sensor signal conditioning solution. The low-side drivers are programmed to drive a specific frequency that matches the external ultrasonic transducer. After transmitting, the same transducer receives the reflected echo signal. The analog front-end filters and amplifies this signal before storing the data in memory. The integrated 8051 microcontroller then processes this data to extract the useful information which typically includes how far away an object is from the transducer. At this point in the process, the information is transmitted through LIN, SCI, or UART.

## 7.2 Functional Block Diagram

Copyright © 2012–2015, Texas Instruments Incorporated

### 7.3 Feature Description

## 7.3.1 Power Supply Block

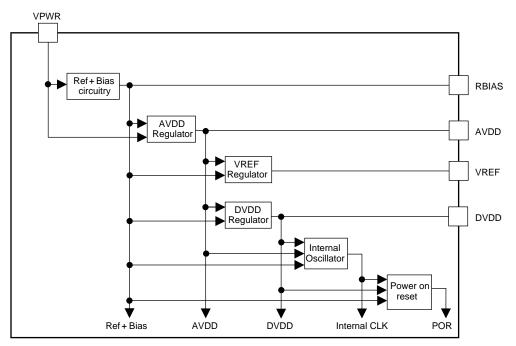

The PGA450-Q1 uses three internal regulators (AVDD, DVDD, and VREF) as supplies for all of the internal circuits. The power-supply block also generates a precision voltage reference, current bias, and internal clock. The internal power-on-reset (POR) signal is released when the internal power supplies, voltage reference, current bias, and internal clock come into regulation.

Figure 7 shows the relationships of the power supplies and the POR signal in the PGA450-Q1 device.

Figure 7. Power-Supply Block

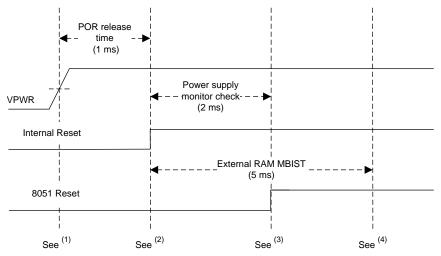

The PGA450-Q1 begins to power up when a voltage is applied to the VPWR pin. Figure 8 shows a typical power-up diagram. The power-up time is typically about 3 ms.

TEXAS INSTRUMENTS

www.ti.com.cn

## Feature Description (continued)

- (1) The VPWR ramp reaches POR level.

- (2) The internal reset to the digital core is released and EXTERNAL RAM MBIST is initiated. SPI communication is available.

- (3) 8051W reset is deasserted. Software starts execution.

- (4) EXTERNAL RAM MBIST is complete. External Scratchpad RAM and FIFO RAM available for use.

### Figure 8. Power-Up Waveforms

The PGA450-Q1 provides two power-control bits for enabling different analog blocks to manage the total current consumption of the device. On power up, the device is in the *QUIET* mode with only the 8051W and LIN transceiver turned on. All other analog blocks are disabled. Setting the ACTIVE\_EN bit enables the low-side drivers required for bursting as well as the echo-processing circuitry that includes the LNA and the ADC. In addition, a separate control bit, VREG\_EN, is provided to enable the VREG circuitry, which is used to charge the external capacitor used during bursting.

The AVDD pin can be used to source current for up to 5 mA for resistive loads, including the loads on the GPIO and Tx pins.

| CONTROL BIT DEFAU |                          | DEFAULT  | FUNCTION                                                                                                          |

|-------------------|--------------------------|----------|-------------------------------------------------------------------------------------------------------------------|

| 1                 | VREG_EN                  | Disabled | Enables the VREG circuitry that provides the 100-mA current to charge the external capacitor used during bursting |

| 2                 | ACTIVE_EN <sup>(1)</sup> | Disabled | Enables the LNA, ADC, ADC REF, and other support circuitry related to burst generation and echo processing        |

#### Table 1. Power Modes

(1) ACTIVE\_EN bit must be set before enabling the burst / saturation or echo-enable bits.

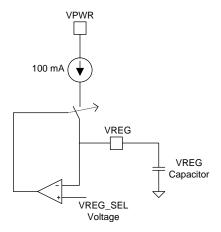

### 7.3.2 VREG

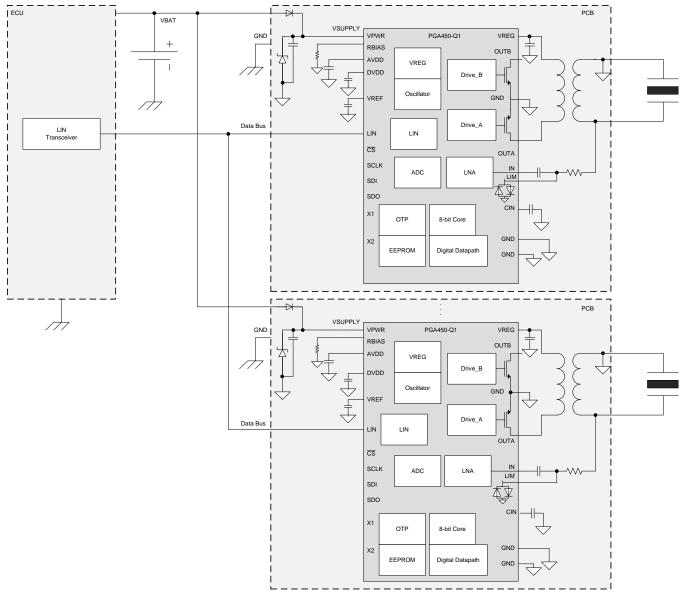

The PGA450-Q1 provides a regulated voltage output which, along with an external capacitor, can be used to drive the primary of the transformer used to excite the transducer. The VREG regulator provides a 100-mA current, sourced from VPWR, to charge the external capacitor. The user can select the desired VREG voltage by setting the VREG\_SEL register to the appropriate value.

For VREG to be regulated to the selected voltage, VPWR must be at least 2 V above the selected VREG voltage.

The energy required for the burst comes from the external capacitor. The device has a VREG\_READY status bit in the STATUS2 register to indicate when the capacitor is fully charged and has reached the regulation voltage.

Figure 9. VREG Regulator

This block is disabled by default. Setting the VREG\_EN bit in the PWR\_MODE register to high, enables this regulator.

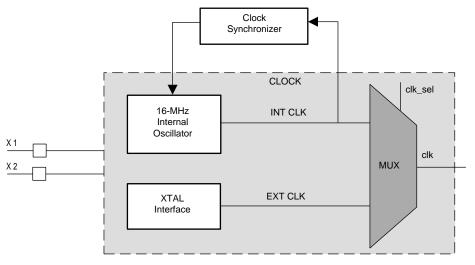

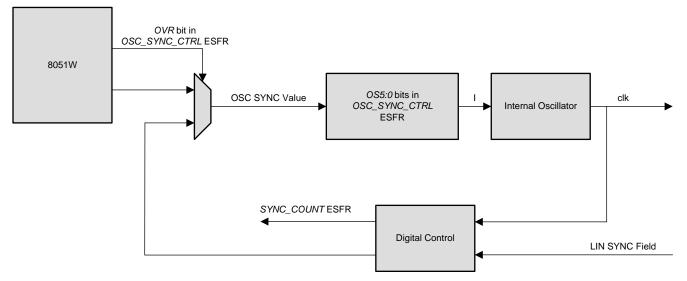

### 7.3.3 Clock

The clock block generates the system clock that is used in the generation of burst, communication, echo time measurement, and the microprocessor clock. Figure 10 shows the clock block in the PGA450-Q1.

Figure 10. Clock Block in PGA450-Q1

The CLK signal provided to various blocks inside the device is derived from one of the following sources:

- 1. Internal oscillator without synchronization with communication: in this mode, the internal oscillator output is the source for the system clock.

- 2. Internal oscillator with synchronization with communication: in this mode, the internal oscillator output is *corrected* for inaccuracy using time measurements of the communication bus. This mode requires the implementation of *CLOCK SYNCHRONIZER* logic in the digital control block. The clock synchronizer uses the *SYNC FIELD* to measure the timer value and adjust the internal oscillator output.

- 3. External crystal: in this mode, a 16-MHz external crystal is the source of the system clock.

The clock source is controlled by the CLK\_SEL register. Table 2 lists the settings of the CLK\_SEL bits and the corresponding clock mode.

| Ų | Texas<br>Instruments |

|---|----------------------|

| Y |                      |

| CLK_SEL BIT VALUES | CLOCK SOURCE                                                               |

|--------------------|----------------------------------------------------------------------------|

| 0b00               | Internal clock. Ignore the synchronization pulse received on the LIN bus.  |

| 0b01               | Internal clock. Process the synchronization pulse received on the LIN bus. |

| 0b10               | External crystal clock                                                     |

| 0b11               | Internal clock. Ignore the synchronization pulse received on the LIN bus.  |

#### Table 2. Clock Selection

#### 7.3.3.1 Clock Synchronizer Using the SYNC Field in the LIN Bus

The clock synchronizer block adjusts the internal oscillator based on a SYNC field in the LIN frame received in the communication line. The internal clock is trimmed to 16 MHz with  $\pm 4\%$  tolerance in the TI factory.

The clock synchronizer improves the instantaneous accuracy of the internal oscillator frequency to 16 MHz  $\pm 0.5\%$  using the LIN SYNC field, assuming an ideal LIN baud rate of 19.2 kBPS. The synchronization algorithm uses the time between two falling edges of the LIN SYNC field to adjust the internal oscillator.

The SYNC\_COUNT is available for the 8051W to determine the effectiveness of the synchronization process based on the LIN SYNC field. That is, if the synchronization was effective, then the SYNC COUNT value should be close to 1667 ±8 counts.

This OSC SYNC value can also be updated by the 8051W microprocessor by setting the OVR bit in OSC\_SYNC\_CTRL ESFR.

Table 3 lists the value of OS<5:0> and the resulting change in frequency.

| OS<5:0> | Delta Frequency |

|---------|-----------------|

| 0       | –3.84 MHz       |

|         |                 |

| 31      | –120 kHz        |

| 32      | 0 kHz           |

| 33      | 120 kHz         |

|         |                 |

| 63      | 3.72 MHz        |

### NOTE

The clock synchronization feature is not available if the device is configured in SCI buffered mode. See the *LIN 2.1 Slave and Buffered SCI* section for details.

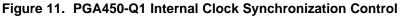

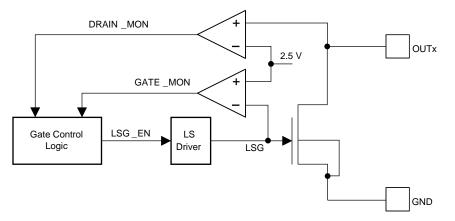

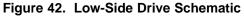

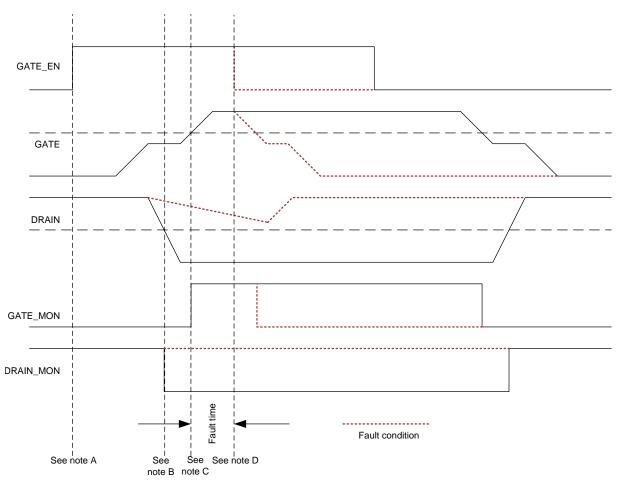

## 7.3.4 Low-Side Drive FETs

The PGA450-Q1 provides two low-side drivers for driving the primary of a transformer or an equivalent load. The *Burst Generator* section describes the control and drive modes for the low-side drive.

The low-driver block also has diagnostics. See the *Diagnostics* section for a description of the diagnostics.

Figure 12 shows the schematic of the low-side drive

Figure 12. Low-Side Drive Block Diagram

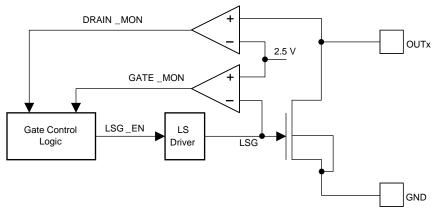

#### 7.3.5 Burst Generator

The burst generator block generates the high-frequency pulses used to drive the gates of the low-side FETs. The low-side FETs ultimately drive the transducer by modulating the primary of the transformer.

The PGA450-Q1 provides mode bits in the BURST MODE register (see the *Burst Mode Register (offset = 0xB3)* [reset = 0] section) to configure each low-side drive MOSFET in three possible drive modes.

The three possible drive modes are:

- **Single-ended:** In this mode, one low-side switch is used to turn current on and off in the primary of the transformer. The rate of change of current in the primary generates a voltage in the secondary of the transformer, which is connected to the transducer.

- **Push-pull:** In this mode, two low-side switches are used to turn current on and off in two primary coils in the transformer. The primary coils have the same number of turns. The rate of change of current in the primary generates a voltage in the secondary of the transformer, which is connected to the transducer. The direction of current in the secondary generates voltages of opposite polarity in the secondary, effectively doubling the peak-to-peak voltage in the secondary.

8051W port drive: In this mode, the low-side switches are controlled through the an 8051W port pin.

Figure 13 shows the block diagram of the burst generator. The figure shows that the burst generator has a number of registers which the user software must configure.

PGA450-Q1 ZHCS861B-APRIL 2012-REVISED JUNE 2015

www.ti.com.cn

**ISTRUMENTS**

EXAS

### Figure 13. Burst Generator

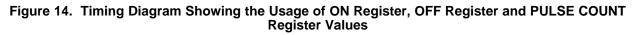

The PGA450-Q1 provides 3 mode bits in the BURST MODE register to select from the five burst configurations available. Table 4 lists the modes of operation of the two low-side gate drives of the burst generator. For an understanding of the configurations, see Figure 14 and for an understanding of the waveforms, see Figure 15.

| Table 4. I | _ow-Side | MOSFET | Gate | Drive | Modes |  |

|------------|----------|--------|------|-------|-------|--|

|            |          |        |      |       |       |  |

| ITEM                                  | DESCRIPTION                                                                                                     |  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Mode Bits in BURST_MODE Register: 000 |                                                                                                                 |  |

| Mode description                      | Low-side A and B are in push-pull                                                                               |  |

| Low-side A trigger                    | Write 1 to BURST_A_EN bit in EN_CTRL register                                                                   |  |

| Low-side B trigger                    | Write 1 to BURST_A_EN bit in EN_CTRL register                                                                   |  |

| No. of pulses on A                    | Set by PULSE_CNTA (0–63 pulses) register                                                                        |  |

| No. of pulses on B                    | Set by PULSE_CNTB (0–63 pulses) register                                                                        |  |

| Low-side A frequency                  | Set by registers:<br>• ON_A (11 bits at 16 MHz)<br>• OFF_A (11 bits at 16 MHz)<br>• DEADTIME (8 bits at 16 MHz) |  |

| Low-side B frequency                  | Set by registers: ON_A (11 bits at 16 MHz), OFF_A (11 bits at 16 MHz), DEADTIME (8 bits at 16 MHz)              |  |

| Mode Bits in BURST_MODE Register: 001 |                                                                                                                 |  |

| Mode description                      | Low-side A is controlled by burst generator A<br>Low-side B through the internal micro P2.1 port                |  |

| Low-side A trigger                    | Write 1 to BURST_A_EN bit in EN_CTRL register                                                                   |  |

| Low-side B trigger                    | Controlled by 8051W software                                                                                    |  |

| No. of pulses on A                    | Set by PULSE_CNTA (0–63 pulses) register                                                                        |  |

| No. of pulses on B                    | Controlled by 8051W software                                                                                    |  |

## Table 4. Low-Side MOSFET Gate Drive Modes (continued)

| ITEM                                  | DESCRIPTION                                                                                        |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------|--|

| Low-side A frequency                  | Set by registers:<br>• ON_A (11 bits at 16 MHz)<br>• OFF_A (11 bits at 16 MHz)                     |  |

| Low-side B frequency                  | Controlled by 8051W software                                                                       |  |

| Mode Bits in BURST_MODE Register: 010 |                                                                                                    |  |

| Mode description                      | Low-side A through the internal micro P2.0 port<br>Low-side B is controlled by burst generator B   |  |

| Low-side A trigger                    | Controlled by 8051W software                                                                       |  |

| Low-side B trigger                    | Write 1 to BURST_B_EN bit in EN_CTRL register                                                      |  |

| No. of pulses on A                    | Controlled by 8051W software                                                                       |  |

| No. of pulses on B                    | Set by PULSE_CNTB (0–63 pulses) register                                                           |  |

| Low-side A frequency                  | Controlled by 8051W software                                                                       |  |

| Low-side B frequency                  | Set by registers: ON_B (11 bits at 16 MHz) and OFF_B (11 bits at 16 MHz)                           |  |

| Mode Bits in BURST_MODE Register: 011 |                                                                                                    |  |

| Mode description                      | Low-side A is controlled by burst generator A<br>Low-side B is controlled by burst generator B     |  |

| Low-side A trigger                    | Write 1 to BURST_A_EN bit in EN_CTRL register                                                      |  |

| Low-Side B trigger                    | Write 1 to BURST_B_EN bit in EN_CTRL register                                                      |  |

| No. of pulses on A                    | Set by PULSE_CNTA (0-63 pulses) register                                                           |  |

| No. of pulses on B                    | Set by PULSE_CNTB (0–63 pulses) register                                                           |  |

| Low-side A frequency                  | Set by registers: ON_A (11 bits at 16 MHz) and OFF_A (11 bits at 16 MHz)                           |  |

| Low-side B frequency                  | Set by registers: ON_B (11 bits at 16 MHz) and OFF_B (11 bits at 16 MHz)                           |  |

| Mode Bits in BURST_MODE Register: 100 |                                                                                                    |  |

| Mode description                      | Low-side A through the internal micro P2.0 port<br>Low-side B through the internal micro P2.1 port |  |

| Low-side A trigger                    | Controlled by 8051W software                                                                       |  |

| Low-side B trigger                    | Controlled by 8051W software                                                                       |  |

| No. of pulses on A                    | Controlled by 8051W software                                                                       |  |

| No. of pulses on B                    | Controlled by 8051W software                                                                       |  |

| Low-side A frequency                  | Controlled by 8051W software                                                                       |  |

| Low-side B frequency                  | Controlled by 8051W software                                                                       |  |

| Mode Bits in BURST_MODE Register: 101 |                                                                                                    |  |

| Mode description                      | Reserved                                                                                           |  |

| Mode Bits in BURST_MODE Register: 110 |                                                                                                    |  |

| Mode description                      | Reserved                                                                                           |  |

| Mode Bits in BURST_MODE Register: 111 |                                                                                                    |  |

| Mode description                      | Reserved                                                                                           |  |

Figure 14 shows the relationship of BURST\_OUTx.

NSTRUMENTS

FXAS

The relationship between the ONTIME, OFFTIME, and DEADTIME values in the push-pull configurations are shown in Figure 15.

### Figure 15. Timing Diagram Showing the Relationship Between ONTIME, OFFTIME, and DEADTIME Registers in the Push-Pull Configuration

Table 5 lists the 8051W port pins used to drive the OUTA and OUTB pins are listed in the 8051W drive mode.

| PGA450-Q1 PIN | 8051W PORT |

|---------------|------------|

| OUTA          | 2.0        |

| OUTB          | 2.1        |

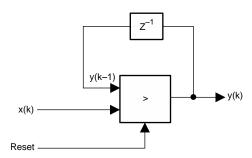

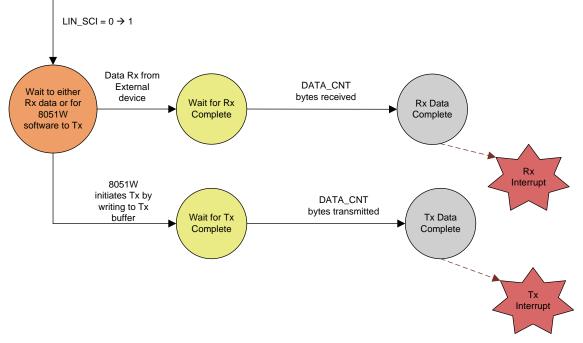

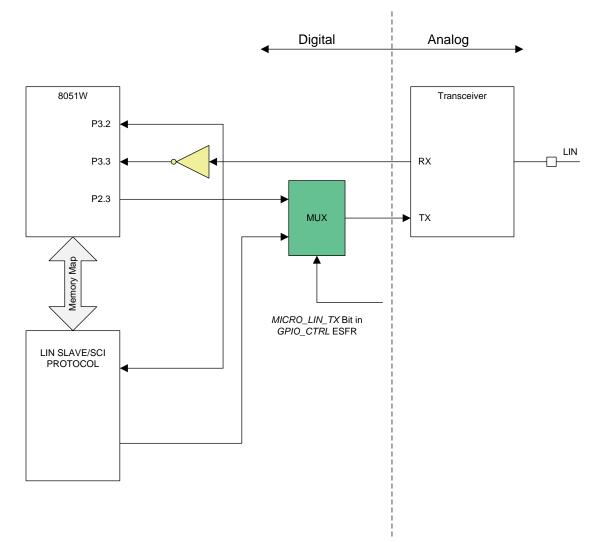

### Table 5. OUTA/OUTB Pin Map