🕳 Sample &

🖥 Buy

## ADS9110

Reference

Design

ZHCSE95A-OCTOBER 2015-REVISED OCTOBER 2015

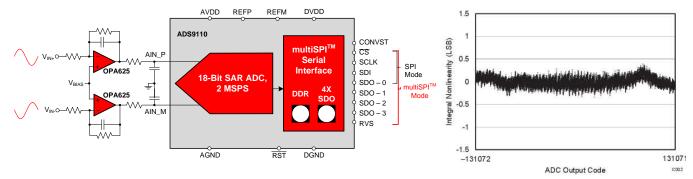

#### ADS9110 18 位、2MSPS、15mW SAR ADC, 具有 multiSPI™ 接口

Technical

Documents

#### 特性 1

- 采样率: 2MSPS

- 无延迟输出

- 出色的直流和交流性能:

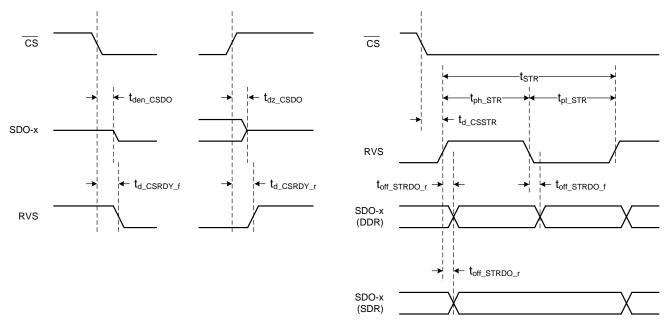

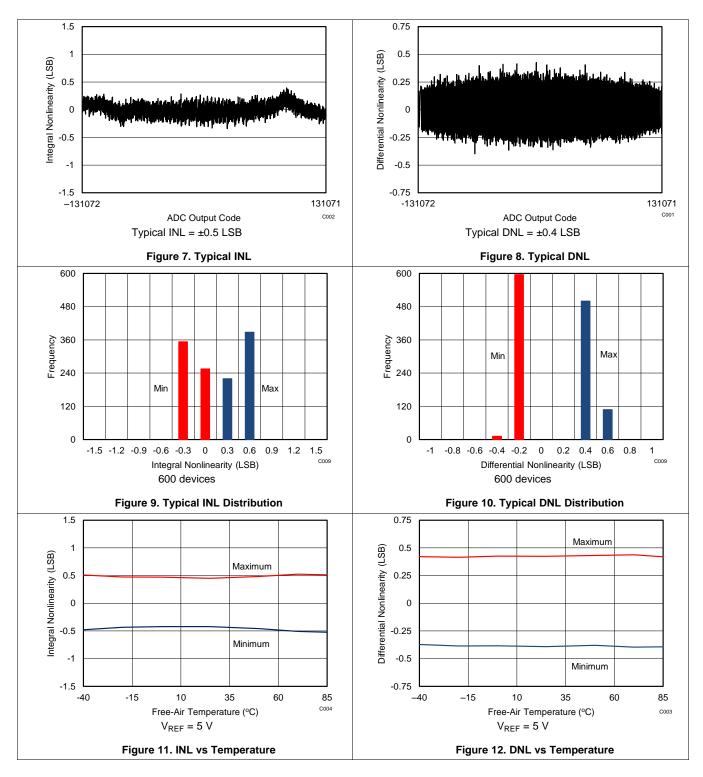

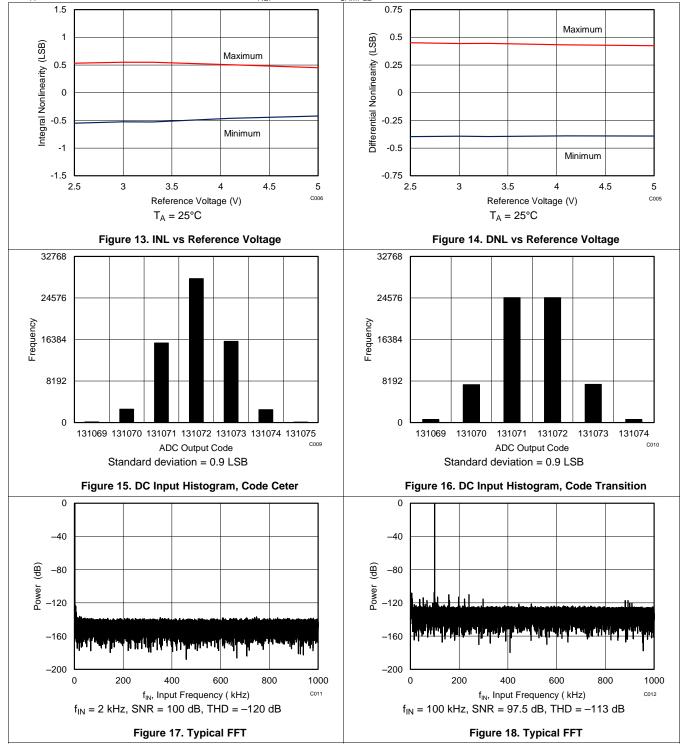

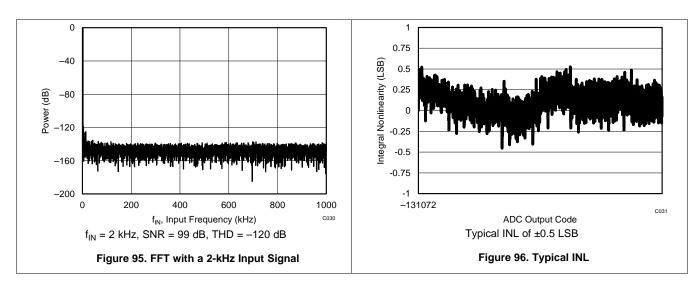

- 积分非线性 (INL): ±0.5 最低有效位 (LSB) (典 型值), ±1.5 LSB(最大值)

- 微分非线性 (DNL): ±0.75 LSB (最大值), 18 位无丢码 (NMC)

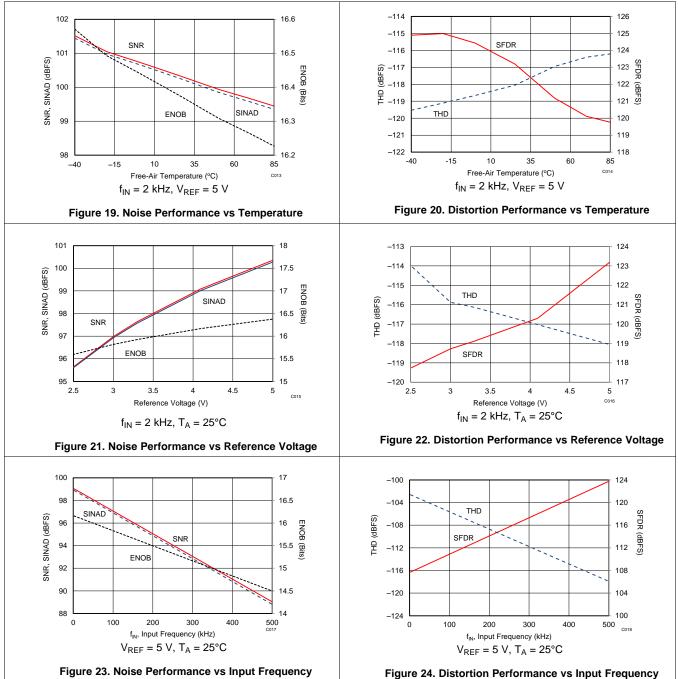

- 信噪比 (SNR): 100dB

- 总谐波失真 (THD): -118dB

- 宽输入范围:

- 单极差分输入范围: ±V<sub>RFF</sub>

- V<sub>RFF</sub> 输入范围: 2.5V 至 5V, 与 AVDD 无关

- 低功耗:

- 2MSPS 时为 9mW(仅限 AVDD)

- 2MSPS 时为 15mW(总功耗)

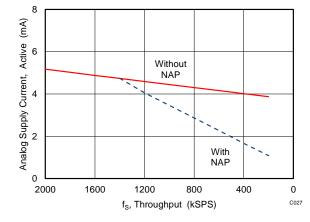

- 灵活的低功耗模式,可根据吞吐量调节功率

- multiSPI: 增强型串行接口

- 符合 JESD8-7A 标准的数字 I/O (1.8V DVDD 时)

- 在 -40℃ 至 +85℃ 的工业温度范围内完全额定运 行

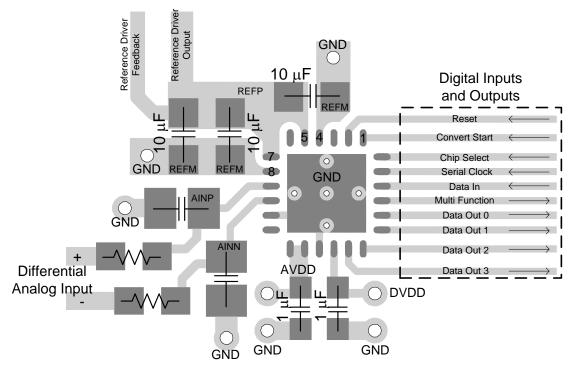

- 小型封装: 4mm × 4mm 超薄四方扁平无引线 (VQFN) 封装

- 2 应用

- 测试和测量

- 医疗成像

- 高精度、高速工业领域

## 3 说明

Tools &

Software

ADS9110 是一款 18 位、2MSPS、逐次逼近寄存器 (SAR) 模数转换器 (ADC), 在典型工作条件下具有 ±0.5 LSB INL 和 100dB SNR 规范值。 高吞吐量使得 开发者能够对输入信号进行过采样,从而提高测量的动 态范围和精度。

Support &

Community

20

该器件支持单极全差分模拟输入信号,并采用 2.5V 至 5V 的外部基准电压,能够提供宽输入选择范围,无需 额外进行输入调节。

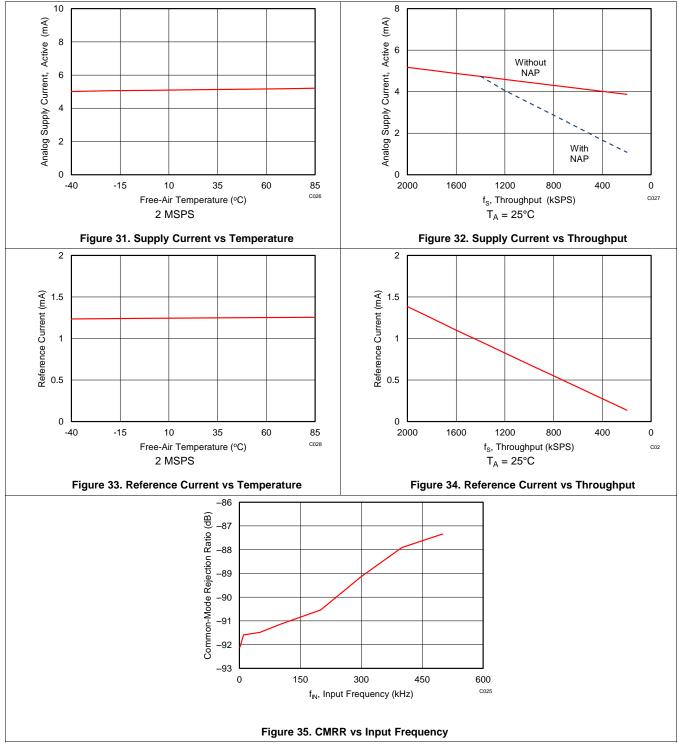

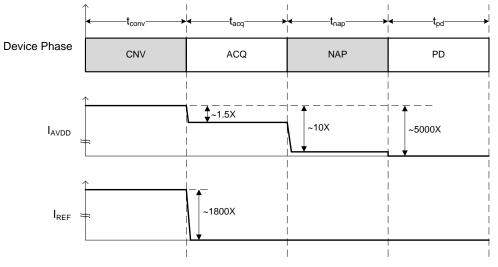

该器件以 2MSPS 全吞吐量运行时的功耗仅为 15mW。 吞吐量较低时,可灵活使用低功耗模式 (NAP 和 PD) 来降低功耗。

集成的 multiSPI 串行接口向后兼容传统 SPI™ 协议。 此外,该器件的可配置功能还能够简化电路板布局、时 序和固件,并且以低时钟速度运行时能够获得高吞吐 量,因此可轻松连接各种微控制器、数字信号处理器 (DSP) 以及现场可编程门阵列 (FPGA)。

该器件采用节省空间的 4mm × 4mm VQFN 封装, 支 持符合 JESD8-7A 标准的 I/O 和标准工业温度范围。

|         | 器件信息      |                 |

|---------|-----------|-----------------|

| 部件号     | 封装        | 封装尺寸(标称值)       |

| ADS9110 | VQFN (24) | 4.00mm x 4.00mm |

|         |           |                 |

如需了解所有可用封装,请见数据表末尾的可订购产品附录。

典型应用图以及积分非线性度与代码间的关系图

ADS9110 ZHCSE95A-OCTOBER 2015-REVISED OCTOBER 2015

## 目录

| 1 | 特性   |                                                                              |

|---|------|------------------------------------------------------------------------------|

| 2 | 应用   | 1                                                                            |

| 3 | 说明   | 1                                                                            |

| 4 | 修订   | 历史记录                                                                         |

| 5 | Pin  | Configuration and Functions                                                  |

| 6 | Spe  | cifications                                                                  |

|   | 6.1  | Absolute Maximum Ratings 4                                                   |

|   | 6.2  | ESD Ratings 4                                                                |

|   | 6.3  | Recommended Operating Conditions 4                                           |

|   | 6.4  | Thermal Information 4                                                        |

|   | 6.5  | Electrical Characteristics 5                                                 |

|   | 6.6  | Timing Requirements: Conversion Cycle7                                       |

|   | 6.7  | Timing Requirements: Asynchronous Reset, NAP, and PD7                        |

|   | 6.8  | Timing Requirements: SPI-Compatible Serial<br>Interface                      |

|   | 6.9  | Timing Requirements: Source-Synchronous Serial<br>Interface (External Clock) |

|   | 6.10 | Timing Requirements: Source-Synchronous Serial<br>Interface (Internal Clock) |

|   | 6.11 | Typical Characteristics 12                                                   |

| 7 | Deta | ailed Description 17                                                         |

# 4 修订历史记录

| Cł | nanges from Original (October 2015) to Revision A | Pag | je |

|----|---------------------------------------------------|-----|----|

| •  | 已发布为量产数据                                          |     | 1  |

|    | 7.1  | Overview                    | 17 |

|----|------|-----------------------------|----|

|    | 7.2  | Functional Block Diagram    | 17 |

|    | 7.3  | Feature Description         | 18 |

|    | 7.4  | Device Functional Modes     | 22 |

|    | 7.5  | Programming                 | 24 |

|    | 7.6  | Register Maps               | 44 |

| 8  | App  | lication and Implementation | 47 |

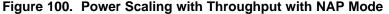

|    | 8.1  | Application Information     | 47 |

|    | 8.2  | Typical Application         | 50 |

| 9  | Pow  | er-Supply Recommendations   | 52 |

|    | 9.1  | Power-Supply Decoupling     | 52 |

|    | 9.2  | Power Saving                | 52 |

| 10 | Lay  | out                         | 54 |

|    | 10.1 | Layout Guidelines           | 54 |

|    | 10.2 | Layout Example              | 55 |

| 11 | 器件   | 和文档支持                       | 56 |

|    | 11.1 | 文档支持                        | 56 |

|    | 11.2 | 社区资源                        | 56 |

|    | 11.3 | 商标                          | 56 |

|    | 11.4 | 静电放电警告                      | 56 |

|    | 11.5 | Glossary                    | 56 |

| 12 | 机械   | 封装和可订购信息                    | 56 |

|    |      |                             |    |

TEXAS INSTRUMENTS

www.ti.com.cn

2

#### ADS9110 ZHCSE95A – OCTOBER 2015 – REVISED OCTOBER 2015

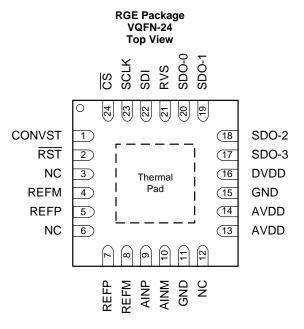

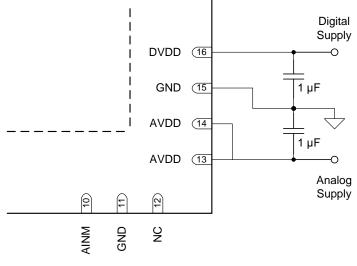

## 5 Pin Configuration and Functions

## **Pin Functions**

| P          | PIN      |                |                                                                                                                                                                                                                             |

|------------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO.      | FUNCTION       | DESCRIPTION                                                                                                                                                                                                                 |

| AINM       | 10       | Analog input   | Negative analog input                                                                                                                                                                                                       |

| AINP       | 9        | Analog input   | Positive analog input                                                                                                                                                                                                       |

| AVDD       | 13, 14   | Power supply   | Analog power supply for the device                                                                                                                                                                                          |

| CONVST     | 1        | Digital input  | Conversion start input pin for the device.<br>A CONVST rising edge brings the device from ACQ state to CNV state.                                                                                                           |

| CS         | 24       | Digital input  | Chip-select input pin for the device; active low<br>The device takes control of the data bus when $\overline{CS}$ is low.<br>The SDO-x pins go to tri-state when $\overline{CS}$ is high.                                   |

| DVDD       | 16       | Power supply   | Interface supply                                                                                                                                                                                                            |

| GND        | 11, 15   | Power supply   | Ground                                                                                                                                                                                                                      |

| NC         | 3, 6, 12 | No connection  | These pins must be left floating with no external connection                                                                                                                                                                |

| REFM       | 4, 8     | Analog input   | Reference ground potential                                                                                                                                                                                                  |

| REFP       | 5, 7     | Analog input   | Reference voltage input                                                                                                                                                                                                     |

| RST        | 2        | Digital input  | Asynchronous reset input pin for the device.<br>A low pulse on the RST pin resets the device and all register bits return to their default state.                                                                           |

| RVS        | 21       | Digital output | Multi-function output pin for the device.<br>With $\overline{CS}$ held high, RVS reflects the status of the internal ADCST signal.<br>With $\overline{CS}$ low, the status of RVS depends on the output protocol selection. |

| SCLK       | 23       | Digital input  | Clock input pin for the serial interface.<br>All system-synchronous data transfer protocols are timed with respect to the SCLK signal.                                                                                      |

| SDI        | 22       | Digital input  | Serial data input pin for the device.<br>This pin is used to feed the data or command into the device.                                                                                                                      |

| SDO-0      | 20       | Digital output | Serial communication: data output 0                                                                                                                                                                                         |

| SDO-1      | 19       | Digital output | Serial communication: data output 1                                                                                                                                                                                         |

| SDO-2      | 18       | Digital output | Serial communication: data output 2                                                                                                                                                                                         |

| SDO-3      | 17       | Digital output | Serial communication: data output 3                                                                                                                                                                                         |

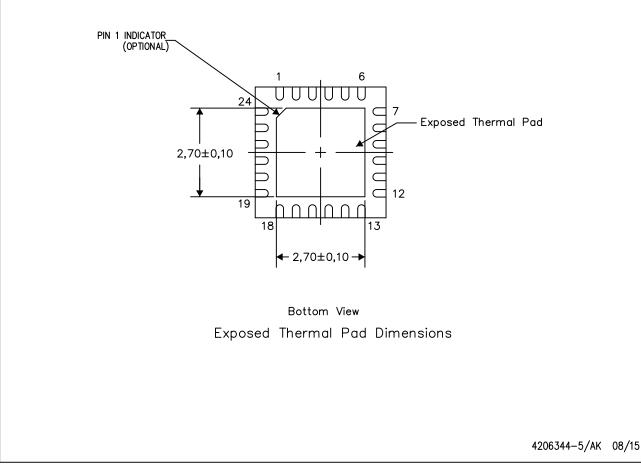

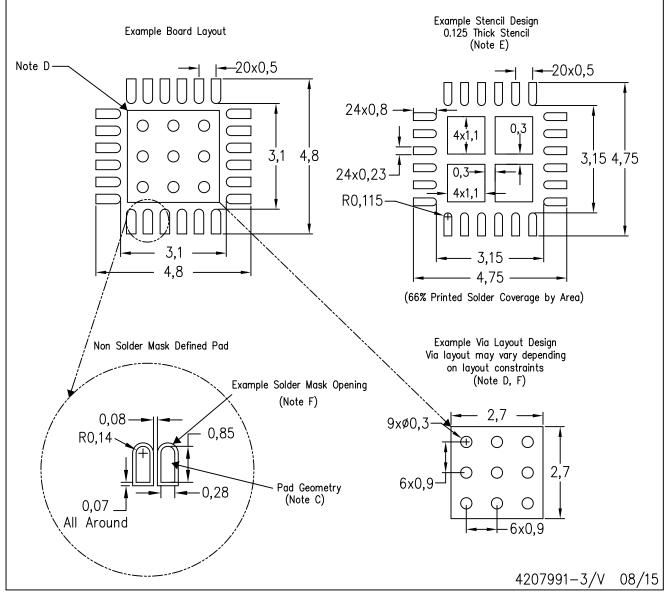

| Thermal pa | ad       | Supply         | Exposed thermal pad; connecting this pin to GND is recommended                                                                                                                                                              |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                         | MIN  | MAX        | UNIT |

|---------------------------------------------------------|------|------------|------|

| AVDD to GND                                             | -0.3 | 2.1        | V    |

| DVDD to GND                                             | -0.3 | 2.1        | V    |

| REFP to REFM                                            | -0.3 | 5.5        | V    |

| REFM to GND                                             | -0.1 | 0.1        | V    |

| Analog (AINP, AINM) to GND                              | -0.3 | REFP + 0.3 | V    |

| Digital input (RST, CONVST, CS, SCLK, SDI) to GND       | -0.3 | DVDD + 0.3 | V    |

| Digital output (RVS, SDO-0, SDO-1, SDO-2, SDO-3) to GND | -0.3 | DVDD + 0.3 | V    |

| Operating temperature, T <sub>A</sub>                   | -40  | 85         | °C   |

| Storage temperature, T <sub>stg</sub>                   | -65  | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatia disabarga | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|      |                        | MIN NO | M MAX | UNIT |

|------|------------------------|--------|-------|------|

| AVDD | Analog supply voltage  | 1      | .8    | V    |

| DVDD | Digital supply voltage | 1      | .8    | V    |

| REFP | Positive reference     |        | 5     | V    |

## 6.4 Thermal Information

|                       |                                              | ADS9110    |       |

|-----------------------|----------------------------------------------|------------|-------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN) | UNITS |

|                       |                                              | 24 PINS    |       |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 31.9       | °C/W  |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 29.9       | °C/W  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 8.9        | °C/W  |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.3        | °C/W  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 8.9        | °C/W  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.0        | °C/W  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A$  = -40°C to +85°C. All typical values are at  $T_A$  = 25°C.

|                      | PARAMETER                                           | TEST CONDITIONS                                                                             | MIN                          | TYP                  | MAX                          | UNIT               |  |

|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------|----------------------|------------------------------|--------------------|--|

| ANALOG               |                                                     |                                                                                             |                              |                      |                              |                    |  |

| FSR                  | Full-scale input range (AINP – AINM) <sup>(1)</sup> |                                                                                             | –V <sub>REF</sub>            |                      | V <sub>REF</sub>             | V                  |  |

| V <sub>IN</sub>      | Absolute input voltage<br>(AINP and AINM to REFGND) |                                                                                             | -0.1                         |                      | V <sub>REF</sub> + 0.1       | V                  |  |

| V <sub>CM</sub>      | Common-mode voltage range<br>(AINP + AINM) / 2      |                                                                                             | (V <sub>REF</sub> / 2) – 0.1 | V <sub>REF</sub> / 2 | (V <sub>REF</sub> / 2) + 0.1 | V                  |  |

| C                    | Input capacitance                                   | In sample mode                                                                              |                              | 60                   |                              | pF                 |  |

| C <sub>IN</sub>      | input capacitance                                   | In hold mode                                                                                |                              | 4                    |                              | μr                 |  |

| I <sub>IL</sub>      | Input leakage current                               |                                                                                             |                              | ±1                   |                              | μA                 |  |

| VOLTAG               | E REFERENCE INPUT                                   |                                                                                             |                              |                      |                              |                    |  |

| V <sub>REF</sub>     | Reference input voltage range                       |                                                                                             | 2.5                          |                      | 5                            | V                  |  |

| I <sub>REF</sub>     | Reference input current                             | Average current, V <sub>REF</sub> = 5 V,<br>2-kHz, full-scale input,<br>throughput = 2 MSPS |                              | 1.25                 |                              | mA                 |  |

| DC ACCU              | JRACY                                               |                                                                                             |                              |                      |                              |                    |  |

|                      | Resolution                                          |                                                                                             |                              | 18                   |                              | Bits               |  |

| NMC                  | No missing codes                                    |                                                                                             | 18                           |                      |                              | Bits               |  |

| 15.11                | late and the effect of the                          | In LSBs                                                                                     | -1.5                         | ±0.5 <sup>(2)</sup>  | 1.5                          | LSB <sup>(3)</sup> |  |

| INL                  | Integral nonlinearity                               | In ppm                                                                                      | -5.7                         | ±2                   | 5.7                          | ppm                |  |

| DNL                  | Differential nonlinearity                           |                                                                                             | -0.75                        | ±0.4 <sup>(2)</sup>  | 0.75                         | LSB <sup>(3)</sup> |  |

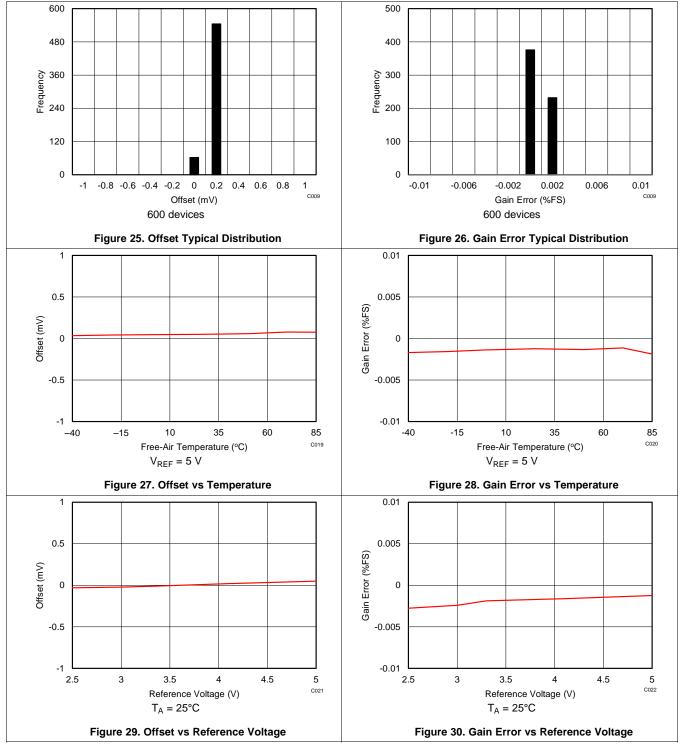

| E <sub>(IO)</sub>    | Input offset error                                  |                                                                                             | -1                           | ±0.05 <sup>(2)</sup> | 1                            | mV                 |  |

| dV <sub>OS</sub> /dT | Input offset thermal drift                          |                                                                                             |                              | 1                    |                              | µV/°C              |  |

| G <sub>E</sub>       | Gain error                                          |                                                                                             | -0.01                        | $\pm 0.005^{(2)}$    | 0.01                         | %FS                |  |

| G <sub>E</sub> /dT   | Gain error thermal drift                            |                                                                                             |                              | 0.25                 |                              | ppm/°C             |  |

|                      | Transition noise                                    |                                                                                             |                              | 0.9                  |                              | LSB <sup>(3)</sup> |  |

| CMRR                 | Common-mode rejection ratio                         | At dc to 20 kHz                                                                             |                              | 80                   |                              | dB                 |  |

| AC ACCI              | JRACY <sup>(4)</sup>                                |                                                                                             | i.                           |                      |                              |                    |  |

|                      |                                                     | f <sub>IN</sub> = 2 kHz                                                                     | 98                           | 99.9                 |                              |                    |  |

| SINAD                | Signal-to-noise + distortion                        | f <sub>IN</sub> = 100 kHz                                                                   |                              | 95.4                 |                              | dB                 |  |

|                      |                                                     | f <sub>IN</sub> = 500 kHz                                                                   |                              | 89                   |                              |                    |  |

|                      |                                                     | f <sub>IN</sub> = 2 kHz                                                                     | 98.1                         | 100                  |                              |                    |  |

| SNR                  | Signal-to-noise ratio                               | f <sub>IN</sub> = 100 kHz                                                                   |                              | 95.5                 |                              | dB                 |  |

|                      |                                                     | f <sub>IN</sub> = 500 kHz                                                                   |                              | 89.3                 |                              |                    |  |

|                      |                                                     | f <sub>IN</sub> = 2 kHz                                                                     |                              | -118                 |                              |                    |  |

| THD                  | Total harmonic distortion <sup>(5)</sup>            | f <sub>IN</sub> = 100 kHz                                                                   |                              | -111                 |                              | dB                 |  |

|                      |                                                     | f <sub>IN</sub> = 500 kHz                                                                   |                              | -101                 |                              |                    |  |

|                      |                                                     | f <sub>IN</sub> = 2 kHz                                                                     |                              | 123                  |                              |                    |  |

| SFDR                 | Spurious-free dynamic range                         | f <sub>IN</sub> = 100 kHz                                                                   |                              | 116                  |                              | dB                 |  |

|                      |                                                     | f <sub>IN</sub> = 500 kHz                                                                   |                              | 106                  |                              |                    |  |

(1) Ideal input span, does not include gain or offset errors.

(2) See Figure 9, Figure 10, Figure 25, and Figure 26 for statistical distribution data for INL, DNL, offset, and gain error parameters.

(3) LSB = least-significant bit. 1 LSB at 18 bits is approximately 3.8 ppm.

(4) All specifications expressed in decibels (dB) refer to the full-scale input (FSR) and are tested with an input signal 0.1 dB below full-scale, unless otherwise specified.

(5) Calculated on the first nine harmonics of the input frequency.

ZHCSE95A-OCTOBER 2015-REVISED OCTOBER 2015

www.ti.com.cn

## **Electrical Characteristics (continued)**

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A = -40^{\circ}$ C to +85°C. All typical values are at  $T_A = 25^{\circ}$ C.

|                 | PARAMETER                             | TEST CONDITIONS               | MIN         | TYP | MAX        | UNIT |  |

|-----------------|---------------------------------------|-------------------------------|-------------|-----|------------|------|--|

| DIGITAL         | L INPUTS <sup>(6)</sup>               |                               | ·           |     |            |      |  |

| V <sub>IH</sub> | High-level input voltage              |                               | 0.65 DVDD   |     | DVDD + 0.3 | V    |  |

| V <sub>IL</sub> | Low-level input voltage               |                               | -0.3        |     | 0.35 DVDD  | V    |  |

| DIGITAL         | L OUTPUTS <sup>(6)</sup>              |                               |             |     |            |      |  |

| V <sub>OH</sub> | High-level output voltage             | I <sub>OH</sub> = 2-mA source | DVDD - 0.45 |     |            | V    |  |

| V <sub>OL</sub> | Low-level output voltage              | I <sub>OH</sub> = 2-mA sink   |             |     | 0.45       | V    |  |

| POWER SUPPLY    |                                       |                               |             |     |            |      |  |

| AVDD            | Analog supply voltage                 |                               | 1.65        | 1.8 | 1.95       | V    |  |

| DVDD            | Digital supply voltage                |                               | 1.65        | 1.8 | 1.95       | V    |  |

|                 | AVDD supply current<br>(AVDD = 1.8 V) | Active, fastest throughput    |             | 5   | 6.25       | A    |  |

| IDD             |                                       | Static, ACQ state             |             | 3.7 |            | mA   |  |

| טטו             |                                       | Low-power, NAP mode           |             | 500 |            |      |  |

|                 |                                       | Power-down, PD state          |             | 1   |            | μA   |  |

|                 |                                       | Active, fastest throughput    |             | 9   | 11.25      | m)// |  |

| P               | AVDD power dissipation                | Static, ACQ state             |             | 6.6 |            | mW   |  |

| PD              | (AVDD = 1.8 V)                        | Low-power, NAP mode           |             | 900 |            |      |  |

|                 |                                       | Power-down, PD state          |             | 1.8 |            | μW   |  |

| TEMPE           | RATURE RANGE                          |                               | ·           |     |            |      |  |

| T <sub>A</sub>  | Operating free-air temperature        |                               | -40         |     | 85         | °C   |  |

(6) As per the JESD8-7A standard. Specified by design; not production tested.

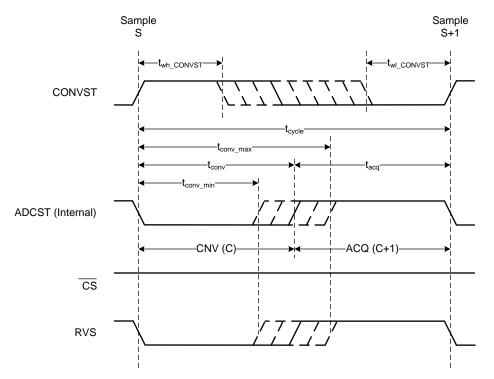

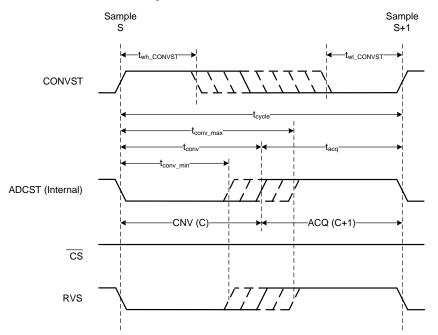

## 6.6 Timing Requirements: Conversion Cycle

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A$  = -40°C to +85°C. All typical values are at  $T_A$  = 25°C. See Figure 1.

|                        |                                       |     | A   |     | 0    |  |

|------------------------|---------------------------------------|-----|-----|-----|------|--|

|                        |                                       | MIN | TYP | MAX | UNIT |  |

| TIMING REQU            | IMING REQUIREMENTS                    |     |     |     |      |  |

| f <sub>cycle</sub>     | Sampling frequency                    |     |     | 2   | MHz  |  |

| t <sub>cycle</sub>     | ADC cycle time period                 | 500 |     |     | ns   |  |

| t <sub>wh_CONVST</sub> | Pulse duration: CONVST high           | 30  |     |     | ns   |  |

| t <sub>wl_CONVST</sub> | Pulse duration: CONVST low            | 30  |     |     | ns   |  |

| t <sub>acq</sub>       | Acquisition time                      | 150 |     |     | ns   |  |

| t <sub>qt_acq</sub>    | Quiet acquisition time <sup>(1)</sup> | 25  |     |     | ns   |  |

| t <sub>d_cnvcap</sub>  | Quiet aperture time <sup>(1)</sup>    | 10  |     |     | ns   |  |

|                        | MING SPECIFICATIONS                   |     |     |     |      |  |

| t <sub>conv</sub>      | Conversion time                       | 300 |     | 340 | ns   |  |

|                        |                                       |     |     |     |      |  |

(1) See Figure 48.

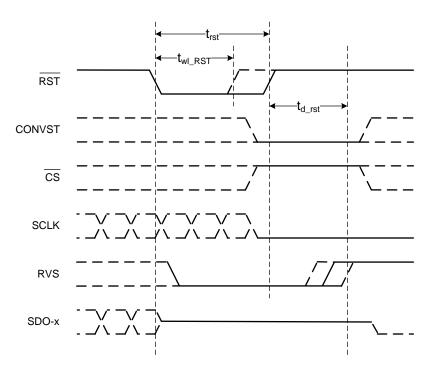

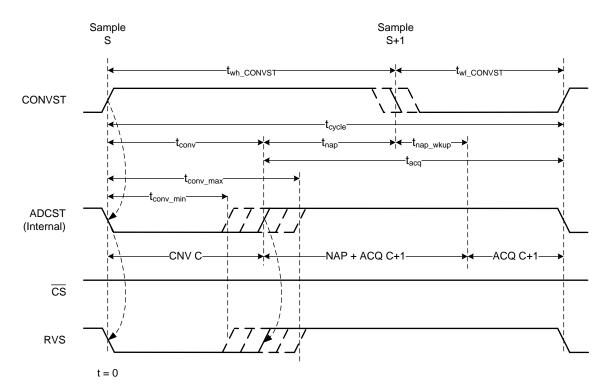

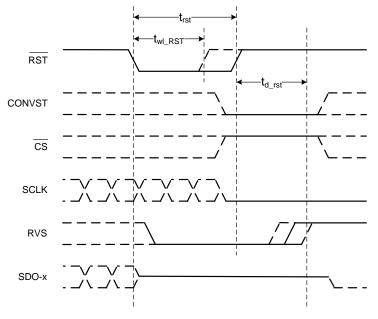

## 6.7 Timing Requirements: Asynchronous Reset, NAP, and PD

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF} = 5$  V, and  $f_{DATA} = 2$  MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A = -40^{\circ}$ C to +85°C. All typical values are at  $T_A = 25^{\circ}$ C. See Figure 2 and Figure 3.

|                       |                                      | MIN | TYP | MAX  | UNIT |  |

|-----------------------|--------------------------------------|-----|-----|------|------|--|

| TIMING REC            | QUIREMENTS                           |     |     |      |      |  |

| t <sub>wl_RST</sub>   | Pulse duration: RST low              | 100 |     |      | ns   |  |

| TIMING SPE            | TIMING SPECIFICATIONS                |     |     |      |      |  |

| t <sub>d_rst</sub>    | Delay time: RST rising to RVS rising |     |     | 1250 | μs   |  |

| t <sub>nap_wkup</sub> | Wake-up time: NAP mode               |     |     | 300  | ns   |  |

| t <sub>PWRUP</sub>    | Power-up time: PD mode               |     |     | 250  | μs   |  |

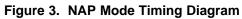

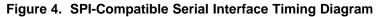

## 6.8 Timing Requirements: SPI-Compatible Serial Interface

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A$  = -40°C to +85°C. All typical values are at  $T_A$  = 25°C. See Figure 4.

|                        |                                                              |                     | MIN   | TYP MAX | UNIT             |

|------------------------|--------------------------------------------------------------|---------------------|-------|---------|------------------|

| TIMING REG             | QUIREMENTS                                                   |                     |       |         |                  |

| f <sub>CLK</sub>       | Serial clock frequency                                       |                     |       | 75      | MHz              |

| t <sub>CLK</sub>       | Serial clock time period                                     |                     | 13.33 |         | ns               |

| t <sub>ph_CK</sub>     | SCLK high time                                               |                     | 0.45  | 0.55    | t <sub>CLK</sub> |

| t <sub>pl_CK</sub>     | SCLK low time                                                |                     | 0.45  | 0.55    | t <sub>CLK</sub> |

| t <sub>su_CSCK</sub>   | Setup time: CS falling to the firs                           | t SCLK capture edge | 5     |         | ns               |

| t <sub>su_CKDI</sub>   | Setup time: SDI data valid to the SCLK capture edge          |                     | 1.2   |         | ns               |

| t <sub>ht_CKDI</sub>   | Hold time: SCLK capture edge to (previous) data valid on SDI |                     | 0.65  |         | ns               |

| t <sub>ht_CKCS</sub>   | Delay time: last SCLK falling to $\overline{CS}$ rising      |                     | 5     |         | ns               |

| TIMING SPE             | ECIFICATIONS                                                 |                     |       |         |                  |

| t <sub>den_CSDO</sub>  | Delay time: CS falling to data er                            | nable               |       | 4.5     | ns               |

| t <sub>dz_CSDO</sub>   | Delay time: CS rising to SDO go                              | bing to 3-state     |       | 10      | ns               |

| t <sub>d_CKDO</sub>    | Delay time: SCLK launch edge to (next) data valid on SDO     |                     |       | 6.5     | ns               |

| t <sub>d_CSRDY_f</sub> | Delay time: CS falling to RVS falling                        |                     |       | 5       | ns               |

|                        | Delay time:                                                  | After NOP operation |       | 10      | ~~~              |

| t <sub>d_CSRDY_r</sub> | CS rising to RVS rising After WR or RD operation             |                     |       | 70      | ns               |

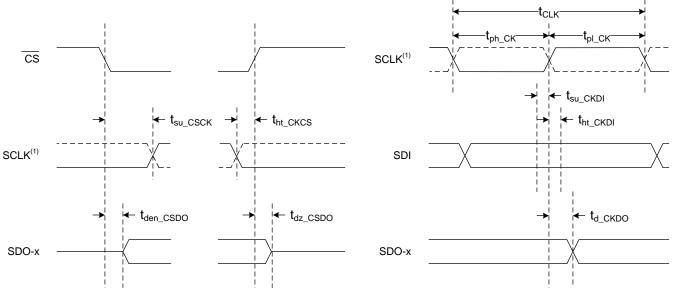

## 6.9 Timing Requirements: Source-Synchronous Serial Interface (External Clock)

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF}$  = 5 V, and  $f_{DATA}$  = 2 MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A$  = -40°C to +85°C. All typical values are at  $T_A$  = 25°C. See Figure 5.

|                          |                                                      |      | A   |     | 0.000 |

|--------------------------|------------------------------------------------------|------|-----|-----|-------|

|                          |                                                      | MIN  | TYP | MAX | UNIT  |

| TIMING REQ               | UIREMENTS                                            |      |     |     |       |

| f <sub>CLK</sub>         | Serial clock frequency                               |      |     | 100 | MHz   |

| t <sub>CLK</sub>         | Serial clock time period                             | 10   |     |     | ns    |

| TIMING SPE               | CIFICATIONS <sup>(1)</sup>                           |      |     |     |       |

| t <sub>d_CKSTR_r</sub>   | Delay time: SCLK launch edge to RVS rising           |      |     | 8.5 | ns    |

| t <sub>d_CKSTR_f</sub>   | Delay time: SCLK launch edge to RVS falling          |      |     | 8.5 | ns    |

| t <sub>off_STRDO_f</sub> | Time offset: RVS rising to (next) data valid on SDO  | -0.5 |     | 0.5 | ns    |

| t <sub>off STRDO r</sub> | Time offset: RVS falling to (next) data valid on SDO | -0.5 |     | 0.5 | ns    |

(1) Other parameters are the same as the *Timing Requirements: SPI-Compatible Serial Interface* table.

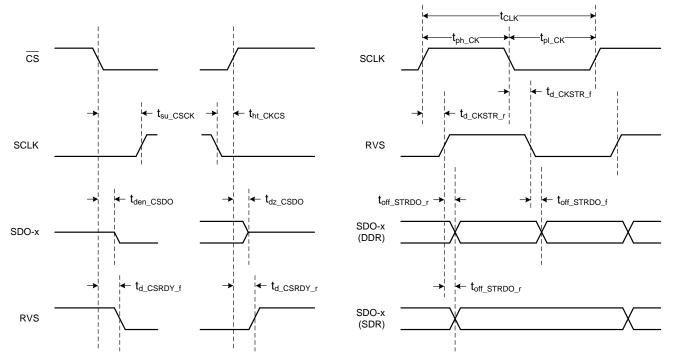

## 6.10 Timing Requirements: Source-Synchronous Serial Interface (Internal Clock)

All specifications are for AVDD = 1.8 V, DVDD = 1.8 V,  $V_{REF} = 5$  V, and  $f_{DATA} = 2$  MSPS, unless otherwise noted. All minimum and maximum specifications are for  $T_A = -40^{\circ}$ C to +85°C. All typical values are at  $T_A = 25^{\circ}$ C. See Figure 6.

|                          |                                 |                        | MIN  | TYP | MAX  | UNIT             |

|--------------------------|---------------------------------|------------------------|------|-----|------|------------------|

| TIMING SPEC              | CIFICATIONS <sup>(1)</sup>      |                        |      |     |      |                  |

| t <sub>d_CSSTR</sub>     | Delay time: CS falling to RVS   | rising                 | 12   |     | 40   | ns               |

| t <sub>off_STRDO_f</sub> | Time offset: RVS rising to (ne  | xt) data valid on SDO  | -0.5 |     | 0.5  | ns               |

| t <sub>off_STRDO_r</sub> | Time offset: RVS falling to (ne | ext) data valid on SDO | -0.5 |     | 0.5  | ns               |

|                          |                                 | INTCLK option          | 9.9  |     | 11.1 |                  |

| t <sub>STR</sub>         | Strobe output time period       | INTCLK / 2 option      | 19.8 |     | 22.2 | ns               |

|                          |                                 | INTCLK / 4 option      | 39.6 |     | 44.4 |                  |

| t <sub>ph_STR</sub>      | Strobe output high time         |                        | 0.45 |     | 0.55 | t <sub>STR</sub> |

| t <sub>pl_STR</sub>      | Strobe output low time          |                        | 0.45 |     | 0.55 | t <sub>STR</sub> |

(1) Other parameters are the same as the Timing Requirements: SPI-Compatible Serial Interface table.

Figure 2. Asynchronous Reset Timing Diagram

(1) The SCLK polarity, launch edge, and capture edge depend on the SPI protocol selected.

ADS9110 ZHCSE95A – OCTOBER 2015 – REVISED OCTOBER 2015

Figure 5. Source-Synchronous Serial Interface Timing Diagram (External Clock)

Figure 6. Source-Synchronous Serial Interface Timing Diagram (Internal Clock)

ADS9110

ZHCSE95A-OCTOBER 2015-REVISED OCTOBER 2015

TEXAS INSTRUMENTS

www.ti.com.cn

## 6.11 Typical Characteristics

## **Typical Characteristics (continued)**

ADS9110 ZHCSE95A – OCTOBER 2015 – REVISED OCTOBER 2015

www.ti.com.cn

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

ADS9110

ZHCSE95A-OCTOBER 2015-REVISED OCTOBER 2015

TEXAS INSTRUMENTS

www.ti.com.cn

## **Typical Characteristics (continued)**

## 7 Detailed Description

## 7.1 Overview

The ADS9110 is a high-speed, successive approximation register (SAR), analog-to-digital converter (ADC) based on the charge redistribution architecture. This compact device features high performance at a high throughput rate and at low power consumption.

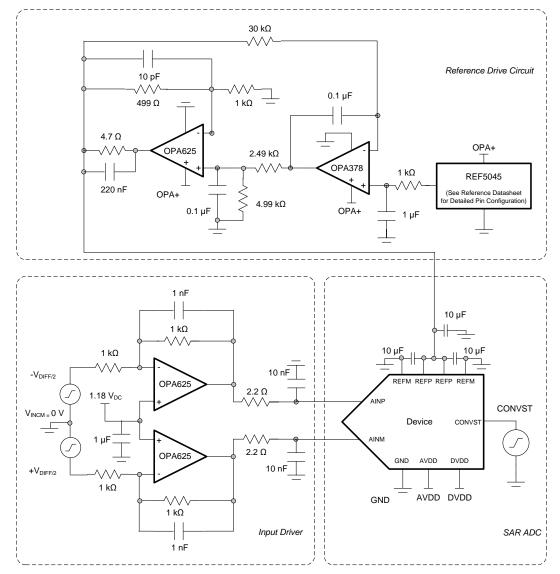

The ADS9110 supports unipolar, fully-differential analog input signals and operates with a 2.5-V to 5-V external reference, offering a wide selection of input ranges without additional input scaling.

When a conversion is initiated, the differential input between the AINP and AINM pins is sampled on the internal capacitor array. The ADS9110 uses an internal clock to perform conversions. During the conversion process, both analog inputs are disconnected from the internal circuit. At the end of conversion process, the device reconnects the sampling capacitors to the AINP and AINM pins and enters acquisition phase.

The device consumes only 15 mW of power when operating at the full 2-MSPS throughput. Power consumption at lower throughputs can be reduced by using the flexible low-power modes (NAP and PD).

The new multiSPI interface simplifies board layout, timing, and firmware, and achieves high throughput at lower clock speeds, thus allowing easy interface to a variety of microprocessors, digital signal processors (DSPs), and field-programmable gate arrays (FPGAs).

## 7.2 Functional Block Diagram

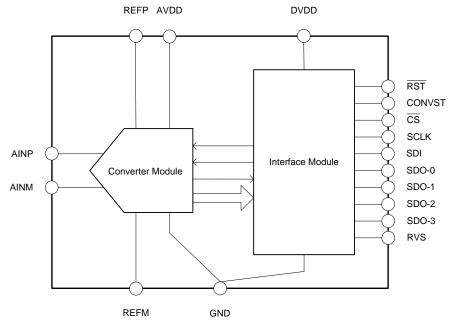

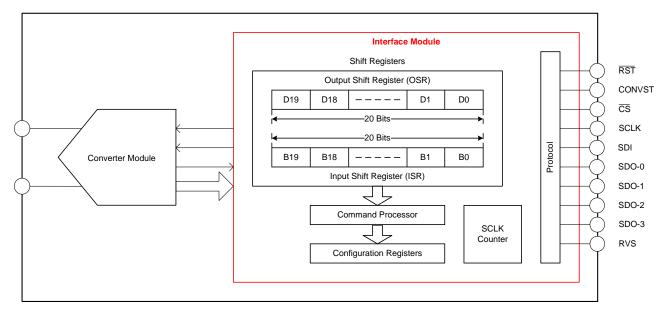

From a functional perspective, the device comprises of two modules: the converter module and the interface module, as shown in Figure 36.

The converter module samples and converts the analog input into an equivalent digital output code whereas the interface module facilitates communication and data transfer with the host controller.

Figure 36. Functional Block Diagram

ADS9110 ZHCSE95A – OCTOBER 2015 – REVISED OCTOBER 2015 TEXAS INSTRUMENTS

## 7.3 Feature Description

### 7.3.1 Converter Module

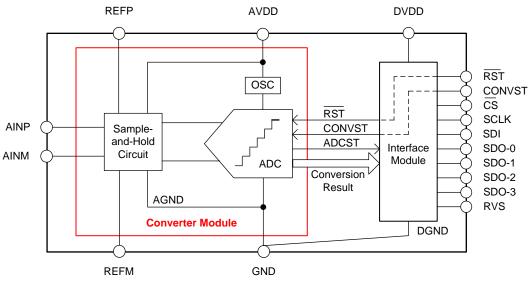

As shown in Figure 37, the converter module samples the analog input signal (provided between the AINP and AINM pins), compares this signal with the reference voltage (provided between the pair of REFP and REFM pins), and generates an equivalent digital output code.

The converter module receives  $\overline{RST}$  and CONVST inputs from the interface module and outputs the ADCST signal and the conversion result back to the interface module.

Figure 37. Converter Module

## 7.3.1.1 Sample-and-Hold Circuit

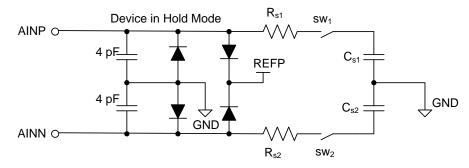

The device supports unipolar, fully-differential analog input signals. Figure 38 shows a small-signal equivalent circuit of the sample-and-hold circuit. Each sampling switch is represented by a resistance ( $R_{s1}$  and  $R_{s2}$ , typically 30  $\Omega$ ) in series with an ideal switch (sw<sub>1</sub> and sw<sub>2</sub>). The sampling capacitors,  $C_{s1}$  and  $C_{s2}$ , are typically 60 pF.

Figure 38. Input Sampling Stage Equivalent Circuit

During the acquisition process (in ACQ state), both positive and negative inputs are individually sampled on  $C_{s1}$  and  $C_{s2}$ , respectively. During the conversion process (in CNV state), the device converts for the voltage difference between the two sampled values:  $V_{AINP} - V_{AINM}$ .

Each analog input pin has electrostatic discharge (ESD) protection diodes to REFP and GND. Keep the analog inputs within the specified range to avoid turning the diodes on.

#### Feature Description (continued)

Equation 1 and Equation 2 show the full-scale voltage range (FSR) and common-mode voltage range ( $V_{CM}$ ) supported at the analog inputs for any external reference voltage ( $V_{REF}$ ).

$$FSR = \pm V_{REF}$$

(1)

$$V_{CM} = \left(\frac{V_{REF}}{2}\right) \pm 0.1 \text{ V}$$

(2)

#### 7.3.1.2 External Reference Source

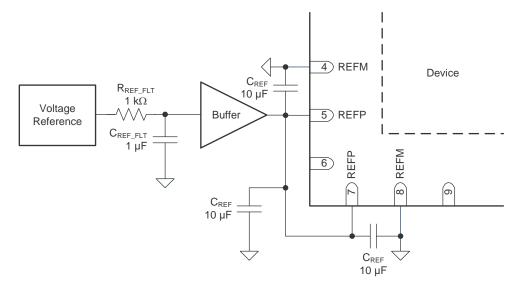

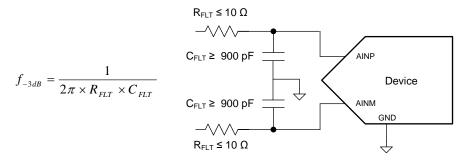

The input range for the device is set by the external voltage applied at the two REFP pins. The REFM pins function as the reference ground and must be connected to each reference capacitor.

The device takes very little static current from the reference pins in the RST and ACQ states. During the conversion process (in CNV state), binary-weighted capacitors are switched onto the reference pins. The switching frequency is proportional to the conversion clock frequency, but the dynamic charge requirements are a function of the absolute values of the input voltage and the reference voltage. Reference capacitors decouple the dynamic reference loads and a low-impedance reference driver is required to keep the voltage regulated to within 1 LSB.

Most reference sources have very high broadband noise. TI recommends filtering the voltage reference source with a 160-Hz filter before being connected to the reference driver, as shown in Figure 39. See the *ADC Reference Driver* section for reference capacitor and driver selection. Also, the reference inputs are sensitive to board layout; thus, the layout guidelines described in the *Layout* section must be followed.

Figure 39. Reference Driver Schematic

#### 7.3.1.3 Internal Oscillator

The device features an internal oscillator (OSC) that provides the conversion clock; see Figure 37. Conversion duration can vary but is bounded by the minimum and maximum value of  $t_{conv}$ , as specified in the *Timing Requirements: Conversion Cycle* table.

The interface module can use this internal clock (OSC) or an external clock (provided by the host controller on the SCLK pin) or a combination of the internal and external clocks for executing the data transfer operations between the device and host controller; see the *Interface Module* section for more details.

## Feature Description (continued)

## 7.3.1.4 ADC Transfer Function

The ADS9110 supports unipolar, fully-differential analog inputs. The device output is in twos compliment format. Figure 40 and Table 1 show the ideal transfer characteristics for the device.

The LSB for the ADC is given by Equation 3:

$$1 \text{ LSB} = \frac{\text{FSR}}{2^{18}} = 2 \times \frac{V_{\text{REF}}}{2^{18}}$$

(3)

$$\int_{Q}^{50} 00000 \\ Q_{\text{ref}}^{50} 0$$

## Figure 40. Differential Transfer Characteristics

| Table 1. Tra | nsfer Characteristics |

|--------------|-----------------------|

|--------------|-----------------------|

| DIFFERENTIAL ANALOG INPUT VOLTAGE<br>(AINP – AINM) | OUTPUT CODE<br>(Hex) |

|----------------------------------------------------|----------------------|

| < -V <sub>REF</sub>                                | 20000                |

| –V <sub>REF</sub> + 1 LSB                          | 20001                |

| –1 LSB                                             | 3FFFF                |

| 0                                                  | 00000                |

| 1 LSB                                              | 00001                |

| > V <sub>REF</sub> – 1 LSB                         | 1FFFF                |

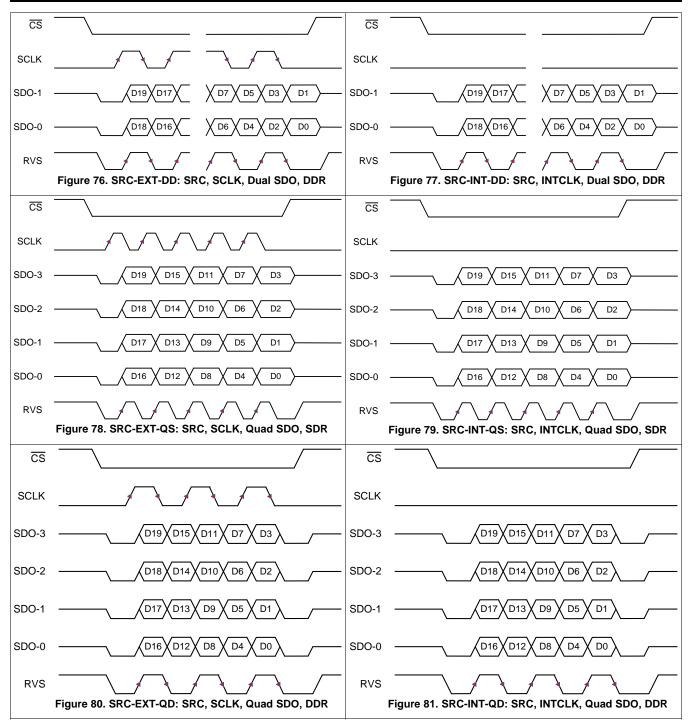

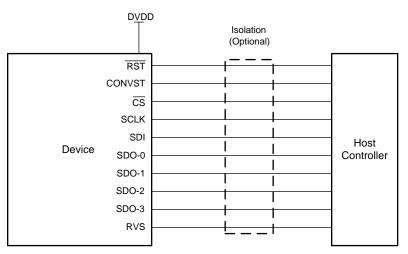

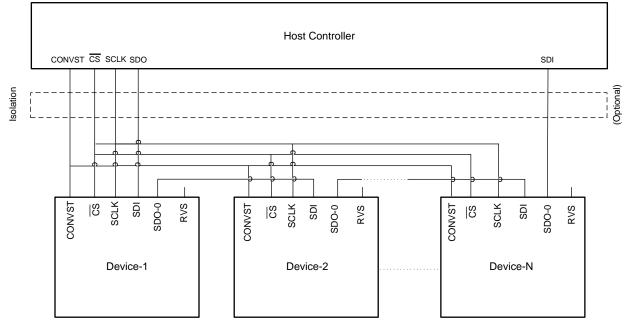

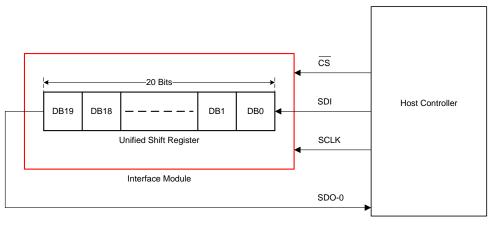

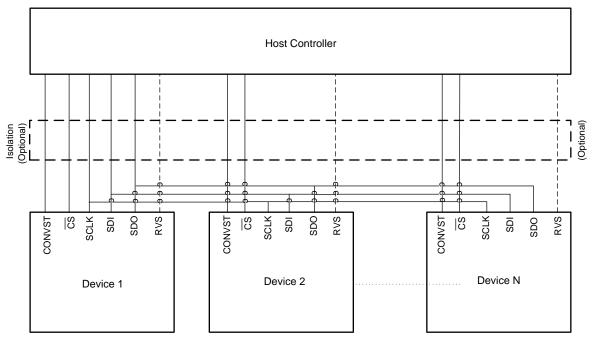

### 7.3.2 Interface Module

The interface module facilitates the communication and data transfer between the device and the host controller. As shown in Figure 41, the module comprises of shift registers (both input and output), configuration registers, and a protocol unit.

## Figure 41. Interface Module

The *Pin Configuration and Functions* section provides descriptions of the interface pins; the *Data Transfer Frame* section details the functions of shift registers, the SCLK counter, and the command processor; the *Data Transfer Protocols* section details supported protocols; and the *Register Maps* section explains the configuration registers and bit settings.

ZHCSE95A-OCTOBER 2015-REVISED OCTOBER 2015

## 7.4 Device Functional Modes

ADS9110

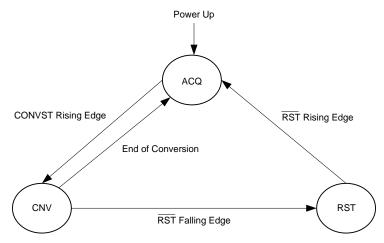

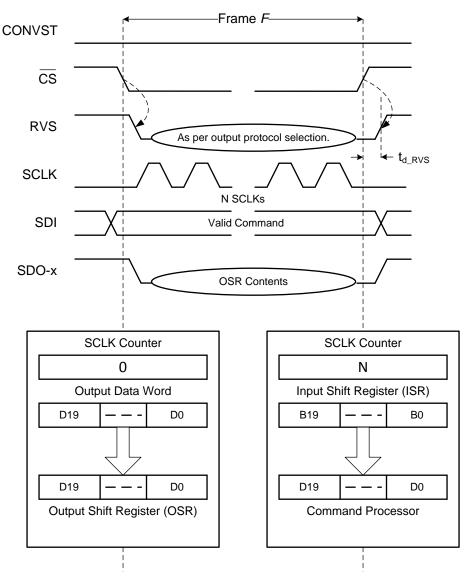

As shown in Figure 42, the device supports three functional states: RST, ACQ, and CNV. The device state is determined by the status of the CONVST and RST control signals provided by the host controller.

Figure 42. Device Functional States

## 7.4.1 RST State

In the ADS9110, the  $\overline{RST}$  pin is an asynchronous digital input. To enter RST state, the host controller must pull the  $\overline{RST}$  pin low and keep it low for the t<sub>wl\_RST</sub> duration (as specified in the *Timing Requirements: Asynchronous Reset, NAP, and PD* table).

In RST state, all configuration registers (see the *Register Maps* section) are reset to their default values, the RVS pins remain low, and the SDO-x pins are tri-stated.

To exit RST state, the host controller must pull the  $\overline{RST}$  pin high with CONVST and SCLK held low and  $\overline{CS}$  held high, as shown in Figure 43. After a delay of t<sub>d rst</sub>, the device enters ACQ state and the RVS pin goes high.

Figure 43. Asynchronous Reset

To operate the device in any of the other two states (ACQ or CNV), RST must be held high. With RST held high, transitions on the CONVST pin determine the functional state of the device.

## **Device Functional Modes (continued)**

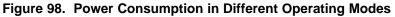

Figure 44 shows a typical conversion process. An internal signal, ADCST, goes low during conversion and goes high at the end of conversion. With CS held high, RVS reflects the status of ADCST.

Figure 44. Typical Conversion Process

## 7.4.2 ACQ State

In ACQ state, the device acquires the analog input signal. The device enters ACQ state on power-up, after any asynchronous reset, or after end of every conversion.

An RST falling edge takes the device from an ACQ state to a RST state. A CONVST rising edge takes the device from an ACQ state to a CNV state.

The device offers a low-power NAP mode to reduce power consumption in the ACQ state; see the *NAP Mode* section for more details on NAP mode.

### 7.4.3 CNV State

The device moves from ACQ state to CNV state on a rising edge of the CONVST pin. The conversion process uses an internal clock and the device ignores any further transitions on the CONVST signal until the ongoing conversion is complete (that is, during the time interval of  $t_{conv}$ ).

At the end of conversion, the device enters ACQ state. The cycle time for the device is given by Equation 4:

$t_{cycle-min} = t_{conv} + t_{acq-min}$

(4)

## NOTE

The conversion time,  $t_{conv}$ , can vary within the specified limits of  $t_{conv\_min}$  and  $t_{conv\_max}$  (as specified in the *Timing Requirements: Conversion Cycle* table). After initiating a conversion, the host controller must monitor for a low-to-high transition on the RVS pin or wait for the  $t_{conv\_max}$  duration to elapse before initiating a new operation (data transfer or conversion). If RVS is not monitored, substitute  $t_{conv}$  in Equation 4 with  $t_{conv\_max}$ .

## 7.5 Programming

The device features four configuration registers (as described in the *Register Maps* section) and supports two types of data transfer operations: *data write* (the host configures the device), and *data read* (the host reads data from the device).

To access the internal configuration registers, the device supports the commands listed in Table 2.

| OPCODE B[19:0]                    | COMMAND ACRONYM | COMMAND DESCRIPTION                                                   |

|-----------------------------------|-----------------|-----------------------------------------------------------------------|

| 0000_0000_0000_0000               | NOP             | No operation                                                          |

| 1001_<8-bit address>_0000_0000    | RD_REG          | Read contents from the <8-bit address>                                |

| 1010_<8-bit address>_<8-bit data> | WR_REG          | Write <8-bit data> to the <8-bit address>                             |

| 1111_1111_1111_1111_1111          | NOP             | No operation                                                          |

| Remaining combinations            | Reserved        | These commands are reserved and treated by the device as no operation |

### **Table 2. Supported Commands**

In the ADS9110, any data write to the device is always synchronous to the external clock provided on the SCLK pin. The data read from the device can be synchronized to the same external clock or to an internal clock of the device by programming the configuration registers (see the *Data Transfer Protocols* section for details).

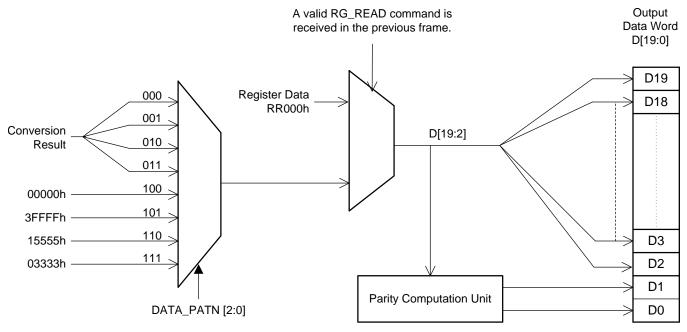

In any data transfer frame, the contents of an internal, 20-bit, output data word are shifted out on the SDO pins. The D[19:2] bits of the 20-bit output data word for any frame (F+1), are determined by the:

- Settings of the DATA\_PATN[2:0] bits applicable to frame F+1 (see the DATA\_CNTL register) and

- Command issued in frame F

If a valid RD\_REG command is executed in frame F, then the D[19:12] bits in frame F+1 reflect the contents of the selected register and the D[11:0] bits are 0s.

If the DATA\_PATN[2:0] bits for frame F+1 are set to 1xxb, then the D[19:2] bits in frame F+1 are the fixed data pattern shown in Figure 45.

For all other combinations, the D[19:2] bits for frame F+1 are the latest conversion result.

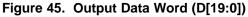

Figure 46 shows further details of the parity computation unit illustrated in Figure 45.

Figure 46. Parity Bits Computation

With the PAR\_EN bit set to 0, the D[1] and D[0] bits of the output data word are set to 0 (default configuration).

When the PAR\_EN bit is set to 1, the device calculates the parity bits (FLPAR and FTPAR) and appends them as bits D[1] and D[0].

- FLPAR is the even parity calculated on bits D[19:2].

- FTPAR is the even parity calculated on the bits defined by FPAR\_LOC[1:0].

See the DATA\_CNTL register for more details on the FPAR\_LOC[1:0] bit settings.

ADS9110 ZHCSE95A – OCTOBER 2015 – REVISED OCTOBER 2015

www.ti.com.cn

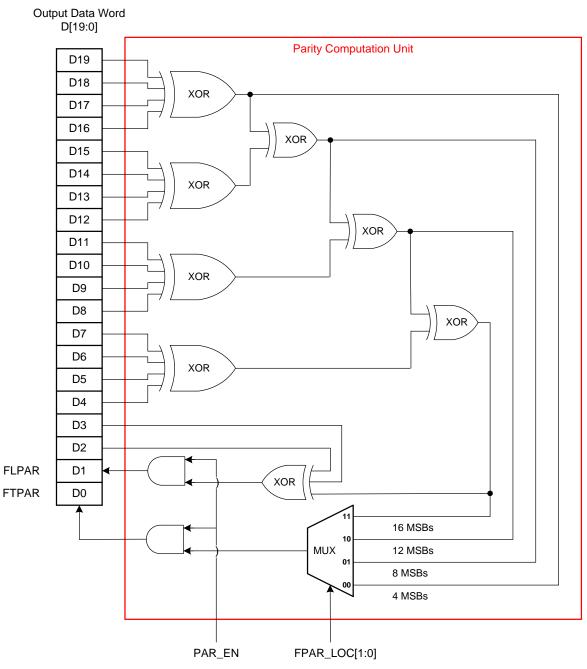

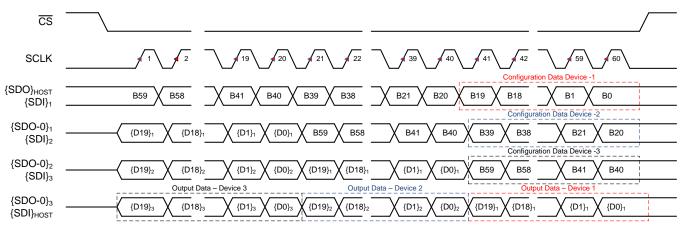

## 7.5.1 Data Transfer Frame

A data transfer frame between the device and the host controller is bounded between a  $\overline{CS}$  falling edge and the subsequent  $\overline{CS}$  rising edge. The host controller can initiate a data transfer frame (as shown in Figure 47) at any time irrespective of the status of the CONVST signal; however, the data read during such a data transfer frame is a function of relative timing between the CONVST and  $\overline{CS}$  signals.

Figure 47. Data Transfer Frame

For this discussion, assume that the CONVST signal remains low.

For a typical data transfer frame F:

- 1. The host controller pulls  $\overline{CS}$  low to initiate a data transfer frame. On the  $\overline{CS}$  falling edge:

- RVS goes low, indicating the beginning of the data transfer frame.

- The SCLK counter is reset to 0.

- The device takes control of the data bus. As shown in Figure 47, the 20-bit contents of the output data word (see Figure 45) are loaded in to the 20-bit OSR (see Figure 41).

- The 20-bit ISR (see Figure 41) is reset to 00000h, corresponding to a NOP command.

- 2. During the frame, the host controller provides clocks on the SCLK pin:

- On each SCLK capture edge, the SCLK counter is incremented and the data bit received on the SDI pin is shifted in to the ISR.

- On each launch edge of the output clock (SCLK in this case), OSR data are shifted out on the selected SDO-x pins.

- The status of the RVS pin depends on the output protocol selection (see the *Protocols for Reading From the Device* section).

- 3. The host controller pulls  $\overline{CS}$  high to end the data transfer frame. On the  $\overline{CS}$  rising edge:

- The SDO-x pins go to tri-state.

- RVS goes high (after a delay of  $t_{d_RVS}$ ).

- As illustrated in Figure 47, the 20-bit contents of the ISR are transferred to the command processor (see Figure 41) for decoding and further action.

After pulling  $\overline{CS}$  high, the host controller must monitor for a low-to-high transition on the RVS pin or wait for the  $t_{d_{RVS}}$  time (see the *Timing Requirements: SPI-Compatible Serial Interface* table) to elapse before initiating a new operation (data transfer or conversion). The delay,  $t_{d_{RVS}}$ , for any data transfer frame F varies based on the data transfer operation executed in the frame F.

At the end of the data transfer frame F:

- If the SCLK counter is < 20, then the device treats the frame F as a *short* data transfer frame. The output

data bits transferred during such a short data transfer frame are still valid data; however, the device ignores

the data received over the SDI pin (similar to a no operation command). The host controller can use these

short data transfer frames to read only the required number of MSB bits from the 20-bit output data word.

- If the SCLK counter = 20, then the device treats the frame F as a *optimal* data transfer frame. At the end of an optimal data transfer frame, the command processor treats the 20-bit contents of the ISR as a valid command word.

- If the SCLK counter > 20, then the device treats the frame F as a *long* data transfer frame. At the end of a long data transfer frame, the command processor treats the 20-bit contents of the ISR as a valid command word. There is no restriction on the maximum number of clocks that can be provided within any data transfer frame F. However, when the host controller provides a long data transfer frame, the last 20 bits shifted into the device prior to the CS rising edge must constitute the desired command.

## NOTE

This example shows a data transfer synchronous to the external clock provided on the SCLK pin. The device also supports data transfer operations that are synchronous to the internal clock; see the *Protocols for Reading From the Device* section for more details.

## 7.5.2 Interleaving Conversion Cycles and Data Transfer Frames

The host controller can operate the ADS9110 at the desired throughput by interleaving the conversion cycles and the data transfer frames.

The cycle time of the device,  $t_{cycle}$ , is the time difference between two consecutive CONVST rising edges provided by the host controller. The response time of the device,  $t_{resp}$ , is the time difference between the host controller initiating a conversion C and the host controller receiving the complete result for conversion C.

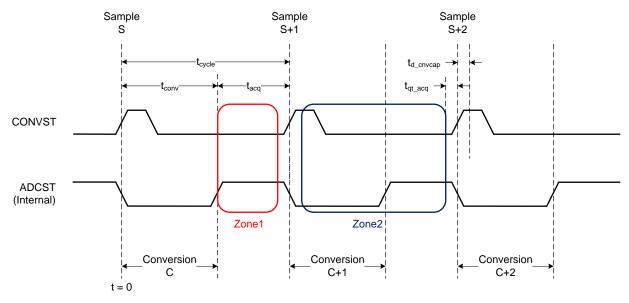

Figure 48 shows three conversion cycles, C, C+1, and C+2. Conversion C is initiated by a CONVST rising edge at the t = 0 time and the conversion result becomes available for data transfer at the  $t_{conv}$  time. However, this result is loaded into the OSR only on the subsequent  $\overline{CS}$  falling edge. This  $\overline{CS}$  falling edge must be provided before the completion of the conversion C+1 (that is, before the  $t_{cvcle} + t_{conv}$  time).

To achieve the rated performance specifications, the host controller must ensure that no digital signals toggle during the quiet acquisition time ( $t_{qt\_acq}$ ) and quiet aperture time ( $t_{d\_cnvcap}$ ). Any noise during  $t_{d\_cnvcap}$  can negatively affect the result of the ongoing conversion whereas any noise during  $t_{qt\_acq}$  can negatively affect the result of the subsequent conversion.

Figure 48. Data Transfer Zones

This architecture allows for two distinct time zones (zone1 and zone2) to transfer data for each conversion. Zone1 and zone2 for conversion C are defined in Table 3.

| Table 3. | Data | Transfer | Zones | Timing |

|----------|------|----------|-------|--------|

|----------|------|----------|-------|--------|

| ZONE                   | STARTING TIME                              | ENDING TIME                           |

|------------------------|--------------------------------------------|---------------------------------------|

| Zone1 for conversion C | t <sub>conv</sub>                          | $t_{cycle} - t_{qt\_acq}$             |

| Zone2 for conversion C | t <sub>cycle</sub> + t <sub>d_cnvcap</sub> | $t_{cycle} + t_{cycle} - t_{qt\_acq}$ |

The response time includes the conversion time and the data transfer time, and is thus a function of the data transfer zone selected.

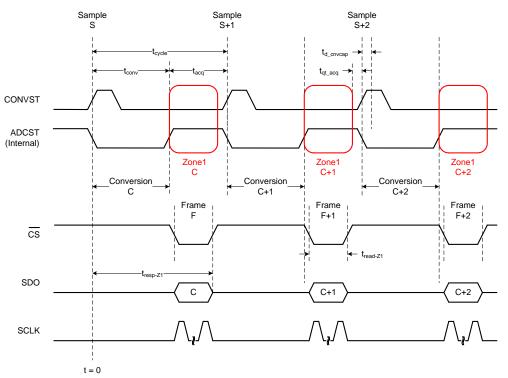

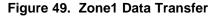

Figure 49 and Figure 50 illustrate interleaving of three conversion cycles (C, C+1, and C+2) with three data transfer frames (F, F+1, and F+2) in zone1 and in zone2, respectively.

To achieve cycle time,  $t_{cycle}$ , the read time in zone1 is given by Equation 5:

$$t_{read-Z1} \le t_{cycle} - t_{conv} - t_{qt\_acq}$$

For an optimal data transfer frame, Equation 5 results in an SCLK frequency given by Equation 6:

$$f_{SCLK} \ge \frac{20}{t_{read-Z1}}$$

(6)

Then, the zone1 data transfer achieves a response time defined by Equation 7:

$$t_{resp-Z1-min} = t_{conv} + t_{read-Z1}$$

As an example, while operating the ADS9110 at its full throughput of 2 MSPS, the host controller can achieve a response time of 1 µs provided that the data transfer in zone1 is completed within 135 ns. However, to achieve this response time, the SCLK frequency must be greater than 148 MHz.

Note that the device does not support such high SCLK speeds. At lower SCLK speeds, t<sub>read-Z1</sub> increases, resulting in slower response times and higher cycle times.

To achieve the same cycle time,  $t_{cycle}$ , the read time in zone2 is given by Equation 8:

$t_{read-Z2} \le t_{cycle} - t_{d\_cnvcap} - t_{qt\_acq}$

For an optimal data transfer frame, Equation 8 results in an SCLK frequency given by Equation 9:

| , 20                  |     |

|-----------------------|-----|

| ISCLK 2               |     |

| t <sub>read_</sub> Z2 | (9) |

Then, the zone2 data transfer achieves a response time defined by Equation 10:

t<sub>resp-Z2-min</sub> = t<sub>cycle</sub> + t<sub>d\_cnvcap</sub> + t<sub>read-Z2</sub>

As an example, the host controller can operate the ADS9110 at its full throughput of 2 MSPS using zone2 data transfer with a 43 MHz SCLK (and a read time of 465 ns). However, zone2 data transfer will result in response time of nearly 2 µs.

Any increase in t<sub>read-Z2</sub> increases response time and can increase cycle time.

For a given cycle time, the zone1 data transfer clearly achieves faster response time but also requires a higher SCLK speed (as evident from Equation 5, Equation 6, and Equation 7), whereas the zone2 data transfer clearly requires a lower SCLK speed but supports slower response time (as evident from Equation 8, Equation 9, and Equation 10).

### NOTE

In zone2, the data transfer is active when the device is converting for the next analog sample. This digital activity can interfere with the ongoing conversion and cause some degradation in SNR performance.

Additionally, a data transfer frame can begin in zone1 and then extend into zone2; however, the host controller must ensure that no digital transitions occur during the  $t_{qt\_acq}$  and  $t_{d\_cnvcap}$  time intervals.

www.ti.com.cn

(5)

(7)

(8)

(10)

#### 7.5.3 Data Transfer Protocols

The device features a multiSPI interface that allows the host controller to operate at slower SCLK speeds and still achieve the required cycle time with a faster response time. The multiSPI interface module offers two options to reduce the SCLK speed required for data transfer:

- 1. An option to increase the width of the output data bus

- 2. An option to enable double data rate (DDR) transfer

These two options can be combined to achieve further reduction in SCLK speed.

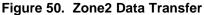

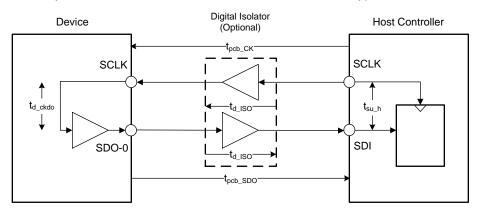

Figure 51 shows the delays between the host controller and the device in a typical serial communication.

Figure 51. Delays in Serial Communication

The total delay in the path is given by Equation 11:

In a standard SPI protocol, the host controller and the device launch and capture data bits on alternate SCLK edges. Therefore, the  $t_{d\_total\_serial}$  delay must be kept less than half of the SCLK duration. Equation 12 shows the fastest clock allowed by the SPI protocol.

$$f_{clk-SPI} \le \frac{1}{2 \times t_{d\_total-serial}}$$

(12)

Larger values of the  $t_{d\_total\_serial}$  delay restrict the maximum SCLK speed for the SPI protocol, resulting in higher read and response times, and can increase cycle times. To remove this restriction on the SCLK speed, the multiSPI interface module supports an *ADC-master* or *source-synchronous* mode of operation.

Figure 52. Delays in Source-Synchronous Communication

(11)

STRUMENTS

As illustrated in Figure 52, in ADC-master or source-synchronous mode, the device provides a synchronous output clock (on the RVS pin) along with the output data (on the SDO-x pins).

For a source-synchronous data transfer, the total delay in the path is given by Equation 13:

$t_{d\_total\_srcsync} = t_{pcb\_RVS} - t_{pcb\_SDO} + t_{su\_h}$

(13)

As illustrated in Equation 11 and Equation 13, the ADC-master or source-synchronous mode completely eliminates the affect of isolator delays and the clock-to-data delays, which are typically the largest contributors in the overall delay computation.

Furthermore, the actual values of  $t_{pcb_RVS}$  and  $t_{pcb_SDO}$  do not matter. In most cases, the  $t_{d_total_srcsync}$  delay can be kept at a minimum by routing the RVS and SDO lines together on the PCB. Therefore, the ADC-master or source-synchronous mode allows the host controller and device to operate at much higher SCLK speeds.

## 7.5.3.1 Protocols for Configuring the Device

As shown in Table 4, the host controller can use any of the four legacy, SPI-compatible protocols (SPI-00-S, SPI-01-S, SPI-10-S, or SPI-11-S) to write data in to the device.

| PROTOCOL | SCLK POLARITY<br>(At CS Falling Edge) | SCLK PHASE<br>(Capture Edge) | SDI_CNTL | SDO_CNTL | DIAGRAM   |

|----------|---------------------------------------|------------------------------|----------|----------|-----------|

| SPI-00-S | Low                                   | Rising                       | 00h      | 00h      | Figure 53 |

| SPI-01-S | Low                                   | Falling                      | 01h      | 00h      | Figure 54 |

| SPI-10-S | High                                  | Falling                      | 02h      | 00h      | Figure 55 |

| SPI-11-S | High                                  | Rising                       | 03h      | 00h      | Figure 56 |

### Table 4. SPI Protocols for Configuring the Device

On power-up or after coming out of any asynchronous reset, the device supports the SPI-00-S protocol for data read and data write operations.

To select a different SPI-compatible protocol, program the SDI\_MODE[1:0] bits in the SDI\_CNTL register. This first write operation must adhere to the SPI-00-S protocol. Any subsequent data transfer frames must adhere to the newly selected protocol.

Figure 53, Figure 54, Figure 55, and Figure 56 detail the four protocols using an optimal, 20-SCLK frame; see the *Timing Requirements: SPI-Compatible Serial Interface* section for associated timing parameters.

### NOTE

As explained in the *Data Transfer Frame* section, a valid write operation to the device requires a minimum of 20 SCLKs to be provided within a data transfer frame.

ADS9110 ZHCSE95A – OCTOBER 2015 – REVISED OCTOBER 2015

| CS   |                                             | CS   |                                        |

|------|---------------------------------------------|------|----------------------------------------|

| SCLK |                                             | SCLK |                                        |

| SDI  | B19 B18 B17 B1 B0                           | SDI  | B19 B18 B1 B0                          |

| RVS  |                                             | RVS  |                                        |

|      | -<br>Figure 53. SPI-00-S Protocol, 20 SCLKs |      | Figure 54. SPI-01-S Protocol, 20 SCLKs |

| ĊŚ   |                                             | CS   |                                        |

| SCLK |                                             | SCLK |                                        |

| SDI  | B19 B18 B17 B1 B0                           | SDI  | B19 B18 B2 B1 B0                       |

| RVS  |                                             | RVS  |                                        |

|      | - Figure 55. SPI-10-S Protocol, 20 SCLKs    |      | Figure 56. SPI-11-S Protocol, 20 SCLKs |

## 7.5.3.2 Protocols for Reading From the Device

The protocols for the data read operation can be broadly classified into three categories:

- 1. Legacy, SPI-compatible (SPI-xy-S) protocols,

- 2. SPI-compatible protocols with bus width options (SPI-xy-D and SPI-xy-Q), and

- 3. Source-synchronous (SRC) protocols

### 7.5.3.2.1 Legacy, SPI-Compatible (SYS-xy-S) Protocols

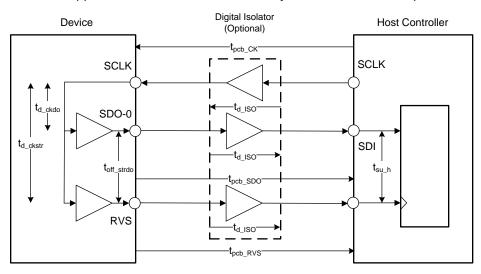

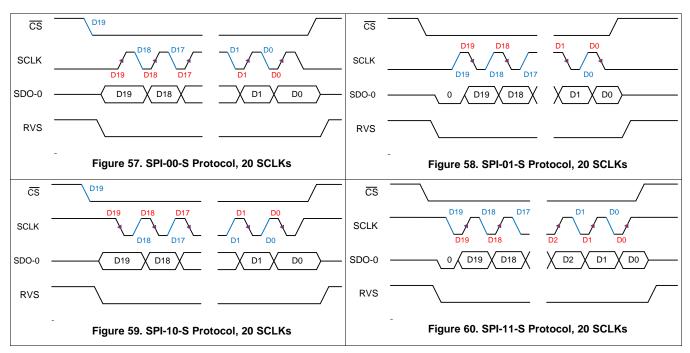

As shown in Table 5, the host controller can use any of the four legacy, SPI-compatible protocols (SPI-00-S, SPI-01-S, SPI-10-S, or SPI-11-S) to read data from the device.

| PROTOCOL | SCLK POLARITY<br>(At CS Falling<br>Edge) | SCLK PHASE<br>(Capture Edge) | MSB BIT<br>LAUNCH EDGE       | SDI_CNTL | SDO_CNTL | DIAGRAM   |

|----------|------------------------------------------|------------------------------|------------------------------|----------|----------|-----------|

| SPI-00-S | Low                                      | Rising                       | CS falling                   | 00h      | 00h      | Figure 57 |

| SPI-01-S | Low                                      | Falling                      | 1 <sup>st</sup> SCLK rising  | 01h      | 00h      | Figure 58 |

| SPI-10-S | High                                     | Falling                      | CS falling                   | 02h      | 00h      | Figure 59 |

| SPI-11-S | High                                     | Rising                       | 1 <sup>st</sup> SCLK falling | 03h      | 00h      | Figure 60 |

Table 5. SPI Protocols for Reading From the Device

On power-up or after coming out of any asynchronous reset, the device supports the SPI-00-S protocol for data read and data write operations. To select a different SPI-compatible protocol for both the data transfer operations:

- 1. Program the SDI\_MODE[1:0] bits in the SDI\_CNTL register. This first write operation must adhere to the SPI-00-S protocol. Any subsequent data transfer frames must adhere to the newly selected protocol.

- 2. Set the SDO\_MODE[1:0] bits = 00b in the SDO\_CNTL register.

When using any of the SPI-compatible protocols, the RVS output remains low throughout the data transfer frame; see the *Timing Requirements: SPI-Compatible Serial Interface* table for associated timing parameters.

### ADS9110

ZHCSE95A-OCTOBER 2015-REVISED OCTOBER 2015

www.ti.com.cn

Figure 57, Figure 58, Figure 59, and Figure 60 explain the details of the four protocols using an optimal, 20-SCLK frame. As explained in the *Data Transfer Frame* section, the host controller can use a *short* data transfer frame to read only the required number of MSB bits from the 20-bit output data word.

With SDO\_CNTL[7:0] = 00h, if the host controller uses a long data transfer frame, the device exhibits daisy-chain operation (see the *Multiple Devices: Daisy-Chain Topology* section).

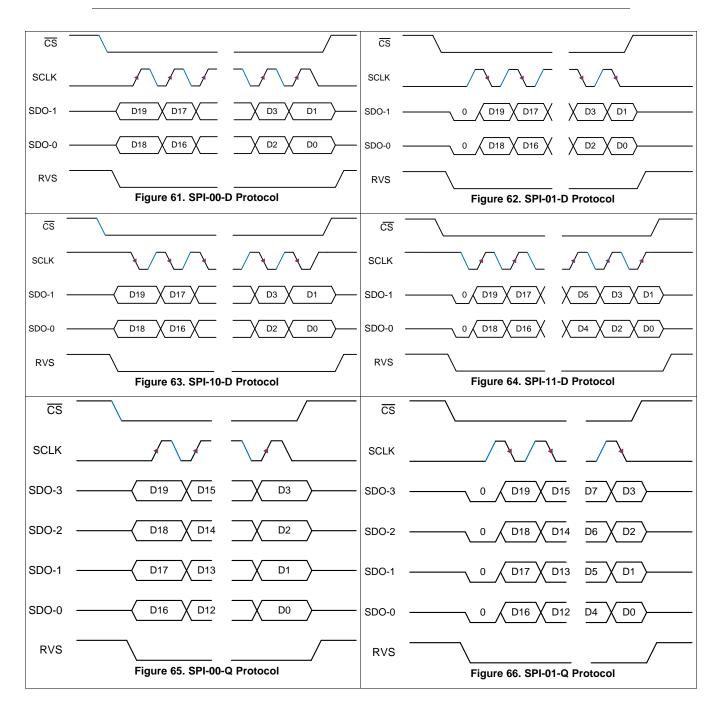

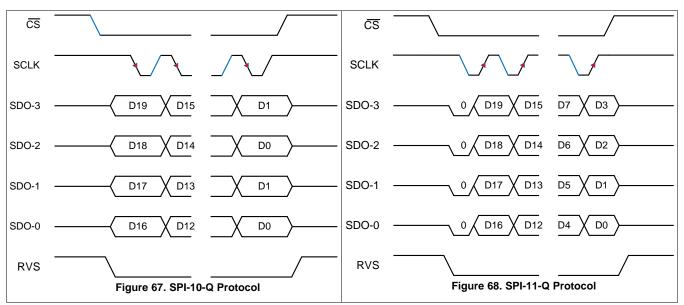

### 7.5.3.2.2 SPI-Compatible Protocols with Bus Width Options

The device provides an option to increase the SDO bus width from one bit (default, single SDO) to two bits (dual SDO) or to four bits (quad SDO) when operating with any of the four legacy, SPI-compatible protocols.

Set the SDO\_WIDTH[1:0] bits in the SDO\_CNTL register to select the SDO bus width.

In dual SDO mode (SDO\_WIDTH[1:0] = 10b), two bits of data are launched on the two SDO pins (SDO-0 and SDO-1) on every SCLK launch edge.

In quad SDO mode (SDO\_WIDTH[1:0] = 11b), four bits of data are launched on the four SDO pins (SDO-0, SDO-1, SDO-2, and SDO-3) on every SCLK launch edge.

The SCLK launch edge depends upon the SPI protocol selection (as shown in Table 6).

| PROTOCOL | SCLK POLARITY<br>(At CS Falling<br>Edge) | SCLK PHASE<br>(Capture Edge) | MSB BIT<br>LAUNCH EDGE | SDI_CNTL | SDO_CNTL | DIAGRAM   |  |  |  |

|----------|------------------------------------------|------------------------------|------------------------|----------|----------|-----------|--|--|--|

| SPI-00-D | Low                                      | Rising                       | CS falling             | 00h      | 08h      | Figure 61 |  |  |  |

| SPI-01-D | Low                                      | Falling                      | First SCLK rising      | 01h      | 08h      | Figure 62 |  |  |  |

| SPI-10-D | High                                     | Falling                      | CS falling             | 02h      | 08h      | Figure 63 |  |  |  |

| SPI-11-D | High                                     | Rising                       | First SCLK falling     | 03h      | 08h      | Figure 64 |  |  |  |

| SPI-00-Q | Low                                      | Rising                       | CS falling             | 00h      | 0Ch      | Figure 65 |  |  |  |

| SPI-01-Q | Low                                      | Falling                      | First SCLK rising      | 01h      | 0Ch      | Figure 66 |  |  |  |

| SPI-10-Q | High                                     | Falling                      | CS falling             | 02h      | 0Ch      | Figure 67 |  |  |  |

| SPI-11-Q | High                                     | Rising                       | First SCLK falling     | 03h      | 0Ch      | Figure 68 |  |  |  |

## Table 6. SPI-Compatible Protocols with Bus Width Options

When using any of the SPI-compatible protocols, the RVS output remains low throughout the data transfer frame.

Figure 61 to Figure 68 illustrate how the wider data bus allows the host controller to read all 20 bits of the output data word using *short* data transfer frames; see the *Timing Requirements: SPI-Compatible Serial Interface* table for associated timing parameters.

# **NOTE** With SDO\_CNTL[7:0] $\neq$ 00h, a long data transfer frame does not result in daisy-chain operation.

ADS9110

ZHCSE95A - OCTOBER 2015 - REVISED OCTOBER 2015

www.ti.com.cn

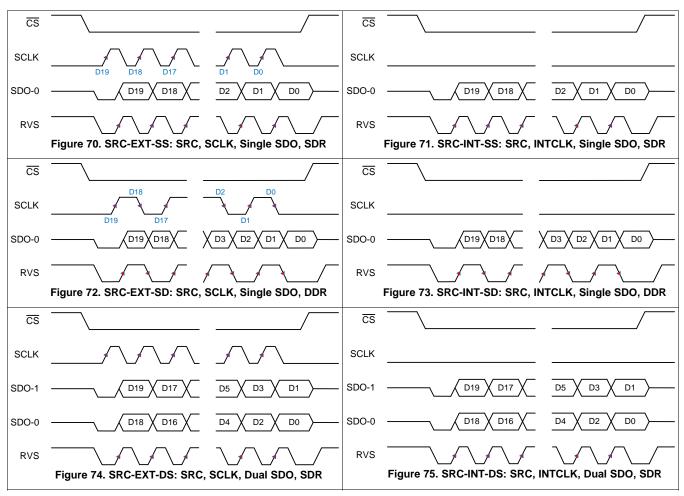

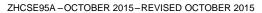

### 7.5.3.2.3 Source-Synchronous (SRC) Protocols

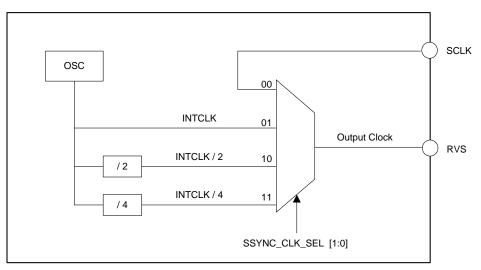

As described in the *Data Transfer Protocols* section, the multiSPI interface supports an ADC-master or sourcesynchronous mode of data transfer between the device and host controller. In this mode, the device provides an output clock that is synchronous with the output data. Furthermore, the host controller can also select the output clock source, data bus width, and data transfer rate.

#### 7.5.3.2.3.1 Output Clock Source Options with SRC Protocols

In all SRC protocols, the RVS pin provides the output clock. The device allows this output clock to be synchronous to either the external clock provided on the SCLK pin or to the internal clock of the device. Furthermore, this internal clock can be divided by a factor of two or four to lower the data rates.

As shown in Figure 69, set the SSYNC\_CLK\_SEL[1:0] bits in the SDO\_CNTL register to select the output clock source.

Figure 69. Output Clock Source options with SRC Protocols

## 7.5.3.2.3.2 Bus Width Options with SRC Protocols

The device provides an option to increase the SDO bus width from one bit (default, single SDO) to two bits (dual SDO) or to four bits (quad SDO) when operating with any of the SRC protocols. Set the SDO\_WIDTH[1:0] bits in the SDO\_CNTL register to select the SDO bus width.

In dual SDO mode (SDO\_WIDTH[1:0] = 10b), two bits of data are launched on the two SDO pins (SDO-0 and SDO-1) on every SCLK rising edge.

In quad SDO mode (SDO\_WIDTH[1:0] = 11b), four bits of data are launched on the four SDO pins (SDO-0, SDO-1, SDO-2, and SDO-3) on every SCLK rising edge.

#### 7.5.3.2.3.3 Output Data Rate Options with SRC Protocols

The device provides an option to transfer the data to the host controller at single data rate (default, SDR) or at double data rate (DDR). Set the DATA\_RATE bit in the SDO\_CNTL register to select the data transfer rate.

In SDR mode (DATA\_RATE = 0b), the RVS pin toggles from low to high and the output data bits are launched on the SDO pins on the output clock rising edge.

In DDR mode (DTA\_RATE = 1b), the RVS pin toggles and the output data bits are launched on the SDO pins on every output clock edge, starting with the first rising edge.

The device supports all 24 combinations of output clock source, bus width, and output data rate, as shown in Table 7.

| PROTOCOL   | OUTPUT CLOCK<br>SOURCE | BUS WIDTH | OUTPUT DATA<br>RATE | SDI_CNTL    | SDO_CNTL | DIAGRAM   |

|------------|------------------------|-----------|---------------------|-------------|----------|-----------|

| SRC-EXT-SS | SCLK                   | Single    | SDR                 |             | 03h      | Figure 70 |

| SRC-INT-SS | INTCLK                 | Single    | SDR                 |             | 43h      |           |

| SRC-IB2-SS | INTCLK / 2             | Single    | SDR                 |             | 83h      | Figure 71 |

| SRC-IB4-SS | INTCLK / 4             | Single    | SDR                 |             | C3h      |           |

| SRC-EXT-DS | SCLK                   | Dual      | SDR                 |             | 0Bh      | Figure 74 |

| SRC-INT-DS | INTCLK                 | Dual      | SDR                 |             | 4Bh      |           |

| SRC-IB2-DS | INTCLK / 2             | Dual      | SDR                 |             | 8Bh      | Figure 75 |

| SRC-IB4-DS | INTCLK / 4             | Dual      | SDR                 |             | CBh      |           |

| SRC-EXT-QS | SCLK                   | Quad      | SDR                 |             | 0Fh      | Figure 78 |

| SRC-INT-QS | INTCLK                 | Quad      | SDR                 |             | 4Fh      |           |

| SRC-IB2-QS | INTCLK / 2             | Quad      | SDR                 |             | 8Fh      | Figure 79 |

| SRC-IB4-QS | INTCLK / 4             | Quad      | SDR                 | 00h, 01h,   | CFh      |           |

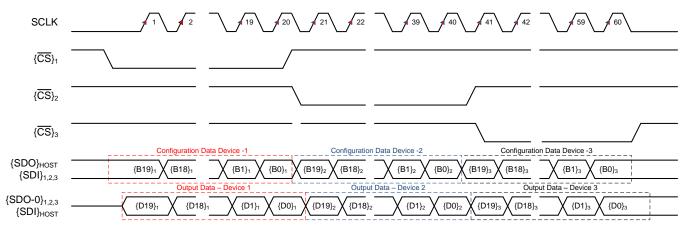

| SRC-EXT-SD | SCLK                   | Single    | DDR                 | 02h, or 03h | 13h      | Figure 72 |