## 双通道、11/16位、2.8 GSPS、 TxDAC+数模转换器

## AD9135/AD9136

#### 产品特性

支持的输入数据速率大于2 GSPS

专有低杂散与失真设计

SFDR = 82 dBc(直流中频, -9 dBFS)

灵活的8通道JESD204B接口

多芯片同步

固定延迟

数据发生器延迟补偿

可选1倍、2倍、4倍或8倍插值滤波器

低功耗架构

发射使能功能可进一步省电,实现输出状态的瞬时控制

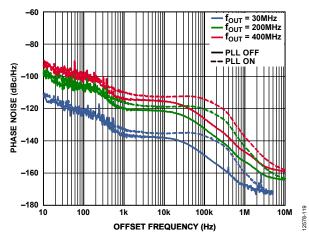

高性能、低噪声锁相环(PLL)时钟倍频器

数字反sinc滤波器

低功耗: 1.42 W(1.6 GSPS, 全部工作条件)

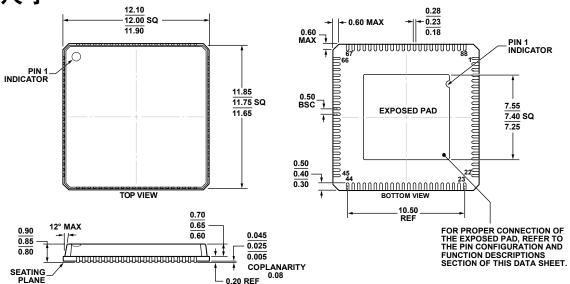

88引脚LFCSP(带裸露焊盘)

#### 应用

无线通信

3G/4G W-CDMA基站

宽带中继器

软件定义无线电

宽带通信

点对点

本地多点分配服务(LMDS)和多通道多点分配服务(MMDS)

发射分集、多路输入/多路输出(MIMO)

仪器仪表

自动测试设备

#### 概述

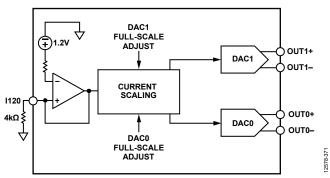

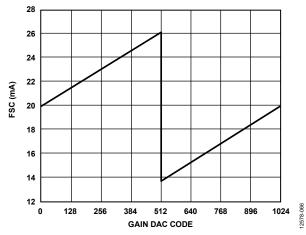

AD9135/AD9136 TxDAC+\*是双通道、11/16位、高动态范围数模转换器(DAC),提供最高2800 MSPS的采样速率,可以在极宽的带宽内产生多载波。DAC输出经过优化,可以与ADI公司的ADRF6720和ADRF670x模拟正交调制器(AQM)无缝接口。可选三线式或四线式串行端口接口(SPI)允许对许多内部参数进行编程和回读。满量程输出电流可以在13.9 mA至27.0 mA典型范围内进行编程。AD9135/AD9136提供88引脚LFCSP封装。

#### Rev. 0 Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

#### 功能框图 QUAD MOD LPF OSYSREF+ ADRF6720/ ADRF670x ≋ DAC 0°/90° PHASE RF OUTPUT ◀ O.IESD204B SHIFTER æ DAC SYNCOUT0± AD9135/ ► SYNCOUT1± AD9136 LO\_IN MOD\_SPI **CLK±** DAC SPI 图1.

#### 产品特色

- 1. 高于2 GHz的超宽复信号带宽,支持新兴的宽带和多频带 无线应用。

- 先进的低杂散与失真设计技术,从基带到高中频的宽带 信号可以实现高质量合成。

- 3. 支持JESD204B子类1,可简化软件和硬件设计中的多芯片同步。

- 4. 对于具有串行器/解串器(SERDES) JESD204B 8通道接口的数据接口宽度,引脚更少。

- 5. 可编程发射使能功能有助于轻松实现功耗与唤醒时间之间的设计平衡。

- 6. 小型封装,尺寸为12 mm×12 mm。

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# 目录

| 特性                | I  |

|-------------------|----|

| 应用                | 1  |

| 功能框图              | 1  |

| 概述                | 1  |

| 产品特色              | 1  |

| 修订历史              | 3  |

| 详细功能框图            | 4  |

| 技术规格              | 5  |

| 直流规格              | 5  |

| 数字规格              | 6  |

| 不同电源下的DAC最大更新速率规格 | 7  |

| JESD204B串行接口速度规格  | 7  |

| SYSREF至DAC时钟时序规格  | 8  |

| 数字输入数据时序规格        | 8  |

| 延迟差异规格            | 9  |

| JESD204B接口电气规格    | 9  |

| 交流规格              | 10 |

| 绝对最大额定值           | 11 |

| 热阻                | 11 |

| ESD警告             | 11 |

| 引脚配置和功能描述         | 12 |

| 术语                | 15 |

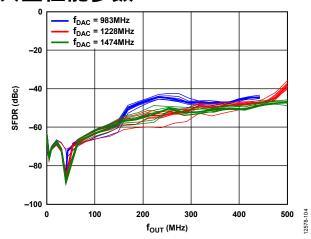

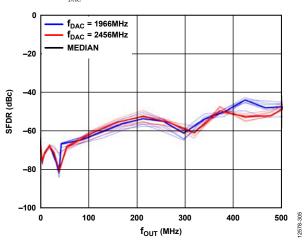

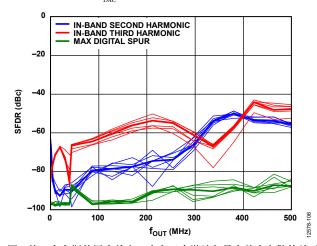

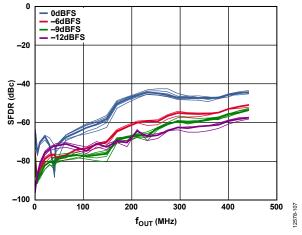

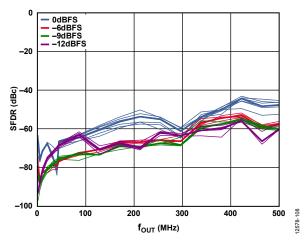

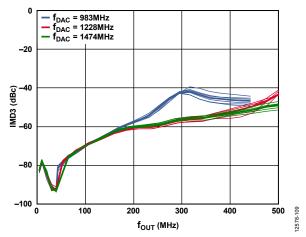

| 典型性能参数            | 16 |

| 工作原理              | 22 |

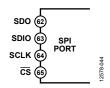

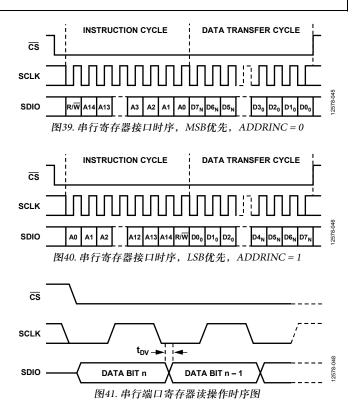

| 串行端口操作            | 23 |

| 数据格式              | 23 |

| 串行端口引脚功能描述        | 23 |

| 串行端口选项            | 23 |

| 芯片信息              | 25 |

| 器件设置指南            | 26 |

| 概述                | 26 |

| 第一步:启动DAC         | 26 |

| 第二步:数字数据路径        | 26 |

| 第三步: 传输层          | 27 |

| 第四步:物理层           | 27 |

| 第五步:数据链路层         | 28 |

| 第六步: 可选错误监控       | 28 |

| 第七步:可选特性          | 28 |

| DAC PLL设置         | 29 |

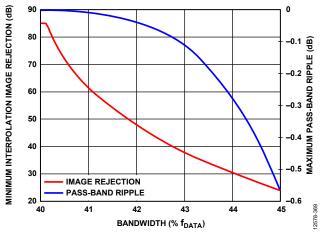

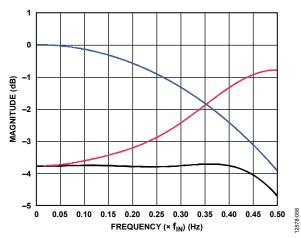

| 插值             | 29 |

|----------------|----|

| JESD204B设置     | 29 |

| SERDES时钟设置     | 30 |

| 均衡模式设置         | 30 |

| 链路延迟设置         | 30 |

| 纵横设置           | 32 |

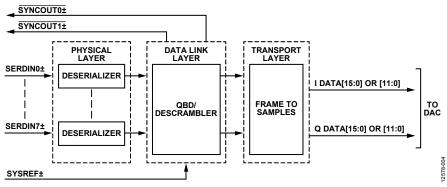

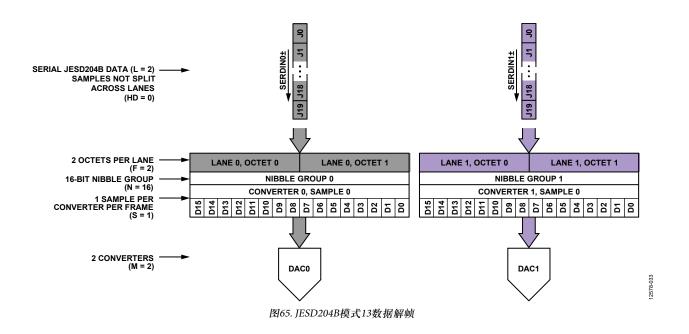

| JESD204B串行数据接口 | 33 |

| JESD204B概述     | 33 |

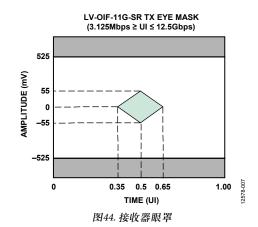

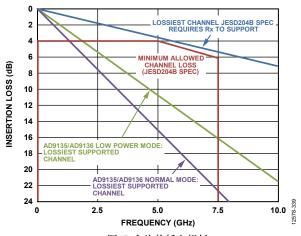

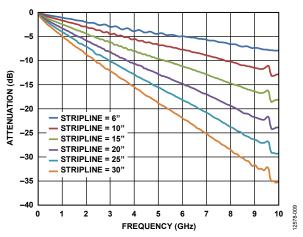

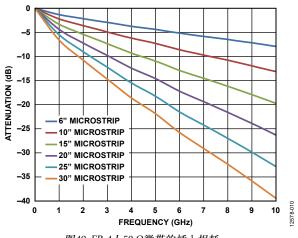

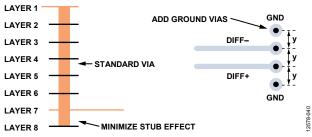

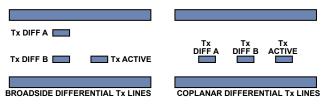

| 物理层            | 34 |

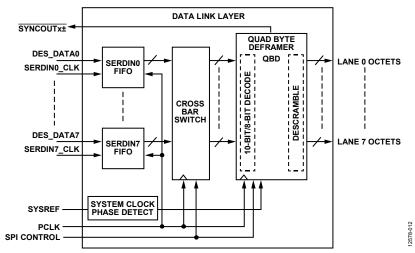

| 数据链路层          | 37 |

| 传输层            | 45 |

| JESD204B测试模式   | 55 |

| JESD204B错误监控   | 56 |

| 硬件考虑           | 58 |

| 数字数据路径         | 62 |

| DAC传呼          | 62 |

| 数据格式           | 62 |

| 插值滤波器          | 62 |

| 反Sinc          | 63 |

| 数字增益、直流偏移和群延迟  | 63 |

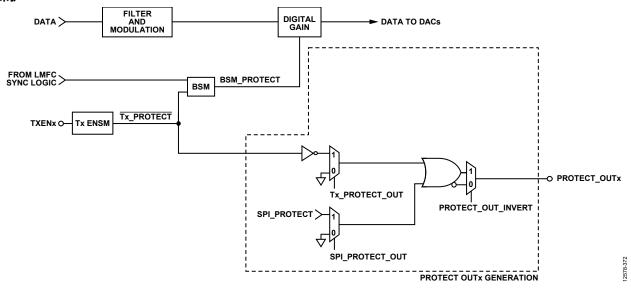

| 下游保护           | 65 |

| 数据路径PRBS       | 66 |

| 直流测试模式         | 67 |

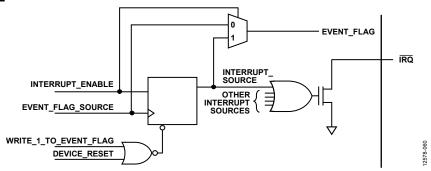

| 中断请求操作         | 68 |

| 中断服务程序         | 68 |

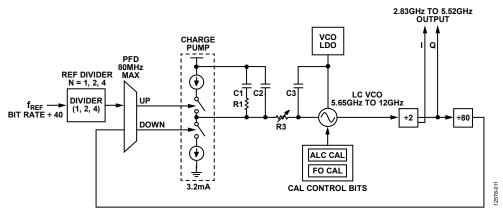

| DAC输入时钟配置      | 70 |

| 驱动CLK±输入       | 70 |

| 时钟倍频           | 70 |

| 启动PLL          | 72 |

| 模拟输出           | 73 |

| 发射DAC操作        | 73 |

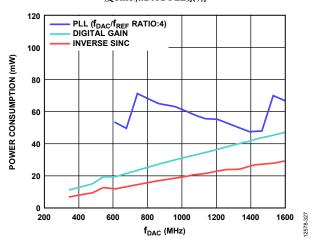

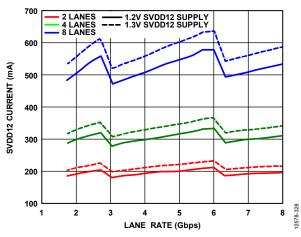

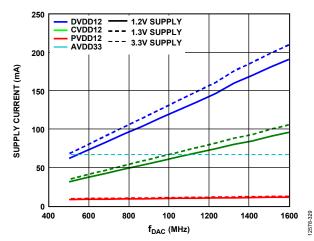

| 器件功耗           | 76 |

| 温度传感器          | 76 |

| 启动序列           | 77 |

| 第一步:启动DAC      | 77 |

| 第二步:数字数据路径     | 77 |

| 第三步: 传输层       | 78 |

| 第四步:物理层        | 78 |

| 第五步:数据链路层      | 78 |

| 第六步: 错误监控      | 78 |

| 寄存器映射和描述79             | 外形尺寸116 |

|------------------------|---------|

| 器件配置寄存器映射79            | 订购指南116 |

| 器件配置寄存器描述85            |         |

| 三种不同DAC PLL参考频率的查找表112 |         |

### 修订历史

2014年10月—修订版0: 初始版

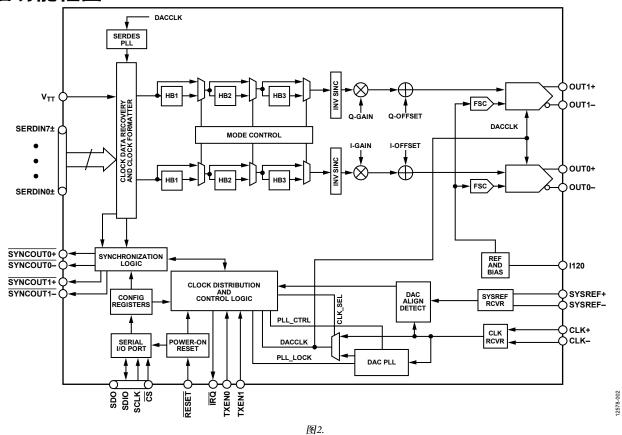

## 详细功能框图

Rev. 0 | Page 4 of 116

## 技术规格

### 直流规格

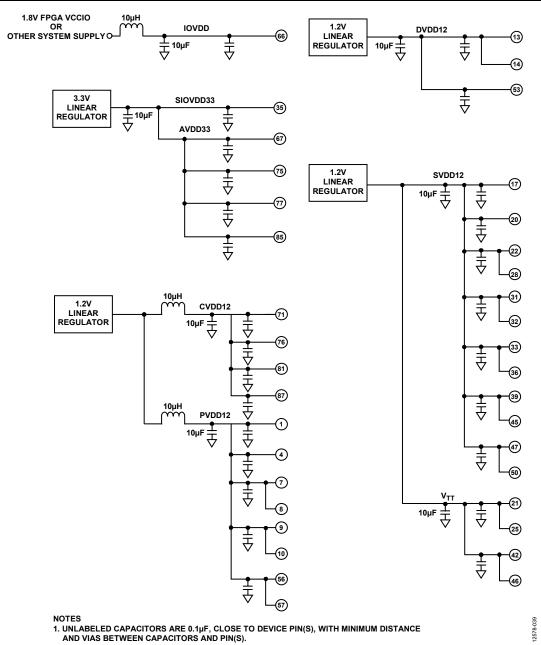

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V,SVDD12 = 1.2 V, $T_A = -40$ °C至+85°C, $T_{OUTES} = 20 \text{ mA}$ 。

### 表1.

|                              |                                                                        | AD9135 |                |       |       |              |       |        |

|------------------------------|------------------------------------------------------------------------|--------|----------------|-------|-------|--------------|-------|--------|

| 参数                           | 测试条件/注释                                                                | 最小值    | 典型值            | 最大值   | 最小值   | 典型值          | 最大值   | 单位     |

| 分辨率                          |                                                                        |        | 11             |       |       | 16           |       | 位      |

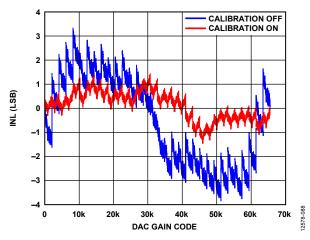

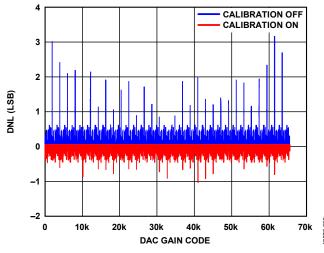

| 精度                           | 经过校准                                                                   |        |                |       |       |              |       |        |

| 差分非线性(DNL)                   |                                                                        |        | ±0.175         |       |       | ±1.0         |       | LSB    |

| 积分非线性(INL)                   |                                                                        |        | ±0.35          |       |       | ±2.0         |       | LSB    |

| 主DAC输出                       |                                                                        |        |                |       |       |              |       |        |

| 增益误差                         | 使用内部基准源                                                                | -2.5   | +2             | +5.5  | -2.5  | +2           | +5.5  | % FSR  |

| I/Q增益失配                      |                                                                        | -0.6   |                | +0.6  | -0.6  |              | +0.6  | % FSR  |

| 满量程输出电流(I <sub>OUTES</sub> ) | 基于I120与GND之间的4 kΩ外部电阻                                                  |        |                |       |       |              |       |        |

| 最大设置                         |                                                                        | 25.5   | 27.0           | 28.6  | 25.5  | 27.0         | 28.6  | mA     |

| 最小设置                         |                                                                        | 13.1   | 13.9           | 14.8  | 13.1  | 13.9         | 14.8  | mA     |

| 输出顺从电压范围                     |                                                                        | -250   |                | +750  | -250  |              | +750  | mV     |

| 输出电阻                         |                                                                        | 230    | 0.2            | 1730  | 230   | 0.2          | 1750  | MΩ     |

| 输出电容                         |                                                                        |        | 3.0            |       |       | 3.0          |       | pF     |

| 增益DAC单调性                     |                                                                        |        | 保证             |       |       | 9.0<br>保证    |       | рі     |

| 建立时间                         | 至±0.5 LSB范围内                                                           |        | <b>米</b> 坦: 20 |       |       | 不 u.c.<br>20 |       | nc     |

|                              | 至±0.5 L3B范围内                                                           | -      | 20             |       |       | 20           |       | ns     |

| 主DAC温度漂移                     |                                                                        |        | 0.04           |       |       | 0.04         |       |        |

| 偏移                           |                                                                        |        | 0.04           |       |       | 0.04         |       | ppm/°C |

| 増益                           |                                                                        |        | 32             |       |       | 32           |       | ppm/°C |

| 基准电压                         |                                                                        |        | 16             |       |       | 16           |       | ppm/°C |

| 基准电压                         |                                                                        |        |                |       |       |              |       |        |

| 内部基准电压                       |                                                                        |        | 1.2            |       |       | 1.2          |       | V      |

| 模拟电源电压                       |                                                                        |        |                |       |       |              |       |        |

| AVDD33                       |                                                                        | 3.13   | 3.3            | 3.47  | 3.13  | 3.3          | 3.47  | V      |

| PVDD12                       |                                                                        | 1.14   | 1.2            | 1.26  | 1.14  | 1.2          | 1.26  | V      |

| CVDD12                       |                                                                        | 1.14   | 1.2            | 1.26  | 1.14  | 1.2          | 1.26  | V      |

| 数字电源电压                       |                                                                        |        |                |       |       |              |       |        |

| SIOVDD33                     |                                                                        | 3.13   | 3.3            | 3.47  | 3.13  | 3.3          | 3.47  | V      |

| $V_{TT}$                     |                                                                        | 1.1    | 1.2            | 1.37  | 1.1   | 1.2          | 1.37  | V      |

| DVDD12                       | 1.2 V标称电源电压                                                            | 1.14   | 1.2            | 1.26  | 1.14  | 1.2          | 1.26  | V      |

|                              | 1.3 V标称电源电压                                                            | 1.274  | 1.3            | 1.326 | 1.274 | 1.3          | 1.326 | V      |

| SVDD12                       | 1.2 V标称电源电压                                                            | 1.14   | 1.2            | 1.26  | 1.14  | 1.2          | 1.26  | V      |

|                              | 1.3 V标称电源电压                                                            | 1.274  | 1.3            | 1.326 | 1.274 | 1.3          | 1.326 | V      |

| IOVDD                        |                                                                        | 1.71   | 1.8            | 3.47  | 1.71  | 1.8          | 3.47  | V      |

|                              |                                                                        |        |                |       |       |              |       |        |

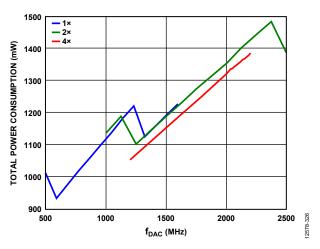

| 1倍插值模式                       | $f_{DAC} = 1.6 \text{ GSPS}, \text{ IF} = 40 \text{ MHz}, \text{ PLL}$ |        | 1.42           | 1.74  |       | 1.42         | 1.74  | W      |

| Пишк                         | 启,数字增益开启,反sinc开启,                                                      |        |                |       |       |              |       |        |

|                              | DAC满量程电流(I <sub>OUTFS</sub> ) = 20 mA                                  |        |                |       |       |              |       |        |

| AVDD33                       | D/C(例至1至1000CTFS) — 20 TIM                                             |        | 68             | 73    |       | 68           | 73    | mA     |

| PVDD12                       |                                                                        |        | 100            | 113.4 |       | 100          | 113.4 | mA     |

| CVDD12                       |                                                                        |        | 101            | 112   |       | 101          | 112   | mA     |

| SVDD12                       | ●<br>包括V <sub>II</sub>                                                 |        | 554            | 665   |       | 554          | 665   | mA     |

| DVDD12                       | - H ·π                                                                 |        | 196            | 224   |       | 196          | 224   | mA     |

| SIOVDD33                     |                                                                        |        | 11             | 12    |       | 11           | 12    | mA     |

|                              |                                                                        |        |                |       |       |              |       |        |

| IOVDD                        |                                                                        |        | 36             | 50    |       | 36           | 50    | μΑ     |

### 数字规格

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V,SVDD12 = 1.2 V, $T_A = -40$ °C至+85°C, $T_{OUTFS} = 20 \text{ mA}$ 。

### 表2.

| 参数                          | 符号               | 测试条件/注释                                            | 最小值         | 典型值  | 最大值                         | 单位   |

|-----------------------------|------------------|----------------------------------------------------|-------------|------|-----------------------------|------|

| CMOS输入逻辑电平                  |                  |                                                    |             |      |                             |      |

| 输入电压(V <sub>IN</sub> )逻辑    |                  |                                                    |             |      |                             |      |

| 高                           |                  | 1.8 V ≤ IOVDD ≤ 3.3 V                              | 0.7 × IOVDD |      |                             | V    |

| 低                           |                  | 1.8 V ≤ IOVDD ≤ 3.3 V                              |             |      | $0.3 \times IOVDD$          | V    |

| CMOS输出逻辑电平                  |                  |                                                    |             |      |                             |      |

| 输出电压(V <sub>our</sub> )逻辑   |                  |                                                    |             |      |                             |      |

| 高                           |                  | 1.8 V ≤ IOVDD ≤ 3.3 V                              | 0.7 × IOVDD |      |                             | V    |

| 低                           |                  | 1.8 V ≤ IOVDD ≤ 3.3 V                              |             |      | $0.3 \times IOVDD$          | V    |

| 最大DAC更新速率 <sup>1</sup>      |                  |                                                    |             |      |                             |      |

|                             |                  | 1倍插值2(参见表4)                                        | 2120        |      |                             | MSPS |

|                             |                  | 2倍插值 <sup>2</sup>                                  | 2120        |      |                             | MSPS |

|                             |                  | 4倍插值 <sup>3</sup>                                  | 2800        |      |                             | MSPS |

|                             |                  | 8倍插值3                                              | 2800        |      |                             | MSPS |

| 调整后的DAC更新速率                 |                  |                                                    |             |      |                             |      |

|                             |                  | 1倍插值                                               | 2120        |      |                             | MSPS |

|                             |                  | 2倍插值                                               | 1060        |      |                             | MSPS |

|                             |                  | 4倍插值                                               | 700         |      |                             | MSPS |

|                             |                  | 8倍插值                                               | 350         |      |                             | MSPS |

| 接口4                         |                  |                                                    |             |      |                             |      |

| JESD204B通道数                 |                  |                                                    |             | 8    |                             | 通道   |

| JESD204B串行接口速度              |                  |                                                    |             |      |                             |      |

| 最小值                         |                  | 每通道                                                |             |      | 1.42                        | Gbps |

| 最大值                         |                  | 每通道,SVDD12 = 1.3 V ± 2%                            | 10.64       |      |                             | Gbps |

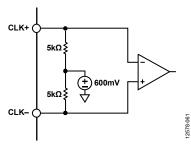

| DAC时钟输入(CLK+、CLK-)          |                  |                                                    |             |      |                             |      |

| 差分峰峰值电压                     |                  |                                                    | 400         | 1000 | 2000                        | mV   |

| 共模电压                        |                  | 自偏置输入,交流耦合                                         |             | 600  |                             | mV   |

| 最大时钟速率                      |                  |                                                    | 2800        |      |                             | MHz  |

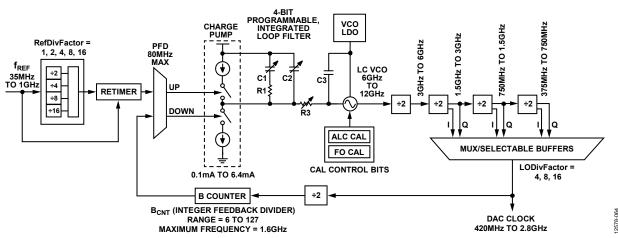

| REFCLK⁵频率(PLL模式)            |                  | $6.0 \text{ GHz} \le f_{VCO} \le 12.0 \text{ GHz}$ | 35          |      | 1000                        | MHz  |

| 系统参考输入                      |                  |                                                    |             |      |                             |      |

| (SYSREF+\ SYSREF-)          |                  |                                                    |             |      |                             |      |

| 差分峰峰值电压                     |                  |                                                    | 400         | 1000 | 2000                        | mV   |

| 共模电压                        |                  |                                                    | 0           |      | 2000                        | mV   |

| SYSREF±频率 <sup>6</sup>      |                  |                                                    |             |      | $f_{DATA}/(K \times (F/S))$ | Hz   |

| SYSREF信号至DAC时钟 <sup>7</sup> |                  | SYSREF差分摆幅 = 0.4 V, 压摆率 = 1.3 V/ns, 测试的共模电压: 交流耦   |             |      |                             |      |

|                             |                  | 合、0V、0.6V、1.25V、2.0V                               |             |      |                             |      |

| 建立时间                        | t <sub>SSD</sub> | 1, 61, 6161, 11261, 2161                           | 131         |      |                             | ps   |

| 保持时间                        | t <sub>HSD</sub> |                                                    | 119         |      |                             | ps   |

| 阻挡窗口                        | KOW              |                                                    |             | 20   |                             | ps   |

| SPI                         |                  |                                                    |             |      |                             | 1    |

| 最大时钟速率                      | SCLK             | IOVDD = 1.8 V                                      | 10          |      |                             | MHz  |

| 最小SCLK脉冲宽度                  |                  |                                                    |             |      |                             | 1    |

| 高                           | t <sub>PWH</sub> |                                                    |             |      | 8                           | ns   |

| 低                           | t <sub>PWL</sub> |                                                    |             |      | 12                          | ns   |

| SDIO至SCLK                   |                  |                                                    |             |      |                             | 1    |

| 建立时间                        | t <sub>DS</sub>  |                                                    | 5           |      |                             | ns   |

| 保持时间                        | t <sub>DH</sub>  |                                                    | 2           |      |                             | ns   |

| 参数       | 符号                | 测试条件/注释 | 最小值 | 典型值 最大值 | 单位 |

|----------|-------------------|---------|-----|---------|----|

| SDO至SCLK |                   |         |     |         |    |

| 数据有效窗口   | t <sub>DV</sub>   |         | 25  |         | ns |

| CS至SCLK  |                   |         |     |         |    |

| 建立时间     | t <sub>s</sub> cs |         | 5   |         | ns |

| 保持时间     | t <sub>H</sub> CS |         | 2   |         | ns |

- <sup>1</sup> DAC更新速率条件的详细规格参见表3。

- <sup>2</sup> 在较高电源电平下, 1倍和2倍插值的最大速度受JESD204B接口的限制。详情参见表4。

- 3 4倍和8倍插值的最大速度受DAC内核的限制。详情参见表4。

- <sup>4</sup> JESD速度条件的详细规格参见表4。

- 5 REFCLK为参考时钟。

- <sup>6</sup>K、F和S为JESD204B传输层参数。完整定义参见表41。

- <sup>7</sup> SYSREF信号至DAC时钟时序条件的详细规格参见表5。

#### 不同电源下的DAC最大更新速率规格

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V,SVDD12 = 1.2 V, $T_A = -40^{\circ}$ C至+85°C, $T_{OUTES} = 20 \text{ mA}$ 。

#### 表3.

| 参数         | 测试条件/注释                                  | 最    | <b>小值</b> | 典型值 | 最大值 | 单位   |

|------------|------------------------------------------|------|-----------|-----|-----|------|

| DAC最大更新速率  |                                          |      |           |     |     |      |

| 2倍、4倍和8倍插值 |                                          |      |           |     |     |      |

|            | DVDD12, CVDD12 = $1.2 \text{ V} \pm 5\%$ | 2.23 | 3         |     |     | GSPS |

|            | DVDD12, CVDD12 = $1.2 \text{ V} \pm 2\%$ | 2.4  |           |     |     | GSPS |

|            | DVDD12, CVDD12 = $1.3 \text{ V} \pm 2\%$ | 2.80 | )         |     |     | GSPS |

| 1倍插值       |                                          |      |           |     |     |      |

|            | DVDD12, CVDD12 = $1.2 \text{ V} \pm 5\%$ | 1.8  |           |     |     | GSPS |

|            | DVDD12, CVDD12 = $1.2 \text{ V} \pm 2\%$ | 1.93 | 3         |     |     | GSPS |

|            | DVDD12, CVDD12 = $1.3 \text{ V} \pm 2\%$ | 2.2  |           |     |     | GSPS |

#### JESD204B串行接口速度规格

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V,SVDD12 = 1.2 V, $T_A = -40^{\circ}$ C至+85°C, $T_{OUTFS} = 20 \text{ mA}_{\circ}$

#### 表4.

| 参数  | 测试条件/注释                  | 最小值  | 典型值 | 最大值   | 单位   |

|-----|--------------------------|------|-----|-------|------|

| 半速率 | SVDD12 = 1.2 V ± 5%      | 5.65 |     | 8.92  | Gbps |

|     | $SVDD12 = 1.2 V \pm 2\%$ | 5.65 |     | 9.42  | Gbps |

|     | $SVDD12 = 1.3 V \pm 2\%$ | 5.65 |     | 10.64 | Gbps |

| 全速率 | SVDD12 = 1.2 V ± 5%      | 2.83 |     | 4.63  | Gbps |

|     | $SVDD12 = 1.2 V \pm 2\%$ | 2.83 |     | 4.93  | Gbps |

|     | $SVDD12 = 1.3 V \pm 2\%$ | 2.83 |     | 5.52  | Gbps |

| 过采样 | SVDD12 = 1.2 V ± 5%      | 1.42 |     | 2.31  | Gbps |

|     | $SVDD12 = 1.2 V \pm 2\%$ | 1.42 |     | 2.46  | Gbps |

|     | $SVDD12 = 1.3 V \pm 2\%$ | 1.42 |     | 2.76  | Gbps |

#### SYSREF信号至DAC时钟时序规格

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V,SVDD12 = 1.2 V, $T_A = -40^{\circ}$ C至+85°C, $T_{OUTES} = 20 \text{ mA}$ ,SYSREF±共模电压 = 0.0 V、0.6 V、1.25 V和2.0 V。

#### 表5.

| 参数                                  | 测试条件/注释 | 最小值 典型值 最大個 | 単位 |

|-------------------------------------|---------|-------------|----|

| SYSREF差分摆幅 = 0.4 V,压摆率 = 1.3 V/ns   |         |             |    |

| 建立时间                                | 交流耦合    | 126         | ps |

|                                     | 直流耦合    | 131         | ps |

| 保持时间                                | 交流耦合    | 92          | ps |

|                                     | 直流耦合    | 119         | ps |

| SYSREF差分摆幅 = 0.7 V, 压摆率 = 2.28 V/ns |         |             |    |

| 建立时间                                | 交流耦合    | 96          | ps |

|                                     | 直流耦合    | 104         | ps |

| 保持时间                                | 交流耦合    | 77          | ps |

|                                     | 直流耦合    | 95          | ps |

| SYSREF摆幅 = 1.0 V,压摆率 = 3.26 V/ns    |         |             |    |

| 建立时间                                | 交流耦合    | 83          | ps |

|                                     | 直流耦合    | 90          | ps |

| 保持时间                                | 交流耦合    | 68          | ps |

|                                     | 直流耦合    | 84          | ps |

### 数字输入数据时序规格

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V,SVDD12 = 1.2 V, $T_A = 25$ °C, $T_{OUTES} = 20 \text{ mA}$ 。

#### 表6.

| 参数     | 测试条件/注释 | 最小值 | 典型值 | 最大值 | 单位                     |

|--------|---------|-----|-----|-----|------------------------|

| 延迟     |         |     |     |     |                        |

| 接口     |         |     | 17  |     | PClock <sup>1</sup> 周期 |

| 插值     |         |     |     |     |                        |

| 1×     |         |     | 66  |     | DAC时钟周期                |

| 2×     |         |     | 137 |     | DAC时钟周期                |

| 4×     |         |     | 251 |     | DAC时钟周期                |

| 8×     |         |     | 484 |     | DAC时钟周期                |

| 反Sinc  |         |     | 17  |     | DAC时钟周期                |

| 数字增益调整 |         |     | 12  |     | DAC时钟周期                |

| 上电时间   |         |     | 60  |     | μs                     |

<sup>&</sup>lt;sup>1</sup> PClock为AD9135/AD9136内部处理时钟,等于通道速率÷40。

#### 延迟差异规格

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V P PVD12 = 1.2 V P

#### 表7.

| 参数      | 最小值 | 典型值 | 最大值 | 单位      | 测试条件/注释 |

|---------|-----|-----|-----|---------|---------|

| DAC延迟差异 |     |     |     |         |         |

| 同步开     |     |     |     |         |         |

| PLL关闭   |     | 0   | 1   | DAC时钟周期 |         |

| PLL开启   | -1  |     | +1  | DAC时钟周期 |         |

#### JESD204B接口电气规格

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V P PVD12 = 1.2 V P

#### 表8.

| 参数                      | 符号                  | 测试条件/注释                                       | 最小值   | . 典型值 | 最大值   | 单位                     |

|-------------------------|---------------------|-----------------------------------------------|-------|-------|-------|------------------------|

| JESD204B数据输入            |                     |                                               |       |       |       |                        |

| 输入漏电流                   |                     | T <sub>A</sub> = 25°C                         |       |       |       |                        |

| 逻辑高电平                   |                     | 输入电平 = 1.2 V ± 0.25 V, V <sub>□</sub> = 1.2 V |       | 10    |       | μΑ                     |

| 逻辑低电平                   |                     | 输入电平 = 0 V                                    |       | -4    |       | μΑ                     |

| 单位间隔                    | UI                  |                                               | 94    |       | 714   | ps                     |

| 共模电压                    | $V_{RCM}$           | 交流耦合                                          | -0.05 |       | +1.85 | V                      |

|                         |                     | $V_{TT} = SVDD12^1$                           |       |       |       |                        |

| 差分电压                    | R_V <sub>DIFF</sub> |                                               | 110   |       | 1050  | mV                     |

| V <sub>T</sub> 源阻抗      | Z <sub>TT</sub>     | 对于直流                                          |       |       | 30    | Ω                      |

| 差分阻抗                    | Z <sub>RDIFF</sub>  | 对于直流                                          | 80    | 100   | 120   | Ω                      |

| 差分回损                    | RL <sub>RDIF</sub>  |                                               |       | 8     |       | dB                     |

| 共模回损                    | RL <sub>RCM</sub>   |                                               |       | 6     |       | dB                     |

| 差分输出(SYNCOUTx±)2        |                     |                                               |       |       |       |                        |

| 输出差分电压                  | V <sub>OD</sub>     |                                               |       |       |       |                        |

| 正常摆幅模式                  |                     | 寄存器0x2A5[0] = 0                               | 192   |       | 235   | mV                     |

| 高摆幅模式                   |                     | 寄存器0x2A5[0] = 1                               | 341   |       | 394   | mV                     |

| 输出失调电压                  | Vos                 |                                               | 1.19  |       | 1.27  | V                      |

| 确定延迟                    |                     |                                               |       |       |       |                        |

| 固定                      |                     |                                               |       |       | 17    | PClock <sup>3</sup> 周期 |

| 可变                      |                     |                                               |       |       | 2     | PClock <sup>3</sup> 周期 |

| SYSREF±至局部多帧计数器(LMFC)延迟 |                     |                                               |       | 4     |       | DAC时钟周期                |

<sup>1</sup> 在交流耦合电容的输入侧测量。

<sup>&</sup>lt;sup>2</sup> IEEE标准1596.3 LVDS兼容。

<sup>&</sup>lt;sup>3</sup> PClock为AD9135/AD9136内部处理时钟,等于通道速率÷40。

#### 交流规格

除非另有说明,AVDD33 = 3.3 V,SIOVDD33 = 3.3 V,IOVDD = 1.8 V,DVDD12 = 1.2 V,CVDD12 = 1.2 V,PVDD12 = 1.2 V,SVDD12 = 1.2 V, $T_A = 25$ °C, $T_{OUTFS} = 20 \text{ mA}$ 。

#### 表9.

| 衣3.                                                     |                             |     |         |        |

|---------------------------------------------------------|-----------------------------|-----|---------|--------|

| 参数                                                      | 测试条件/注释                     | 最小值 | 典型值 最大化 | 直 单位   |

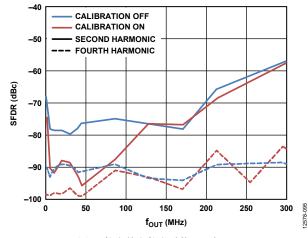

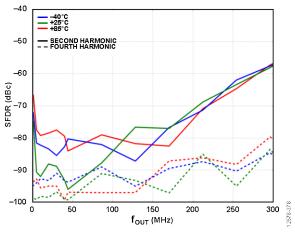

| 无杂散动态范围(SFDR)                                           | -9 dBFS单音                   |     |         |        |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | f <sub>OUT</sub> = 20 MHz   | 8   | 82      | dBc    |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | $f_{OUT} = 150 \text{ MHz}$ | 7   | 76      | dBc    |

| $f_{DAC} = 1966.08 \text{ MSPS}$                        | f <sub>OUT</sub> = 20 MHz   | 3   | 81      | dBc    |

| $f_{DAC} = 1966.08 \text{ MSPS}$                        | f <sub>OUT</sub> = 170 MHz  | 6   | 69      | dBc    |

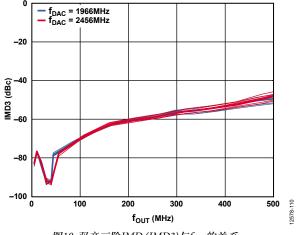

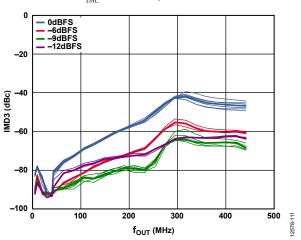

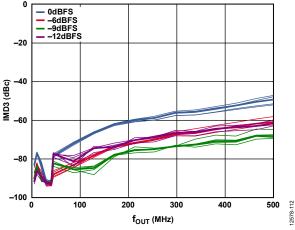

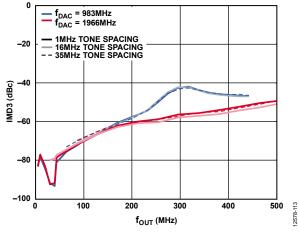

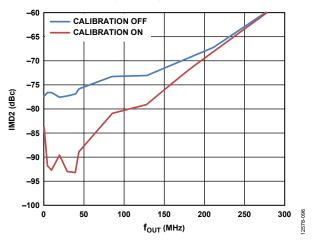

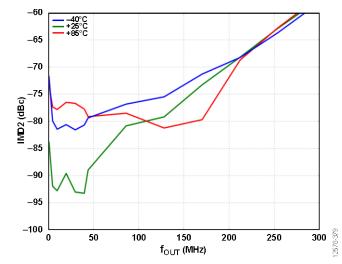

| 双音交调失真(IMD)                                             | −9 dBFS                     |     |         |        |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | f <sub>OUT</sub> = 20 MHz   | 9   | 90      | dBc    |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | f <sub>оит</sub> = 150 MHz  | 8   | 82      | dBc    |

| $f_{DAC} = 1966.08 \text{ MSPS}$                        | f <sub>OUT</sub> = 20 MHz   | 9   | 90      | dBc    |

| $f_{DAC} = 1966.08 \text{ MSPS}$                        | f <sub>OUT</sub> = 170 MHz  | 8   | 81      | dBc    |

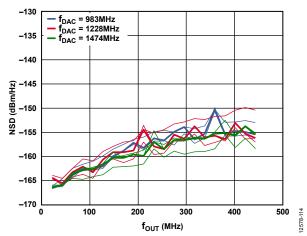

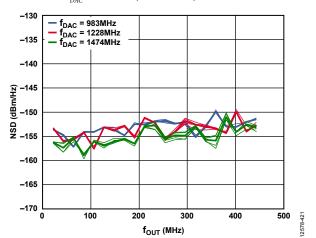

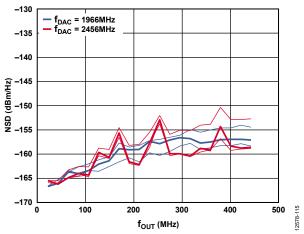

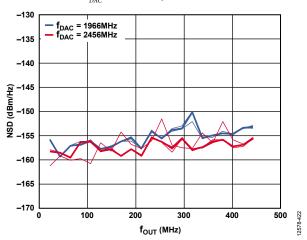

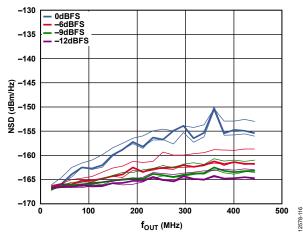

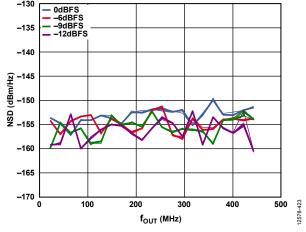

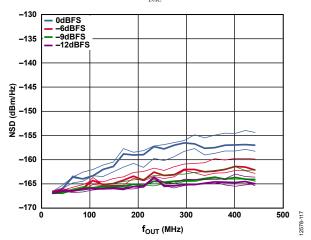

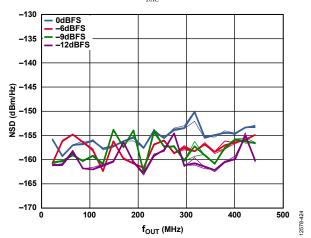

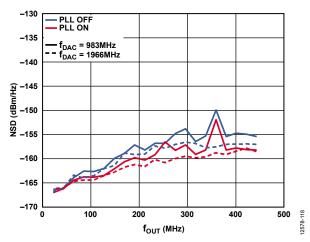

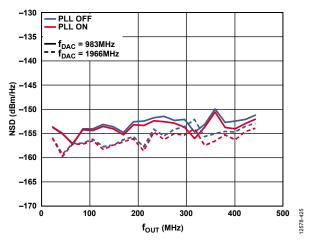

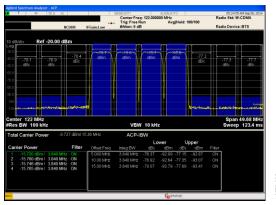

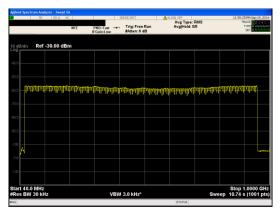

| 噪声谱密度(NSD), 单音                                          | 0 dBFS                      |     |         |        |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | $f_{OUT} = 150 \text{ MHz}$ | -   | -162    | dBm/Hz |

| $f_{DAC} = 1966.08 \text{ MSPS}$                        | f <sub>оит</sub> = 150 MHz  | -   | –163    | dBm/Hz |

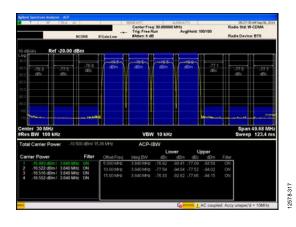

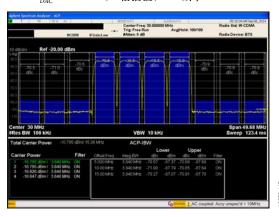

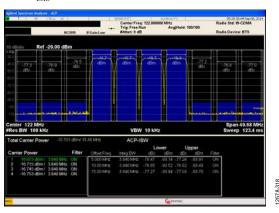

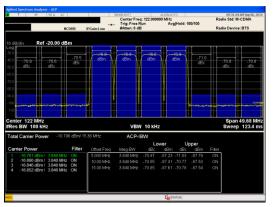

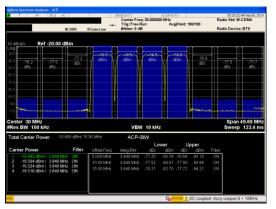

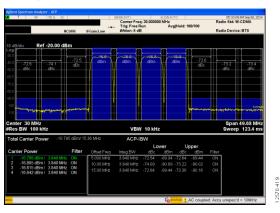

| W-CDMA第一邻道泄漏比(ACLR),单载波<br>RATIO (ACLR), SINGLE CARRIER | 0 dBFS                      |     |         |        |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | f <sub>OUT</sub> = 30 MHz   | 8   | 82      | dBc    |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | f <sub>оит</sub> = 150 MHz  | 8   | 80      | dBc    |

| $f_{DAC} = 1966.08 MSPS$                                | f <sub>оит</sub> = 150 MHz  | 8   | 80      | dBc    |

| W-CDMA第二邻道泄漏比(ACLR), 单载波                                | 0 dBFS                      |     |         |        |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | f <sub>OUT</sub> = 30 MHz   | 8   | 84      | dBc    |

| $f_{DAC} = 983.04 \text{ MSPS}$                         | f <sub>оит</sub> = 150 MHz  | 8   | 85      | dBc    |

| $f_{DAC} = 1966.08 \text{ MSPS}$                        | $f_{OUT} = 150 \text{ MHz}$ | 8   | 85      | dBc    |

<sup>&</sup>lt;sup>1</sup> 对于表9中的所有f<sub>DAC</sub> = 1966.08 MSPS条件,SVDD12 = 1.3 V。

## 绝对最大额定值

#### 表10.

| 1X 10.                      |                         |

|-----------------------------|-------------------------|

| 参数                          | 额定值                     |

| l120至地                      | -0.3 V至AVDD33 + 0.3 V   |

| SERDINx±、VTT、SYNCOUT1±/     | -0.3 V至SIOVDD33 + 0.3 V |

| SYNCOUT0±、TXENx             |                         |

| OUTx±                       | −0.3 V至AVDD33 + 0.3 V   |

| SYSREF±                     | GND - 0.5 V至+2.5 V      |

| CLK±至地                      | −0.3 V至PVDD12 + 0.3 V   |

| RESET, IRQ, CS, SCLK, SDIO, | -0.3 V至IOVDD + 0.3 V    |

| SDO至地                       |                         |

| LDO_BYP1                    | -0.3 V至SVDD12 + 0.3 V   |

| LDO_BYP2                    | -0.3 V至PVDD12 + 0.3 V   |

| LDO24                       | −0.3 V至AVDD33 + 0.3 V   |

| 工作环境温度(T <sub>4</sub> )     | −40°C至+85°C             |

| 结温                          | 125°C                   |

| 存储温度范围                      | -65°C至+150°C            |

注意,等于或超出上述绝对最大额定值可能会导致产品永久性损坏。这只是额定最值,并不能以这些条件或者在任何其它超出本技术规范操作章节中所示规格的条件下,推断产品能否正常工作。长期在超出最大额定值条件下工作会影响产品的可靠性。

#### 热阻

88引脚LFCSP封装的裸露焊盘(EPAD)必须焊接到接地层。 EPAD提供到电路板的电气、热和机械连接。

$\theta_{JA}$ 、 $\theta_{JB}$ 和 $\theta_{JC}$ 典型值的测试条件为4层JESD51-7高效导热测试板和有引脚表贴封装。 $\theta_{JA}$ 在静止空气条件下获得(JESD51-2)。气流可增强散热,从而有效降低 $\theta_{JA}$ 。 $\theta_{JB}$ 在双环冷板测试条件下获得(JESD51-8)。测量 $\theta_{JC}$ 时,在裸露焊盘底部监控测试外壳温度。

$\Psi_{\Pi}$ 和 $\Psi_{\Pi}$ 是热特性参数,利用静止空气条件下的 $\theta_{IA}$ 获得。

结温(T,)可利用下式估算:

$$T_J = T_T + (\Psi_{JT} \times P)$$

或者

$$T_J = T_B + (\Psi_{JB} \times P)$$

其中:

$T_{\tau}$ 是在封装顶部测得的温度。

P是器件总功耗。

$T_{R}$ 是在电路板测得的温度。

#### 表11. 热阻

| 封装                      | θја  | θјв  | θιс  | Ψл  | $\Psi_{JB}$ | 单位   |

|-------------------------|------|------|------|-----|-------------|------|

| 88引脚 LFCSP <sup>1</sup> | 22.6 | 5.59 | 1.17 | 0.1 | 5.22        | °C/W |

<sup>1</sup> 裸露焊盘必须牢固连接到接地层。

### ESD警告

#### ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。 尽管本产品具有专利或专有保护电路,但在遇到高 能量ESD时,器件可能会损坏。因此,应当采取适当 的ESD防范措施,以避免器件性能下降或功能丧失。

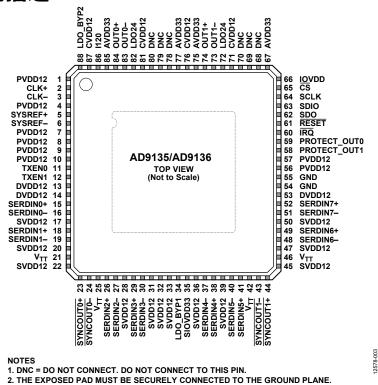

## 引脚配置和功能描述

图3. 引脚配置

表12. 引脚功能描述

| 引脚编号 | 引脚名称     | 说明                                                                  |

|------|----------|---------------------------------------------------------------------|

| 1    | PVDD12   | 1.2 V电源。PVDD12提供干净的电源。                                              |

| 2    | CLK+     | PLL参考/时钟输入(+)。使用PLL时,这是参考时钟正输入。不使用PLL时,这是器件时钟正输入。                   |

|      |          | 此引脚自偏置,必须交流耦合。                                                      |

| 3    | CLK-     | PLL参考/时钟输入(-)。使用PLL时,这是参考时钟负输入。不使用PLL时,这是器件时钟负输入。                   |

|      |          | 此引脚自偏置,必须交流耦合。                                                      |

| 4    | PVDD12   | 1.2 V电源。PVDD12提供干净的电源。                                              |

| 5    | SYSREF+  | 确定延迟的正参考时钟。此引脚自偏置,支持交流耦合。它既可采用交流耦合,也可采用直流耦合。                        |

| 6    | SYSREF—  | 确定延迟的负参考时钟。此引脚自偏置,支持交流耦合。它既可采用交流耦合,也可采用直流耦合。                        |

| 7    | PVDD12   | 1.2 V电源。PVDD12提供干净的电源。                                              |

| 8    | PVDD12   | 1.2 V电源。PVDD12提供干净的电源。                                              |

| 9    | PVDD12   | 1.2 V电源。PVDD12提供干净的电源。                                              |

| 10   | PVDD12   | 1.2 V电源。PVDD12提供干净的电源。                                              |

| 11   | TXEN0    | DAC0的发射使能。CMOS电平相对于IOVDD确定。                                         |

| 12   | TXEN1    | DAC1的发射使能。CMOS电平相对于IOVDD确定。                                         |

| 13   | DVDD12   | 1.2 V数字电源。                                                          |

| 14   | DVDD12   | 1.2 V数字电源。                                                          |

| 15   | SERDIN0+ | 串行通道输入0 (+)。CML兼容。SERDIN0+使用校准的50 Ω电阻内部端接到V <sub></sub> 引脚电压。此引脚只能  |

|      |          | 交流耦合。                                                               |

| 16   | SERDINO- | 串行通道输入0 (–)。CML兼容。SERDIN0-使用校准的50 Ω电阻内部端接到Vπ引脚电压。此引脚只能              |

|      |          | 交流耦合。                                                               |

| 17   | SVDD12   | 1.2 V JESD204B接收器电源。                                                |

| 18   | SERDIN1+ | 串行通道输入1(+)。CML兼容。SERDIN1+使用校准的50Ω电阻内部端接到Vπ引脚电压。此引脚只能                |

|      |          | 交流耦合。                                                               |

| 19   | SERDIN1- | 串行通道输入1 (-)。CML兼容。SERDIN1-使用校准的50 Ω电阻内部端接到V <sub>Π</sub> 引脚电压。此引脚只能 |

| -    |          | 交流耦合。                                                               |

| 引脚编号     | 引脚名称               | 说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20       | SVDD12             | 1.2 V JESD204B接收器电源。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21       | V <sub>TT</sub>    | 1.2 V端接电压。将V <sub>T</sub> 连接到SVDD12电源引脚。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 22       | SVDD12             | 1.2 V JESD204B接收器电源。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23       | SYNCOUT0+          | 正LVDS同步(低电平有效)输出信号通道链路0。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 24       | SYNCOUT0-          | 负LVDS同步(低电平有效)输出信号通道链路0。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25       | V <sub>TT</sub>    | 1.2 V端接电压。将V <sub>T</sub> 连接到SVDD12电源引脚。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 26       | SERDIN2+           | 串行通道输入2 (+)。CML兼容。SERDIN2+使用校准的50 Ω电阻内部端接到V <sub>T</sub> 引脚电压。此引脚只能<br>交流耦合。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 27       | SERDIN2-           | 串行通道输入2 (-)。CML兼容。SERDIN2-使用校准的50 Ω电阻内部端接到V <sub>π</sub> 引脚电压。此引脚只能<br>交流耦合。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 28       | SVDD12             | 1.2 V JESD204B接收器电源。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 29       | SERDIN3+           | 串行通道输入3 (+)。CML兼容。SERDIN3+使用校准的50 Ω电阻内部端接到V <sub>T</sub> 引脚电压。此引脚只能<br>交流耦合。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 30       | SERDIN3-           | 串行通道输入3 (¬)。CML兼容。SERDIN3-使用校准的50 Ω电阻内部端接到V <sub>π</sub> 引脚电压。此引脚只能<br>交流耦合。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 31       | SVDD12             | 1.2 V JESD204B接收器电源。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 32       | SVDD12             | 1.2 V JESD204B接收器电源。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 33       | SVDD12             | 1.2 V JESD204B接收器电源。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 34       | LDO_BYP1           | LDO SERDES旁路。此引脚需要一个1 Ω电阻与一个1 μF电容串联接地。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

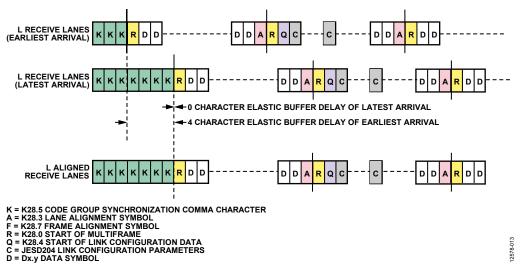

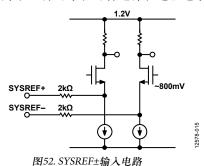

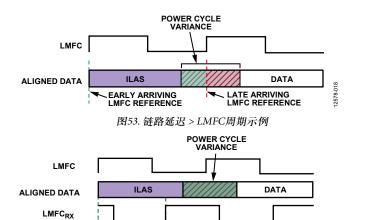

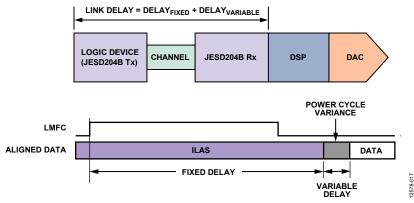

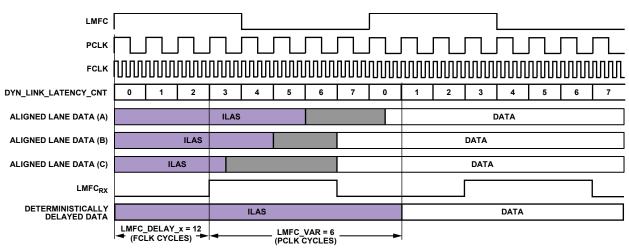

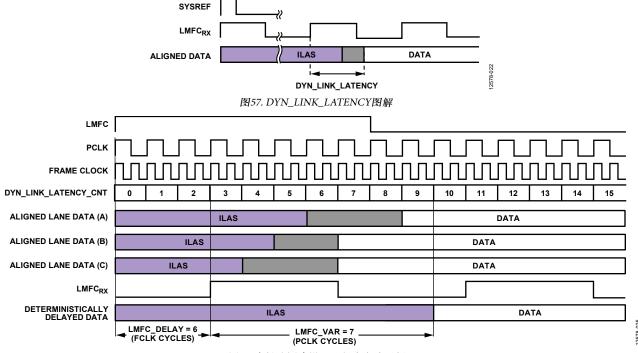

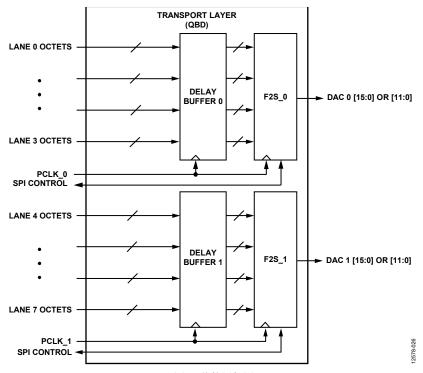

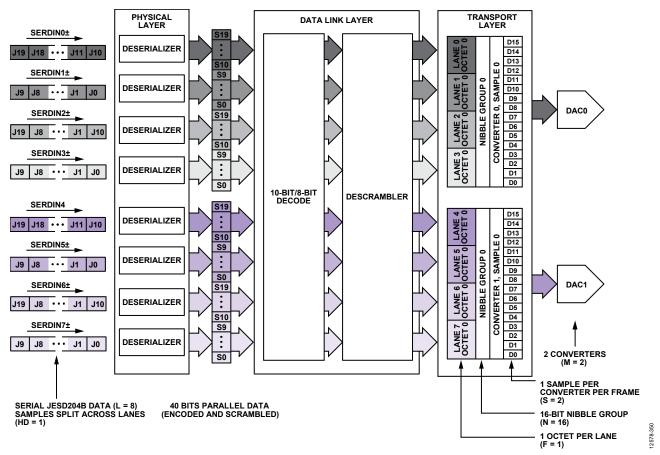

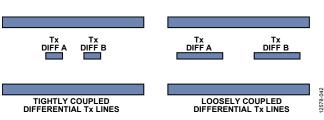

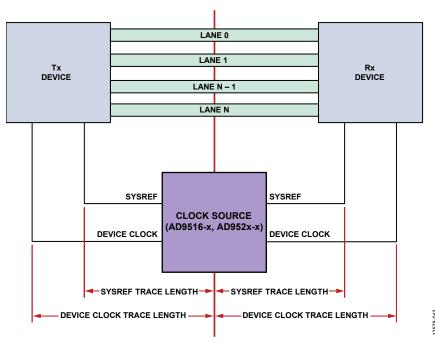

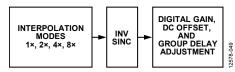

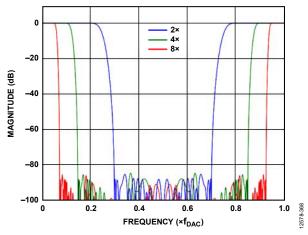

| 35       | SIOVDD33           | 3.3 V SERDES电源。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |