# **ANALOG** 16-Channel DAS with 14-Bit, Bipolar Input, Dual Simultaneous Sempling ADS **Dual Simultaneous Sampling ADC**

**Data Sheet**

#### **FEATURES**

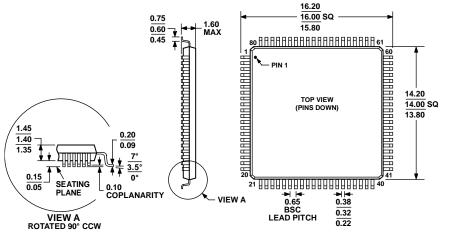

16-channel, dual, simultaneously sampled inputs Independently selectable channel input ranges True bipolar: ±10 V, ±5 V, ±2.5 V Single 5 V analog supply and 2.3 V to 3.6 V VDRIVE supply Fully integrated data acquisition solution Analog input clamp protection Input buffer with 1 M $\Omega$  analog input impedance First-order antialiasing analog filter On-chip accurate reference and reference buffer **Dual 14-bit SAR ADC** Throughput rate: 2×1 MSPS per channel pair Oversampling capability with digital filter Flexible sequencer with burst mode Flexible parallel/serial interface SPI/QSPI/MICROWIRE/DSP compatible **Optional CRC error checking** Hardware/software configuration Performance 85.3 dB typical SNR at 500 kSPS (2× oversampling) 85 dB typical SNR at 1 MSPS -103 dB typical THD at ±10 V range ±0.3 LSB INL (typical), ±0.99 LSB DNL (maximum) 8 kV ESD analog input pins only **On-chip self detect function** 80-lead LQFP package

#### **APPLICATIONS**

**Power line monitoring Protective relays Multiphase motor control** Instrumentation and control systems Data acquisition systems (DASs)

#### **GENERAL DESCRIPTION**

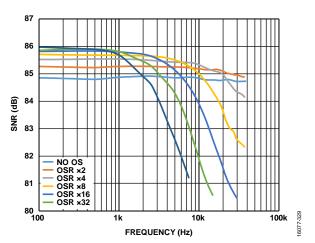

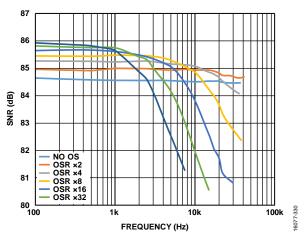

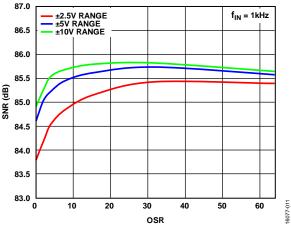

The AD7617 is a 14-bit, DAS that supports dual simultaneous sampling of 16 channels. The AD7617 operates from a single +5 V supply and can accommodate  $\pm 10$  V,  $\pm 5$  V, and  $\pm 2.5$  V true bipolar input signals while sampling at throughput rates up to 1 MSPS per channel pair with 85 dB signal-to-noise ratio (SNR). Higher SNR performance can be achieved with the on-chip oversampling mode (85.3 dB for an oversampling ratio (OSR) of 2).

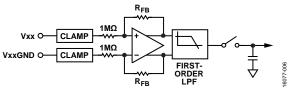

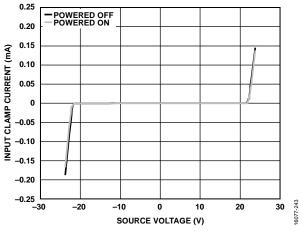

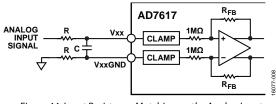

The input clamp protection circuitry can tolerate voltages up to  $\pm 21$  V. The AD7617 has 1 M $\Omega$  analog input impedance, regardless of sampling frequency. The single-supply operation, on-chip filtering, and high input impedance eliminate the need for driver op amps and external bipolar supplies.

The device contains analog input clamp protection, a dual, 14-bit charge redistribution successive approximation register (SAR) analog-to-digital converter (ADC), a flexible digital filter, a 2.5 V reference and reference buffer, and high speed serial and parallel interfaces. The AD7617 is serial peripheral interface (SPI)/QSPI<sup>™</sup>/DSP/MICROWIRE compatible.

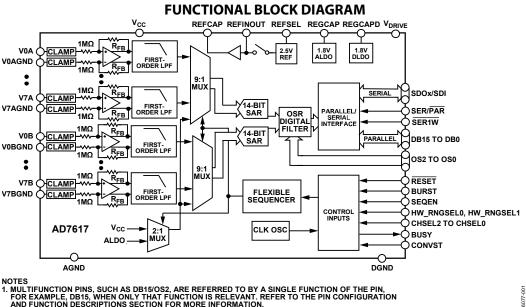

1. MULTIFUNCTION PINS, SUCH AS DB15/0S2, ARE REFERRED TO BY A SINGLE FUNCTION OF THE PIN, FOR EXAMPLE, DB15, WHEN ONLY THAT FUNCTION IS RELEVANT. REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONS SECTION FOR MORE INFORMATION.

Figure 1. AD7617 Functional Block Diagram

**Document Feedback** Rev. 0 Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

# **AD7617\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 08/04/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

AD7616/AD7616-P Evaluation Board

### **DOCUMENTATION**

#### **Application Notes**

- AN-1409: Achieving Pseudosimultaneous Sampling by Using the AD7616 Flexible Sequencer and Burst Mode

- AN-1416: Setup Example for Configuring the AD7616 for High Dynamic Range Applications

#### **Data Sheet**

• AD7617: 16-Channel DAS with 14-Bit, Bipolar Input, Dual Simultaneous Sampling ADC Data Sheet

#### **User Guides**

• UG-1012: Evaluating the AD7616/AD7616-P 16-Channel DAS with 16-Bit, Bipolar Input, Dual Simultaneous Sampling ADC

### SOFTWARE AND SYSTEMS REQUIREMENTS

AD7616 No-OS/HDL Drivers

### TOOLS AND SIMULATIONS $\Box$

AD7616/AD7617 IBIS Model

### DESIGN RESOURCES

- AD7617 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all AD7617 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# TABLE OF CONTENTS

| Features 1                                    |

|-----------------------------------------------|

| Applications1                                 |

| General Description 1                         |

| Functional Block Diagram 1                    |

| Revision History 2                            |

| Specifications                                |

| Timing Specifications6                        |

| Absolute Maximum Ratings10                    |

| Thermal Resistance10                          |

| ESD Caution10                                 |

| Pin Configuration and Function Descriptions11 |

| Typical Performance Characteristics 15        |

| Terminology                                   |

| Theory of Operation                           |

| Converter Details                             |

| Analog Input23                                |

| ADC Transfer Function24                       |

| Internal/External Reference                   |

| Shutdown Mode25                               |

| Digital Filter                                |

| Applications Information                      |

| Functionality Overview                        |

| Power Supplies                                |

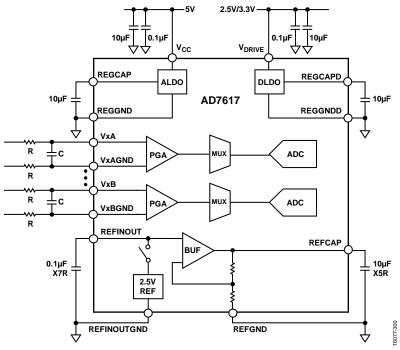

| Typical Connections                           |

| Device Configuration                          |

| Operational Mode28                            |

| Internal/External Reference                   |

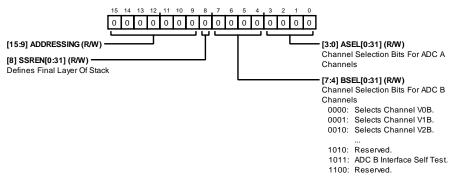

### Register Summary ...... 41 Configuration Register ...... 43 Channel Register ...... 44 Input Range Registers ...... 45 Sequencer Stack Registers ...... 49 Status Register ...... 50 Ordering Guide ..... 51

#### **REVISION HISTORY**

7/2017—Revision 0: Initial Version

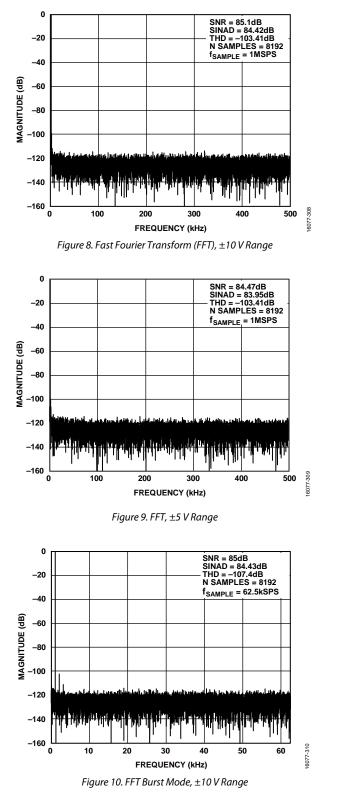

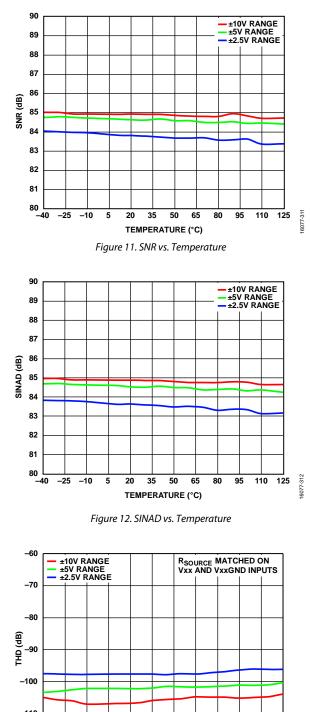

## **SPECIFICATIONS**

$V_{REF} = 2.5 \text{ V}$  external/internal,  $V_{CC} = 4.75 \text{ V}$  to 5.25 V,  $V_{DRIVE} = 2.3 \text{ V}$  to 3.6 V, sampling frequency ( $f_{SAMPLE}$ ) = 1 MSPS,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted.

#### Table 1.

| Parameter                                           | Test Conditions/Comments                                         | Min  | Тур   | Max   | Unit             |

|-----------------------------------------------------|------------------------------------------------------------------|------|-------|-------|------------------|

| DYNAMIC PERFORMANCE                                 | $f_{IN} = 1$ kHz sine wave, unless otherwise                     |      |       |       |                  |

|                                                     | noted                                                            |      |       |       |                  |

| Signal-to-Noise Ratio (SNR) <sup>1, 2</sup>         | No oversampling, ±10 V range                                     | 84.5 | 85    |       | dB               |

|                                                     | $OSR = 2, \pm 10 V range$ , <sup>3</sup> $f_{SAMPLE} = 500 kSPS$ |      | 85.3  |       | dB               |

|                                                     | $OSR = 4, \pm 10 V range^{3}$                                    |      | 85.5  |       | dB               |

|                                                     | No oversampling, ±5 V range                                      | 84   | 84.5  |       | dB               |

|                                                     | No oversampling, ±2.5 V range                                    | 83   | 83.5  |       | dB               |

| Signal-to-Noise-and-Distortion (SINAD) <sup>1</sup> | No oversampling, ±10 V range                                     | 84   | 84.5  |       | dB               |

|                                                     | No oversampling, ±5 V range                                      | 83.5 | 84    |       | dB               |

|                                                     | No oversampling, ±2.5 V range                                    | 82.5 | 83.5  |       | dB               |

| Dynamic Range                                       | No oversampling, ±10 V range                                     |      | 85.5  |       | dB               |

|                                                     | No oversampling, ±5 V range                                      |      | 85.1  |       | dB               |

|                                                     | No oversampling, ±2.5 V range                                    |      | 84.5  |       | dB               |

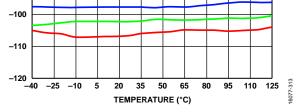

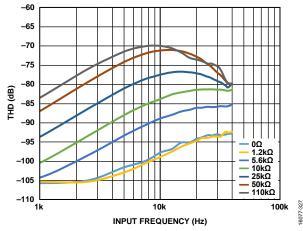

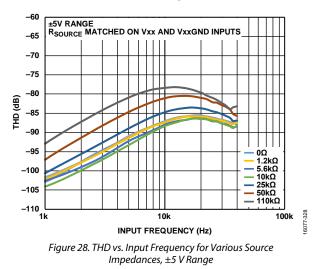

| Total Harmonic Distortion (THD) <sup>1</sup>        | No oversampling, ±10 V range                                     |      | -103  | -93.5 | dB               |

|                                                     | No oversampling, ±5 V range                                      |      | -100  |       | dB               |

|                                                     | No oversampling, $\pm 2.5$ V range                               |      | -97   |       | dB               |

| Peak Harmonic or Spurious Noise <sup>1</sup>        | ······································                           |      | -103  |       | dB               |

| Intermodulation Distortion (IMD) <sup>1</sup>       | fa = 1 kHz, fb = 1.1 kHz                                         |      |       |       |                  |

| Second-Order Terms                                  |                                                                  |      | -105  |       | dB               |

| Third-Order Terms                                   |                                                                  |      | -113  |       | dB               |

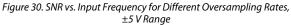

| Channel to Channel Isolation <sup>1</sup>           | f <sub>™</sub> on unselected channels up to 5 kHz                |      | -106  |       | dB               |

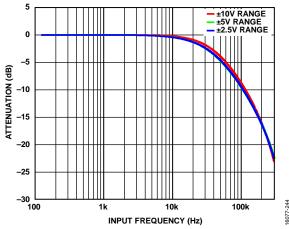

| ANALOG INPUT FILTER                                 |                                                                  |      | -100  |       | ub               |

| Full Power Bandwidth                                | $2 dP \pm 10 V range$                                            |      | 39    |       | kHz              |

|                                                     | $-3 \text{ dB}, \pm 10 \text{ V}$ range                          |      |       |       | kHz              |

|                                                     | $-3  dB, \pm 5  V/+2.5  V$ range                                 |      | 33    |       |                  |

|                                                     | -0.1 dB                                                          |      | 5.5   |       | kHz              |

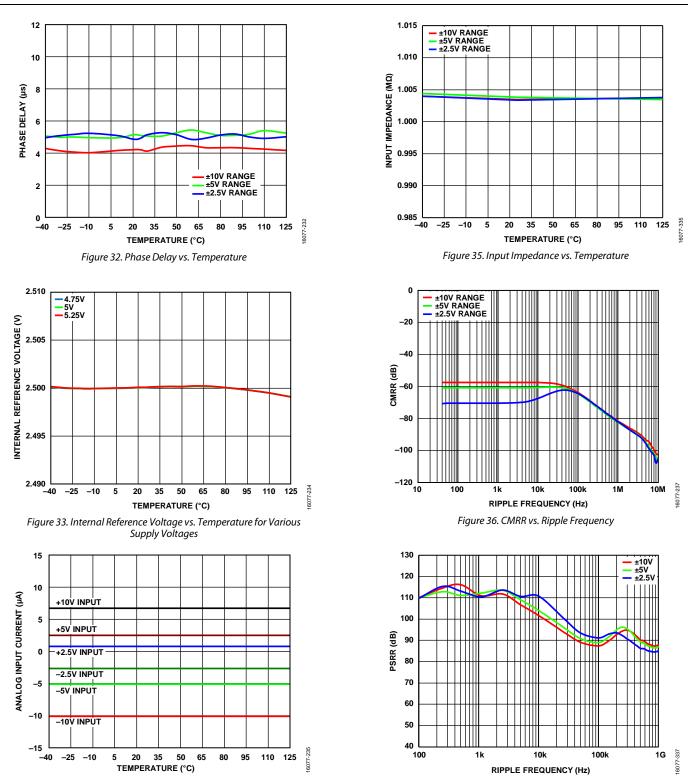

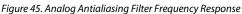

| Phase Delay <sup>1, 3</sup>                         | ±10 V range                                                      |      | 4.4   | 6     | μs               |

|                                                     | ±5V range                                                        |      | 5     |       | μs               |

|                                                     | ±2.5 V range                                                     |      | 4.9   | _     | μs               |

| Drift <sup>1, 3</sup>                               | ±10 V range                                                      |      | ±0.55 | +5    | ns/°C            |

| Matching (Dual Simultaneous Pair) <sup>1, 3</sup>   | ±10 V range                                                      |      | 4.4   | 100   | ns               |

|                                                     | ±5 V range                                                       |      | 4.7   |       | ns               |

|                                                     | ±2.5 V range                                                     |      | 4.1   |       | ns               |

| DC ACCURACY                                         |                                                                  |      |       |       |                  |

| Resolution                                          | No missing codes                                                 | 14   |       |       | Bits             |

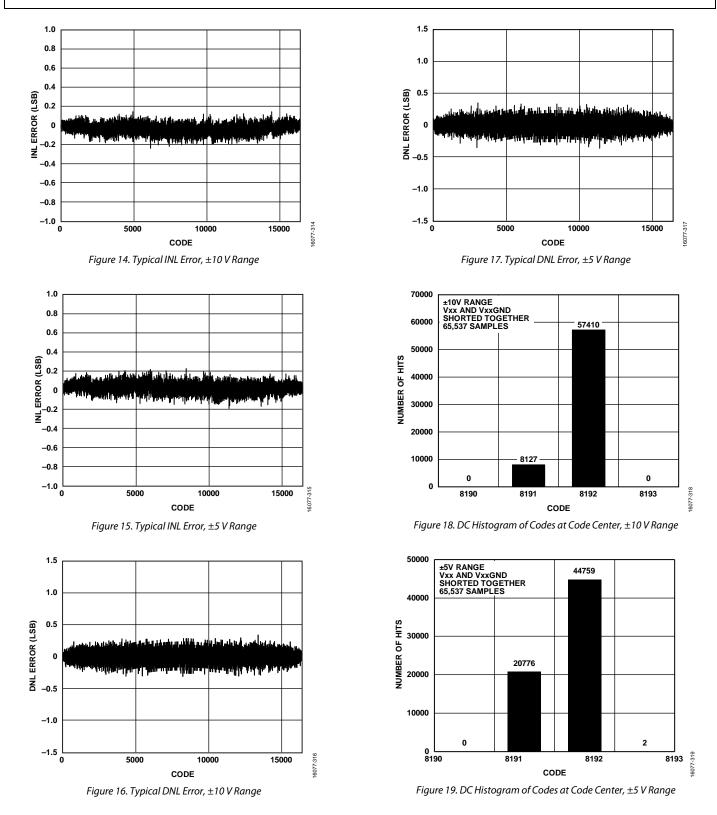

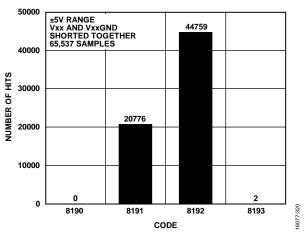

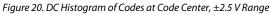

| Differential Nonlinearity (DNL) <sup>1</sup>        |                                                                  |      | ±0.1  | ±0.99 | LSB <sup>4</sup> |

| Integral Nonlinearity (INL) <sup>1</sup>            |                                                                  |      | ±0.3  | ±1    | LSB              |

| Total Unadjusted Error (TUE)                        | ±10 V range                                                      |      | ±1.5  |       | LSB              |

|                                                     | ±5 V range                                                       |      | ±2    |       | LSB              |

|                                                     | ±2.5 V range                                                     |      | ±2.5  |       | LSB              |

| Positive Full-Scale Error (PFS) <sup>5</sup>        |                                                                  |      |       |       |                  |

| External Reference                                  | ±10 V range                                                      |      | ±1.25 | ±8    | LSB              |

|                                                     | ±5 V range                                                       |      | ±1    |       | LSB              |

|                                                     | ±2.5 V range                                                     |      | ± 0.5 |       | LSB              |

| Internal Reference                                  |                                                                  |      | _ 0.5 |       | 250              |

|                                                     | ±10 V range                                                      |      | ±1.25 |       | LSB              |

|                                                     | ±10 v lange                                                      |      | 1.23  |       | LOD              |

| Parameter                                         | Test Conditions/Comments                                                       | Min   | Тур   | Max       | Unit   |

|---------------------------------------------------|--------------------------------------------------------------------------------|-------|-------|-----------|--------|

| Drift <sup>3</sup>                                | External reference                                                             |       | ±2    | ±5        | ppm/°C |

|                                                   | Internal reference                                                             |       | ±3    | ±10       | ppm/°C |

| Matching <sup>1</sup>                             | ±10 V range                                                                    |       | 1     | 3         | LSB    |

|                                                   | ±5 V range                                                                     |       | 1     |           | LSB    |

|                                                   | ±2.5 V range                                                                   |       | 1     |           | LSB    |

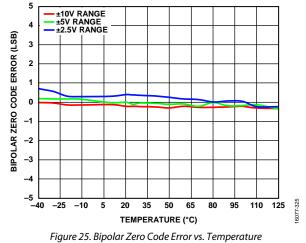

| Bipolar Zero Code Error <sup>1</sup>              | ±10 V range                                                                    |       | ±0.15 | ±2.5      | LSB    |

|                                                   | ±5 V range                                                                     |       | ±0.2  | ±2.5      | LSB    |

|                                                   | ±2.5 V range                                                                   |       | ±0.7  | ±3.5      | LSB    |

| Drift <sup>3</sup>                                | ±10 V range                                                                    |       | ±1.5  | ±21       | μV/°C  |

|                                                   | ±5 V range                                                                     |       | ±1    |           | μV/°C  |

|                                                   | ±2.5 V range                                                                   |       | ±0.5  |           | µV/°C  |

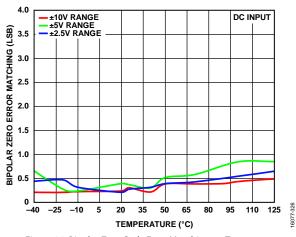

| Matching <sup>1</sup>                             | ±10 V range                                                                    |       | ±0.5  | ±2.5      | LSB    |

| -                                                 | ±5 V range                                                                     |       | ±0.75 |           | LSB    |

|                                                   | ±2.5 V range                                                                   |       | ±0.75 |           | LSB    |

| Negative Full-Scale (NFS) Error <sup>1, 5</sup>   | External reference                                                             |       |       |           |        |

| -                                                 | ±10 V range                                                                    |       | ±1    | ±8        | LSB    |

|                                                   | ±5 V range                                                                     |       | ±0.75 |           | LSB    |

|                                                   | ±2.5 V range                                                                   |       | ±1.5  |           | LSB    |

|                                                   | Internal reference                                                             |       |       |           |        |

|                                                   | ±10 V range                                                                    |       | ±1    |           | LSB    |

| Drift <sup>3</sup>                                | External reference                                                             |       | ±2    | ±5        | ppm/°C |

|                                                   | Internal reference                                                             |       | ±4    | ±10       | ppm/°C |

| Matching <sup>1</sup>                             | ±10 V range                                                                    |       | 1     | 3         | LSB    |

|                                                   | ±5 V range                                                                     |       | 1     |           | LSB    |

|                                                   | ±2.5 V range                                                                   |       | 2     |           | LSB    |

| ANALOG INPUT                                      |                                                                                |       |       |           |        |

| Input Voltage Ranges                              | Software/hardware selectable, ±10 V range                                      |       |       | ±10       | V      |

|                                                   | Software/hardware selectable, ±5 V range                                       |       |       | ±5        | V      |

|                                                   | Software/hardware selectable, ±2.5 V range                                     |       |       | ±2.5      | V      |

| Analog Input Current                              | ±10 V range, see Figure 34                                                     |       | ±10.5 |           | μA     |

| 5 1                                               | ±5 V range, see Figure 34                                                      |       | ±6.5  |           | μA     |

|                                                   | ±2.5 V range, see Figure 34                                                    |       | ±4    |           | μA     |

| Input Capacitance <sup>6</sup>                    |                                                                                |       | 10    |           | pF     |

| Input Impedance                                   | See the Analog Input section                                                   | 0.85  | 1     |           | MΩ     |

| Input Impedance Drift <sup>3</sup>                |                                                                                |       |       | 25        | ppm/°C |

| REFERENCE INPUT/OUTPUT                            |                                                                                |       |       | -         |        |

| Reference Input Voltage Range                     | See the ADC Transfer Function section                                          | 2.495 | 2.5   | 2.505     | V      |

| DC Leakage Current                                |                                                                                |       |       | ±1        | μA     |

| Input Capacitance <sup>6</sup>                    | REFSEL = 1                                                                     |       | 7.5   |           | pF     |

| Reference Output Voltage                          | Measured at REFINOUT                                                           | 2.495 |       | 2.505     | V      |

| Reference Temperature Coefficient <sup>3</sup>    |                                                                                |       | ±2    | ±15       | ppm/°C |

| LOGIC INPUTS                                      |                                                                                |       |       |           | pp, c  |

| Input Voltage                                     |                                                                                |       |       |           |        |

| High (VINH)                                       | $V_{DRIVE} = 2.7 V \text{ to } 3.6 V$                                          | 2     |       |           | v      |

|                                                   | $V_{DRVE} = 2.3 V \text{ to } 3.0 V$<br>$V_{DRVE} = 2.3 V \text{ to } 2.7 V$   | 1.7   |       |           | v      |

| Low (V <sub>INL</sub> )                           | $V_{DRIVE} = 2.7 V \text{ to } 3.6 V$                                          |       |       | 0.8       | v      |

|                                                   | $V_{DRIVE} = 2.3 V \text{ to } 3.0 V$<br>$V_{DRIVE} = 2.3 V \text{ to } 2.7 V$ |       |       | 0.8       | v      |

| Input Current (I <sub>IN</sub> )                  |                                                                                |       |       | 0.7<br>±1 | μA     |

| Input Capacitance (C <sub>IN</sub> ) <sup>6</sup> |                                                                                |       | 5     | <u> </u>  | рF     |

|                                                   |                                                                                |       | J     |           | Pi     |

| Parameter                                      | Test Conditions/Comments                     | Min                      | Тур    | Max  | Unit |

|------------------------------------------------|----------------------------------------------|--------------------------|--------|------|------|

| LOGIC OUTPUTS                                  |                                              |                          |        |      |      |

| Output Voltage                                 |                                              |                          |        |      |      |

| High (V <sub>он</sub> )                        | $I_{SOURCE} = 100 \ \mu A$                   | $V_{\text{DRIVE}} - 0.2$ |        |      | V    |

| Low (V <sub>OL</sub> )                         | I <sub>SINK</sub> = 100 μA                   |                          |        | 0.4  | V    |

| Floating State Leakage Current                 |                                              |                          | ±0.005 | ±1   | μA   |

| Floating State Output Capacitance <sup>6</sup> |                                              |                          | 5      |      | pF   |

| Output Coding                                  | Twos complement                              |                          |        |      |      |

| CONVERSION RATE                                |                                              |                          |        |      |      |

| Conversion Time                                | Per channel pair                             |                          | 0.5    |      | μs   |

| Acquisition Time                               | Per channel pair                             |                          | 0.5    |      | μs   |

| Throughput Rate                                | Per channel pair                             |                          |        | 1    | MSPS |

| POWER REQUIREMENTS                             |                                              |                          |        |      |      |

| Vcc                                            |                                              | 4.75                     |        | 5.25 | V    |

| VDRIVE                                         |                                              | 2.3                      |        | 3.6  | V    |

| lvcc                                           |                                              |                          |        |      |      |

| Normal Mode                                    |                                              |                          |        |      |      |

| Static                                         |                                              |                          | 37     | 57   | mA   |

| Operational                                    | $f_{SAMPLE} = 1 MSPS$                        |                          | 42     | 65   | mA   |

| Shutdown Mode                                  |                                              |                          | 28     |      | μA   |

| Idrive                                         | Digital inputs = $0 V \text{ or } V_{DRIVE}$ |                          |        |      |      |

| Normal Mode                                    |                                              |                          |        |      |      |

| Static                                         |                                              |                          | 0.3    | 0.75 | mA   |

| Operational                                    | $f_{SAMPLE} = 1 MSPS$                        |                          | 2.4    | 3.2  | mA   |

| Shutdown Mode                                  |                                              |                          | 20     |      | μΑ   |

| Power Dissipation                              |                                              |                          |        |      |      |

| Normal Mode                                    |                                              |                          |        |      |      |

| Static                                         |                                              |                          | 185    | 300  | mW   |

| Operational                                    | $f_{SAMPLE} = 1 MSPS$                        |                          | 230    | 350  | mW   |

| Shutdown Mode                                  |                                              |                          | 0.25   |      | mW   |

<sup>1</sup> See the Terminology section.

<sup>2</sup> The user can achieve 85.3 dB SNR by enabling oversampling. The values are valid for manual mode. In burst mode, values degrade by ~1 dB.

<sup>3</sup> Not production tested. Sample tested during initial release to ensure compliance.

<sup>4</sup> LSB means least significant bit. With a ±2.5 V input range, 1 LSB = 305.175 µV. With a ±5 V input range, 1 LSB = 610.351 µV. With a ±10 V input range, 1 LSB = 1.220 mV.

<sup>5</sup> Positive and negative full-scale error for the internal reference excludes reference errors.

<sup>6</sup> Supported by simulation data.

#### TIMING SPECIFICATIONS

#### **Universal Timing Specifications**

$V_{CC} = 4.75 \text{ V}$  to 5.25 V,  $V_{DRIVE} = 2.3 \text{ V}$  to 3.6 V,  $V_{REF} = 2.5 \text{ V}$  external reference/internal reference,  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted. Interface timing tested using a load capacitance ( $C_{LOAD}$ ) of 30 pF, dependent on  $V_{DRIVE}$  and load capacitance for serial interface (see Table 15).

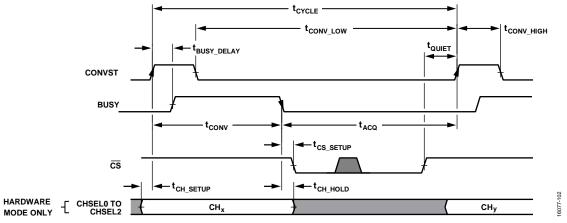

| Parameter <sup>1</sup>   | Min  | Тур | Max | Unit | Description                                                                                                     |

|--------------------------|------|-----|-----|------|-----------------------------------------------------------------------------------------------------------------|

| <b>t</b> cycle           | 1    |     |     | μs   | Minimum time between consecutive CONVST rising edges (excluding burst and                                       |

|                          |      |     |     | -    | oversampling modes)                                                                                             |

| t <sub>conv_low</sub>    | 50   |     |     | ns   | CONVST low pulse width                                                                                          |

| t <sub>CONV_HIGH</sub>   | 50   |     |     | ns   | CONVST high pulse width                                                                                         |

| tbusy_delay              |      |     | 32  | ns   | CONVST high to BUSY high (manual mode)                                                                          |

| tcs_setup                | 20   |     |     | ns   | BUSY falling edge to CS falling edge setup time                                                                 |

| tch_setup                | 50   |     |     | ns   | Channel select setup time in hardware mode for CHSELx                                                           |

| t <sub>CH_HOLD</sub>     | 20   |     |     | ns   | Channel select hold time in hardware mode for CHSELx                                                            |

| t <sub>conv</sub>        |      | 475 | 520 | ns   | Conversion time for the selected channel pair                                                                   |

| t <sub>ACQ</sub>         | 480  |     |     | ns   | Acquisition time for the selected channel pair                                                                  |

| tquiet                   | 50   |     |     | ns   | CS rising edge to next CONVST rising edge                                                                       |

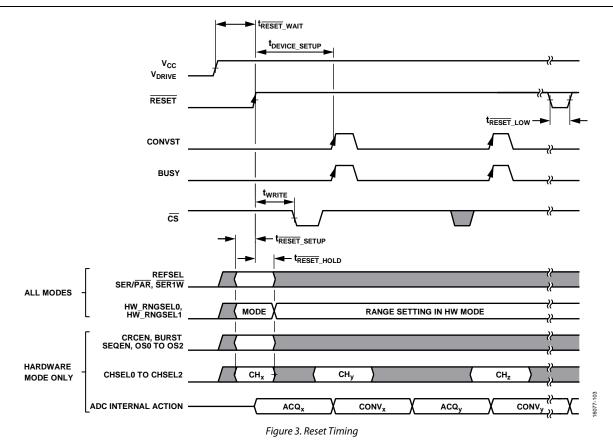

| t <sub>reset_low</sub>   |      |     |     |      |                                                                                                                 |

| Partial Reset            | 40   |     | 500 | ns   | Partial RESET low pulse width                                                                                   |

| Full Reset               | 1.2  |     |     | μs   | Full RESET low pulse width                                                                                      |

| tdevice_setup            |      |     |     |      |                                                                                                                 |

| Partial Reset            | 50   |     |     | ns   | Time between partial RESET high and CONVST rising edge                                                          |

| Full Reset               | 15   |     |     | ms   | Time between full RESET high and CONVST rising edge                                                             |

| twrite                   |      |     |     |      |                                                                                                                 |

| Partial Reset            | 50   |     |     | ns   | Time between partial RESET high and CS for write operation                                                      |

| Full Reset               | 240  |     |     | μs   | Time between full RESET high and CS for write operation                                                         |

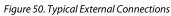

| t <sub>reset_wait</sub>  | 1    |     |     | ms   | Time between stable $V_{CC}/V_{DRIVE}$ and release of RESET (see Figure 51)                                     |

| t <sub>reset_setup</sub> |      |     |     |      | Time prior to release of RESET that queried hardware inputs must be stable for (see Figure 51)                  |

| Partial Reset            | 10   |     |     | ns   |                                                                                                                 |

| Full Reset               | 0.05 |     |     | ms   |                                                                                                                 |

| t <sub>reset_</sub> hold |      |     |     |      | Time after release of $\overline{\text{RESET}}$ that queried hardware inputs must be stable for (see Figure 51) |

| Partial Reset            | 10   |     |     | ns   |                                                                                                                 |

| Full Reset               | 0.24 |     |     | ms   |                                                                                                                 |

<sup>1</sup> Not production tested. Sample tested during initial release to ensure compliance.

Figure 2. Universal Timing Diagram Across All Interfaces

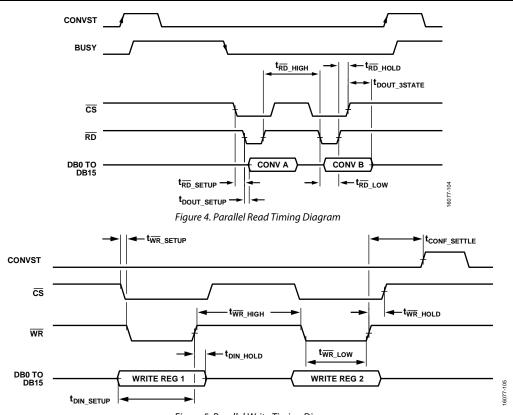

#### Parallel Mode Timing Specifications

| Table | . 2 |

|-------|-----|

| Lable | 23. |

| Parameter                | Min | Тур | Max | Unit | Description                                                          |

|--------------------------|-----|-----|-----|------|----------------------------------------------------------------------|

| t <sub>RD_SETUP</sub>    | 10  |     |     | ns   | CS falling edge to RD falling edge setup time                        |

| t <sub>rd_hold</sub>     | 10  |     |     | ns   | $\overline{RD}$ rising edge to $\overline{CS}$ rising edge hold time |

| t <sub>RD_</sub> HIGH    | 10  |     |     | ns   | RD high pulse width                                                  |

| t <sub>RD_LOW</sub>      | 30  |     |     | ns   | RD low pulse width                                                   |

| tdout_setup              |     |     | 30  | ns   | Data access time after falling edge of RD                            |

| tdout_3state             |     |     | 11  | ns   | CS rising edge to DBx high impedance                                 |

| twr_setup                | 10  |     |     | ns   | CS to WR setup time                                                  |

| t <sub>wr_</sub> high    | 20  |     |     | ns   | WR high pulse width                                                  |

| $t_{\overline{WR}\_LOW}$ | 30  |     |     | ns   | WR low pulse width                                                   |

| twr_hold                 | 10  |     |     | ns   | WR hold time                                                         |

| tdin_setup               | 30  |     |     | ns   | Configuration data to WR setup time                                  |

| tdin_hold                | 10  |     |     | ns   | Configuration data to WR hold time                                   |

| t <sub>conf_settle</sub> | 20  |     |     | ns   | Configuration data settle time, WR rising edge to CONVST rising edge |

#### Figure 5. Parallel Write Timing Diagram

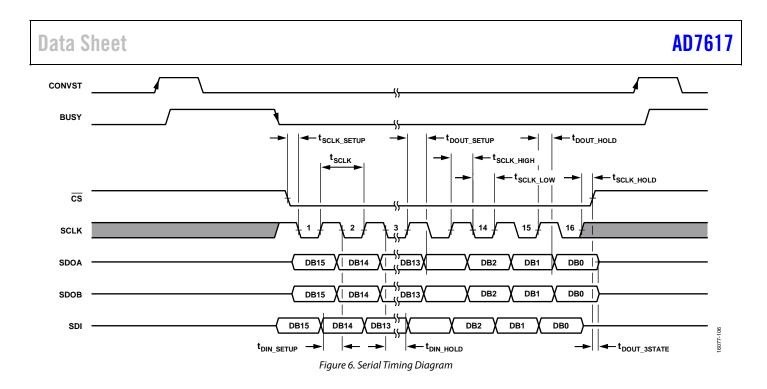

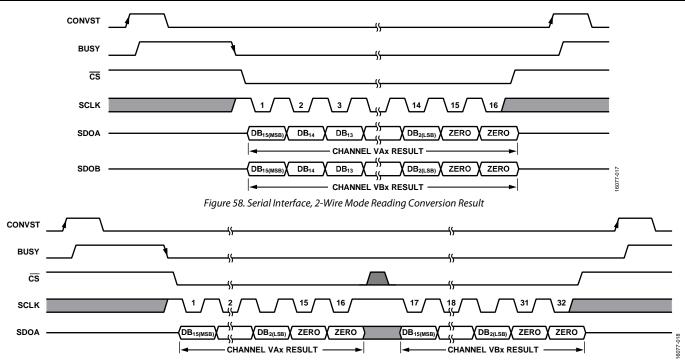

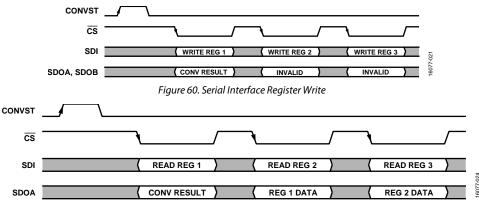

#### Serial Mode Timing Specifications

Table 4.

| Parameter                | Min                 | Тур | Max   | Unit | Description                                                      |

|--------------------------|---------------------|-----|-------|------|------------------------------------------------------------------|

| fsclk <sup>1</sup>       |                     |     | 40/50 | MHz  | SCLK frequency                                                   |

| t <sub>SCLK</sub>        | 1/f <sub>SCLK</sub> |     |       |      | Minimum SCLK period                                              |

| tsclk_setup <sup>1</sup> | 10.5                |     |       | ns   | CS to SCLK falling edge setup time, V <sub>DRIVE</sub> above 3 V |

|                          | 13.5                |     |       | ns   | CS to SCLK falling edge setup time, VDRIVE above 2.3 V           |

| tsclk_hold               | 10                  |     |       | ns   | SCLK to $\overline{\text{CS}}$ rising edge hold time             |

| tsclk_low                | 8                   |     |       | ns   | SCLK low pulse width                                             |

| tsclk_high               | 9                   |     |       | ns   | SCLK high pulse width                                            |

| tdout_setup <sup>1</sup> |                     |     | 9     | ns   | Data out access time after SCLK rising edge, VDRIVE above 3 V    |

|                          |                     |     | 11    | ns   | Data out access time after SCLK rising edge, VDRIVE above 2.3 V  |

| tdout_hold               | 4                   |     |       | ns   | Data out hold time after SCLK rising edge                        |

| tdin_setup               | 10                  |     |       | ns   | Data in setup time before SCLK falling edge                      |

| t <sub>DIN_HOLD</sub>    | 8                   |     |       | ns   | Data in hold time after SCLK falling edge                        |

| tdout_3state             |                     |     | 10    | ns   | CS rising edge to SDOx high impedance                            |

$^{\scriptscriptstyle 1}$  Dependent on  $V_{\text{DRIVE}}$  and  $C_{\text{LOAD}}$  (see Table 15).

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 5.

| Parameter                                 | Rating                               |

|-------------------------------------------|--------------------------------------|

| V <sub>cc</sub> to AGND                   | –0.3 V to +7 V                       |

| V <sub>DRIVE</sub> to AGND                | -0.3 V to V <sub>CC</sub> + 0.3 V    |

| Analog Input Voltage to AGND <sup>1</sup> | ±21 V                                |

| Digital Input Voltage to AGND             | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |

| Digital Output Voltage to AGND            | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |

| REFINOUT to AGND                          | $-0.3$ V to V_{CC} + 0.3 V           |

| Input Current to Any Pin Except           |                                      |

| Supplies <sup>1</sup>                     | ±10 mA                               |

| Operating Temperature Range               | -40°C to +125°C                      |

| Storage Temperature Range                 | -65°C to +150°C                      |

| Junction Temperature                      | 150°C                                |

| Soldering Reflow                          |                                      |

| Pb/Sn Temperature (10 sec to 30 sec)      | 240 (+0)°C                           |

| Pb-Free Temperature                       | 260 (+0)°C                           |

| ESD                                       |                                      |

| All Pins Except Analog Inputs             | 2 kV                                 |

| Analog Input Pins Only                    | 8 kV                                 |

$^{\rm 1}$  Transient currents of up to 100 mA do not cause silicon controlled rectifier (SCR) latch-up.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA} \text{ is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure. } \theta_{JC} \text{ is the junction to case thermal resistance.}$

#### Table 6. Thermal Resistance

| Package Type         | θја | θις | Unit |  |  |  |  |  |

|----------------------|-----|-----|------|--|--|--|--|--|

| ST-80-2 <sup>1</sup> | 41  | 7.5 | °C/W |  |  |  |  |  |

<sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board. See JEDEC JESD51.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

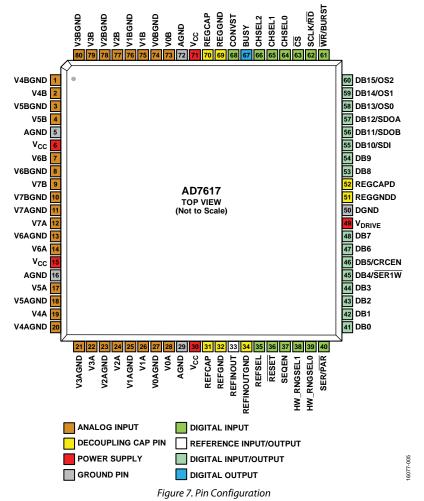

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 7. Pin Function Descriptions

| Pin No.       | <b>Type</b> <sup>1</sup> | Mnemonic <sup>2</sup> | Description                                                                                                                                                                                                           |

|---------------|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | AI GND                   | V4BGND                | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V4B.                                                                                                                                                |

| 2             | AI                       | V4B                   | Analog Input for Channel 4, ADC B.                                                                                                                                                                                    |

| 3             | AI GND                   | V5BGND                | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V5B.                                                                                                                                                |

| 4             | AI                       | V5B                   | Analog Input for Channel 5, ADC B.                                                                                                                                                                                    |

| 5, 16, 29, 72 | GND                      | AGND                  | Analog Supply Ground Pin.                                                                                                                                                                                             |

| 6, 15, 30, 71 | Ρ                        | Vcc                   | Analog Supply Voltage, 4.75 V to 5.25 V. This supply voltage is applied to the internal frontend amplifiers and to the ADC core. Decouple these pins to AGND using 0.1 $\mu$ F and 10 $\mu$ F capacitors in parallel. |

| 7             | AI                       | V6B                   | Analog Input for Channel 6, ADC B.                                                                                                                                                                                    |

| 8             | AI GND                   | V6BGND                | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V6B.                                                                                                                                                |

| 9             | AI                       | V7B                   | Analog Input for Channel 7, ADC B.                                                                                                                                                                                    |

| 10            | AI GND                   | V7BGND                | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V7B.                                                                                                                                                |

| 11            | AI GND                   | V7AGND                | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V7A.                                                                                                                                                |

| 12            | AI                       | V7A                   | Analog Input for Channel 7, ADC A.                                                                                                                                                                                    |

| 13            | AI GND                   | V6AGND                | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V6A.                                                                                                                                                |

| 14            | AI                       | V6A                   | Analog Input for Channel 6, ADC A.                                                                                                                                                                                    |

| 17            | AI                       | V5A                   | Analog Input for Channel 5, ADC A.                                                                                                                                                                                    |

| 18            | AI GND                   | V5AGND                | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V5A.                                                                                                                                                |

| 19            | AI                       | V4A                   | Analog Input for Channel 4, ADC A.                                                                                                                                                                                    |

| 20            | AI GND                   | V4AGND                | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V4A.                                                                                                                                                |

| Pin No.     | Type <sup>1</sup> | Mnemonic <sup>2</sup>     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21          | AI GND            | V3AGND                    | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V3A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 22          | AI                | V3A                       | Analog Input for Channel 3, ADC A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 23          | AI GND            | V2AGND                    | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V2A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24          | AI                | V2A                       | Analog Input for Channel 2, ADC A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 25          | AI GND            | V1AGND                    | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V1A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 26          | AI                | V1A                       | Analog Input for Channel 1, ADC A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 27          | AI GND            | V0AGND                    | Analog Input Ground Pin. This pin corresponds to Analog Input Pin V0A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 28          | AI                | VOA                       | Analog Input for Channel 0, ADC A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

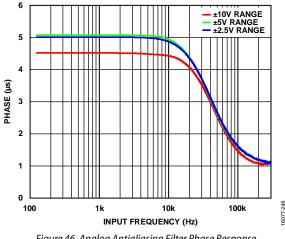

| 31          | САР               | REFCAP                    | Reference Buffer Output Force/Sense Pin. Decouple this pin to REFGND using a low effective series resistance (ESR), 10 $\mu$ F, X5R ceramic capacitor, as close to the REFCAP pin as possible. The voltage on this pin is typically 4.096 V.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 32          | CAP               | REFGND                    | Reference Ground Pin. Connect this pin to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 33          | REF               | REFINOUT                  | Reference Input/Reference Output. The on-chip reference of 2.5 V is available on this pin for external use when the REFSEL pin is set to logic high. Alternatively, the internal reference can be disabled by setting the REFSEL pin to logic low, and an external reference of 2.5 V can be applied to this input. Decoupling is required on this pin for both the internal and external reference options. Connect a 100 nF, X7R capacitor between the REFINOUT and REFINOUTGND pins, as close to the REFINOUT pin as possible. If using an external reference, connect a 10 k $\Omega$ series resistor to this pin to band limit the reference signal. |

| 34          | CAP               | REFINOUTGND               | Reference Input, Reference Output Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 35          | DI                | REFSEL                    | Internal/External Reference Selection Input. REFSEL is a logic input. If this pin is set to logic high, the internal reference is selected and enabled. If this pin is set to logic low, the internal reference is disabled, and an external reference voltage must be applied to the REFINOUT pin. The signal state is latched on the release of a full reset and requires an additional full reset to reconfigure.                                                                                                                                                                                                                                      |

| 36          | DI                | RESET                     | Reset Input. Connect a 100 pF capacitor between RESET and ground. Full and partial reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             |                   |                           | options are available. The type of reset is determined by the length of the RESET pulse.<br>Keeping RESET low places the device into shutdown mode. See the Reset Functionality<br>section for further details.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 37          | DI                | SEQEN                     | Channel Sequencer Enable Input (Hardware Mode Only). When SEQEN is tied low, the sequencer is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |                   |                           | When SEQEN is high, the sequencer is enabled (with restricted functionality in hardware mode). See the Sequencer section for further details. The signal state is latched on the release of a full reset, and requires an additional full reset to reconfigure.                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                   |                           | In software mode, this pin must be connected to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 38, 39      | DI                | HW_RNGSEL1,<br>HW_RNGSEL0 | Hardware/Software Mode Selection, Hardware Mode Range Select Inputs. Hardware/software mode selection is latched at full reset. Range selection in hardware mode is not latched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                   |                           | HW_RNGSELx = 00: software mode; the AD7617 is configured via the software registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             |                   |                           | HW_RNGSELx = 01: hardware mode; analog input range is $\pm 2.5$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                   |                           | HW_RNGSELx = 10: hardware mode; analog input range is $\pm 5$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 40          | DI                | SER/PAR                   | HW_RNGSELx = 11: hardware mode; analog input range is ±10 V.<br>Serial/Parallel Interface Selection Input. Logic input. If this pin is tied to logic low, the parallel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 40          |                   | SERVEAN                   | interface is selected. If this pin is tied to logic high, the serial interface is selected. The signal state is latched on the release of a full reset, and requires an additional full reset to reconfigure.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 41, 42, 43, | DO/DI             | DB0, DB1, DB2,            | Parallel Output/Input Data Bit 0 to Data Bit 3. In parallel mode, DB2 is the LSB of the 14-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 44          |                   | DB3                       | conversion result and DB0 and DB1output zero. In software parallel mode, DB0, DB1, DB2, and DB3 are the four LSBs of a register write/read operation. In hardware parallel mode, DB0 and DB1 can be left floating or pulled to DGND via a 10 k $\Omega$ pull-down resistor. Refer to the Parallel Interface section for further details. In serial mode, these pins must be tied to DGND.                                                                                                                                                                                                                                                                 |

# **Data Sheet**

| Pin No.    | Type <sup>1</sup> | Mnemonic <sup>2</sup>              | Description                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------|-------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 45         | DO/DI             | DB4/SER1W                          | Parallel Output/Input Data Bit 4/Serial Output Selection. In parallel mode, this pin acts as a three-state parallel digital output/input pin. Refer to the Parallel Interface section for further details.                                                                                                                                                                                                  |  |

|            |                   |                                    | In serial mode, this pin determines whether the serial output operates over SDOA and SDOB or just SDOA. When SER1W is low, the serial output operates over SDOA only. When SER1W is high, the serial output operates over both SDOA and SDOB. The signal state is latched on the release of a full reset, and requires an additional full reset to reconfigure.                                             |  |

| 46         | DO/DI             | DB5/CRCEN                          | Parallel Output/Input Data Bit 5/Cyclic Redundancy Check (CRC) Enable Input. In parallel mode, this pin acts as a three-state parallel digital input/output. While in serial mode, this pin acts as a CRC enable input. The CRCEN signal state is latched on the release of a full reset, and requires an additional full reset to reconfigure. Refer to the Digital Interface section for further details. |  |

|            |                   |                                    | In serial mode, when CRCEN is low, there is no CRC word following the conversion results; when CRCEN is high, an extra CRC word follows the last conversion word configured by CHSELx. See the CRC section for further details.                                                                                                                                                                             |  |

|            |                   |                                    | In software mode, this pin must be connected to DGND.                                                                                                                                                                                                                                                                                                                                                       |  |

| 47, 48     | DO/DI             | DB6, DB7                           | Parallel Output/Input Data Bit 6 and Data Bit 7. When SER/PAR = 0, these pins act as three-<br>state parallel digital input/outputs. Refer to the Parallel Interface section for further details. In<br>serial mode, when SER/PAR = 1, these pins must be tied to DGND.                                                                                                                                     |  |

| 49         | Ρ                 | Vdrive                             | Logic Power Supply Input. The voltage (2.3 V to 3.6 V) supplied at this pin determines the operating voltage of the interface. This pin is nominally at the same supply as the supply of the host interface. Decouple this pin with 0.1 $\mu$ F and 10 $\mu$ F capacitors in parallel.                                                                                                                      |  |

| 50         | GND               | DGND                               | Digital Ground. This pin is the ground reference point for all digital circuitry on the AD7617.<br>The DGND pin must connect to the DGND plane of a system.                                                                                                                                                                                                                                                 |  |

| 51         | CAP               | REGGNDD                            | Ground for the Digital Low Dropout (LDO) Regulator Connected to REGCAPD (Pin 52).                                                                                                                                                                                                                                                                                                                           |  |

| 52         | CAP               | REGCAPD                            | Decoupling Capacitor Pin for Voltage Output from Internal Digital Regulator. Decouple this output pin separately to REGGNDD using a 10 µF capacitor. The voltage at this pin is 1.89 V typical                                                                                                                                                                                                              |  |

| 53, 54     | DO/DI             | DB8, DB9                           | Parallel Output/Input Data Bit 9 and Data Bit 8. When SER/PAR = 0, these pins act as three-<br>state parallel digital input/outputs. Refer to the Parallel Interface section for further details.<br>In serial mode, when SER/PAR = 1, these pins must be tied to DGND.                                                                                                                                     |  |

| 55         | DO/DI             | DB10/SDI                           | Parallel Output/Input Data Bit DB10/Serial Data Input. When SER/PAR = 0, this pin acts as a three-state parallel digital input/output. Refer to the Parallel Interface section for further details. In hardware serial mode, tie this pin to DGND.                                                                                                                                                          |  |

|            |                   |                                    | In serial mode, when SER/ $\overline{PAR} = 1$ , this pin acts as the data input of the SPI interface.                                                                                                                                                                                                                                                                                                      |  |

| 56         | DO/DI             | DB11/SDOB                          | Parallel Output/Input Data Bit 11/Serial Data Output B. When SER/PAR = 0, this pin acts as a three-state parallel digital input/output. Refer to the Parallel Interface section for further details.                                                                                                                                                                                                        |  |

|            |                   |                                    | In serial mode, when SER/ $\overline{PAR} = 1$ and DB4/ $\overline{SER1W} = 1$ , this pin functions as SDOB and outputs serial conversion data.                                                                                                                                                                                                                                                             |  |

| 57         | DO/DI             | DB12/SDOA                          | Parallel Output/Input Data Bit 12/Serial Data Output A. When SER/PAR = 0, this pin acts as a three-state parallel digital input/output. Refer to the Parallel Interface section for further details.                                                                                                                                                                                                        |  |

|            |                   |                                    | In serial mode, when SER/PAR = 1, this pin functions as SDOA and outputs serial conversion data.                                                                                                                                                                                                                                                                                                            |  |

| 58, 59, 60 | DO/DI             | DB13/OS0,<br>DB14/OS1,<br>DB15/OS2 | Parallel Output/Input Data Bit 13, Data Bit 14, and Data Bit 15/Oversampling Ratio Selection.<br>When SER/PAR = 0, these pins act as three-state parallel digital input/outputs. Refer to the<br>Parallel Interface section for further details.                                                                                                                                                            |  |

|            |                   |                                    | In serial hardware mode, these pins control the oversampling settings. The signal state is latched on the release of a full reset and requires an additional full reset to reconfigure. See the Digital Filter section for further details.                                                                                                                                                                 |  |

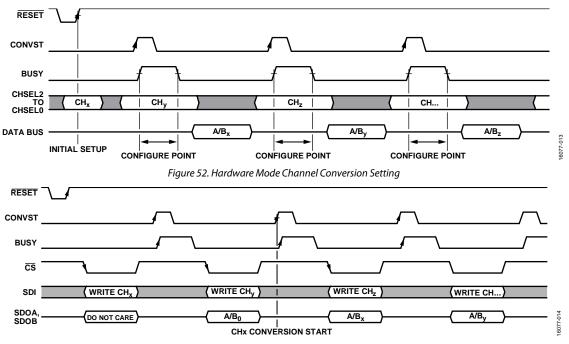

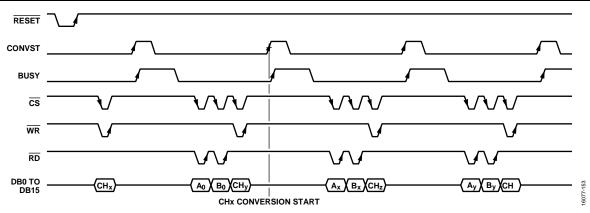

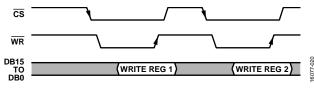

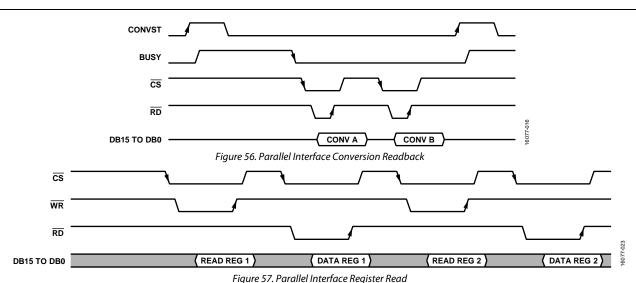

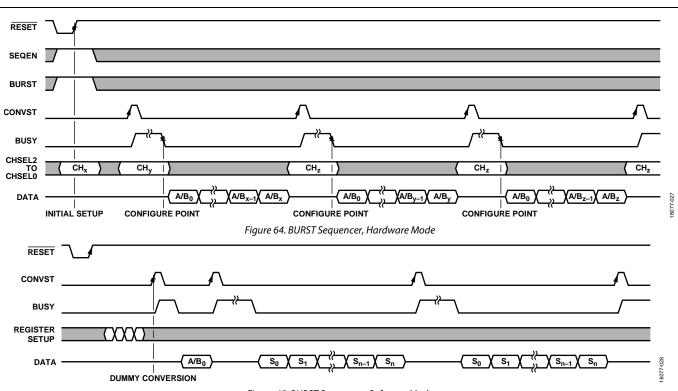

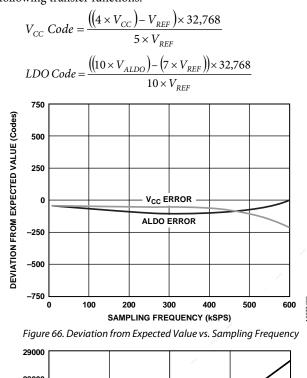

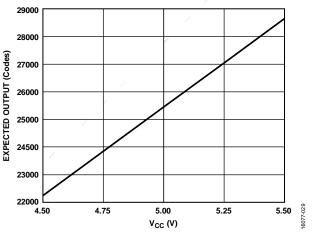

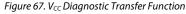

|            |                   |                                    | In software serial mode, these pins must be connected to DGND.                                                                                                                                                                                                                                                                                                                                              |  |