# Narrow Voltage DC Battery Charger

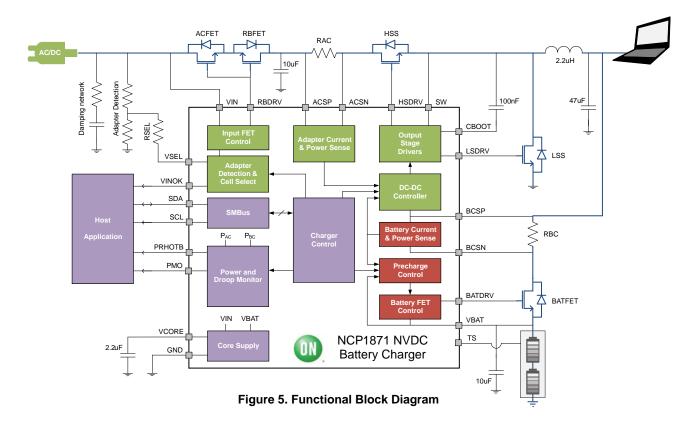

The NCP1871 is a NVDC switching battery charger designed for 2–3–4 battery cell applications such as ultra books or tablets. It is optimized for use with the mobile computing chipsets, and is also compatible with most mobile solutions.

The NCP1871 is designed around a full NMOS DC to DC controller that brings down the high voltage charger adapter voltage to a regulated system supply that is in the same range as the battery pack voltage. This limits the variation on the system supply voltage, and improves the efficiency of the core converters. The device includes a voltage droop monitor, charger adapter validation and blocking as well as an intelligent battery connection control. The adapter current, charge current and system current are closely monitored and an image is provided to the host. The NCP1871 is fully programmable through an  $\rm I^2C$  friendly SMBus Interface.

#### **Features**

- SMBus Host-controlled NVDC-1 2S-4S Battery Charge Controller

- Instant-on Works with No Battery or Deeply Discharged Battery

- Automatic Supplement Mode with BATFET Control

- Battery Removal Sensor

- Programmable Switching Frequency

- SMBUS Clock up to 400 kHz (I<sup>2</sup>C compatible)

- Programmable Charge Current, Charge Voltage, Input Current Limit with Interrupt Management

- ◆ ±0.5% Charge Voltage Regulation up to 18.08 V

- ±3% Input/Charge Current Regulation up to 8.064 A

- Support Battery LEARN Function

- Support Shipping Mode and Hard System Reset

- Ultra-Low Quiescent Current of 10 μA at OFF Mode and High PFM Light Load Efficiency 80% at 20 mA Load to Meet Energy Star and ErP Lot6

- Full NMOS Solution

- Current and Power Monitoring

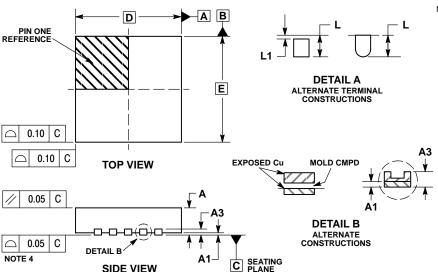

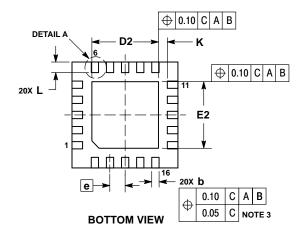

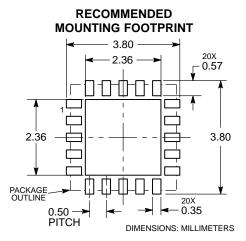

- 3.5 mm x 3.5 mm QFN-20 Package

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

# **Typical Applications**

- Ultrabook

- Notebook

- Tablet PC

# ON Semiconductor®

www.onsemi.com

#### MARKING DIAGRAM

XXXXX = Specific Device Code

A = Assembly Location

L = Wafer Lot Y = Year W = Work Week • Pb-Free Package

(Note: Microdot may be in either location)

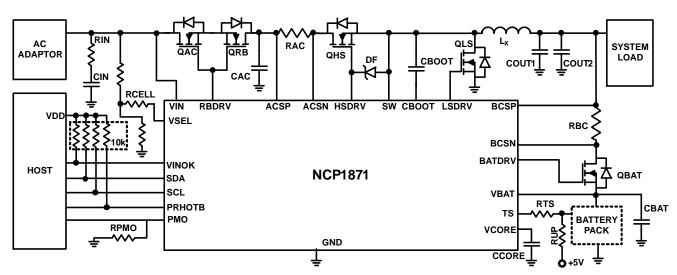

## **PIN CONFIGURATION**

#### **ORDERING INFORMATION**

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| NCP1871MNTXG | QFN20<br>(Pb-Free) | 3000 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

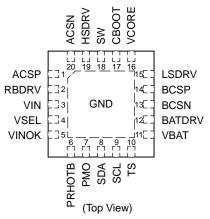

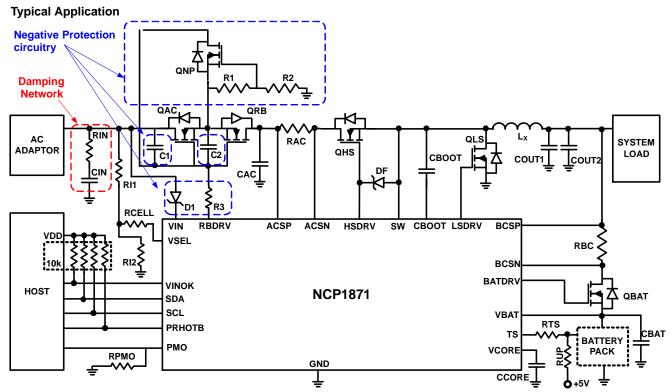

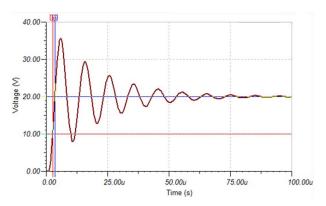

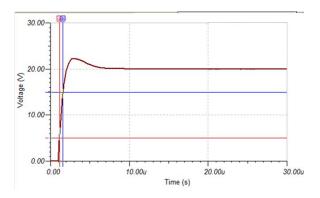

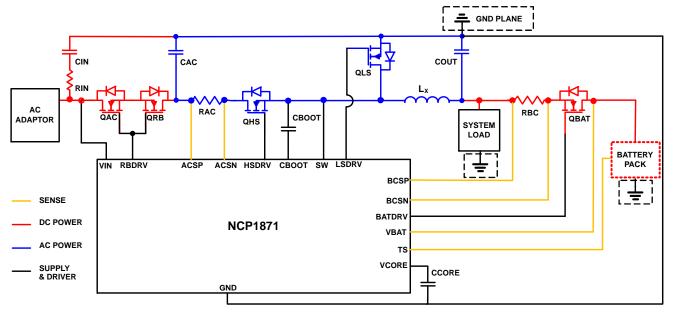

Figure 1. Typical Application Circuit

Figure 2. Pin Out Description (Top View)

# **Table 1. PIN FUNCTIONAL DESCRIPTION**

| Pin | Name          | Туре              | Description                                                                                                                                                                                                                   |  |

|-----|---------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | ACSP          | ANALOG INPUT      | Charger Adapter Current Sense Positive terminal. Use a 10 m $\Omega$ sense resistor RAC. Bypass ACSP with a 10 $\mu$ F capacitor                                                                                              |  |

| 2   | RBDRV         | ANALOG OUTPUT     | Reverse Blocking FET Driver. Drives the gate of the RBFET NMOS Can also drive gate optional ACFET NMOS.                                                                                                                       |  |

| 3   | VIN           | ANALOG INPUT      | Charger Adapter Input. Bypass with a Damping network                                                                                                                                                                          |  |

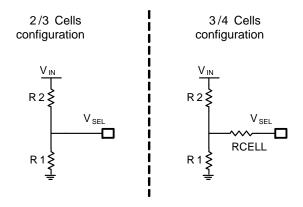

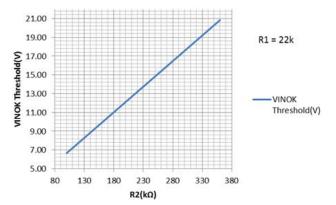

| 4   | VSEL          | ANALOG INPUT      | Adapter detection input. Program adapter valid input threshold by connecting a resistor divider from adapter input to VSEL pin to GND pin. Connect a serial resistance of 220 k $\Omega$ to select 3–4 Cells default setting. |  |

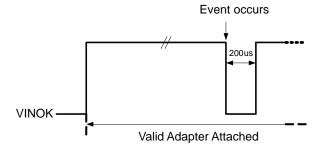

| 5   | VINOK         | OPEN DRAIN OUTPUT | Charge Adapter Valid Output. Signals the VIN is within the target range.  Open drain output requiring an external pull up. Also use for short pulse signal interrupt generation                                               |  |

| 6   | PRHOTB        | OPEN DRAIN OUTPUT | Processor Hot Signal Output. Pulled low to reduce processor speed based on BCSP.                                                                                                                                              |  |

| 7   | PMO           | ANALOG OUTPUT     | Current based indication of system power. Amplified version of the adapter power, the battery power or sum of both.                                                                                                           |  |

| 8   | SDA           | DIGITAL IN/OUT    | Control Bus Data Line.                                                                                                                                                                                                        |  |

| 9   | SCL           | DIGITAL INPUT     | Control Bus Clock Line.                                                                                                                                                                                                       |  |

| 10  | TS            | ANALOG INPUT      | Battery Presence Detection. Connect this pin to the battery thermistor sensor.                                                                                                                                                |  |

| 11  | VBAT          | ANALOG IN/OUT     | Battery Connection. Bypass with at least 10 μF capacitor.                                                                                                                                                                     |  |

| 12  | BATDRV        | ANALOG OUTPUT     | Battery FET Driver.                                                                                                                                                                                                           |  |

| 13  | BCSN          | ANALOG INPUT      | Battery Current Sense Negative Terminal. Use a 10 m $\Omega$ sense resistor RBC.                                                                                                                                              |  |

| 14  | BCSP          | ANALOG INPUT      | Battery Current Sense Positive Terminal. Use a 10 m $\Omega$ sense resistor RBC.                                                                                                                                              |  |

| 15  | LSDRV         | ANALOG OUTPUT     | Low Side Switch Driver. Drives the gate of the DC to DC low side NMOS.                                                                                                                                                        |  |

| 16  | VCORE         | ANALOG OUTPUT     | Core Voltage. Do not connect load on this pin. Bypass with a 2.2 $\mu\text{F}$ capacitor                                                                                                                                      |  |

| 17  | CBOOT         | ANALOG IN/OUT     | Bootstrap Capacitor Connection.                                                                                                                                                                                               |  |

| 18  | SW            | ANALOG OUTPUT     | Switching Node. Connection to the 2.2 µH inductor.                                                                                                                                                                            |  |

| 19  | HSDRV         | ANALOG OUTPUT     | High Side Switch Driver. Drives the gate of the DC to DC high side NMOS. Supplied from the bootstrap capacitor.                                                                                                               |  |

| 20  | ACSN          | ANALOG INPUT      | Charger Adapter Current Sense Negative terminal. Use a 10 m $\Omega$ sense resistor RAC.                                                                                                                                      |  |

| 1   | EXPOSE<br>PAD | GROUND            | Internally connected to ground                                                                                                                                                                                                |  |

**Table 2. MAXIMUM RATINGS**

| Rating                                                                                         | Symbol                             | Value                | Unit    |

|------------------------------------------------------------------------------------------------|------------------------------------|----------------------|---------|

| VIN , RBDRV (Note 1)                                                                           | V <sub>MR_AC</sub>                 | -0.3 to +30          | V       |

| ACSP, ACSN, HSDRV, SW, CBOOT, BCSP, BCSN, BATDRV, VBAT (Note 1)                                | V <sub>MR_ACS</sub>                | -0.3 to +30          | V       |

| TS (Note 1)                                                                                    | V <sub>MR_DRP</sub>                | -0.3 to +7.0         | V       |

| CBOOT with respect to SW (JEDEC standard JESD22-A108)                                          | V <sub>MR_CBOOT</sub>              | -0.3 to +7.0         | V       |

| LSDRV, VCORE, PRHOTB, PMO, VINOK, VSEL (Note 1)                                                | $V_{MR\_LV}$                       | -0.3 to +7.0         | V       |

| Digital Input: SCL, SDA (Note 1) Input Voltage Input Current                                   | V <sub>DG</sub><br>I <sub>DG</sub> | -0.3 to +7.0 V<br>20 | V<br>mA |

| Human Body Model (HBM) ESD Rating are (Note 2)                                                 | ESD HBM                            | 1500                 | V       |

| Charged Device Model (CDM) ESD Rating are (Note 2)                                             | ESD CDM                            | 750                  | V       |

| Latch up Current (Note 3):  All Digital pins( V <sub>DG</sub> )  VINOK, VSEL  All others pins. | lLU                                | ±10<br>±30<br>±100   | mA      |

| Storage Temperature Range                                                                      | T <sub>STG</sub>                   | -65 to + 150         | °C      |

| Maximum Junction Temperature (Note 4)                                                          | T <sub>J</sub>                     | -40 to + TSD         | °C      |

| Moisture Sensitivity (Note 5)                                                                  | MSL                                | Level 1              |         |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 1. With Respect to GND. According to JEDEC standard JESD22-A108.

- 2. This device series contains ESD protection and passes the following tests:. Human Body Model (HBM) ±1.5 kV per JEDEC standard: JESD22–A114. Charged Device Model (CDM) ±750 V per JEDEC standard: JESD22–C101.

- 3. Latch up Current Maximum Rating: ±100 mA or per ±10 mA JEDEC standard: JESD78 class II.

- 4. A thermal shutdown protection avoids irreversible damage on the device due to power dissipation.

- 5. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020.

**Table 3. OPERATING CONDITION**

| Symbol                                                                                    | Parameter                          | Conditions          | Min | Тур | Max               | Unit |

|-------------------------------------------------------------------------------------------|------------------------------------|---------------------|-----|-----|-------------------|------|

| V <sub>IN</sub>                                                                           | Operational Power Supply           |                     | 4.5 |     | V <sub>INOV</sub> | V    |

| $V_{DG}$                                                                                  | Digital input voltage level        |                     | 0   |     | 5.5               | V    |

| T <sub>A</sub>                                                                            | Ambient Temperature Range          |                     | -40 | 25  | +85               | °C   |

| Isink                                                                                     | VINOK sink current                 |                     |     |     | 10                | mA   |

| C <sub>IN</sub>                                                                           | Decoupling input capacitor         |                     |     | 4.7 |                   | μF   |

| R <sub>IN</sub>                                                                           | Damping resistor                   |                     |     | 2   |                   | Ω    |

| C <sub>AC</sub>                                                                           | Decoupling Switcher capacitor      |                     |     | 10  |                   | μF   |

| C <sub>BOOT</sub>                                                                         | Bootstrap capacitor                |                     |     | 100 |                   | nF   |

| C <sub>CORE</sub>                                                                         | Decoupling core supply capacitor   |                     |     | 2.2 |                   | μF   |

| C <sub>OUT1</sub> , C <sub>OUT2</sub>                                                     | Decoupling system capacitor        |                     |     | 47  |                   | μF   |

| L <sub>X</sub>                                                                            | Switcher Inductor                  |                     |     | 2.2 |                   | μΗ   |

| R <sub>AC</sub> , R <sub>BC</sub>                                                         | Current sense resistor             |                     |     | 10  |                   | mΩ   |

| R <sub>DSONQRB,</sub> R <sub>DSONQHS,</sub><br>R <sub>DSON QLS,</sub> R <sub>DSONQB</sub> | RDSON resistance                   | N-channel<br>MOSFET |     | 10  |                   | mΩ   |

| C <sub>GQRB</sub> ,C <sub>GQHS</sub> , C <sub>GQLS</sub> , C <sub>GQB</sub>               | Total Gate Charge                  | $V_{GS} = 5 V$      |     | 10  |                   | nC   |

| $R_{	heta JA}$                                                                            | Thermal Resistance Junction to Air | (Notes 4 and 6)     |     | 50  |                   | °C/W |

| T <sub>J</sub>                                                                            | Junction Temperature Range         |                     | -40 | 25  | +125              | °C   |

<sup>6.</sup> The R<sub>0JA</sub> is dependent on the PCB heat dissipation. Board used to drive this data was a 2s2p JEDEC PCB standard. Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**Table 4. ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A$  between  $-20^{\circ}C$  to  $+85^{\circ}C$  and  $T_J$  up to  $+125^{\circ}C$  for  $V_{IN}$  between 4.5 V to 22 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}C$  and  $V_{IN} = 12$  V (Unless otherwise noted).

| Symbol               | Parameter                          | Conditions                                           |                                    | Min   | Тур                                       | Max   | Unit  |

|----------------------|------------------------------------|------------------------------------------------------|------------------------------------|-------|-------------------------------------------|-------|-------|

| INPUT VOL            | _TAGE                              |                                                      |                                    | L     | <u> </u>                                  |       |       |

| V <sub>INDET</sub>   | Presence input detection threshold | V <sub>IN</sub> rising                               |                                    | 3.2   | 3.5                                       | 3.8   | V     |

|                      |                                    | Hysteresis                                           |                                    |       | 175                                       |       | mV    |

| V <sub>INSYS</sub>   | Charger mode detection threshold   | V <sub>IN</sub> – V <sub>BCSP</sub> , V <sub>I</sub> | N rising                           | 95    | 150                                       | 200   | mV    |

|                      | voltage                            | V <sub>IN</sub> – V <sub>BCSP</sub> , V <sub>I</sub> | N falling                          | 10    | 50                                        | 90    | mV    |

| V <sub>INLO</sub>    |                                    | V <sub>SEL</sub> rising                              |                                    | 1.188 | 1.2                                       | 1.212 | V     |

|                      |                                    | Hysteresis                                           |                                    | 25    | 50                                        | 75    | mV    |

| V <sub>CELL</sub>    | Cells detection threshold          | V <sub>SEL</sub> rising                              |                                    | 0.4   | 0.45                                      | 0.5   | V     |

|                      |                                    | Hysteresis                                           |                                    |       | 50                                        |       | mV    |

| V <sub>INMINOK</sub> | Operating charger valid            | V <sub>IN</sub> rising, Ratio                        | o of V <sub>SYSMIN</sub>           | 103.4 | 106                                       | 108.6 | %     |

|                      | threshold                          | Hysteresis                                           |                                    | 101.4 | 104                                       | 106.6 | %     |

| V <sub>INOV</sub>    | Valid input high threshold         | V <sub>IN</sub> rising (Note                         | 7)                                 | 22    | 22.5                                      | 23    | V     |

|                      |                                    | Hysteresis                                           |                                    |       | 125                                       |       | mV    |

| T <sub>VINOV</sub>   | Max Hot Plug Rise time             | ACFET present no overvoltage                         | r, from 0 to 30 V,<br>on ACSP      |       | 10                                        |       | V/μs  |

|                      |                                    | RBFET only, fro                                      |                                    | 10    |                                           |       |       |

| INPUT CUE            | RRENT LIMITING                     |                                                      |                                    |       |                                           |       |       |

| I <sub>INLIM</sub>   | Input current limit                | Input Current Limit Range,<br>Average value.         |                                    | 128   |                                           | 8064  | mA    |

|                      |                                    | Input Current Limit Default. (Note 8)                |                                    |       | 3328                                      |       | mA    |

|                      |                                    | Input Current Granularity                            |                                    |       | 128                                       |       | mA    |

|                      |                                    | Input Current                                        | 128 mA to 2048 mA                  | -64   |                                           | +64   | mA    |

|                      |                                    | Accuracy                                             | 2048 mA to 4096 mA                 | -3    |                                           | +3    | %     |

| T <sub>IIN</sub>     | Current Ramping                    |                                                      |                                    |       | 128/16                                    |       | mA/μs |

| I <sub>INSHORT</sub> | Short Circuit Detect               | Input Current Li                                     | mit ILIM                           | 10    | 11                                        | 12    | Α     |

| T <sub>INSHORT</sub> | Short Circuit Detect Delay         |                                                      |                                    |       | 10                                        |       | μs    |

| BATTERY              | AND SYSTEM VOLTAGE                 | •                                                    |                                    |       |                                           |       |       |

| V <sub>CHG</sub>     | Output voltage range               | Programmable                                         |                                    | 3328  |                                           | 18080 | mV    |

|                      |                                    | Default value, (                                     | Note 9)                            |       | V <sub>SYSMIN</sub> + V <sub>SYSOFF</sub> |       |       |

|                      | Voltage regulation accuracy        | Constant voltag                                      | je mode, ICHG>=500 mA              | -0.5  |                                           | 0.5   | %     |

|                      | Programmable granularity           |                                                      |                                    |       | 16                                        |       | mV    |

|                      | Voltage Ramping                    |                                                      |                                    |       | 64/16                                     |       | mV/μs |

| V <sub>SYSOV</sub>   | System OVP                         | VBCSP                                                | VCHG ≤ 9V                          |       | 10.8                                      |       | V     |

|                      |                                    | Rising                                               | 9 V ≤ VCHG ≤ 13.5 V                |       | 14.4                                      |       | V     |

|                      |                                    | VCHG > 13.5 V                                        |                                    |       | 21.6                                      |       | V     |

|                      | SYSOV Release Threshold            | Hysteresis, Rat                                      | io of V <sub>CHG</sub> Rising Edge |       | 102                                       |       | %     |

| V <sub>BUCKOV</sub>  | Buck Out of Regulation             |                                                      | Ratio of V <sub>CHG</sub> Rising   |       | 104                                       |       | %     |

|                      |                                    |                                                      | ı                                  | 1     | 1                                         | 1     |       |

<sup>7. 19</sup> V and 14.5 V versions are available upon request

<sup>8. 2560</sup> mA versions is available upon request

9. 5.6 V, 12.352 V and 16.592 V versions are available upon request

$<sup>10.512\ \</sup>text{mA},\,1024\ \text{mA}$  and  $2048\ \text{mA}$  versions are available upon request

<sup>11. 256</sup> mA, 128 mA and 0 mA versions are available upon request

<sup>12.5.6</sup> V, 5.7 V, 5.8 V versions are available upon request

**Table 4. ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A$  between  $-20^{\circ}C$  to  $+85^{\circ}C$  and  $T_J$  up to  $+125^{\circ}C$  for  $V_{IN}$  between 4.5 V to 22 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}C$  and  $V_{IN} = 12$  V (Unless otherwise noted).

| Symbol               | Parameter                                 | Conditions                                             | Min  | Тур    | Max   | Unit  |

|----------------------|-------------------------------------------|--------------------------------------------------------|------|--------|-------|-------|

| BATTERY              | AND SYSTEM VOLTAGE                        |                                                        | -    |        |       |       |

| V <sub>SYSMIN</sub>  | Minimum System Voltage Range              |                                                        | 3328 |        | 17792 | mV    |

|                      | Minimum System Voltage Default            | RCELL = $0 \Omega$ (2–3 cells)                         |      | 7936   |       | mV    |

|                      |                                           | RCELL = 220 kΩ (3-4 cells)                             |      | 12032  |       | mV    |

|                      |                                           | Hysteresis                                             |      | 50     |       | mV    |

|                      | Minimum System Voltage<br>Granularity     |                                                        |      | 128    |       | mV    |

| V <sub>SYSOFF</sub>  | System Voltage Regulation Offset          | SYSOFF_SEL = 0, Default                                |      | 384    |       | mV    |

|                      |                                           | SYSOFF_SEL = 1                                         |      | 256    |       | mV    |

| CHARGE (             | CURRENT                                   |                                                        | •    |        | •     |       |

| I <sub>CHG</sub>     | Charge current range                      | Programmable                                           | 128  |        | 8064  | mA    |

|                      |                                           | Default value, (Note 10)                               |      | 128    |       | mA    |

|                      | Charge current accuracy                   | 128 mA to 2048 mA                                      | -64  |        | +64   | mA    |

|                      |                                           | 2048 mA to 8064 mA                                     | -3   |        | 3     | %     |

|                      | I <sup>2</sup> C Programmable granularity |                                                        |      | 128    |       | mA    |

| T <sub>ICHG</sub>    | Current Ramping                           |                                                        |      | 128/16 |       | mA/μs |

| I <sub>EOC</sub>     | End of Charge Current Range               |                                                        | 128  |        | 1024  | mA    |

|                      | End of Charge Current Default             |                                                        |      | 256    |       | mA    |

|                      | End of Charge Current Granularity         |                                                        |      | 128    |       | mA    |

|                      | End of Charge Current Accuracy            |                                                        | -64  |        | +64   | mA    |

| REVERSE              | BLOCKING FET                              |                                                        | •    |        | •     |       |

| T <sub>RBDR</sub>    | RBDRV Rise Time                           | 3 nC Load                                              |      | 2      |       | ms    |

| T <sub>RBDF</sub>    | RBDRV Fall Time                           | 10 nC Load                                             |      | 1      |       | μS    |

| R <sub>RBDL</sub>    | RBDRV Output High                         | Referred to ground                                     |      |        | 30    | V     |

| R <sub>RBDH</sub>    |                                           | Referred to VIN, VIN ≥ 9 V                             | 4.45 | 5      | 5.5   | V     |

| V <sub>RBDL</sub>    | RBDRV Output Low                          | V <sub>IN</sub> < V <sub>ACSP</sub> , Referred to VIN  |      | 0      |       | V     |

| V <sub>RBDH</sub>    |                                           | V <sub>IN</sub> > V <sub>ACSP</sub> , Referred to ACSP |      | 0      |       | V     |

| VINOK PIN            |                                           |                                                        | •    |        | •     |       |

| V <sub>OL</sub>      | FLAG output low voltage                   | I <sub>VINOK</sub> = 3 mA                              |      |        | 0.4   | V     |

| I <sub>INOKLK</sub>  | Off-state leakage                         | V <sub>VINOK</sub> = 5 V                               |      |        | 1     | μΑ    |

| BATTERY              | MOSFET FET and PRECHARGE MOI              | DE .                                                   | •    |        | •     |       |

| V <sub>PRERED</sub>  | Precharge Current Reduction Range         | SYSOFF_SEL = 0,<br>BCSP-VSYSMIN, IBAT(DC) = 0 A.       | 49   |        | 399   | mV    |

| V <sub>PRESTOP</sub> | Precharge Current Reduction Range         | BCSP-VSYSMIN, IBAT(AC) = 0 A.                          | 0    |        | 128   |       |

| V <sub>DRCON</sub>   | Battery FET Reconnect Detection Threshold | End of Charge, VBAT-BCSP                               |      | 256    |       | mV    |

| V <sub>DOPEN</sub>   | Battery FET Re-open Detection Threshold   | Supplement, VBAT-BCSP                                  | -1   |        | +5    | mV    |

|                      |                                           | •                                                      |      |        |       |       |

<sup>7. 19</sup> V and 14.5 V versions are available upon request

<sup>8. 2560</sup> mA versions is available upon request

<sup>9. 5.6</sup> V, 12.352 V and 16.592 V versions are available upon request

<sup>10.512</sup> mA, 1024 mA and 2048 mA versions are available upon request

<sup>11. 256</sup> mA, 128 mA and 0 mA versions are available upon request

<sup>12.5.6</sup> V, 5.7 V, 5.8 V versions are available upon request

**Table 4. ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A$  between  $-20^{\circ}$ C to  $+85^{\circ}$ C and  $T_J$  up to  $+125^{\circ}$ C for  $V_{IN}$  between 4.5 V to 22 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}$ C and  $V_{IN} = 12$  V (Unless otherwise noted).

| Symbol                 | Parameter                                          | Conditions                                                                                                | Min  | Тур | Max  | Unit |

|------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|-----|------|------|

| BATTERY                | MOSFET FET and PRECHARGE MOI                       | DE .                                                                                                      |      | •   |      |      |

| V <sub>PRE</sub>       | Precharge voltage threshold                        | V <sub>BAT</sub> rising, Ratio of V <sub>SYSMIN</sub>                                                     |      | 100 |      | %    |

|                        |                                                    | Accuracy                                                                                                  | -2   |     | +2   | %    |

|                        |                                                    | Hysteresis                                                                                                |      | 98  |      | %    |

| I <sub>PREMAX</sub>    | Precharge Current Range                            |                                                                                                           | 128  |     | 512  | mA   |

|                        | Precharge Current Default                          | Default value (Note 11)                                                                                   |      | 512 |      | mA   |

|                        | Precharge Current Accuracy                         |                                                                                                           | -64  |     | +64  | mA   |

| $V_{BFH}$              | BATDRV Output High                                 | VBAT ≥ 3.3 V, Referred to VBAT                                                                            | 4.5  | 5   | 8    | V    |

| $V_{BFL}$              | BATDRV Output Low                                  | Referred to GND                                                                                           | -0.3 | 0   | 0.3  | V    |

| T <sub>FBF</sub>       | BATDRV Fall Time                                   | From V <sub>BFH</sub> to V <sub>BFL</sub> , 10 nC Load                                                    |      | 200 |      | μs   |

| $T_{FBR}$              | BATDRV Rise Time                                   | From V <sub>BFL</sub> to V <sub>BFH</sub> 3 nC Load, From<br>End of Charge to Supplement mode             |      | 2   |      | μs   |

|                        |                                                    | From V <sub>BFL</sub> to V <sub>BFH</sub> , 3 nC Load.                                                    |      | 5   |      | ms   |

| I <sup>2</sup> C/SMBus | 3                                                  |                                                                                                           |      |     |      |      |

| F <sub>SCL</sub>       | Bus operating frequency                            |                                                                                                           | 10   |     | 400  | kHz  |

| T <sub>I2CTO</sub>     | Bus Timeout                                        |                                                                                                           | 25   |     | 35   | ms   |

| VI <sub>2CINT</sub>    | Peak voltage at SCL line                           |                                                                                                           | 2.7  |     | 5.5  | V    |

| V <sub>I2CIL</sub>     | SCL, SDA low input voltage                         |                                                                                                           | -0.5 |     | 0.5  | V    |

| V <sub>I2CIH</sub>     | SCL, SDA high input voltage                        |                                                                                                           | 1.7  |     | 5.5  | V    |

| V <sub>I2COL</sub>     | SDA low output voltage                             | Sink 3 mA                                                                                                 | 0    |     | 0.4  | V    |

| BUCK COI               | NVERTER                                            |                                                                                                           |      | •   | •    |      |

| F <sub>SWCHG</sub>     | Switching Frequency Range                          |                                                                                                           | 600  |     | 1200 | kHz  |

|                        | Switching Frequency Default                        |                                                                                                           |      | 800 |      | kHz  |

|                        | Switching Frequency Granularity                    |                                                                                                           |      | 200 |      | kHz  |

|                        | Switching Frequency Accuracy                       |                                                                                                           | -10  |     | +10  | %    |

| F <sub>SWSMB</sub>     | Spread Spectrum Modulation Bandwidth               | Ratio of FSW                                                                                              |      | 6   |      | %    |

| F <sub>SWSMR</sub>     | Spread Spectrum Modulation Rate                    |                                                                                                           |      | 23  |      | kHz  |

| I <sub>OUTMAX</sub>    | Output Current Capability                          |                                                                                                           | 8    |     |      | Α    |

| I <sub>PKMAX</sub>     | Maximum peak inductor current                      |                                                                                                           |      | 9   |      | Α    |

| GENERAL                | PARAMETERS                                         |                                                                                                           |      | •   | •    |      |

| I <sub>OFF</sub>       | OFF Mode quiescent current (Measured on BAT)       | PMO_EN = 0, VDROOP_EN = 0,<br>VIN = 0 V, 2~3 Cells                                                        |      |     | 10   | μА   |

|                        |                                                    | PMO_EN = 0, VDROOP_EN = 0,<br>VIN = 0 V, 4 Cells                                                          |      |     | 12   |      |

| I <sub>QLB</sub>       | Drop Detection Quiescent Current (Measured on BAT) | OFF mode. PMO_EN = 0,<br>VDROOP_EN = 1 VIN = 0 V, VBAT><br>V <sub>LOBAT</sub> , VDRP_SEL! = 00, 2~3 Cells |      |     | 80   | μΑ   |

|                        |                                                    | OFF mode. PMO_EN = 0,<br>VDROOP_EN = 1 VIN =0V, VBAT><br>V <sub>LOBAT</sub> , VDRP_SEL! = 00, 4 Cells     |      |     | 140  |      |

| I <sub>STBY</sub>      | PMO block quiescent current (Measured on BAT)      | OFF mode. PMO_EN = 1, VDROOP_EN = 0 VIN = 0 V, VBAT> 4 V                                                  |      |     | 1500 | μΑ   |

|                        |                                                    |                                                                                                           |      |     |      |      |

<sup>7. 19</sup> V and 14.5 V versions are available upon request

<sup>8. 2560</sup> mA versions is available upon request

<sup>9. 5.6</sup> V, 12.352 V and 16.592 V versions are available upon request

<sup>10.512</sup> mA, 1024 mA and 2048 mA versions are available upon request

<sup>11. 256</sup> mA, 128 mA and 0 mA versions are available upon request

<sup>12.5.6</sup> V, 5.7 V, 5.8 V versions are available upon request

Table 4. ELECTRICAL CHARACTERISTICS Min & Max Limits apply for  $T_A$  between  $-20^{\circ}C$  to  $+85^{\circ}C$  and  $T_J$  up to  $+125^{\circ}C$  for  $V_{IN}$ between 4.5 V to 22 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}C$  and  $V_{IN} = 12$  V (Unless otherwise noted).

| Symbol                             | Parameter                                 | Conditions                                                                                                                   | Min  | Тур   | Max  | Unit              |

|------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------------------|

| GENERAL                            | PARAMETERS                                |                                                                                                                              |      |       |      |                   |

| E <sub>ECO</sub>                   | NCP1871 Efficiency                        | With Recommended operating condition,<br>VIN = 12 V , VBAT = 8.4 V, PMO_EN =<br>0, VDROOP_EN = 0 ECO_MODE = 1,<br>20 mA load |      | 80    |      | %                 |

| V <sub>CORE</sub>                  | Core supply voltage                       | VIN > 5.5 V                                                                                                                  |      | 5     |      | V                 |

| $V_{UVLO}$                         | System UVLO                               | VIN or VBAT rising, SMBus register available                                                                                 |      |       | 4    | V                 |

| T <sub>SD</sub>                    | Thermal Shutdown                          |                                                                                                                              |      | 135   |      | °C                |

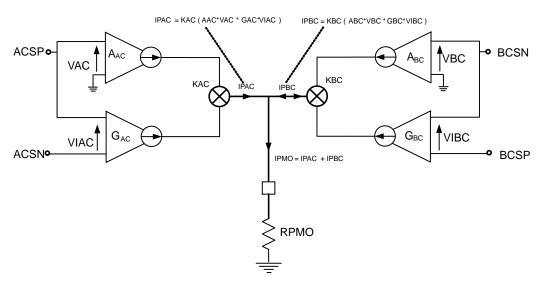

| CURRENT                            | AND POWER MONITORING                      |                                                                                                                              |      |       |      |                   |

| G <sub>BC</sub>                    | Battery Current Sense Gain                | GBC_SEL = 0, Default                                                                                                         |      | 0.2   |      | μA/mV             |

|                                    |                                           | GBC_SEL = 1                                                                                                                  |      | 0.4   |      | μA/mV             |

| A <sub>BC</sub>                    | Battery Voltage Sense Scaling             |                                                                                                                              |      | 2     |      | μA/V              |

| G <sub>AC</sub>                    | Adapter Current Sense Gain                |                                                                                                                              |      | 0.2   |      | μA/mV             |

| A <sub>AC</sub>                    | Adapter Voltage Sense Scaling             |                                                                                                                              |      | 2     |      | μ <b>A</b> /V     |

| K <sub>AC</sub> , K <sub>BC</sub>  | Mixer Gain                                | GAIN_SEL = 0, Default                                                                                                        |      | 250   |      | kA/A <sup>2</sup> |

|                                    |                                           | GAIN_SEL = 1                                                                                                                 |      | 500   |      | kA/A <sup>2</sup> |

| I <sub>PMO</sub>                   | Power Monitor Output Current              | Full Scale                                                                                                                   |      | 100   |      | μА                |

| I <sub>PAC</sub> ,I <sub>PBC</sub> | Power Monitor Accuracy                    | 1.00x Full Scale                                                                                                             | -5   |       | 5    | %                 |

|                                    | per channel                               | 0.10x Full Scale                                                                                                             | -8.5 |       | 8.5  | %                 |

|                                    |                                           | 0.03x Full Scale                                                                                                             | -20  |       | 20   | %                 |

| F <sub>PMO</sub>                   | Power Monitor Bandwidth                   |                                                                                                                              |      | 8     |      | kHz               |

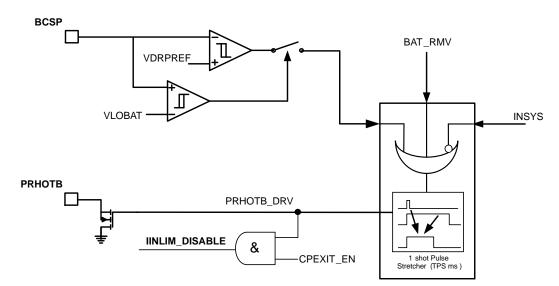

| $V_{DRPREF}$                       | VDRP Fast Comparator Reference<br>Voltage | DRP_SEL = 00, Relative to V <sub>SYSMIN</sub>                                                                                |      | 97    |      | %                 |

|                                    |                                           | DRP_SEL = 01                                                                                                                 |      | 5.6   |      | V                 |

|                                    |                                           | DRP_SEL = 10, Default                                                                                                        |      | 5.8   |      | V                 |

|                                    |                                           | DRP_SEL = 11                                                                                                                 |      | 6     |      | V                 |

|                                    | VDRP Fast Comparator Accuracy             |                                                                                                                              | -2.1 |       | +2.1 | %                 |

|                                    | VDRP Fast Comparator Debounce             |                                                                                                                              |      | 2     |      | μs                |

| $V_{LOBAT}$                        | VDRP Slow Comparator                      | VLOBAT_REG = 00, Ratio of VDRPREF                                                                                            |      | OFF   |      | %                 |

|                                    | Detection Level                           | VLOBAT_REG = 01                                                                                                              |      | 105   |      |                   |

|                                    |                                           | VLOBAT_REG = 10, Default                                                                                                     |      | 107.5 |      |                   |

|                                    |                                           | VLOBAT_REG = 11                                                                                                              |      | 110   |      |                   |

| $T_LBDEB$                          | VDRP Slow Comparator Debounce             |                                                                                                                              |      | 128   |      | ms                |

| I <sub>LBSK</sub>                  | PRHOTB Sink Capability                    | Output 0.4 V                                                                                                                 | 40   |       |      | mA                |

| $T_{LBPS}$                         | Pulse Stretch Duration                    |                                                                                                                              |      | 10    |      | ms                |

| $V_{BAT\_RMV}$                     | Battery Removal Detection                 | BATRMV_SEL = 0, Default                                                                                                      | 2.7  | 2.85  | 3    | V                 |

|                                    | Threshold                                 | BATRMV_SEL = 1                                                                                                               | 1.5  | 1.6   | 1.7  |                   |

|                                    | Battery Removal Detection time            |                                                                                                                              |      | 4     |      | μS                |

| I <sub>BAT_RMV</sub>               | TS Input Leakage                          |                                                                                                                              |      |       | 100  | nA                |

<sup>7. 19</sup> V and 14.5 V versions are available upon request

<sup>8. 2560</sup> mA versions is available upon request

<sup>9. 5.6</sup> V, 12.352 V and 16.592 V versions are available upon request

<sup>10.512</sup> mA, 1024 mA and 2048 mA versions are available upon request

<sup>11. 256</sup> mA, 128 mA and 0 mA versions are available upon request 12.5.6 V, 5.7 V, 5.8 V versions are available upon request

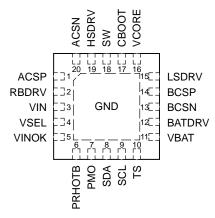

#### **Charging Process**

INCHG\_OK = (INOK and not VINOK\_SEL) or (INMINOK and VINOK\_SEL)

Figure 3. Charging State Machine

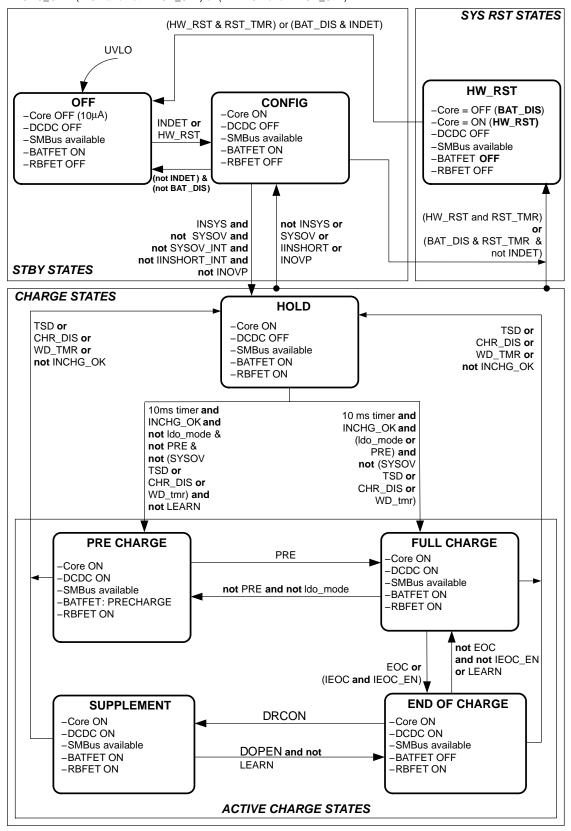

## **Block Diagram**

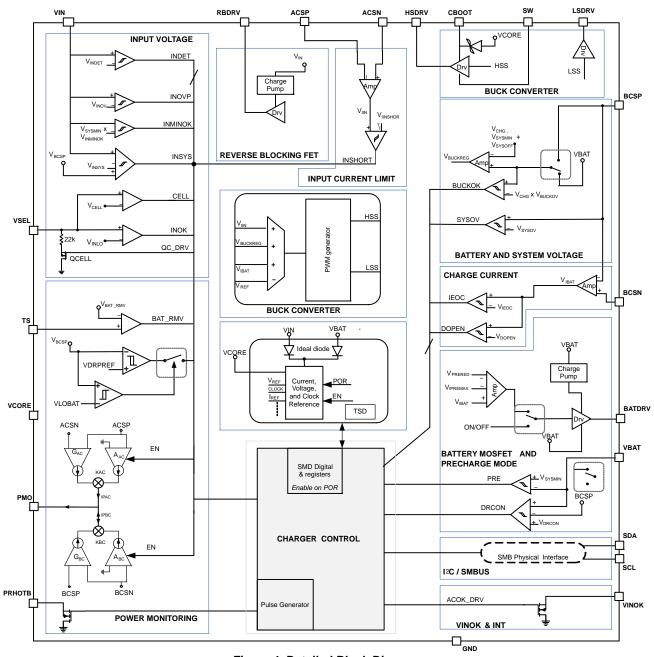

Figure 4. Detailed Block Diagram

# **SMBUS Registers Map**

SMBUS slave address (binary): b0001001x.

|     | ChargeOption Register – Memory Location : 12h |             |               |           |                                                                                            |  |  |  |  |  |

|-----|-----------------------------------------------|-------------|---------------|-----------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit | Туре                                          | Reset       | Name          | RST Value | Function                                                                                   |  |  |  |  |  |

| 0   | RW                                            | POR, TR_OFF | CHR_DIS       | 0         | Charge is suspend when set 1                                                               |  |  |  |  |  |

| 1   | RW                                            | POR, TR_OFF | EOC           | 0         | Set 1 will jump to End of Charge state from FULL charge: signal dictated by the Fuel Gauge |  |  |  |  |  |

| 2   | RW                                            | POR, TR_OFF | IEOC_EN       | 0         | Set 1 enable the charger end of charge detection                                           |  |  |  |  |  |

| 3   | RW                                            | POR, TR_OFF | LEARN         | 0         | Set 1 enable the LEARN mode                                                                |  |  |  |  |  |

| 4   | RW                                            | POR, TR_OFF | PMOBAT_EN     | 0         | Set 1 enable the Battery Power monitoring circuitry                                        |  |  |  |  |  |

| 5   | RW                                            | POR, TR_OFF | PMOAC_EN      | 0         | Set 1 enable the Input Power monitoring circuitry                                          |  |  |  |  |  |

| 6   | RW                                            | POR, TR_OFF | GAIN_SEL      | 0         | Multiplier Gain selection<br>0: Full scale 100 W<br>1: Full scale 50 W                     |  |  |  |  |  |

| 7   | RW                                            | POR, TR_OFF | PMO_IMO_SEL   | 0         | 0 : PMO selected 1: IMO selected                                                           |  |  |  |  |  |

| 8   | RW                                            | POR, TR_OFF | GBC_SEL       | 0         | 0: Battery Current Sense Gain is 10<br>1: Battery Current Sense Gain is 20                 |  |  |  |  |  |

| 9   | RW                                            | POR, TR_OFF | WDTMR_SET[0]  | 1         | Watchdog timer [1:0]:<br>00: Disable                                                       |  |  |  |  |  |

| 10  | RW                                            | POR, TR_OFF | WDTMR_SET[1]  | 0         | - 01: 32s<br>10: 64s<br>11: 128s                                                           |  |  |  |  |  |

| 11  | RW                                            | POR, TR_OFF | FREQ_SEL[0]   | 01        | DCDC frequency selection[1:0]:<br>00: 600 kHz                                              |  |  |  |  |  |

| 12  | RW                                            | POR, TR_OFF | FREQ_SEL[1]   |           | 01: 800 kHz<br>10: 1000 kHz<br>11: 1200 kHz                                                |  |  |  |  |  |

| 13  | RW                                            | POR, TR_OFF | VLOBAT_REG[0] | 0         | Ratio of VDRPREF[1:0]:<br>00: Off                                                          |  |  |  |  |  |

| 14  | RW                                            | POR, TR_OFF | VLOBAT_REG[1] | 1         | - 01: 105%<br>10: 107.5%<br>11: 110%                                                       |  |  |  |  |  |

| 15  | RW                                            | POR, TR_OFF | VDROOP_EN     | 0         | 0: Critical Voltage Monitoring disable 1: Critical Voltage Monitoring enable               |  |  |  |  |  |

|     | ChargeCurrent Register – Memory Location : 14h |             |        |           |                                |  |  |  |  |  |

|-----|------------------------------------------------|-------------|--------|-----------|--------------------------------|--|--|--|--|--|

| Bit | Туре                                           | Reset       | Name   | RST Value | Function                       |  |  |  |  |  |

| 0   | RW                                             | POR, TR_OFF | IPRE_0 | 11        | 00: 0 mA<br>01: 128 mA         |  |  |  |  |  |

| 1   | RW                                             | POR, TR_OFF | IPRE_1 |           | 10: 256 mA<br>11: 512 mA       |  |  |  |  |  |

| 2   | R                                              |             |        |           | Not Used                       |  |  |  |  |  |

| 3   | R                                              |             |        |           | Not Used                       |  |  |  |  |  |

| 4   | R                                              |             |        |           | Not Used                       |  |  |  |  |  |

| 5   | R                                              |             |        |           | Not Used                       |  |  |  |  |  |

| 6   | R                                              |             |        |           | Not Used                       |  |  |  |  |  |

| 7   | RW                                             | POR, TR_OFF | ICHG_0 | 000001    | 000001 : 128 mA (Lower Clamp)  |  |  |  |  |  |

| 8   | RW                                             | POR, TR_OFF | ICHG_1 |           | 111111: 8064 mA (Higher Clamp) |  |  |  |  |  |

| 9   | RW                                             | POR, TR_OFF | ICHG_2 |           | Step : 128 mA                  |  |  |  |  |  |

| 10  | RW                                             | POR, TR_OFF | ICHG_3 |           |                                |  |  |  |  |  |

| 11  | RW                                             | POR, TR_OFF | ICHG_4 |           |                                |  |  |  |  |  |

| 12  | RW                                             | POR, TR_OFF | ICHG_5 |           |                                |  |  |  |  |  |

| 13  | R                                              |             |        |           | Not Used                       |  |  |  |  |  |

| 14  | R                                              |             |        |           | Not Used                       |  |  |  |  |  |

| 15  | R                                              |             |        |           | Not Used                       |  |  |  |  |  |

|     | ChargeVoltage Register – Memory Location : 15h |             |         |           |                                                                 |  |  |  |  |

|-----|------------------------------------------------|-------------|---------|-----------|-----------------------------------------------------------------|--|--|--|--|

| Bit | Type                                           | Reset       | Name    | RST Value | Function                                                        |  |  |  |  |

| 0   | R                                              |             |         |           | Not Used                                                        |  |  |  |  |

| 1   | R                                              |             |         |           | Not Used                                                        |  |  |  |  |

| 2   | R                                              |             |         |           | Not Used                                                        |  |  |  |  |

| 3   | R                                              |             |         |           | Not Used                                                        |  |  |  |  |

| 4   | RW                                             | POR, TR_OFF | VCHG_0  | VSYSMIN + | 00000000000 : 3.328 V                                           |  |  |  |  |

| 5   | RW                                             | POR, TR_OFF | VCHG_1  | VSYSOFF   | 00011010000 : 3.328 V (Lower Clamp)                             |  |  |  |  |

| 6   | RW                                             | POR, TR_OFF | VCHG_2  |           | 10001101010 : 18.080 V (Higher Clamp)<br>11111111111 : 18.080 V |  |  |  |  |

| 7   | RW                                             | POR, TR_OFF | VCHG_3  |           | Step: 16 mV                                                     |  |  |  |  |

| 8   | RW                                             | POR, TR_OFF | VCHG_4  |           |                                                                 |  |  |  |  |

| 9   | RW                                             | POR, TR_OFF | VCHG_5  |           |                                                                 |  |  |  |  |

| 10  | RW                                             | POR, TR_OFF | VCHG_6  |           |                                                                 |  |  |  |  |

| 11  | RW                                             | POR, TR_OFF | VCHG_7  |           |                                                                 |  |  |  |  |

| 12  | RW                                             | POR, TR_OFF | VCHG_8  |           |                                                                 |  |  |  |  |

| 13  | RW                                             | POR, TR_OFF | VCHG_9  |           |                                                                 |  |  |  |  |

| 14  | RW                                             | POR, TR_OFF | VCHG_10 |           |                                                                 |  |  |  |  |

| 15  | R                                              |             |         |           | Not Used                                                        |  |  |  |  |

|     |      |             | ChargeOption2 Register | r – Memory Locati | on : 3Ch                                                           |

|-----|------|-------------|------------------------|-------------------|--------------------------------------------------------------------|

| Bit | Туре | Reset       | Name                   | RST Value         | Function                                                           |

| 0   | RW   | POR, TR_OFF | HW_RST                 | 0                 | Set 1 will disconnect the battery after RST_TMR                    |

| 1   | RW   | POR, TR_OFF | BAT_DIS                | 0                 | Set 1 disconnect the battery when IN unplug until the next IN plug |

| 2   | RW   | POR, TR_OFF | FAULT_MSK              | 0                 | Set 1 Mask fault interuption                                       |

| 3   | RW   | POR, TR_OFF | STATUS_MSK             | 0                 | Set 1 Mask Status interruption                                     |

| 4   | R    |             | STATE[0]               |                   | Charge state [2:0]:<br>000: OFF<br>001: CONFIG                     |

| 5   | R    |             | STATE[1]               |                   | 010: HOLD<br>011: PRECHARGE<br>100: FULLCHARGE                     |

| 6   | R    |             | STATE[2]               |                   | 101: SUPPLEMENT<br>110: END OF CHARGE<br>111: HW_RST               |

| 7   | RW   | POR, TR_OFF | RST_TMR_SET[0]         | 0                 | Reset Timer<br>00: 0 ms<br>01: 512 ms                              |

| 8   | RW   | POR, TR_OFF | RST_TMR_SET[1]         | 1                 | 10: 1024 ms<br>11: 2048 ms                                         |

| 9   | RW   | POR, TR_OFF | FREQ_S_EN              | 0                 | Frequency Spread Spectrum enable 0: Disable 1: Enable              |

| 10  | RW   | POR, TR_OFF | CPEXIT_EN              | 0                 | 0: CP exit disable<br>1: CP exit Enable                            |

| 11  | RW   | POR, TR_OFF | IEOC[0]                | 1                 | 000: 128 mA<br>001: 256 mA<br>010: 384 mA                          |

| 12  | RW   | POR, TR_OFF | IEOC[1]                | 0                 | 011: 512 mA<br>100: 640 mA                                         |

| 13  | RW   | POR, TR_OFF | IEOC[2]                | 0                 | - 101: 768 mA<br>110: 896 mA<br>111: 1024 mA                       |

| 14  | RW   | POR, TR_OFF | LDO_MODE               | 0                 | Set 1 select LDO mode                                              |

| 15  | RW   | POR, TR_OFF | ECO_MODE               | 1                 | 0: No Eco Mode<br>1: Eco Mode                                      |

|     |      |          | Interrupt Register - | Memory Location | : 3Dh                               |

|-----|------|----------|----------------------|-----------------|-------------------------------------|

| Bit | Type | Reset    | Name                 | RST Value       | Function                            |

| 0   | RC   | POR, OFF | EOC_INT              | 0               | Flag End of Charge State is reached |

| 1   | RC   | POR, OFF | PRE_INT              | 0               | Flag Precharge state is reached     |

| 2   | RC   | POR, OFF | LEARNB_INT           | 0               | Flag entering/exiting Learn mode    |

| 3   | RC   | POR, OFF | WDOG_INT             | 0               | Flag a WatchDog Timer expired       |

| 4   | RC   | POR, OFF | IPEAK_INT            | 0               | Flag IPEAK MAX is reached           |

| 5   | RC   | POR, OFF | INOVP_INT            | 0               | Flag VIN> VINOV                     |

| 6   | RC   | POR, OFF | BUCK_OVP_INT         | 0               | Flag BUCK OV                        |

| 7   | R    | POR, OFF | IINSHORT_INT         | 0               | Flag IIN> IINSHORT                  |

| 8   | RC   | POR      | HW_RST_INT           | 0               | Flag HW_RST state and HW_RST=1      |

| 9   | RC   | POR      | BAT_DIS_INT          | 0               | Flag HW_RST state and BAT_DIS=1     |

| 10  | W1C  | POR, OFF | SYSOV_INT            | 0               | Flag System Overvoltage             |

| 11  | RC   | POR, OFF | BAT_RMV_INT          | 0               | Flag battery is removed             |

| 12  | R    |          |                      |                 | Not Used                            |

| 13  | R    |          |                      |                 | Not Used                            |

| 14  | R    |          |                      |                 | Not Used                            |

| 15  | R    |          |                      |                 | Not Used                            |

|     |      |             | MinSysVoltage Register | r – Memory Locatio | n : 3Eh                                                                                 |

|-----|------|-------------|------------------------|--------------------|-----------------------------------------------------------------------------------------|

| Bit | Type | Reset       | Name                   | RST Value          | Function                                                                                |

| 0   | RW   | POR, TR_OFF | VDYNPRE_EN             | 1                  | Dynamic precharge disable     Dynamic precharge enable                                  |

| 1   | RW   | POR, TR_OFF | VINOK_SEL              | 0                  | Control VINOK signal 0: INOK is set by VSEL 1 INOK is set by VSYSMIN                    |

| 2   | R    |             |                        |                    | Not Used                                                                                |

| 3   | R    |             |                        |                    | Not Used                                                                                |

| 4   | R    |             |                        |                    | Not Used                                                                                |

| 5   | R    |             |                        |                    | Not Used                                                                                |

| 6   | R    |             |                        |                    | Not Used                                                                                |

| 7   | RW   | POR, TR_OFF | VSYSMIN_0              | See electrical     | 00000000 : 3.328 V                                                                      |

| 8   | RW   | POR, TR_OFF | VSYSMIN_1              | characteristics    | 00011010 : 3.328 V (Lower Clamp)                                                        |

| 9   | RW   | POR, TR_OFF | VSYSMIN_2              | ]                  | 10001011 : 17.792 V (Higher Clamp)<br>11111111 : 17.792 V                               |

| 10  | RW   | POR, TR_OFF | VSYSMIN_3              | 1                  | Step : 128 mV                                                                           |

| 11  | RW   | POR, TR_OFF | VSYSMIN_4              | 1                  |                                                                                         |

| 12  | RW   | POR, TR_OFF | VSYSMIN_5              | ]                  |                                                                                         |

| 13  | RW   | POR, TR_OFF | VSYSMIN_6              | 1                  |                                                                                         |

| 14  | RW   | POR, TR_OFF | VSYSMIN_7              | 1                  |                                                                                         |

| 15  | RW   | POR, TR_OFF | N_CELL_EN              | 1                  | 0: VSYSMIN default value detection disable<br>1: VSYSMIN default value detection enable |

# Reset Legend:

- OFF: Set bit to RST VALUE when the charging state machine is in OFF state.

- TR\_OFF: Set bit to RST VALUE when the charging state machine transits to OFF state.

- POR: Set bit to RST VALUE on power on reset.

- W1C : Need to write 1 to reset this bit to 0

- RC : Read this bit to reset to 0

|     |      |             | InputCur | rent Register – Memory Lo | ocation : 3Fh                     |

|-----|------|-------------|----------|---------------------------|-----------------------------------|

| Bit | Туре | Reset       | Name     | RST Value                 | Function                          |

| 0   | R    |             |          |                           | Not Used                          |

| 1   | R    |             |          |                           | Not Used                          |

| 2   | R    |             |          |                           | Not Used                          |

| 3   | R    |             |          |                           | Not Used                          |

| 4   | R    |             |          |                           | Not Used                          |

| 5   | R    |             |          |                           | Not Used                          |

| 6   | R    |             |          |                           | Not Used                          |

| 7   | RW   | POR, TR_OFF | IINLIM_0 | 011010                    | 000000: 128 mA                    |

| 8   | RW   | POR, TR_OFF | IINLIM_1 |                           | 000001 : 128 mA (Lower Clamp)     |

| 9   | RW   | POR, TR_OFF | IINLIM_2 |                           | 111111 : 8064 mA<br>Step : 128 mA |

| 10  | RW   | POR, TR_OFF | IINLIM_3 |                           | Stop 1 120 1101                   |

| 11  | RW   | POR, TR_OFF | IINLIM_4 |                           |                                   |

| 12  | RW   | POR, TR_OFF | IINLIM_5 |                           |                                   |

| 13  | R    |             |          |                           | Not Used                          |

| 14  | R    |             |          |                           | Not Used                          |

| 15  | R    |             |          |                           | Not Used                          |

|     |      |             | ChargeOptio | n3 Register – Memory | Location : 40h                                                                        |

|-----|------|-------------|-------------|----------------------|---------------------------------------------------------------------------------------|

| Bit | Туре | Reset       | Name        | RST Value            | Function                                                                              |

| 0   | RW   | POR, TR_OFF | SYSOFF_SEL  | 0                    | VSYS offset selection:<br>0 : 384 mV<br>1 : 256 mV                                    |

| 1   | RW   | POR, TR_OFF | DRP_SEL[0]  | 10                   | VDROOP threshold selection:<br>00 : 97% Relative to V <sub>SYSMIN</sub><br>01 : 5.6 V |

| 2   | RW   | POR, TR_OFF | DRP_SEL[1]  |                      | 10 : 5.8 V<br>11 : 6 V                                                                |

| 3   | RW   | POR, TR_OFF | BATRMV_SEL  | 0                    | Battery removal threshold selection:<br>0:2.85 V<br>1:1.6 V                           |

| 4   | R    |             |             |                      | Not Used                                                                              |

| 5   | R    |             |             |                      | Not Used                                                                              |

| 6   | R    |             |             |                      | Not Used                                                                              |

| 7   | R    |             |             |                      | Not Used                                                                              |

| 8   | R    |             |             |                      | Not Used                                                                              |

| 9   | R    |             |             |                      | Not Used                                                                              |

| 10  | R    |             |             |                      | Not Used                                                                              |

| 11  | R    |             |             |                      | Not Used                                                                              |

| 12  | R    |             |             |                      | Not Used                                                                              |

| 13  | R    |             |             |                      | Not Used                                                                              |

| 14  | R    |             |             |                      | Not Used                                                                              |

| 15  | R    |             |             |                      | Not Used                                                                              |

|     |      |       | Manufact     | urerID Register – M | emory Location : FEh |

|-----|------|-------|--------------|---------------------|----------------------|

| Bit | Type | Reset | Name         | RST Value           | Function             |

| 0   | R    |       | MAN_ID[15:0] | 0                   |                      |

| 1   | R    |       |              | 0                   |                      |

| 2   | R    |       |              | 0                   |                      |

| 3   | R    |       |              | 0                   |                      |

| 4   | R    |       |              | 0                   |                      |

| 5   | R    |       |              | 0                   |                      |

| 6   | R    |       |              | 0                   |                      |

| 7   | R    |       |              | 0                   |                      |

| 8   | R    |       |              | 0                   |                      |

| 9   | R    |       |              | 0                   |                      |

| 10  | R    |       |              | 0                   |                      |

| 11  | R    |       |              | 0                   |                      |

| 12  | R    |       |              | 0                   |                      |

| 13  | R    |       |              | 1                   |                      |

| 14  | R    |       |              | 1                   |                      |

| 15  | R    |       |              | 1                   |                      |

|     |      |       | Devic        | eID Register - Memo | ory Location : FFh |

|-----|------|-------|--------------|---------------------|--------------------|

| Bit | Туре | Reset | Name         | RST Value           | Function           |

| 0   | R    |       | DEV_ID[15:0] | 0                   |                    |

| 1   | R    |       |              | 0                   |                    |

| 2   | R    |       |              | 0                   |                    |

| 3   | R    |       |              | 0                   |                    |

| 4   | R    |       |              | 0                   |                    |

| 5   | R    |       |              | 0                   |                    |

| 6   | R    |       |              | 0                   |                    |

| 7   | R    |       |              | 0                   |                    |

| 8   | R    |       |              | 0                   |                    |

| 9   | R    |       |              | 0                   |                    |

| 10  | R    |       |              | 0                   |                    |

| 11  | R    |       |              | 0                   |                    |

| 12  | R    |       |              | 0                   |                    |

| 13  | R    |       |              | 1                   |                    |

| 14  | R    |       |              | 1                   |                    |

| 15  | R    |       |              | 1                   |                    |

#### **FUNCTIONAL DESCRIPTION**

#### Overview

The NCP1871 is part of On Semiconductor's growing switching battery charger family for wireless and mobile computing. The NCP1871 is a NVDC switching battery charger with characteristics that makes it perfectly suited for 2–stacked battery cell applications such as ultrabooks or tablets.