# 1.8 V 12.288 MHz OmniClock Generator with Single Ended (LVCMOS) Output

The NB3V60113GV3, which is a member of the OmniClock family, is a low power PLL-based clock generator. The device accepts a 6.144 MHz single ended (LVCMOS) reference clock as input. It generates one single ended (LVCMOS) output of 12.288 MHz. The device can be powered down using the Power Down pin (PD#).

#### **Features**

- Member of the OmniClock Family of Programmable Clock Generators

- Operating Power Supply:  $1.8 \text{ V} \pm 0.1 \text{ V}$

- I/O Standards

- Input: 6.144 MHz Reference Clock (LVCMOS)

- Output: 12.288 MHz (LVCMOS)

- Output Drive Current for Single Ended Output: 8 mA

- Power Saving Mode through Power Down Pin

- Temperature Range –40°C to 85°C

- Packaged in 8-Pin WDFN

- These are Pb-Free Devices

# **Typical Application**

• Audio Systems (Lightning Audio Module)

## ON Semiconductor®

www.onsemi.com

WDFN8 CASE 511AT

#### **MARKING DIAGRAM**

V3 = Specific Device Code

M = Date Code

= Pb-Free Device

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 6 of this data sheet.

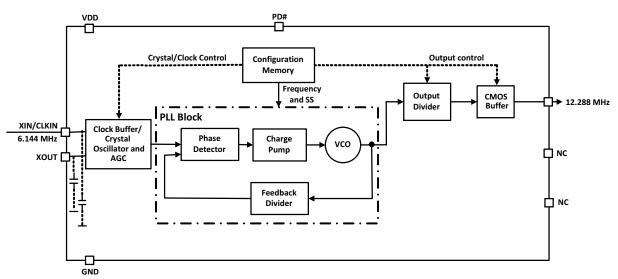

## **BLOCK DIAGRAM**

Figure 1. Simplified Block Diagram

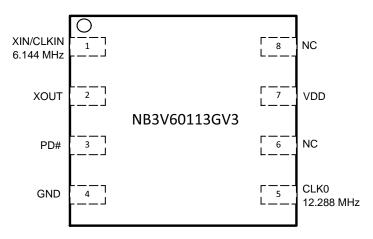

# PIN FUNCTION DESCRIPTION

Figure 2. Pin Connections (Top View) - WDFN8

**Table 1. PIN DESCRIPTION**

| Pin No. | Pin Name  | Pin Type | Description                                                                                                                                                                                   |

|---------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | XIN/CLKIN | Input    | 6.144 MHz single-ended external reference input clock (LVCMOS)                                                                                                                                |

| 2       | XOUT      | Output   | Crystal output. Float this pin when external reference clock is connected at XIN                                                                                                              |

| 3       | PD#       | Input    | Asynchronous LVCMOS input. Active Low Master Reset to disable the device and set outputs Low. Internal pull–down resistor. This pin needs to be pulled High for normal operation of the chip. |

| 4       | GND       | Ground   | Power supply ground                                                                                                                                                                           |

| 5       | CLK0      | Output   | 12.288 MHz Single-ended (LVCMOS) output                                                                                                                                                       |

| 6       | NC        | 1        | No Connection. Not to be connected to any circuit                                                                                                                                             |

| 7       | VDD       | Power    | 1.8 V Power Supply                                                                                                                                                                            |

| 8       | NC        | _        | No Connection. Not to be connected to any circuit                                                                                                                                             |

**Table 2. POWER DOWN FUNCTION TABLE**

| PD# Function |                     |  |

|--------------|---------------------|--|

| 0            | Device Powered Down |  |

| 1            | Device Powered Up   |  |

NOTE: PD# has internal pull down resistor.

**Table 3. ATTRIBUTES**

| Characteristic                                                 | Value                |

|----------------------------------------------------------------|----------------------|

| ESD Protection Human Body Model                                | 2 kV                 |

| Internal Input Default State Pull up/ down Resistor            | 50 kΩ                |

| Moisture Sensitivity, Indefinite Time Out of Dry Pack (Note 1) | MSL1                 |

| Flammability Rating Oxygen Index: 28 to 34                     | UL 94 V-0 @ 0.125 in |

| Transistor Count                                               | 130 k                |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test         |                      |

<sup>1.</sup> For additional information, see Application Note AND8003/D.

Table 4. ABSOLUTE MAXIMUM RATING (Note 2)

| Symbol            | Parameter                                         | Rating             | Unit              |      |

|-------------------|---------------------------------------------------|--------------------|-------------------|------|

| VDD               | Positive power supply with respect to Ground      |                    | -0.5 to +4.6      | V    |

| VI                | Input Voltage with respect to chip ground         |                    | -0.5 to VDD + 0.5 | V    |

| T <sub>A</sub>    | Operating Ambient Temperature Range (Industrial G | irade)             | -40 to +85        | °C   |

| T <sub>STG</sub>  | Storage temperature                               |                    | -65 to +150       | °C   |

| T <sub>SOL</sub>  | Max. Soldering Temperature (10 sec)               |                    | 265               | °C   |

| $\theta_{\sf JA}$ | Thermal Resistance (Junction–to–ambient) (Note 3) | 0 lfpm<br>500 lfpm | 129<br>84         | °C/W |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction-to-case)             |                    | 35 to 40          | °C/W |

| ТJ                | Junction temperature                              |                    | 125               | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and not valid simultaneously. If stress limits are exceeded device functional operation is not implied, damage may occur and reliability may be affected.

JEDEC standard multilayer board – 2S2P (2 signal, 2 power). ESD51.7 type board. Back side Copper heat spreader area 100 sq mm, 2 oz

<sup>(0.070</sup> mm) copper thickness.

## **Table 5. RECOMMENDED OPERATION CONDITIONS**

| Symbol          | Parameter                                      | Condition                         | Min | Тур   | Max | Unit |

|-----------------|------------------------------------------------|-----------------------------------|-----|-------|-----|------|

| V <sub>DD</sub> | Core Power Supply Voltage                      | 1.8 V operation                   | 1.7 | 1.8   | 1.9 | V    |

| CL              | Clock output load capacitance for LVCMOS clock |                                   |     |       | 15  | pF   |

| fclkin          | Reference Clock Frequency                      | Single ended Clock input (LVCMOS) |     | 6.144 |     | MHz  |

| C <sub>X</sub>  | XIN / XOUT pin stray Capacitance               |                                   |     | 4.5   |     | pF   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

Table 6. DC ELECTRICAL CHARACTERISTICS (V<sub>DD</sub> = 1.8 V  $\pm$  0.1 V; GND = 0 V, T<sub>A</sub> =  $-40^{\circ}$ C to  $+85^{\circ}$ C)

| Symbol                | Parameter                 | Condition                          | Min                  | Тур | Max                  | Unit |

|-----------------------|---------------------------|------------------------------------|----------------------|-----|----------------------|------|

| I <sub>DD_1.8 V</sub> | Power Supply current      | fout = 12.288 MHz                  |                      | 13  |                      | mA   |

| I <sub>PD</sub>       | Power Down Supply Current | PD# is Low to make all outputs OFF |                      |     | 20                   | μΑ   |

| V <sub>IH</sub>       | Input HIGH Voltage        | Pin XIN/CLKIN                      | 0.65 V <sub>DD</sub> |     | $V_{DD}$             | V    |

|                       |                           | Pin PD#                            | 0.85 V <sub>DD</sub> |     | $V_{DD}$             |      |

| V <sub>IL</sub>       | Input LOW Voltage         | Pin XIN/CLKIN                      | 0                    |     | 0.35 V <sub>DD</sub> | V    |

|                       |                           | Pin PD#                            | 0                    |     | 0.15 V <sub>DD</sub> |      |

| Cin                   | Input Capacitance         | Pin PD#                            |                      | 4   | 6                    | pF   |

## **LVCMOS OUTPUT**

| $V_{OH}$        | Output HIGH Voltage | V <sub>DD</sub> = 1.8 V | $I_{OH} = 8 \text{ mA}$ | 0.75*V <sub>DD</sub> |                      | V |

|-----------------|---------------------|-------------------------|-------------------------|----------------------|----------------------|---|

| V <sub>OL</sub> | Output LOW Voltage  | V <sub>DD</sub> = 1.8 V | $I_{OL} = 8 \text{ mA}$ |                      | 0.25*V <sub>DD</sub> | V |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Table 7. AC ELECTRICAL CHARACTERISTICS ( $V_{DD}$  = 1.8  $V \pm 0.1$  V, GND = 0 V,  $T_A$  = -40°C to +85°C)

| Symbol          | Parameter                          | Conditions                                                             | Min | Тур    | Max | Unit |

|-----------------|------------------------------------|------------------------------------------------------------------------|-----|--------|-----|------|

| fout            | Single Ended Output Frequency      |                                                                        |     | 12.288 |     | MHz  |

| t <sub>PU</sub> | Stabilization time from Power-up   | V <sub>DD</sub> = 1.8 V                                                |     | 3.0    |     | ms   |

| t <sub>PD</sub> | Stabilization time from Power Down | Time from falling edge on PD# pin to tri–stated outputs (Asynchronous) |     | 3.0    |     | ms   |

| Eppm            | Synthesis Error                    |                                                                        |     | 0      |     | ppm  |

# SINGLE ENDED OUTPUT (V\_DD = 1.8 V $\pm$ 0.1 V; T\_A = -40 $^{\circ}C$ to $85 ^{\circ}C)$

| t <sub>JITTER-1.8</sub> V             | Period Jitter Peak-to-Peak | Configuration Dependent                                                                             |    | 200 |    | ps |

|---------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|----|-----|----|----|

|                                       | Cycle-Cycle Peak Jitter    | Configuration Dependent                                                                             |    | 200 |    |    |

| t <sub>r</sub> / t <sub>f 1.8 V</sub> | Rise/Fall Time             | Measured between 20% to 80% with 15 pF load, f <sub>out</sub> = 12.288 MHz, V <sub>DD</sub> = 1.8 V |    | 1   |    | ns |

| t <sub>DC</sub>                       | Output Clock Duty Cycle    | V <sub>DD</sub> = 1.8 V;<br>Duty Cycle of Ref clock is 50%<br>PLL Clock                             | 45 | 50  | 55 | %  |

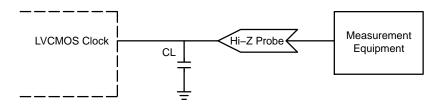

## PARAMETER MEASUREMENT TEST CIRCUIT

Figure 3. LVCMOS Clock Parameter Measurement

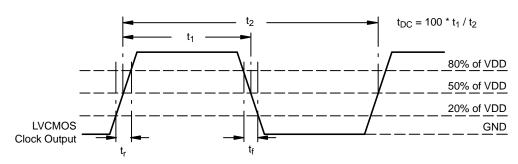

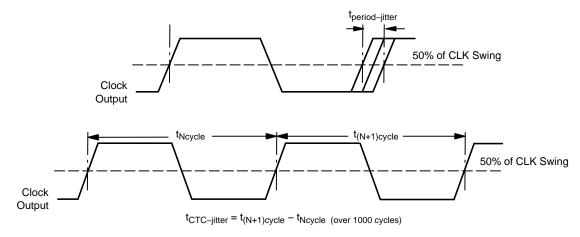

## **TIMING MEASUREMENT DEFINITIONS**

Figure 4. LVCMOS Measurement for AC Parameters

Figure 5. Period and Cycle-Cycle Jitter Measurement

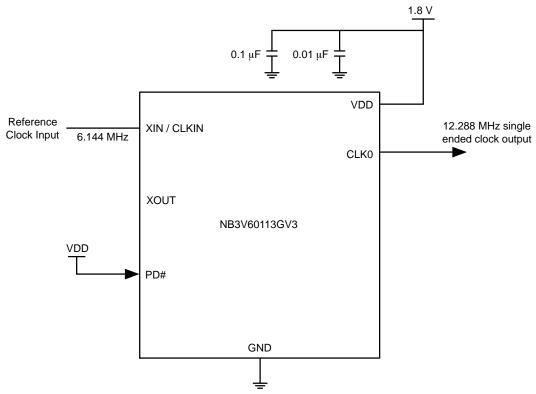

Figure 6. Typical Application Setup

## **ORDERING INFORMATION**

| Device            | Case  | Package            | Shipping <sup>†</sup> |

|-------------------|-------|--------------------|-----------------------|

| NB3V60113GV3MTR2G | 511AT | DFN-8<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

NOTE: Please contact your ON Semiconductor sales representative for information on un-programmed versions of this device.

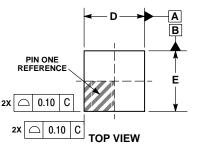

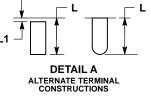

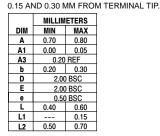

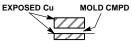

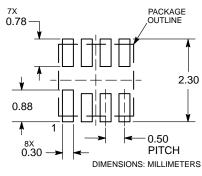

#### PACKAGE DIMENSIONS

## WDFN8 2x2, 0.5P CASE 511AT **ISSUE O**

DIMENSIONING AND TOLERANCING PER

ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS. DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN

DFTAIL B ALTERNATE CONSTRUCTIONS

## **RECOMMENDED SOLDERING FOOTPRINT\***

NOTES:

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

DETAIL B С 0.05 8X \alpha 0.05 C **A1** SEATING PLANE С SIDE VIEW e/2 **DETAIL A** e L2 0.10 С Α В С 0.05 NOTE 3 **BOTTOM VIEW**

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative