# Single 6 A High-Speed, Low-Side SiC MOSFET Driver

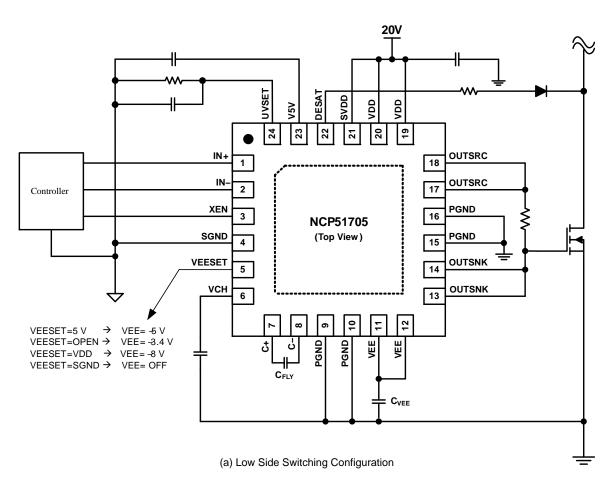

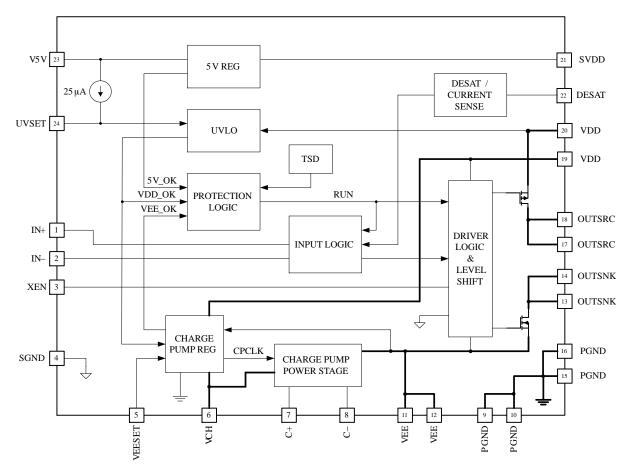

The NCP51705 driver is designed to primarily drive SiC MOSFET transistors. To achieve the lowest possible conduction losses, the driver is capable to deliver the maximum allowable gate voltage to the SiC MOSFET device. By providing high peak current during turn-on and turn-off, switching losses are also minimized. For improved reliability, dV/dt immunity and even faster turn-off, the NCP51705 can utilize its on-board charge pump to generate a user selectable negative voltage rail.

For full compatibility and to minimize the complexity of the bias solution in isolated gate drive applications the NCP51705 also provides an externally accessible 5 V rail to power the secondary side of digital or high speed opto isolators.

The NCP51705 offers important protection functions such as under-voltage lockout monitoring for the bias power and thermal shutdown based on the junction temperature of the driver circuit.

### Features

- High Peak Output Current with Split Output Stages to allow independent Turn-ON/Turn-OFF Adjustment;

- Source Capability: 6 A

- Sink Capability: 6 A

- Extended Positive Voltage Rating for Efficient SiC MOSFET Operation during the Conduction Period

- User-adjustable Built-in Negative Charge Pump for Fast Turn-off and Robust dV/dt Immunity

- Accessible 5 V Reference / Bias Rail for Digital Oscillator Supply

- Adjustable Under-Voltage Lockout

- Desaturation Function

- Thermal Shutdown Function (TSD)

- Small & Low Parasitic Inductance QFN24 Package

### **Typical Applications**

- Driving SiC MOSFET

- Industrial Inverters, Motor Drivers

- PFC. AC to DC and DC to DC Converters

## **ON Semiconductor®**

www.onsemi.com

### ORDERING INFORMATION

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCP51705MNTXG | QFN24<br>(Pb-Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

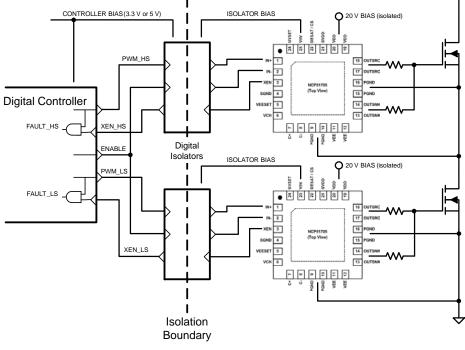

(b) Half Bridge Switching Configuration

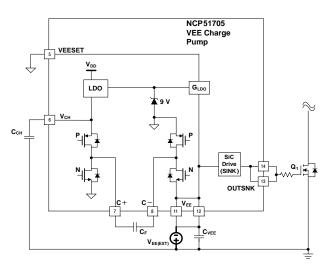

**Figure 1. Typical Application Schematics**

Figure 2. Internal Block Diagram

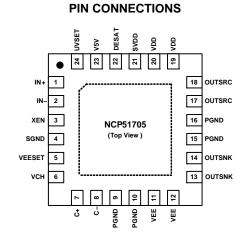

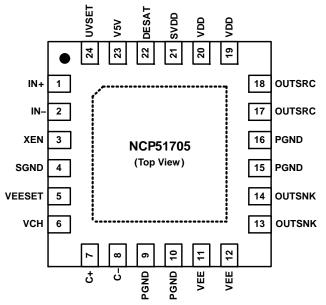

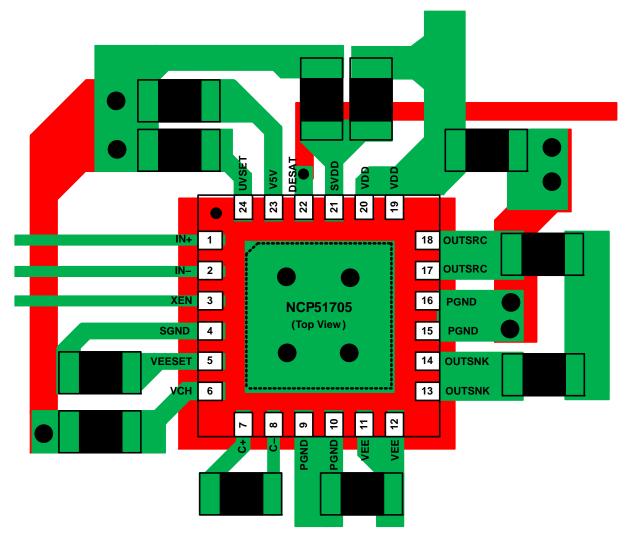

### **PIN CONNECTIONS**

Figure 3. Pin Assignments – 24 Leads QFN (Top View)

### **PIN FUNCTION DESCRIPTION**

| Pin #      | Name   | Description                                                                               |  |

|------------|--------|-------------------------------------------------------------------------------------------|--|

| 1          | IN+    | Input for non-inverting, logic level PWM signal or ENABLE signal.                         |  |

| 2          | IN–    | Input for inverting, logic level PWM signal or DISABLE signal.                            |  |

| 3          | XEN    | Driver state flag. See the application description for details.                           |  |

| 4          | SGND   | Signal ground.                                                                            |  |

| 5          | VEESET | Negative bias voltage select pin.                                                         |  |

| 6          | VCH    | Regulated bias voltage for the charge pump.                                               |  |

| 7          | C+     | Positive node of the flying charge pump capacitor.                                        |  |

| 8          | C-     | Negative node of the flying charge pump capacitor.                                        |  |

| 9,10,15,16 | PGND   | Power ground.                                                                             |  |

| 11,12      | VEE    | Negative drive voltage, the output of the charge pump                                     |  |

| 13,14      | OUTSNK | Pull down drive.                                                                          |  |

| 17,18      | OUTSRC | Pull up drive.                                                                            |  |

| 19,20      | VDD    | Positive bias voltage for the high current driver section.                                |  |

| 21         | SVDD   | Positive bias voltage for the control section of the driver.                              |  |

| 22         | DESAT  | Sense input for the desaturation / current limit input of the driver.                     |  |

| 23         | V5V    | External bypass for 5 V controller bias – suitable to power digital isolators             |  |

| 24         | UVSET  | Input for setting the Under voltage lock out threshold. (minimum operating voltage level) |  |

### **OUTPUT LOGIC**

| IN+        | IN–        | OUTSRC |

|------------|------------|--------|

| 0 (Note 1) | 0          | 0      |

| 0 (Note 1) | 1 (Note 1) | 0      |

| 1          | 0          | 1      |

| 1          | 1 (Note 1) | 0      |

1. Default input signal if no external connection is made.

| Symbol              | Parameter                                         | Min.                 | Max.                 | Unit |

|---------------------|---------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub>     | Power Supply Voltage                              | -0.3                 | 28                   | V    |

| V <sub>V5V</sub>    | Bias Rail                                         | -0.3                 | 5.5                  | V    |

| V <sub>CH</sub>     | Charge Pump Supply Voltage                        | -0.3                 | 10                   | V    |

| $V_{EE}$            | Charge Pump Output; Negative Gate Drive Voltage   | -9                   | +0.3                 | V    |

| V <sub>VEESET</sub> | Charge Pump Output Voltage Select                 | -0.3                 | 28                   | V    |

| $V_{IN+;} V_{IN-}$  | Logic Input Voltage Levels                        | -0.3                 | V5V+0.3              | V    |

| V <sub>UVSET</sub>  | UVLO SET Voltage                                  | -0.3                 | V5V+0.3              | V    |

| $V_{XEN}$           | Logic Output Voltage Levels                       | -0.3                 | V5V+0.3              | V    |

| V <sub>DESAT</sub>  | Desaturation / Current sense voltage              | -0.3                 | 12                   | V    |

| V <sub>C+</sub>     | Positive node of the flying charge pump capacitor | -0.3                 | VCH+0.3              | V    |

| V <sub>C-</sub>     | Negative node of the flying charge pump capacitor | +0.3                 | V <sub>EE</sub> -0.3 | V    |

| VOUTSRC             | Gate Drive Source Output Voltage                  | V <sub>EE</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| V <sub>OUTSNK</sub> | Gate Drive Sink Output Voltage                    | V <sub>EE</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| f <sub>MAX</sub>    | Maximum Operating Frequency (Note 2)              |                      | 500                  | kHz  |

| TJ                  | Junction Temperature                              | -55                  | 150                  | °C   |

| T <sub>STG</sub>    | Storage Temperature                               | -55                  | 150                  | °C   |

### **ABSOLUTE MAXIMUM RATINGS**

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2. Maximum operating frequency refers to ground reference applications and might be limited by power dissipation below the recommended value.

### **THERMAL CHARACTERISTICS**

| Parameters                                    | Symbol                 | Value         | Unit |      |

|-----------------------------------------------|------------------------|---------------|------|------|

|                                               | 1S0P with thermal vias | $\theta_{JA}$ | 127  |      |

| Thermal Characteristics, QFN 4x4 24 Leads     | 1S2P with thermal vias | °JA           | 43   | °C/W |

| Thermal Resistance Junction-Air (Notes 3 & 4) | 1S0P with thermal vias | Ψjt           | 12   | °C/W |

|                                               | 1S2P with thermal vias | ŦJt           | 3.7  |      |

|                                               | 1S0P with thermal vias | _             | 0.98 |      |

| Power Dissipation (Note 4)                    | 1S2P with thermal vias | PD            | 2.9  | W    |

3. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

4. JEDEC standard: JESD51–2, JESD51–3. Mounted on 76.2×114.3×1.6mm PCB (FR–4 glass epoxy material).

1S0P with thermal vias: one signal layer with zero power plane and thermal vias

1S2P with thermal vias: one signal layer with two power plane and thermal vias.

### **ESD CAPABILITY**

| Symbol | Parameter                                  | Value | Unit |

|--------|--------------------------------------------|-------|------|

| ESD    | Human Body Model, JESD22–A114 (Note 5)     | 2000  | V    |

| ESD    | Charged Device Model, JESD22–C101 (Note 5) | 1000  | V    |

5. Meets JEDEC standards JESD 22-A114 and JESD 22-C101.

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol              | Parameter                          | Min. | Max. | Unit |

|---------------------|------------------------------------|------|------|------|

| V <sub>DD</sub>     | Positive Power Supply Voltage      | 10   | 22   | V    |

| $V_{EE}$            | Negative Power Supply Voltage      | -8   | 0    | V    |

| V <sub>CH</sub>     | Charge Pump Power Supply Voltage   | 0    | 8    | V    |

| V <sub>V5V</sub>    | 5 V internal/external bias output  | 0    | 5.5  | V    |

| V <sub>ENA</sub>    | Logic Enable Voltage               | 0    | 5.5  | V    |

| V <sub>IN</sub>     | Logic Input Voltage                | 0    | 5.5  | V    |

| $V_{XEN}$           | Logic Output Voltage               | 0    | 5.5  | V    |

| V <sub>VEESET</sub> | Charge Pump Output Voltage Setting | 0    | 22   | V    |

| V <sub>UVSET</sub>  | UVLO Threshold Setting             | 2    | 3.5  | V    |

| V <sub>DESAT</sub>  | Desaturation Voltage               | 0    | 10   | V    |

| f <sub>SW</sub>     | Operating Frequency (Note 6)       |      | 500  | kHz  |

| T <sub>A</sub>      | Operating Ambient Temperature      | -40  | 125  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.Maximum operating frequency refers to ground referenced applications and might be limited by power dissipation below the recommended

value.

| Symbol                 | Parameters                                                               | Test Conditions                                                                                                              | Min.  | Тур. | Max. | Units |

|------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| VDD Sectior            | 1                                                                        |                                                                                                                              |       |      |      |       |

| I <sub>DD</sub>        | Operating V <sub>DD</sub> Supply Current                                 | f <sub>IN</sub> = 100 kHz                                                                                                    |       | 12   | 18   | mA    |

| I <sub>QDD1</sub>      | Quiescent V <sub>DD</sub> Supply Current 1                               | V <sub>IN</sub> = 0 V or 5 V                                                                                                 |       | 4.5  | 6.5  | mA    |

| I <sub>QDD2</sub>      | Quiescent V <sub>DD</sub> Supply Current 2                               | $V_{IN} = 0 V \text{ or } 5 V$ , VEESET = 0 V                                                                                |       | 0.85 | 1    | mA    |

| IUVSET                 | Source Current for UV Voltage Set                                        | V <sub>UVSET</sub> = 3 V                                                                                                     | 22    | 25   | 28   | μA    |

| V <sub>DDUV+</sub>     | V <sub>DD</sub> Supply Under–Voltage<br>Positive–going Threshold Voltage | V <sub>UVSET</sub> = 3 V                                                                                                     | 17    | 18   | 19   | V     |

| V <sub>DDUV-</sub>     | V <sub>DD</sub> Supply Under–Voltage<br>Negative–going Threshold Voltage | V <sub>UVSET</sub> = 3 V                                                                                                     | 16    | 17   | 18   | V     |

| V <sub>DDHYS</sub>     | V <sub>DD</sub> Supply UVLO Hysteresis Voltage                           | V <sub>DDUV+</sub> – V <sub>DDUV-</sub>                                                                                      |       | 1    |      | V     |

| V <sub>UVSET,MIN</sub> | UVSET pin short protection Threshold Voltage                             | V <sub>UVSET</sub> rising                                                                                                    |       | 1.55 |      | V     |

| V <sub>UVSET,HYS</sub> | UVSET pin short protection Hysteresis                                    |                                                                                                                              |       | 0.2  |      | V     |

| 5V Regulato            | r Section                                                                |                                                                                                                              |       |      |      |       |

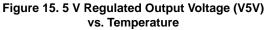

| .,                     |                                                                          | $T_A = 25^{\circ}C$                                                                                                          | 4.9   | 5    | 5.1  | V     |

| $V_{V5V}$              | 5 V Bias (Note 9)                                                        | Total Variation                                                                                                              | 4.75  | 5    | 5.25 | V     |

| V <sub>V5V_Reg</sub>   | 5 V Line Regulation                                                      | 10 V < V <sub>DD</sub> < 22 V, I <sub>OUT</sub> = 10 mA                                                                      |       |      | 50   | m٧    |

|                        | 5 V Load Regulation                                                      | 0.1 mA < I <sub>OUT</sub> < 10 mA                                                                                            |       |      | 50   | m۷    |

| I <sub>5V_MAX</sub>    | Maximum Output Current (Note 10)                                         | for external load                                                                                                            | 20    | 25   |      | mA    |

| VEE Regulat            | tor Section                                                              |                                                                                                                              |       |      |      |       |

| IVEESET                | Input V <sub>EESET</sub> Bias Current                                    |                                                                                                                              |       | 5    |      | μA    |

| V <sub>VCH,MAX</sub>   | Maximum V <sub>CH</sub> Output Voltage (Note 10)                         |                                                                                                                              |       |      | 10   | V     |

| Charge Pum             | p Section                                                                |                                                                                                                              |       |      |      |       |

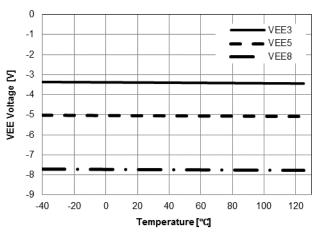

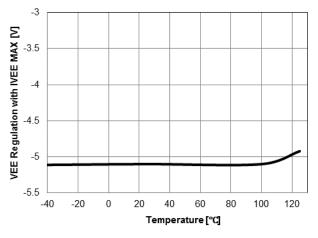

|                        |                                                                          | V <sub>EESET</sub> = 5 V                                                                                                     | - 5.5 | -5   | -4.5 | V     |

| $V_{EE}$               | Negative Bias Rail Voltage                                               | V <sub>EESET</sub> = open                                                                                                    | -3.8  | -3.4 | -3.0 | V     |

|                        |                                                                          | V <sub>EESET</sub> = V <sub>DD</sub>                                                                                         |       | -8   |      | V     |

| $I_{VEE, MAX}$         | Maximum Output Current of V <sub>EE</sub>                                | $\begin{array}{l} C_{FYL} = 0.47 \; \mu\text{F}, \; C_{VEE} = 1.5 \; \mu\text{F} \\ C_{LOAD} = 8.5 \; n\text{F} \end{array}$ |       |      | 50   | mA    |

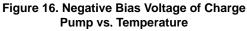

| fosc                   | Oscillator Switching Frequency for Charge Pump                           |                                                                                                                              | 350   | 390  | 430  | kHz   |

| Desaturation           | n Section                                                                |                                                                                                                              |       |      |      | -     |

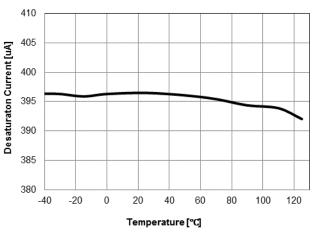

| IDESAT                 | DC Source Current                                                        | V <sub>DESAT</sub> = 0 V                                                                                                     | 360   | 400  | 440  | μA    |

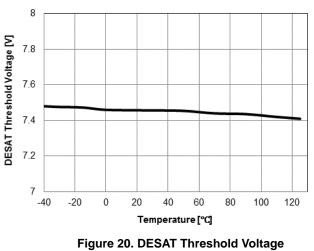

| V <sub>TH,DESAT</sub>  | Desaturation Protection Threshold Voltage                                |                                                                                                                              | 7     | 7.5  | 8    | V     |

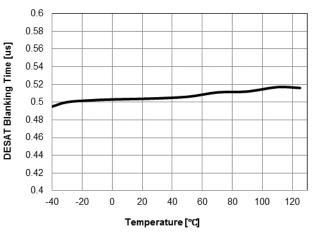

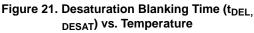

| t <sub>DEL,DESAT</sub> | Blanking Time after turn-on                                              |                                                                                                                              | 350   | 500  | 650  | ns    |

| R <sub>ON,DESAT</sub>  | Active Pull Down Resistance                                              |                                                                                                                              |       | 5    | 10   | Ω     |

| Thermal Shu            | utdown Section                                                           | ·                                                                                                                            | •     | -    | -    |       |

| TSD                    | Thermal ShutDown Temperature (Note 10)                                   |                                                                                                                              | 130   | 150  |      | °C    |

| TSD_HYS                | TSD Hysteresis (Note 10)                                                 |                                                                                                                              | 1     | 25   |      | °C    |

**ELECTRICAL CHARACTERISTICS** (V<sub>DD</sub>=20 V, V<sub>EESET</sub>= 5 V and C<sub>LOAD</sub> = 1000 pF for typical values T<sub>A</sub>=25°C, for min/max values T<sub>A</sub>=-40°C to +125°C, unless otherwise specified.) (Notes 7, 8)

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at T<sub>J</sub> = T<sub>A</sub> = 25°C.

Exclude overshoot voltage at start–up.

This parameter, although guaranteed by design, is not tested in production.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>DD</sub> =20 V, V <sub>EESET</sub> = 5 V and C <sub>LOAD</sub> = 1000 pF for typical values T <sub>A</sub> =25°C, for min/max values |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $T_J=T_A=-40^{\circ}C$ to +125°C, unless otherwise specified.) (Notes 7, 8)                                                                                                    |  |

| Symbol              | Parameters                                       | Test Conditions           | Min. | Тур. | Max. | Units |

|---------------------|--------------------------------------------------|---------------------------|------|------|------|-------|

| Input Logic         | Section; IN+; IN-                                |                           |      |      |      |       |

| VIH                 | High Level Input Voltage                         |                           |      | 1.6  | 2.0  | V     |

| VIL                 | Low Level Input Voltage                          |                           | 0.8  | 1.2  |      | V     |

| VINHYS              | Input Logic Hysteresis                           |                           |      | 0.4  |      | V     |

| I <sub>IN+</sub>    | High Level Logic Input Bias Current              | V <sub>IN+</sub> = 5 V    |      | 50   |      | μA    |

| I <sub>IN-</sub>    | Low Level Logic Input Bias Current               | V <sub>IN-</sub> = 0 V    |      | 50   |      | μA    |

| R <sub>IN+</sub>    | Logic Input Pull–Down Resistance                 |                           | 75   | 100  | 125  | kΩ    |

| R <sub>IN-</sub>    | Logic Input Pull–Up Resistance                   |                           | 75   | 100  | 125  | kΩ    |

| Output Logi         | ic Section; XEN                                  |                           |      |      |      |       |

| V <sub>OHX</sub>    | High Level Output Voltage (V5V–V <sub>OH</sub> ) | I <sub>OUT</sub> = 10 mA  |      | 0    | 0.5  | V     |

| V <sub>OLX</sub>    | Low Level Output Voltage                         | I <sub>OUT</sub> = 10 mA  |      | 0    | 0.2  | V     |

| I <sub>XENH</sub>   | High Level Logic Output Source Current (Note 10) |                           |      |      | 5    | mA    |

| I <sub>XENL</sub>   | High Level Logic Output Sink Current (Note 10)   |                           |      |      | 5    | mA    |

| Gate Driver         | Output Section                                   | _                         | _    | _    | _    |       |

| I <sub>SOURCE</sub> | OUTSRC Source Current (Note 10)                  | OUTSRC = 0 V              |      | 6    |      | А     |

| I <sub>SINK</sub>   | OUTSNK Sink Current (Note 10)                    | OUTSNK = 20 V             |      | 6    |      | А     |

| V <sub>OH</sub>     | High Level Output Voltage (VDD-VOUT)             | I <sub>OUT</sub> = 100 mA |      | 0    | 0.5  | V     |

| V <sub>OL</sub>     | Low Level Output Voltage                         | I <sub>OUT</sub> = 100 mA |      | 0    | 0.2  | V     |

| t <sub>ON</sub>     | Turn-On Propagation Delay Time                   | C <sub>LOAD</sub> = 1 nF  |      | 25   | 50   | ns    |

| t <sub>OFF</sub>    | Turn-Off Propagation Delay Time                  | C <sub>LOAD</sub> = 1 nF  |      | 25   | 50   | ns    |

| t <sub>R</sub>      | Turn–On Rise Time                                | C <sub>LOAD</sub> = 1 nF  |      | 8    | 15   | ns    |

| t <sub>F</sub>      | Turn–Off Fall Time                               | C <sub>LOAD</sub> = 1 nF  |      | 8    | 15   | ns    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at T<sub>J</sub> = T<sub>A</sub> = 25°C.

9. Exclude overshoot voltage at start-up.

10. This parameter, although guaranteed by design, is not tested in production.

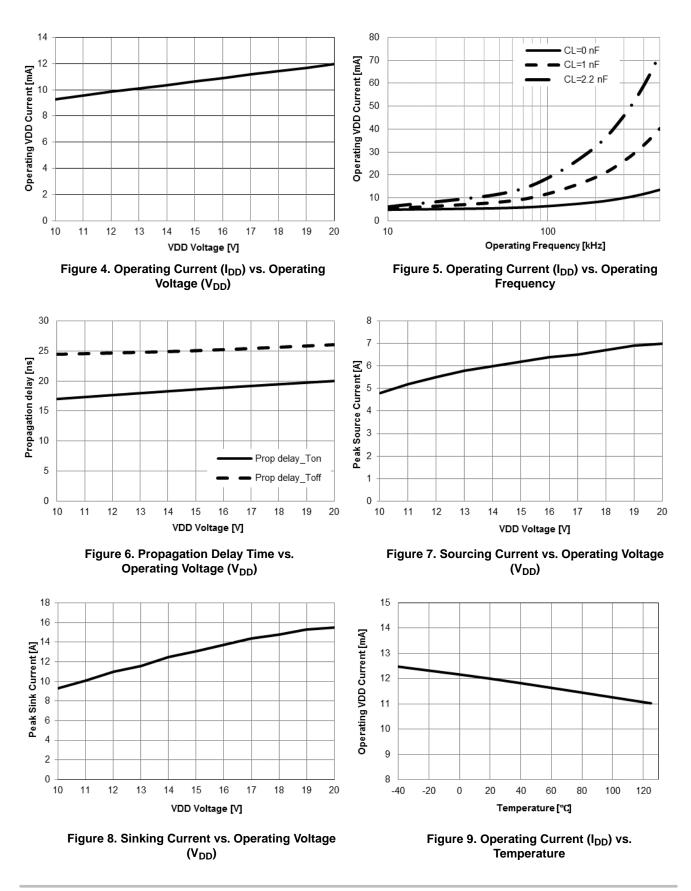

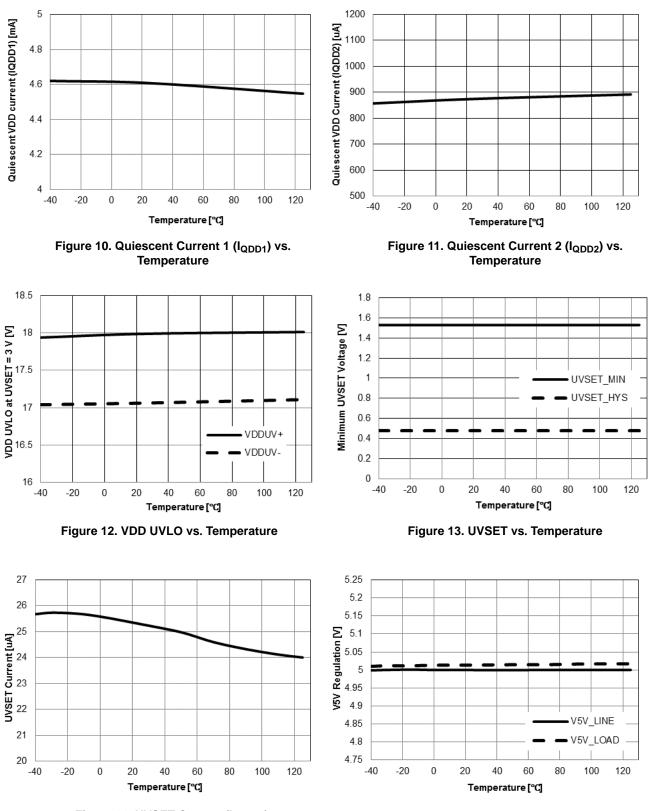

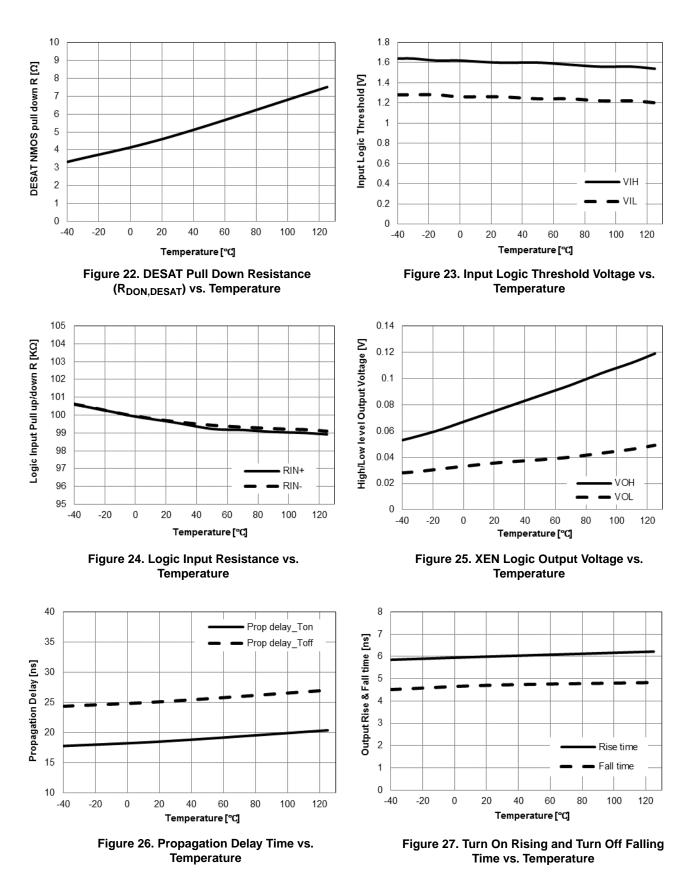

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 18. Charge Pump Operating Frequency (f<sub>OSC</sub>) vs. Temperature

(V<sub>TH,DESAT</sub>) vs. Temperature

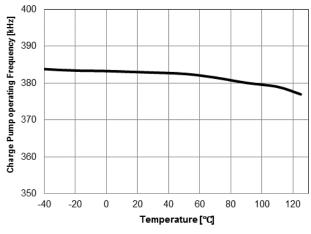

Figure 17. VEE5 Regulated Voltage with I<sub>VEE,MAX</sub> vs. Temperature

Figure 19. Desaturation Current (I<sub>DESAT</sub>) vs. Temperature

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### **APPLICATIONS INFORMATION**

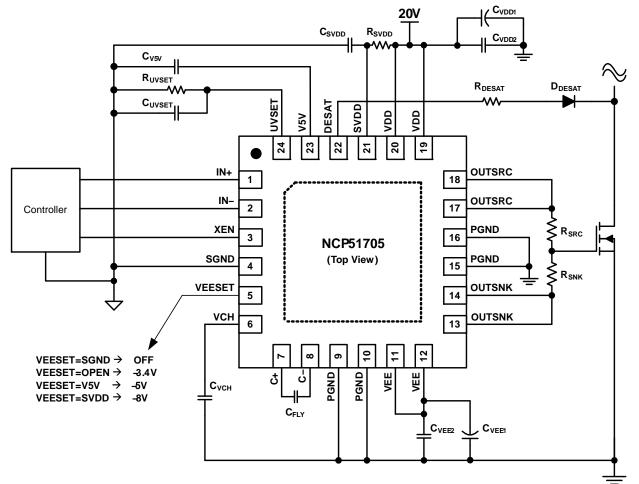

The NCP51705 can be quickly configured by following the steps outlined in this section. The component references

made throughout this section refer to the schematic diagram and reference designations shown in Figure 28.

Figure 28. Application Schematic

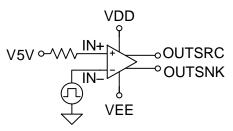

### Input (IN+, IN-)

Both independent PWM inputs are TTL compatible and are internally pulled to the correct states such that each corresponding driver input is defaulted to the inactive (disabled) state. The TTL input thresholds provide buffer and level translation functions from logic inputs. The input thresholds meet industry-standard TTL-logic thresholds, independent of the V<sub>DD</sub> voltage, and there is a hysteresis voltage of approximately 0.4 V. These levels permit the inputs to be driven from a range of input logic signal levels for which a voltage over 2 V is considered logic high. The driving signal for the TTL inputs should have fast rising and falling edges with a slew rate of 6 V/us or faster, so a rise time from 0 to 3.3 V should be 550 ns or less. With reduced slew rate, circuit noise could cause the driver input voltage to exceed the hysteresis voltage and retrigger the driver input, causing erratic operation.

For non-inverting input logic the PWM input signal is applied to IN+ while the IN- input can be used as an enable

function. If IN- is pulled HIGH, the driver output remains LOW, regardless of the state of IN+. To enable the driver output, IN- should be tied to SGND through a 10 k $\Omega$ resistor, as shown in Figure 29, or can be used as an active LOW enable pull down. The start-up logic waveforms shown in Figure 30 illustrate the expected behavior when applying a PWM input signal to the IN+ input while the INinput is pulled LOW to SGND. In this example, the PWM signal is applied prior to the application of VDD. When VDD is greater than  $\sim$  7.5 V, the NCP51705 internal charge pump is enabled and begins switching. The output is only enabled when VDD is greater than the set UVLO ON level (VON) and VEE is less than 80% of the programmed voltage level. The output begins switching corresponding to the next PWM rising edge after both UVLO thresholds have been crossed. This method of edge detection, assures the output accurately represents the PWM input while preventing the output from possibly switching in the middle of an IN+, PWM pulse on-time.

Figure 29. Non-inverting input configuration

| Table 1. No | on-inverting | logic, IN+, | truth table |

|-------------|--------------|-------------|-------------|

|-------------|--------------|-------------|-------------|

| IN+ (PWM                                            | ) IN- (SGN | ID) | OUTS      | SRC | OUTSNK |  |

|-----------------------------------------------------|------------|-----|-----------|-----|--------|--|

| 0                                                   | 0          |     | 0         |     | 1      |  |

| 1                                                   | 0          |     | 1         |     | 0      |  |

| VDD<br>VON<br>7.5 V<br>0 V<br>0 V<br>0.8*VEE<br>VEE |            |     |           |     |        |  |

| IN+<br>0 V                                          |            | ГЛ  | <b>TU</b> | ΥЛ  |        |  |

| IN-(0 V)                                            |            |     |           |     |        |  |

| OUT<br>0 V —                                        |            |     |           |     |        |  |

| VEE                                                 | VE         | E V |           |     | JUUUL  |  |

(EN) (UVLO) (UVLO)

#### Figure 30. Non-inverting start-up logic

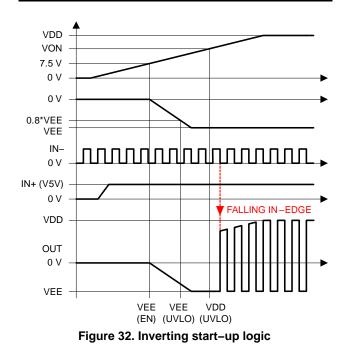

For inverting input logic the PWM input signal is applied to IN- while the IN+ input can be used as an enable function. If IN+ is pulled LOW, the driver output remains LOW, regardless of the state of IN-. To enable the driver output, IN+ should be tied to V5V (5 V) through a 10 k $\Omega$  resistor, as shown in Figure 31, or can be used as an active HIGH enable pull up. The start-up logic waveforms shown in Figure 32 illustrate the expected behavior when applying a PWM input signal to the IN– input while the IN+ input is pulled HIGH to V5V. In this example, the PWM signal is applied prior to the application of VDD. When VDD is greater than 7.5 V, the NCP51705 internal charge pump is enabled and begins switching. The output is only enabled when VDD is greater than the set UVLO ON level (VON) and VEE is less than 80% of the programmed voltage level. The output begins switching corresponding to the next PWM falling edge after both UVLO thresholds have been crossed. This method of edge detection, assures the output accurately represents the PWM input while preventing the output from possibly switching in the middle of an IN-, PWM pulse off-time.

Figure 31. Inverting input configuration

| Table 2. Invo | erting logic | , IN–, | truth table |

|---------------|--------------|--------|-------------|

|---------------|--------------|--------|-------------|

| IN+ (V5V) | IN- (PWM) | OUTSRC | OUTSNK |  |

|-----------|-----------|--------|--------|--|

| 1         | 0         | 1      | 0      |  |

| 1         | 1         | 0      | 1      |  |

### **Driver State Reporting (XEN)**

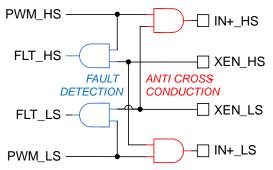

The XEN signal is a 5 V digital output representation of the output state of the NCP51705 driver. XEN is directly derived from the output of the driver and should not be considered as the inverse of the non–inverting logic input to the driver, IN+. The output of the NCP51705 driver can be commanded to its OFF state while the input signal is still HIGH by any of the protection functions of the driver. In such instances, XEN will accurately represent that the river is OFF, independent of the input signal to the device.

The intent of this signal is that it can be used as a fault flag and in half-bridge power topologies, can provide a synchronization signal for implementing cross-conduction (overlap) protection for the power transistors.

Whenever XEN is HIGH,  $V_{GS}$  is LOW and the SiC MOSFET is OFF. Therefore, if XEN and the PWM input signals are both HIGH, a fault condition is detected and can be digitally assigned to take whatever precautions might be desired. XEN can also be used as a control signal for

cross-conduction prevention between a high-side and low-side switch used in a half or full-bridge configuration. The schematic diagram shown in Figure 33 illustrates a circuit example how to utilize the XEN signals for fault detection and cross-conduction prevention. As can be seen in this implementation, the functions are independent and it is up to the designer to decide whether any one or both functions are needed to be implemented in the system.

If XEN\_HS transitions from LOW to HIGH while PWM\_HS is HIGH, the PWM pulse width had been terminated early by one of the protection functions of the NCP51705. The protection function are; any of the Under Voltage Lock–Out (UVLO) protections, Thermal Shut Down (TSD), and Desaturation Detection (DESAT). As Figure 33 indicates a FAULT signal can be generated by a simple AND connection of the PWM input signal and the corresponding XEN output.

In case of cross-conduction prevention, the XEN signal of one driver is used to enable the operation of the other driver as depicted in a simplified manner in Figure 33. The isolation for the high side driver is not shown in the simplified schematic of Figure 33 but the operation of the system can be easily followed. While the high-side driver is ON, XEN\_HS is LOW preventing any gate drive to be applied to the low-side driver. Once the high-side driver turns OFF its XEN\_HS signal transitions to HIGH and the PWM\_LS signal can pass through to the low-side driver. An identical sequence exists to ensure that the high-side driver cannot be turned ON until the low-side driver is OFF.

### Signal Ground (SGND) and Power Ground (PGND)

Signal ground connection (SGND) is the GND for all control logic biased from the 5 V rail (V5V). Internally, the SGND and PGND pins are tied together by two anti–parallel diodes to limit ground bounce difference due to bond wire inductances during the switching actions of the high–current gate drive circuits. It is recommended to connect the SGND and PGND pins together with a short, low–impedance trace on the PCB.

PGND is the reference potential (0 V) for the high-current gate-drive circuit. Two bypass capacitors should be connected between the VDD pin and the PGND pin. One is

the  $V_{DD}$  energy storage capacitor, which provides bias power during startup until the bootstrap power supply comes up. The value of the energy storage capacitor is a strong function of the gate charge requirement of the SiC MOSFET. It is recommended to use a minimum of 1  $\mu$ F to ensure proper operation but the value is primarily dictated by the biasing scheme and startup time of the system. The second capacitor shall be a good–quality ceramic bypass capacitor, located as close as possible to the PGND and VDD pins to filter the high peak currents of the gate driver source circuit. A ceramic bypass capacitor in the range of 10 nF to 100 nF is recommended.

Similarly, two bypass capacitors should be connected between the VEE pin and the PGND pin. One is the  $V_{EE}$ energy storage capacitor, which smoothes the ripple voltage seen at output of the internal charge pump power stage. It is recommended to use a minimum of 470 nF to ensure accurate DC regulation. The second capacitor shall be a good–quality ceramic bypass capacitor, located as close as possible to the PGND and VEE pins to filter the high peak currents of the gate driver sink circuit. A ceramic bypass capacitor in the range of 10 nF to 100 nF is recommended.

Note that the exposed metal pad beneath the IC is thermally conductive but electrically not always connected to GND potential. *Do not connect this pad to SGND or PGND*.

### Programmable VEE Voltage (VEESET)

V<sub>EE</sub> is regulated to the voltage set at V<sub>CH</sub> which is determined by the internal low dropout regulator (LDO) voltage, programmable by the VEESET pin. The NCP51705 offers several convenient pin strapping options for VEESET. If VEESET is left floating (a 100 pF bypass capacitor from VEESET to SGND is recommended), then  $V_{EE}$  is set to regulate at -3 V. For a -5 V  $V_{EE}$  voltage, the VEESET pin should be connected directly to V5V (pin 23). If VEESET is connected to any voltage between 9 V and  $V_{DD}$ , then  $V_{EE}$  is clamped and set to regulate at the minimum charge pump voltage of -8 V. The charge pump starts when  $V_{DD} > 7.5$  V. Additionally, the  $V_{EE}$  voltage rail includes an internally fixed under-voltage lockout (UVLO) set to 80% of the programmed  $V_{EE}$  value. Since  $V_{DD}$  and V<sub>EE</sub> are each monitored by independent UVLO circuits, the NCP51705 is smart enough to realize when both voltage rails are within limits deemed safe for switching a given SiC MOSFET.

Some SiC MOSFETs can operate between 0 V and VDD. For these applications, 0 V<OUT<V<sub>DD</sub> switching can be achieved by disabling the charge pump entirely. When VEESET is connected to SGND and VEE is connected to PGND, the charge pump is disabled. With the charge pump disabled and V<sub>EE</sub> tied directly to PGND, the output switches between 0 V<OUT<V<sub>DD</sub>. During this mode of operation the internal V<sub>EE</sub> UVLO function is also disabled accordingly.

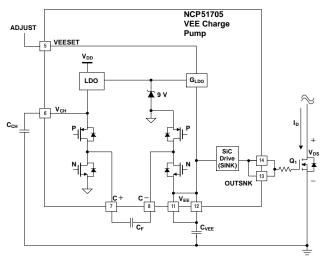

Table 3

Another configuration is to disable the charge pump but allow the use of an external negative  $V_{EE}$  voltage rail. This option permits  $-V_{EE}$ <0UT< $V_{DD}$  switching with a slight savings in IC power dissipation, since the charge pump is not switching. With VEESET connected to SGND, an external negative voltage rail,  $V_{EE(EXT)}$ , can be connected directly between VEE and PGND as shown in (bold highlight) Figure 34.  $V_{EE(EXT)}$  can be supplied from a dedicated bias winding, LDO or an external negative DC power converter. When using an external  $V_{EE(EXT)}$  bias, be mindful that since VEESET is 0 V, the internal  $V_{EE}$  UVLO is disabled and therefore the NCP51705 is unaware if the  $V_{EE}$  voltage level is within or outside of the expected range.

Figure 34. Supplying VEE with negative external voltage bias

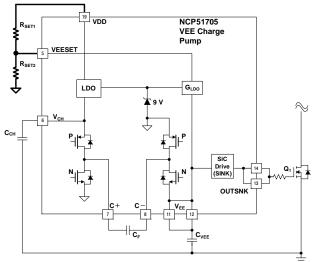

If none of the pin strapping options provide the desired  $V_{EE}$  negative bias voltage, the VEESET pin can be programmed using an external voltage bias. An external LDO from VDD or a simple resistive divider connected between VDD and SGND can be used as shown in (bold highlight) Figure 35.

Figure 35. Applying bias voltage to VEESET

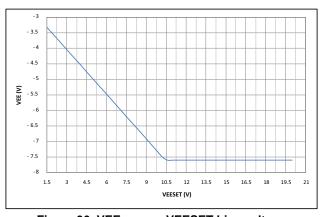

The VEE voltage can programmed from -3.4 V<VEE<-7.6 V for a range of VEESET bias voltage between 1.5 V<VEESET<10.5 V. The absolute minimum programmable VEE voltage is -3 V and can be set by applying 1 V to VEESET, or by simply leaving the VEESET pin floating. For any VEESET voltage greater than 10.5 V, up to VDD, the VEE voltage rail is clamped to an absolute maximum programmable voltage of -7.6 V. The range of programmable VEE negative voltage versus VEESET bias voltage is shown graphically in Figure 36.

Figure 36. VEE versus VEESET bias voltage The configurability of the VEESET pin is summarized in

| Tahla 2  | Summary   | of VEEQET Din  | Configuration |

|----------|-----------|----------------|---------------|

| Table 3. | Summary c | DT VEESE I PIN | Contiduration |

| VEESET              | COMMENT                                                               | V <sub>EE</sub>   | V <sub>EE(UVLO)</sub> |

|---------------------|-----------------------------------------------------------------------|-------------------|-----------------------|

| V <sub>DD</sub>     | 10.5 V <veeset<v<sub>DD</veeset<v<sub>                                | –8 V              | –6.4 V                |

| V5V                 |                                                                       | –5 V              | -4 V                  |

| OPEN                | Add C <sub>VEE</sub> ≤100 pF<br>from VEESET to<br>SGND                | –3.4 V            | -2.72 V               |

| SGND                | Remove $C_{\text{VEE}}$ and connect $\text{V}_{\text{EE}}$ to PGND    | 0 V               | NA                    |

| SGND                | Connect V <sub>EE</sub> to ex-<br>ternal negative volt-<br>age supply | -V <sub>EXT</sub> | NA                    |

| Resistor<br>divider | Resistor divider from V <sub>DD</sub> to SGND                         | Variable          | NA                    |

### Charge Pump Configuration (VCH, C+, C- and VEE)

As can be seen from the charge pump functional block diagram shown in Figure 37, only three external capacitors ( $C_{CH}$ ,  $C_F$  and  $C_{VEE}$ ) are required to establish the negative  $V_{EE}$  voltage rail. The charge pump power stage essentially consists of two PMOS and two NMOS switches arranged in a bridge configuration.

Figure 37. NCP51705 V<sub>EE</sub> Charge Pump

An external flying capacitor,  $C_F$ , is connected between the midpoints of each leg of the bridge as shown. The switching frequency is internally set at 390 kHz. The  $V_{EE}$  output is seen at the VEE pin and is released after  $V_{DD}$ >7 V. Once  $V_{EE}$  exceeds 80% of the set amplitude, the VEE power rail is deemed sufficient and the VEE Under Voltage Lock Out no longer prevents switching.

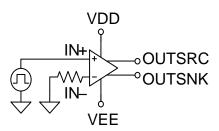

### **Output (OUTSNK and OUTSRC)**

The NCP51705 output is driven by a pure MOS, low-impedance totem pole output stage to ensure full VEE to VDD, rail-to-rail switching. The output slew rate is determined primarily by V<sub>DD</sub>, V<sub>EE</sub> and the C<sub>iss</sub> of the SiC MOSFET. The turn-on (OUTSRC) and turn-off (OUTSNK) functions each have dual dedicated pins. This allows a single resistor between each pin and the SiC MOSFET gate to independently control gate ringing as well as fine tuning dV<sub>DS</sub>/dT turn-on and turn-off transitions present on the SiC drain-source voltage. The driver provides the high peak currents necessary for high-speed switching, even at the higher Miller plateau voltage typical of SiC MOSFETs. The outputs of the NCP51705 (OUTSRC, OUTSNK) are rated to 6 A peak current capability.

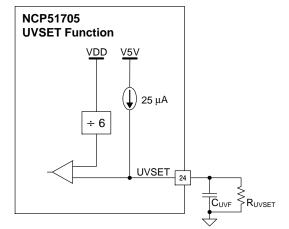

### Programmable Under-Voltage Lockout (UVSET)

UVLO for a gate driver IC is important for protecting the MOSFET by disabling the output until  $V_{DD}$  is above a known threshold. This not only protects the load but verifies to the controller that the applied  $V_{DD}$  voltage is above the turn–on threshold. Because the on–resistance of a SiC MOSFET has a strong dependency on  $V_{GS}$  (and therefore  $V_{DD}$ ), allowing the driver output to switch at low  $V_{DD}$  can

be detrimental for one SiC MOSFET but may be acceptable for another depending on heat–sinking, cooling and  $V_{DD}$ start–up time. The optimal UVLO turn–on threshold can also vary depending on how the  $V_{DD}$  voltage rail is derived. Some power systems may have a dedicated, housekeeping, bias supply while others might rely on a  $V_{DD}$  bootstrapping technique.

The NCP51705 addresses this need through a programmable UVLO turn–on threshold that can be set with a single resistor between UVSET and SGND. As shown in Figure 38, the UVSET pin is internally driven by a 25  $\mu$ A current source. The UVSET resistor, R<sub>UVSET</sub>, is chosen according to a desired UVLO turn–on voltage, V<sub>ON</sub>, as defined by:

$$R_{\text{UVSET}} = \frac{V_{\text{ON}}}{6 \times 25 \ \mu\text{A}} \tag{eq. 1}$$

### Figure 38. NCP51705 UVSET Programmable UVLO

The value for V<sub>ON</sub> is typically determined by referencing the SiC MOSFET voltage versus current, output characteristic curves. Because the on–resistance of a SiC MOSFET dramatically increases even for a slight decrease in V<sub>GS</sub>, the allowable UVLO hysteresis must be small. For this reason, the NCP51705 has a fixed 1 V hysteresis so that the turn–off voltage, V<sub>OFF</sub> is always 1 V less than the set V<sub>ON</sub>. Due to the narrow, 1 V hysteresis band, a small filter capacitor, C<sub>UVF</sub>, is recommended to prevent any periodic or random noise disturbances on the UVSET pin. A ceramic capacitor in the range of 10 nF<C<sub>UVF</sub><100 nF should be placed between UVSET and SGND as close as possible to the IC.

### Positive Bias Voltage (VDD and SVDD)

The positive bias voltage for the driver OUTSRC is provided through VDD. The input bias voltage to the internal 5 V regulator is provided through SVDD. VDD and SVDD should be the same value coming from the same voltage source but they are seperated to allow a small RC filter to be used at the input to SVDD. A small resistor (few  $\Omega$ 's) can be inserted between VDD and SVDD to help prevent any switching noise that might be present on VDD from coupling into the control logic biased by the internal 5 V regulator. In many cases this resistor may not be necessary and VDD can be connected directly to SVDD. However, it is recommended to allow a placeholder on the PCB design to accommodate this resistor until it can be determined if it is needed or not.

For V<sub>DD</sub>>7 V, quiescent current ramps up linearly until the set UVLO threshold, V<sub>ON</sub>, is crossed. After V<sub>DD</sub>>V<sub>ON</sub> and V<sub>EE</sub>>V<sub>EE(UVLO)</sub>, the IC is properly biased to allow output switching. Except for the case when VEESET=SGND (VEE=0 V), both VDD and VEE UVLO conditions must be met before output switching can ensue. Two bypass capacitors must be used between VDD and PGND as detailed in Signal Ground (SGND) and Power Ground (PGND) section.

### **Over-Current Protection (DESAT)**

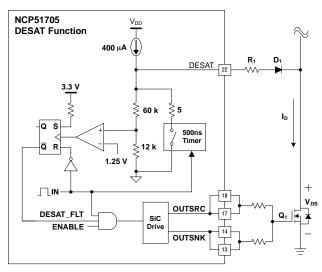

The implementation of the NCP51705 DESAT function can be realized using only two external components. As shown in Figure 39, the drain–source voltage of the SiC MOSFET,  $Q_1$  is monitored via the DESAT pin through  $R_1$ and  $D_1$ .

During the time that  $Q_1$  is off several hundred volts can appear across the drain-source terminals. Once Q1 is turned on, the drain-source voltage rapidly falls and this transition from high-voltage to near zero voltage is expected to happen in less than a few hundred nano-seconds. During the turn-on transition, the leading edge of the DESAT signal is blanked by a 500 ns timer, consisting of a 5  $\Omega$ , low impedance pull-down resistance. This allows sufficient time for V<sub>DS</sub> to fall while at the same time ensuring DESAT is not inadvertently activated. After 500 ns, the DESAT pin is released and the 400 µA current source provides a constant current through R<sub>1</sub>, D<sub>1</sub> and the SiC MOSFET on-resistance. During the on-time, if the DESAT pin rises above 7.5 V, the DESAT comparator output goes HIGH which triggers the clock input of an RS latch. Such a fault will reduce the on-time of the Q\_NOT output on a cycle-by-cycle basis.

The 400  $\mu$ A current source is sufficient to ensure a predictable forward voltage drop across D<sub>1</sub> while also allowing the voltage drop across R<sub>1</sub> to be independent of V<sub>DS</sub> during the on-time of the SiC MOSFET. If desired, DESAT protection can be disabled by connecting the DESAT pin to ground. Conversely, if the DESAT pin is left floating, or R<sub>1</sub> fails open, the 400  $\mu$ A current source flowing through the 12 k $\Omega$  resistor, puts a constant 4.8 V on the non-inverting input of the DESAT comparator. This condition essentially disables the gate drive to the SiC MOSFET. The voltage on the DESAT pin, V<sub>DESAT</sub>, is determined as:

$$V_{\text{DESAT}} = (400 \ \mu\text{A} \times \text{R}_1) + V_{\text{D1}} + (\text{I}_{\text{D}} \times \text{R}_{\text{DS}}) \quad (\text{eq. 2})$$

After assigning the maximum value for  $I_D$  (plus allowing any additional design margin)  $R_1$  and  $I_D$  are selected such that  $V_{DESAT}$ <7.5 V. Solving for  $R_1$  gives:

$$R_{1} = \frac{V_{\text{DESAT}} - V_{\text{D1}} - (I_{\text{D}} \times R_{\text{DS}})}{400 \, \mu \text{A}} \qquad (\text{eq. 3})$$

In addition to setting the maximum allowable  $V_{DS}$ voltage, R1 also serves the dual purpose of limiting the instantaneous current through the junction capacitance of D<sub>1</sub>. Because the drain voltage on the SiC MOSFET sees extremely high dV/dt, the current through the p-n junction capacitance of D<sub>1</sub> can become very high if R<sub>1</sub> is not sized appropriately. Therefore, selecting a fast, high-voltage diode with lowest junction capacitance should be a priority. Typical values for R<sub>1</sub> will be near the range of  $5k\Omega < R_1 < 10k\Omega$  but this can vary according to the I<sub>D</sub> and R<sub>DS</sub> parameters of the selected SiC MOSFET. If R<sub>1</sub> is much smaller than 5 k $\Omega$ , the instantaneous current into the DESAT pin can be hundreds of milliamps, which is problematic to the 400 µA internal DESAT current source. Conversely, if  $R_1$  is much larger than 10 k $\Omega$ , a RC delay ensues as a product of R<sub>1</sub> and the junction capacitance of D<sub>1</sub>. The delay can be on the order of few  $\mu$ s, resulting in an additional delay time responding to an over current condition.

#### 5 V Bias (V5V)

This is the bypass capacitor pin for the internal 5 V bias rail powering the control circuitry. The recommended capacitor value is 2.2  $\mu$ F. At least a 1  $\mu$ F, good–quality, high–frequency, ceramic capacitor should be placed in close proximity to the pin. A smaller ceramic capacitor value such as 100 nF will assure stability but may result in a 500 mV overshoot on the 5 V rail during start–up. The 5 V rail starts to rise approximately 30  $\mu$ s after V<sub>DD</sub> is applied. Once the 7 V threshold is exceeded at the VDD pin, the 5 V rail is enabled. The V5V pin can source up to 10 mA making it suitable for use as a low power bias supply for housekeeping circuits such as open collector pull–up, optocoupler or digital isolator bias.

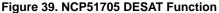

### Applications Information – High–Side Gate Drive Example

Many high–voltage switching applications use power topologies that include high–side, low–side gate drive schemes. Some well known examples include converter topologies such as: LLC, half–bridge and full–bidge. The NCP51705 can be applied in half–bridge (or full–bridge) power topologies such as the one shown in Figure 40. High–voltage applications tend to prefer isolated drivers for both, the high–side and low–side gate drive. This implies the need for two digital isolators. In addition to providing electrical safety and galvanic isolation, the digital isolator assigned to the high–side gate driver, serves the dual purpose of level shifting the IN+ PWM input signal. Since the low–side drive is ground referenced, the digital isolator dedicated to the low-side gate drive is not level shifted and therefore only serves the purpose of electrical safety and galvanic isolation. In this simplified example, IN+ (non-inverting PWM logic) and IN- (active enable) are the only two signals sourced from the digital controller and XEN is read back from the NCP51705. XEN can be used as the timing information basis for developing gate drive timing, cross conduction prevention, dead-time adjustment and fault detection. The V5V from the NCP51705 can be used to power the secondary side of each digital isolator as shown Figure 40.

Figure 41. Recommend PCB drawing

First of all, to optimize operation of SiC gate driving should be minimize influence of the parasitic inductance and capacitance on the layout. The following should be considered before beginning a PCB layout using the NCP51705.

- The SiC driver should be locate as close as possible to the SiC MOSFET.

- VDD, SVDD, V5V, Charge Pump and VEE capacitor should be locate as close as possible to the device.

- When the VEESET = GND, the VEE should be as close as possible to the PGND trace.

- Driver input and DESAT should not going close to the high dV/dT traces. It can cause abnormal operation by significant noise.

- If the device operated in High temperature condition, use the thermal pad as Connecting it to the PGND. But, please be careful that the driver GND trace should not near in the high current path of MOSFET.

- Use wide traces for OUTSRC, OUTSNK and VEE related with main gate driving path.

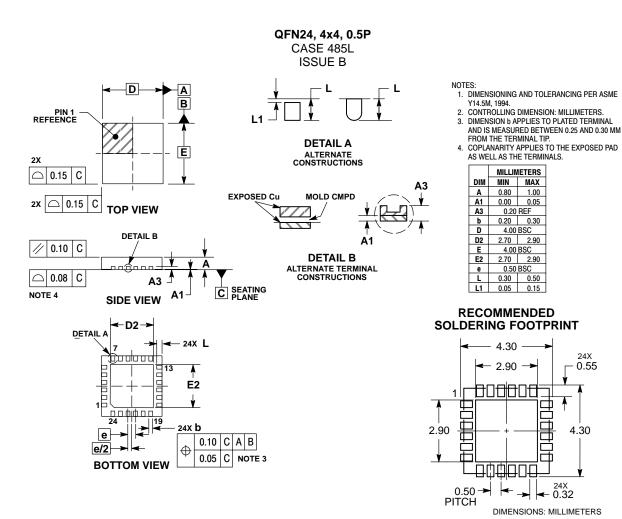

### PACKAGE DIMENSIONS

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights or the rights of others. ON Semiconductor and tesigned, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconducts harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative