# 7 Series FPGAs GTP Transceivers

**User Guide**

UG482 (v1.0) January 3, 2012

#### **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.

#### **Automotive Applications Disclaimer**

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

© Copyright 2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. CPRI is a trademark of Siemens AG. PCI, PCIe and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

## **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                |

|----------|---------|-------------------------|

| 01/03/12 | 1.0     | Initial Xilinx release. |

# Table of Contents

| Revision History                                            | 2  |

|-------------------------------------------------------------|----|

| Preface: About This Guide                                   |    |

| Guide Contents                                              |    |

| Additional Resources                                        |    |

| Additional References                                       | 10 |

| Chapter 1: Transceiver and Tool Overview                    |    |

| Overview and Features                                       | 11 |

| 7 Series FPGAs Transceivers Wizard                          | 16 |

| Simulation                                                  |    |

| Functional Description                                      |    |

| Ports and Attributes                                        |    |

| GTPE2_COMMON Attributes                                     | 18 |

| GTPE2_CHANNEL Attributes                                    | 19 |

| Implementation                                              | 20 |

| Functional Description                                      |    |

| Serial Transceiver Channels by Device/Package               | 21 |

| Chapter 2: Shared Features  Reference Clock Input Structure | 23 |

| Functional Description                                      |    |

| Ports and Attributes                                        |    |

| Use Modes: Reference Clock Termination                      | 25 |

| Reference Clock Selection and Distribution                  | 25 |

| Functional Description                                      |    |

| Ports and Attributes                                        |    |

| External Reference Clock Use Model                          |    |

| Single External Reference Clock Use Model                   |    |

| Multiple External Reference Clock Use Model                 |    |

| PLL                                                         |    |

| Functional Description                                      |    |

| Ports and Attributes                                        |    |

| Loopback                                                    |    |

| Functional Description                                      |    |

|                                                             |    |

| Dynamic Reconfiguration Port                                |    |

| Functional Description                                      |    |

| Ports and Attributes                                        |    |

| Write Operation                                             |    |

| Read Operation                                              | Δ1 |

## **Chapter 3: Transmitter**

| TX Overview                                        | 43 |

|----------------------------------------------------|----|

| Functional Description                             |    |

| FPGA TX Interface                                  |    |

| Functional Description                             |    |

| Interface Width Configuration                      |    |

| TXUSRCLK and TXUSRCLK2 Generation                  |    |

| Ports and Attributes                               | 45 |

| Using TXOUTCLK to Drive the TX Interface           | 46 |

| TXOUTCLK Driving GTP Transceiver TX in 2-Byte      |    |

| TXOUTCLK Driving GTP Transceiver TX in 4-Byte Mode | 49 |

| TX 8B/10B Encoder                                  | 5  |

| Functional Description                             | 5  |

| 8B/10B Bit and Byte Ordering                       |    |

| K Characters                                       |    |

| Running Disparity                                  |    |

| Ports and Attributes                               |    |

| Enabling and Disabling 8B/10B Encoding             | 54 |

| TX Gearbox                                         |    |

| Functional Description                             |    |

| Ports and Attributes                               |    |

| Enabling the TX Gearbox                            |    |

| TX Gearbox Bit and Byte Ordering                   |    |

| TX Gearbox Operating Modes                         |    |

| External Sequence Counter Operating Mode           |    |

| Internal Sequence Counter Operating Mode           | 60 |

| TX Buffer                                          | 63 |

| Functional Description                             | 63 |

| Ports and Attributes                               | 64 |

| Using the TX Buffer                                | 65 |

| TX Buffer Bypass                                   | 6! |

| Functional Description                             | 65 |

| Ports and Attributes                               |    |

| TX Pattern Generator                               | 60 |

| Functional Description                             |    |

| Ports and Attributes                               |    |

| Use Models                                         |    |

| TX Polarity Control                                |    |

| Functional Description                             |    |

| Ports and Attributes                               |    |

| Using TX Polarity Control                          |    |

| ,                                                  |    |

| TX Fabric Clock Output Control                     |    |

| Functional Description                             |    |

| Parallel Clock Divider and Selector                |    |

| Parallel Clock Divider and Selector                |    |

|                                                    |    |

| TX Phase Interpolator PPM Controller               |    |

| Functional Description                             |    |

| Ports and Attributes                               |    |

| TX Phase Interpolator PPM Controller Use Mode      | 7  |

| TX Configurable Driver                             |     |

|----------------------------------------------------|-----|

| Functional Description                             |     |

| Ports and Attributes                               |     |

| TX Receiver Detect Support for PCI Express Designs |     |

| Functional Description                             |     |

| Ports and Attributes                               |     |

| Using the TX Receiver Detection for PCI Express    |     |

| TX Out-of-Band Signaling                           |     |

| Functional Description                             |     |

| Ports and Attributes                               | 90  |

| Chapter 4: Receiver                                |     |

| RX Overview                                        | 03  |

| Functional Description                             |     |

| *                                                  |     |

| RX Analog Front End                                |     |

| Ports and Attributes                               |     |

| Use Modes—RX Termination                           |     |

| RX Out-of-Band Signaling                           |     |

| Functional Description                             |     |

| Ports and Attributes                               |     |

| RX Equalizer                                       |     |

| Functional Description                             |     |

| Ports and Attributes                               |     |

| RX CDR                                             |     |

| Functional Description                             |     |

| Ports and Attributes                               |     |

| RX Fabric Clock Output Control                     |     |

| Functional Description                             |     |

| Serial Clock Divider                               |     |

| Parallel Clock Divider and Selector                |     |

| Ports and Attributes                               | 107 |

| RX Margin Analysis                                 | 108 |

| Functional Description                             |     |

| Eye Scan Theory                                    | 109 |

| Eye Scan Architecture                              |     |

| Ports and Attributes                               | 113 |

| RX Polarity Control                                |     |

| Functional Description                             |     |

| Ports and Attributes                               |     |

| Using RX Polarity Control                          |     |

| RX Pattern Checker                                 |     |

| Functional Description                             |     |

| Ports and Attributes                               |     |

| Use Models                                         |     |

| RX Byte and Word Alignment                         |     |

| Functional Description                             |     |

| Enabling Comma Alignment                           |     |

| Configuring Comma Patterns                         | 120 |

| Alignment Status Signals                                | 121 |

|---------------------------------------------------------|-----|

| Manual Alignment                                        |     |

| Ports and Attributes                                    | 125 |

| RX 8B/10B Decoder                                       | 129 |

| Functional Description                                  | 129 |

| 8B/10B Bit and Byte Ordering                            |     |

| RX Running Disparity                                    |     |

| Special Characters                                      |     |

| Ports and Attributes                                    | 132 |

| Enabling and Disabling 8B/10B Decoding                  | 134 |

| RX Buffer Bypass                                        | 134 |

| Functional Description                                  |     |

| Ports and Attributes                                    |     |

| RX Elastic Buffer                                       |     |

| Functional Description                                  |     |

| Ports and Attributes                                    |     |

| Using the RX Elastic Buffer                             |     |

| ~                                                       |     |

| RX Clock Correction                                     |     |

| Functional Description                                  |     |

| Ports and Attributes                                    |     |

| Using RX Clock Correction                               |     |

| Enabling Clock Correction                               |     |

| Setting RX Elastic Buffer Limits                        |     |

| Setting Clock Correction Sequences                      |     |

| Clock Correction Options                                |     |

|                                                         |     |

| RX Channel Bonding                                      |     |

| Functional Description                                  |     |

| Ports and Attributes                                    |     |

| Using RX Channel Bonding                                |     |

| Enabling Channel Bonding                                |     |

| Channel Bonding Mode                                    |     |

| Connecting Channel Bonding Ports                        |     |

| Setting Channel Bonding Sequences                       |     |

| Setting the Maximum Skew                                |     |

| Precedence between Channel Bonding and Clock Correction |     |

| RX Gearbox                                              |     |

| Functional Description                                  |     |

| Ports and Attributes                                    |     |

| Enabling the RX Gearbox                                 |     |

| RX Gearbox Operating Modes                              |     |

| RX Gearbox Block Synchronization                        | 171 |

| FPGA RX Interface                                       | 174 |

| Functional Description                                  |     |

| Interface Width Configuration                           |     |

| RXUSRCLK and RXUSRCLK2 Generation                       | 175 |

| Ports and Attributes                                    | 176 |

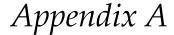

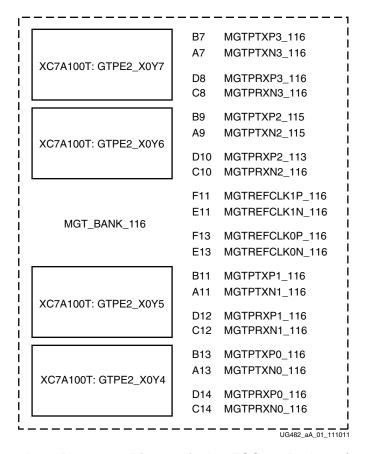

| Appendix A: | Placement Information by Package       |     |

|-------------|----------------------------------------|-----|

| FGG67       | 6 Package Placement Diagram            | 180 |

| Appendix B: | Placement Information by Device        |     |

| Appendix C: | 8B/10B Valid Characters                |     |

| Appendix D: | DRP Address Map of the GTP Transceiver |     |

## About This Guide

Xilinx® 7 series FPGAs include three unified FPGA families that are all designed for lowest power to enable a common design to scale across families for optimal power, performance, and cost. The Artix<sup>TM</sup>-7 family is optimized for lowest cost and absolute power for the highest volume applications. The Virtex®-7 family is optimized for highest system performance and capacity. The Kintex<sup>TM</sup>-7 family is an innovative class of FPGAs optimized for the best price-performance. This guide serves as a technical reference describing the 7 series FPGAs GTP transceivers.

The 7 series FPGAs GTP transceivers user guide, part of an overall set of documentation on the 7 series FPGAs, is available on the Xilinx website at www.xilinx.com/7.

#### In this document:

- 7 series FPGAs GTP transceiver channel is abbreviated as GTP transceiver.

- GTPE2\_CHANNEL is the name of the instantiation primitive that instantiates one GTP transceiver channel.

- GTPE2\_COMMON is the name of the primitive that instantiates two ring oscillator PLLs (PLL0 and PLL1).

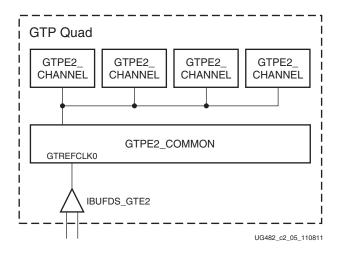

- A Quad or Q is a cluster or set of four GTP transceiver channels, one GTPE2\_COMMON primitive, two differential reference clock pin pairs, and analog supply pins.

## **Guide Contents**

#### This manual contains:

- Chapter 1, Transceiver and Tool Overview

- Chapter 2, Shared Features

- Chapter 3, Transmitter

- Chapter 4, Receiver

- Appendix A, Placement Information by Package

- Appendix B, Placement Information by Device

- Appendix C, 8B/10B Valid Characters

- Appendix D, DRP Address Map of the GTP Transceiver

#### **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/support/documentation/index.htm.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

#### **Additional References**

These documents provide additional information useful to this document:

High-Speed Serial I/O Made Simple http://www.xilinx.com/publications/archives/books/serialio.pdf

# Transceiver and Tool Overview

#### **Overview and Features**

The 7 series FPGAs GTP transceiver is a power-efficient transceiver, supporting line rates between 500 Mb/s and 6.6 Gb/s. The GTP transceiver is highly configurable and tightly integrated with the programmable logic resources of the FPGA. Table 1-1 summarizes the features by functional group that support a wide variety of applications.

Table 1-1: 7 Series FPGAs Transceiver Features

| Group | Feature                                                                                | GTP | GTX | GTH |

|-------|----------------------------------------------------------------------------------------|-----|-----|-----|

| PCS   | 2-byte internal datapath                                                               | х   | х   | х   |

|       | 4-byte internal datapath                                                               |     | х   | х   |

|       | 8B/10B encoding and decoding                                                           | Х   | х   | Х   |

|       | 64B/66B and 64B/67B support                                                            | х   | х   | х   |

|       | Comma detection and byte and word alignment                                            | х   | х   | х   |

|       | PRBS generator and checker                                                             | Х   | х   | Х   |

|       | FIFO for clock correction and channel bonding                                          | х   | х   | х   |

|       | Programmable FPGA logic interface                                                      | х   | х   | х   |

| PMA   | One shared LC tank PLL per Quad                                                        |     | х   | х   |

|       | One ring oscillator PLL per channel                                                    |     | х   | х   |

|       | Two shared ring oscillator PLLs per Quad                                               | х   |     |     |

|       | Flexible reference clocking options                                                    | Х   | х   | х   |

|       | Decision feedback equalization (DFE)                                                   |     | х   | х   |

|       | Power-efficient adaptive linear equalizer mode called the low-power mode (LPM)         | х   | х   | х   |

|       | TX Pre-emphasis                                                                        | Х   | х   | Х   |

|       | Beacon signaling for PCI Express® designs                                              | х   | х   | х   |

|       | Out-of-band (OOB) signaling including COM signal support for Serial ATA (SATA) designs | х   | x   | х   |

|       | RX Margin Analysis                                                                     | Х   | х   | Х   |

The GTP transceiver supports these use modes:

- PCI Express, Revision 1.1/2.0

- Interlaken

- 10 Gb Attachment Unit Interface (XAUI), Reduced Pin eXtended Attachment Unit Interface (RXAUI)

- Common Packet Radio Interface (CPRI<sup>TM</sup>)/Open Base Station Architecture Initiative (OBSAI)

- OC-48

- OTU-1

- Serial RapidIO (SRIO)

- Serial Advanced Technology Attachment (SATA)/Serial Attached SCSI (SAS)

- Serial Digital Interface (SDI)

In comparison to prior generation transceivers in Spartan®-6 FPGAs, the GTP transceiver in the 7 series FPGAs has the following new or enhanced features:

- 2-byte internal datapath

- Two ring oscillator PLLs per Quad

- Power-efficient, adaptive continuous time linear equalizer (CTLE)

- RX margin analysis feature to provide non-destructive, 2-D post-equalization eye scan.

The first-time user is recommended to read *High-Speed Serial I/O Made Simple* [Ref 1], which discusses high-speed serial transceiver technology and its applications. The CORE Generator™ tool includes a wizard to automatically configure GTP transceivers to support configurations for different protocols or perform custom configuration. The GTP transceiver offers a data rate range and features that allow physical layer support for various protocols.

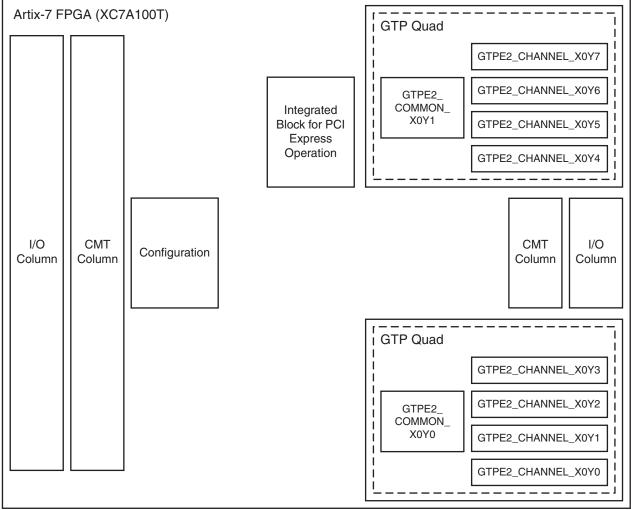

Figure 1-1, page 13 shows the GTP transceiver placement in an example Artix<sup>TM</sup>-7 device (XCA100T). This device has 8 GTP transceivers.

UG482\_C1\_01\_110811

Figure 1-1: GTP Transceiver Inside Artix-7 XC7A100T FPGA

Additional information on the functional blocks of 7 series FPGAs is available at:

<u>UG470</u>, 7 Series FPGAs Configuration User Guide provides more information on the configuration and clocking.

<u>UG471</u>, 7 *Series FPGAs SelectIO Resources User Guide* provides more information on the I/O blocks.

<u>UG472</u>, 7 Series FPGAs Clocking Resources User Guide provides more information on the mixed mode clock manager (MMCM).

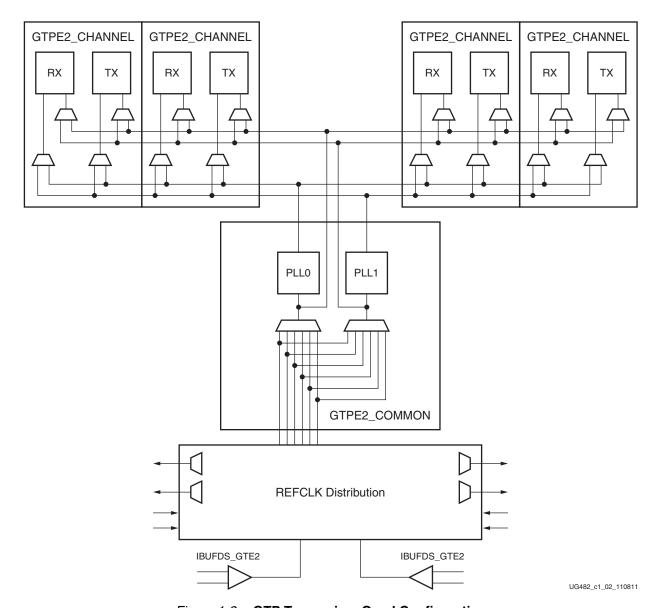

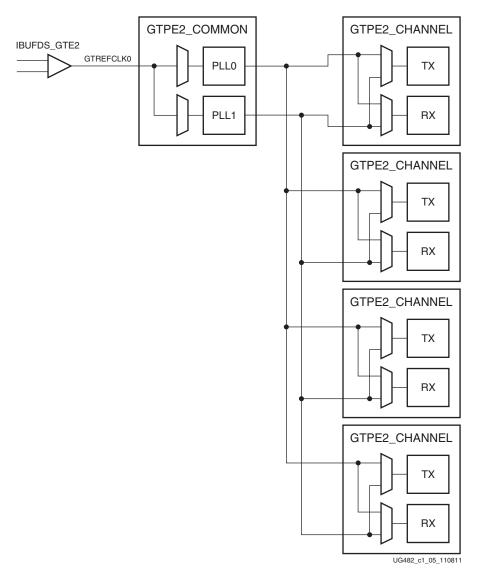

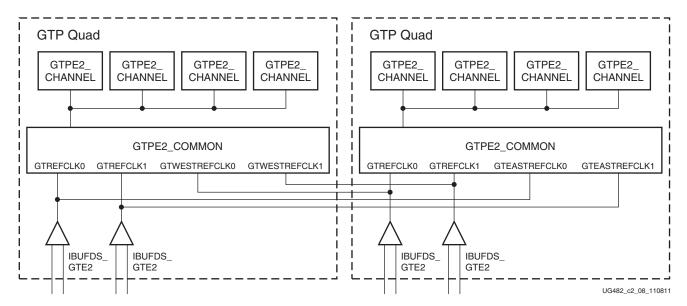

Figure 1-2 illustrates the clustering of four GTPE2\_CHANNEL primitives and one GTPE2\_COMMON primitive to form a Quad.

Figure 1-2: GTP Transceiver Quad Configuration

Four GTPE2 channels clustered together with one GTPE2\_COMMON primitive are called a *Quad* or *Q*.

The GTPE2\_COMMON primitive contains two ring oscillator PLLs (PLL0 and PLL1). GTPE2\_COMMON must always be instantiated.

Each GTPE2\_CHANNEL primitive consists of a transmitter and a receiver.

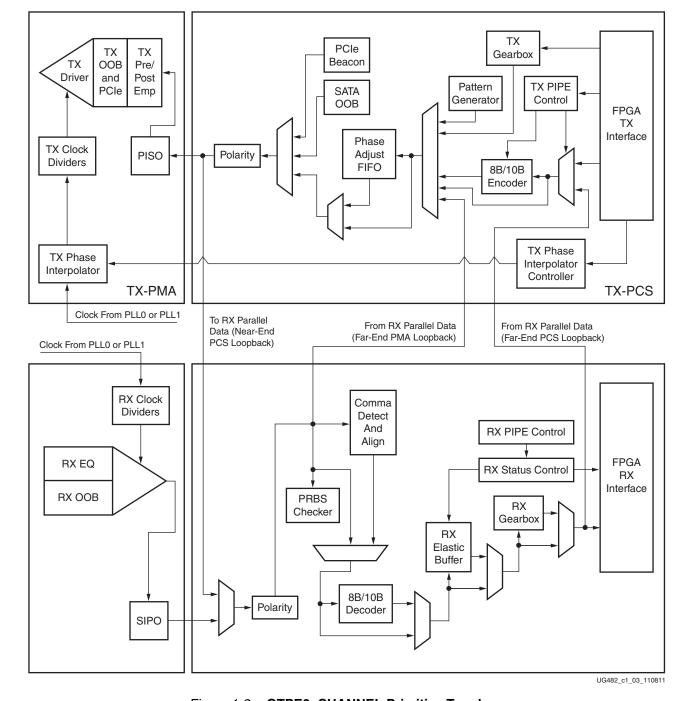

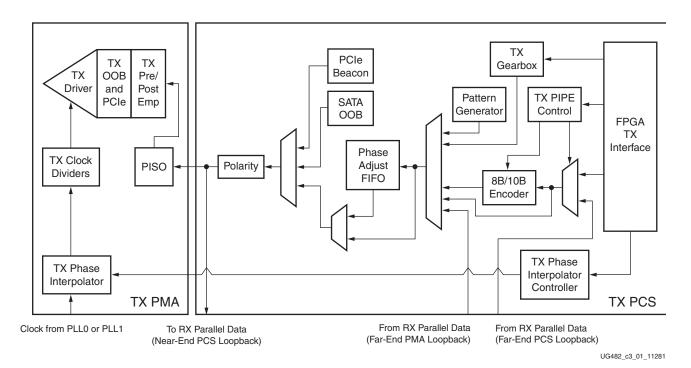

Figure 1-3 illustrates the topology of a GTPE2\_CHANNEL primitive.

Figure 1-3: GTPE2\_CHANNEL Primitive Topology

Refer to Figure 2-9, page 35 for the description of the channel clocking architecture, which provides clocks to the RX and TX clock dividers.

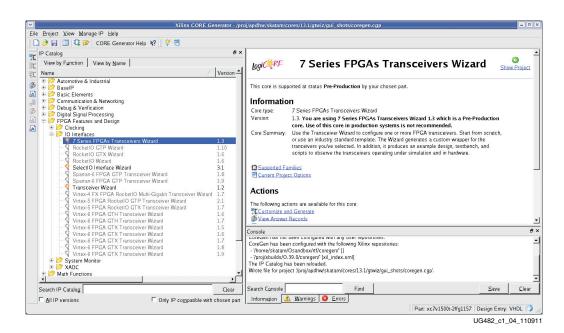

#### 7 Series FPGAs Transceivers Wizard

The 7 Series FPGAs Transceivers Wizard (hereinafter called the Wizard) is the preferred tool to generate a wrapper to instantiate GTP transceiver primitives called GTPE2\_COMMON and GTPE2\_CHANNEL. The Wizard is located in the CORE Generator tool. The user is recommended to download the most up-to-date IP update before using the Wizard. Details on how to use this Wizard can be found in <a href="https://linearchy.com/uccept/9/LogiCORE"><u>UG769</u></a>, <a href="https://linearchy.com/uccept/9/LogiCORE"><u>LogiCORE IP 7 Series FPGAs Transceivers Wizard User Guide</u></a>.

Follow these steps to launch the Wizard:

- 1. Start the CORE Generator tool.

- 2. Locate the 7 Series FPGAs Transceivers Wizard in the taxonomy tree under:

/FPGA Features & Design/IO Interfaces See Figure 1-4.

Figure 1-4: 7 Series FPGAs Transceivers Wizard

3. Double-click 7 Series FPGAs Transceivers Wizard to launch the Wizard.

#### **Simulation**

## Functional Description

Simulations using the GTPE2\_CHANNEL and GTPE2\_COMMON primitives have specific prerequisites that the simulation environment and the test bench must fulfill. For instructions on how to set up the simulation environment for supported simulators depending on the used hardware description language (HDL), see the latest version of UG626, Synthesis and Simulation Design Guide. This design guide can be downloaded from the Xilinx website.

The prerequisites for simulating a design with the GTPE2\_CHANNEL and GTPE2\_COMMON primitives are:

- A simulator with support for SecureIP models.

- SecureIP models are encrypted versions of the Verilog HDL used for implementation of the modeled block. SecureIP is an IP encryption methodology. To support SecureIP models, a Verilog LRM IEEE Std 1364-2005 encryption compliant simulator is required.

- A mixed-language simulator for VHDL simulation.

SecureIP models use a Verilog standard. To use them in a VHDL design, a mixed-language simulator is required. The simulator must be able to simulate VHDL and Verilog simultaneously.

- An installed GTP transceiver SecureIP model.

- The correct setup of the simulator for SecureIP use (initialization file, environment variables).

- The ability to run COMPXLIB, which compiles the simulation libraries (e.g., UNISIM, SIMPRIMS) in the correct order.

- The correct simulator resolution (Verilog).

- The user guide of the simulator and <u>UG626</u>, *Synthesis and Simulation Design Guide* provide a detailed list of settings for SecureIP support.

#### Ports and Attributes

There are no simulation-only ports on the GTPE2\_COMMON and GTPE2\_CHANNEL primitives.

#### GTPE2\_COMMON Attributes

The GTPE2\_COMMON primitive has attributes intended only for simulation. Table 1-2 lists the simulation-only attributes of the GTPE2\_COMMON primitive. The names of these attributes start with *SIM*\_.

Table 1-2: GTPE2\_COMMON Simulation-Only Attributes

| Attribute          | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIM_PLL0REFCLK_SEL | 3-bit<br>Binary | This attribute selects the reference clock source used to drive PLL0 in simulation for designs where PLL0 is always driven by the same reference clock source.  SIM_PLL0REFCLK_SEL allows for simulation before and after the port swap changes. This allows for the block to be simulated with the correct clock source both before and after the port swap.  SIM_PLL0REFCLK_SEL must be set to the same value as PLL0REFCLK SEL[2:0]. For designs that require the reference clock source to be changed on the fly, the port PLL0REFCLKSEL is used instead to dynamically select the reference clock source. |

| SIM_PLL1REFCLK_SEL | 3-bit<br>Binary | This attribute selects the reference clock source used to drive PLL1 in simulation for designs where PLL1 is always driven by the same reference clock source.  SIM_PLL1REFCLK_SEL allows for simulation before and after the port swap changes. This allows for the block to be simulated with the correct clock source both before and after the port swap.  SIM_PLL1REFCLK_SEL must be set to the same value as PLL1REFCLK SEL[2:0]. For designs that require the reference clock source to be changed on the fly, the port PLL1REFCLKSEL is used instead to dynamically select the reference clock source. |

Table 1-2: GTPE2\_COMMON Simulation-Only Attributes (Cont'd)

| Attribute         | Туре    | Description                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIM_RESET_SPEEDUP | Boolean | If the SIM_RESET_SPEEDUP attribute is set to TRUE (default), an approximated reset sequence is used to speed up the reset time for simulations, where faster reset times and faster simulation times are desirable. If the SIM_RESET_SPEEDUP attribute is set to FALSE, the model emulates hardware reset behavior in detail. |

| SIM_VERSION       | String  | This attribute selects the simulation version to match different steppings of silicon. The default for this attribute is 1.1.                                                                                                                                                                                                 |

#### GTPE2\_CHANNEL Attributes

The GTPE2\_CHANNEL primitive has attributes intended only for simulation. Table 1-3 lists the simulation-only attributes of the GTPE2\_CHANNEL primitive. The names of these attributes start with *SIM*\_.

Table 1-3: GTPE2\_CHANNEL Simulation-Only Attributes

| Attribute                | Туре    | Description                                                                                                                                                                                                                                                                                                                   |

|--------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIM_RESET_SPEEDUP        | Boolean | If the SIM_RESET_SPEEDUP attribute is set to TRUE (default), an approximated reset sequence is used to speed up the reset time for simulations, where faster reset times and faster simulation times are desirable. If the SIM_RESET_SPEEDUP attribute is set to FALSE, the model emulates hardware reset behavior in detail. |

| SIM_RECEIVER_DETECT_PASS | Boolean | SIM_RECEIVER_DETECT_PASS is a string TRUE/FALSE attribute to determine if a receiver detect operation should indicate a pass or fail in simulation.                                                                                                                                                                           |

| SIM_TX_EIDLE_DRIVE_LEVEL | String  | SIM_TX_EIDLE_DRIVE_LEVEL can be set to 0, 1, X, or Z to allow for simulation of electrical idle and receiver detect operations using an external pull-up resistor. The default for this attribute is X.                                                                                                                       |

| SIM_VERSION              | Real    | This attribute selects the simulation version to match different steppings of silicon. The default for this attribute is 1.0.                                                                                                                                                                                                 |

## **Implementation**

#### **Functional Description**

This section provides the information needed to map 7 series GTP transceivers instantiated in a design to device resources, including:

- The location of the GTP transceiver Quads on the available device and package combinations.

- The pad numbers of external signals associated with each GTP transceiver Quad.

- How the GTPE2\_CHANNEL primitive, the GTPE2\_COMMON primitive, and clocking resources instantiated in a design are mapped to available locations with a user constraints file (UCF).

It is a common practice to define the location of GTP transceiver Quads early in the design process to ensure correct usage of clock resources and to facilitate signal integrity analysis during board design. The implementation flow facilitates this practice through the use of location constraints in the UCF.

This section describes how to instantiate GTP transceiver clocking components.

The position of each GTP transceiver channel and common primitive is specified by an XY coordinate system that describes the column number and the relative position within that column.

For a given device/package combination, the transceiver with the coordinates X0Y0 is always located at the lowest position of the lowest available bank.

There are two ways to create a UCF for designs that utilize the GTP transceiver. The preferred method is to use the 7 Series FPGAs Transceivers Wizard. The Wizard automatically generates UCF templates that configure the transceivers and contain placeholders for GTP transceiver placement information. The UCFs generated by the Wizard can then be edited to customize operating parameters and placement information for the application.

The second approach is to create the UCF by hand. When using this approach, the designer must enter both configuration attributes that control transceiver operation as well as tile location parameters. Care must be taken to ensure that all of the parameters needed to configure the GTP transceiver are correctly entered.

If a design requires the use of any of the GTP channels in a given GTP Quad, a GTPE2\_COMMON primitive must be instantiated as shown in Figure 1-5. At a minimum, at least one GTPE2\_CHANNEL must also be instantiated. Figure 1-5 shows four GTPE2\_CHANNEL primitives instantiated.

Figure 1-5: Four Channel Configuration

## Serial Transceiver Channels by Device/Package

See <u>UG475</u>, 7 Series FPGAs Packaging and Pinout Specification.

# Shared Features

## **Reference Clock Input Structure**

## **Functional Description**

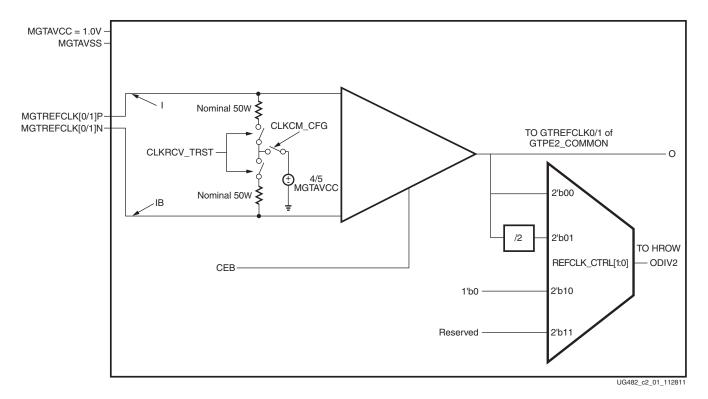

The reference clock input structure is illustrated in Figure 2-1. The input is terminated internally with  $50\Omega$  on each leg to 4/5 MGTAVCC. The reference clock is instantiated in software with the IBUFDS\_GTE2 software primitive. The ports and attributes controlling the reference clock input are tied to the IBUFDS\_GTE2 software primitive.

Figure 2-1 shows the internal structure of the reference clock input buffer.

Figure 2-1: Reference Clock Input Structure

#### Ports and Attributes

Table 2-1 defines the reference clock input ports in the IBUFDS\_GTE2 software primitive.

Table 2-1: Reference Clock Input Ports (IBUFDS\_GTE2)

| Port                 | Dir      | Clock Domain | Description                                                                                                                                                                                                                                                                                                       |

|----------------------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I<br>IB              | In (pad) | N/A          | These are the reference clock input ports that get mapped to GTREFCLK0P/GTREFCLK0N and GTREFCLK1P/GTREFCLK1P.                                                                                                                                                                                                     |

| СЕВ                  | In       | N/A          | This is the active-Low asynchronous clock enable signal for the clock buffer. Setting this signal High powers down the clock buffer.                                                                                                                                                                              |

| O                    | Out      | N/A          | This output drives the GTREFCLK[0/1] signals in the GTPE2_COMMON software primitives. Refer to Reference Clock Selection and Distribution, page 25 for more details.                                                                                                                                              |

| ODIV2 <sup>(1)</sup> | Out      | N/A          | This output is a divide-by-2 version of the O signal, which can drive the BUFG* software primitives via Hrow routing. The selection is controlled automatically by the software depending on whether port O or ODIV2 is connected. Refer to Reference Clock Selection and Distribution, page 25 for more details. |

#### Notes:

Table 2-2 defines the attributes in the IBUFDS\_GTE2 software primitive that configure the reference clock input.

Table 2-2: Reference Clock Input Attributes (IBUFDS\_GTE2)

| Attribute    | Туре         | Description                                                                                                                             |

|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| CLK_RCV_TRST | Boolean      | Reserved. This attribute switches the $50\Omega$ termination resistors into the signal path. This attribute must always be set to TRUE. |

| CLKCM_CFG    | Boolean      | Reserved. This attribute switches in the termination voltage for the $50\Omega$ termination. This attribute must always be set to TRUE. |

| CLKSWING_CFG | 2-bit Binary | Reserved. This attribute controls the internal swing of the clock. This attribute must always be set to 2 'b11.                         |

<sup>1.</sup> The O and ODIV2 outputs are not phase matched to each other.

#### Use Modes: Reference Clock Termination

The reference clock input is to be externally AC coupled. Table 2-3 shows the port and attribute settings required to achieve this.

Table 2-3: Port and Attribute Settings

| Input Type | Settings              |  |

|------------|-----------------------|--|

| Ports      | CEB = 0               |  |

|            | CLKRCV_TRST = TRUE    |  |

| Attributes | $CLKCM\_CFG = TRUE$   |  |

|            | CLKSWING_CFG = 2 'b11 |  |

#### **Reference Clock Selection and Distribution**

#### **Functional Description**

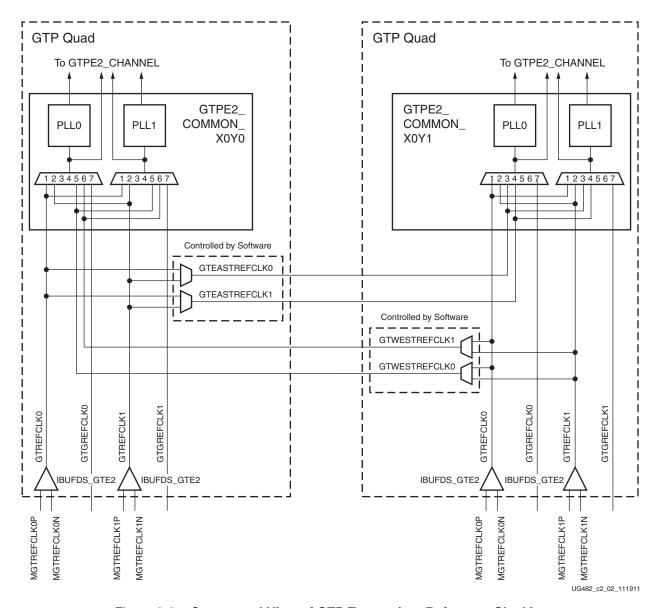

The GTP transceivers in 7 series FPGAs provide different reference clock input options. Clock selection and availability differs slightly from 7 series GTX transceiver in that reference clock routing is east and west bound rather than north and south bound.

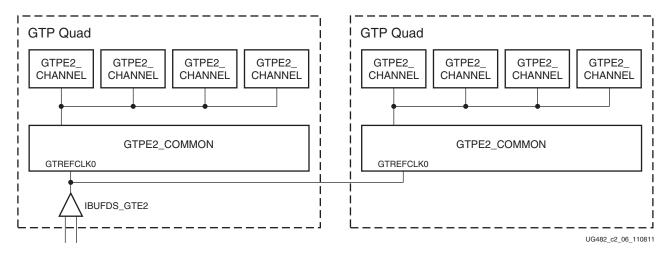

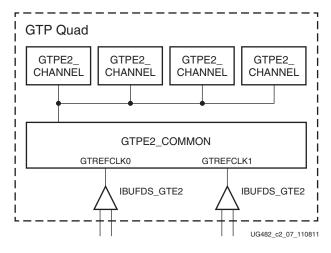

Architecturally, the concept of a Quad (or Q), contains a grouping of four GTPE2\_CHANNEL primitives, one GTPE2\_COMMON primitive, two dedicated external reference clock pin pairs, and dedicated reference clock routing. The GTPE2\_COMMON primitive must always be instantiated, and the GTPE2\_CHANNEL primitive must be instantiated for each transceiver. For the larger Artix<sup>TM</sup>-7 devices that contain 16 GTP transceivers, the reference clock supplied to the PLLs in a given Quad can also be sourced from the adjacent Quad in the same half of the device. A Quad located in the top half of the device can share its two local reference clocks with the other Quad located in the top half. Similarly, a Quad located in the bottom half of the device can share its two reference clocks with the other Quad located in the bottom half.

Reference clock features include:

- Clock routing for east and west bound clocks.

- Flexible reference clock inputs available for PLL0 and PLL1.

- Static or dynamic selection of the reference clock for PLL0 and PLL1.

Figure 2-2 shows the reference clock architecture with the GTPE2\_COMMON primitive, two dedicated reference clock pin pairs, and dedicated east or west reference clock routing. Each GTPE2\_COMMON in a Quad has four clock inputs available:

- Two local reference clock pin pairs, GTREFCLK0 or GTREFCLK1

- Two reference clock pin pairs from the other Quad situated in the same half of the device

Figure 2-2: Conceptual View of GTP Transceiver Reference Clocking

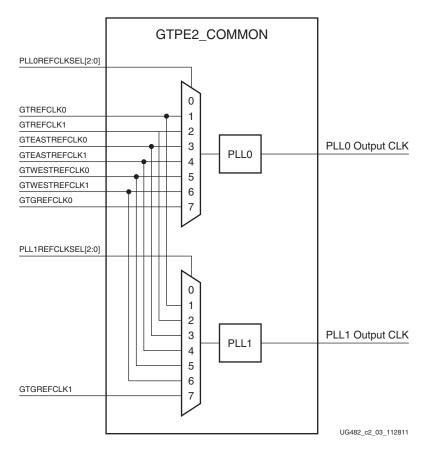

Figure 2-3 shows the shows the detailed view of the reference clock multiplexer structures within a single GTPE2\_COMMON primitive. The PLL0REFCLKSEL and PLL1REFCLKSEL ports are required when multiple reference clock sources are connected to the multiplexers. A single reference clock is most commonly used. In this case, the PLL[0/1]REFCLKSEL port can be tied to 3 'b001, and the Xilinx software tools handle the complexity of the multiplexers and associated routing. See External Reference Clock Use Model, page 31 for more information.

Figure 2-3: PLL0 and PLL1 Reference Clock Selection Multiplexer

#### Ports and Attributes

Table 2-4 and Table 2-5 define the clocking ports and attributes for the GTPE2\_COMMON primitive.

Table 2-4: GTPE2\_COMMON Clocking Ports

| Port          | Direction | Clock<br>Domain | Description                                                                                                      |

|---------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------|

| GTGREFCLK0    | In        | Clock           | Reference clock generated by the internal FPGA logic. This input is reserved for internal testing purposes only. |

| GTGREFCLK1    | In        | Clock           | Reference clock generated by the internal FPGA logic. This input is reserved for internal testing purposes only. |

| GTREFCLK0     | In        | Clock           | External clock driven by IBUFDS_GTE2 for PLL0 and/or PLL1.                                                       |

| GTREFCLK1     | In        | Clock           | External clock driven by IBUFDS_GTE2 for PLL0 and/or PLL1.                                                       |

| GTWESTREFCLK0 | In        | Clock           | West-bound clock from the Quad on the right side of the device.                                                  |

Table 2-4: GTPE2\_COMMON Clocking Ports (Cont'd)

| Port          | Direction | Clock<br>Domain | Description                                                                                            |

|---------------|-----------|-----------------|--------------------------------------------------------------------------------------------------------|

| GTWESTREFCLK1 | In        | Clock           | West-bound clock from the Quad on the right side of the device.                                        |

| GTEASTREFCLK0 | In        | Clock           | East-bound clock from the Quad on the left side of the device.                                         |

| GTEASTREFCLK1 | In        | Clock           | East-bound clock from the Quad on the left side of the device.                                         |

| PLL0OUTCLK    | Out       | Clock           | PLL0 clock output. The user must connect this port to the PLL0CLK port on the GTPE2_CHANNEL primitive. |

| PLL1OUTCLK    | Out       | Clock           | PLL1 clock output. The user must connect this port to the PLL1CLK port on the GTPE2_CHANNEL primitive. |

| PLL0OUTREFCLK | Out       | Clock           | The user must connect this port to the PLL0REFCLK port on the GTPE2_CHANNEL primitive.                 |

| PLL1OUTREFCLK | Out       | Clock           | The user must connect this port to the PLL1REFCLK port on the GTPE2_CHANNEL primitive.                 |

Table 2-4: GTPE2\_COMMON Clocking Ports (Cont'd)

| Port               | Direction | Clock<br>Domain | Description                                                                                                                                                                                   |

|--------------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL0REFCLKSEL[2:0] | In        | Async           | Input to dynamically select the input reference clock to PLL0. This input should be set to 3 'b001 when only one clock source is connected to the PLL0 reference clock selection multiplexer. |

|                    |           |                 | Reset must be applied to PLL0 after changing the reference clock input.                                                                                                                       |

|                    |           |                 | 000: Reserved                                                                                                                                                                                 |

|                    |           |                 | 001: GTREFCLK0 selected                                                                                                                                                                       |

|                    |           |                 | 010: GTREFCLK1 selected                                                                                                                                                                       |

|                    |           |                 | 011: GTEASTREFCLK0 selected                                                                                                                                                                   |

|                    |           |                 | 100: GTEASTREFCLK1 selected                                                                                                                                                                   |

|                    |           |                 | 101: GTWESTREFCLK0 selected                                                                                                                                                                   |

|                    |           |                 | 110: GTWESTREFCLK1 selected                                                                                                                                                                   |

|                    |           |                 | 111: GTGREFCLK0 selected                                                                                                                                                                      |

| PLL1REFCLKSEL[2:0] | In        | Async           | Input to dynamically select the input reference clock to PLL1. This input should be set to 3 'b001 when only one clock source is connected to the PLL1 reference clock selection multiplexer. |

|                    |           |                 | Reset must be applied to PLL1 after changing the reference clock input.                                                                                                                       |

|                    |           |                 | 000: Reserved                                                                                                                                                                                 |

|                    |           |                 | 001: GTREFCLK0 selected                                                                                                                                                                       |

|                    |           |                 | 010: GTREFCLK1 selected                                                                                                                                                                       |

|                    |           |                 | 011: GTEASTREFCLK0 selected                                                                                                                                                                   |

|                    |           |                 | 100: GTEASTREFCLK1 selected                                                                                                                                                                   |

|                    |           |                 | 101: GTWESTREFCLK0 selected                                                                                                                                                                   |

|                    |           |                 | 110: GTWESTREFCLK1 selected                                                                                                                                                                   |

|                    |           |                 | 111: GTGREFCLK1 selected                                                                                                                                                                      |

Table 2-5: GTPE2\_COMMON Attributes

| Attribute          | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIM_PLL0REFCLK_SEL | 3-bit Binary | This attribute selects the reference clock source used to drive PLL0 in simulation for designs where PLL0 is always driven by the same reference clock source.  SIM_PLL0REFCLK_SEL allows for simulation before and after the port swap changes. This allows for the block to be simulated with the correct clock source both before and after the port swap.  SIM_PLL0REFCLK_SEL must be set to the same value as PLL0REFCLK SEL[2:0]. For designs that require the reference clock source to be changed on the fly, the port PLL0REFCLKSEL is used instead to dynamically select the reference clock source. |

| SIM_PLL1REFCLK_SEL | 3-bit Binary | This attribute selects the reference clock source used to drive PLL1 in simulation for designs where PLL1 is always driven by the same reference clock source.  SIM_PLL1REFCLK_SEL allows for simulation before and after the port swap changes. This allows for the block to be simulated with the correct clock source both before and after the port swap.  SIM_PLL1REFCLK_SEL must be set to the same value as PLL1REFCLK SEL[2:0]. For designs that require the reference clock source to be changed on the fly, the port PLL1REFCLKSEL is used instead to dynamically select the reference clock source. |

Table 2-6 defines the clocking ports for the GTPE2\_CHANNEL primitive.

Table 2-6: GTPE2\_CHANNEL Clocking Ports

| Port        | Direction | Clock<br>Domain | Description                                                                                             |

|-------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------|

| RXSYSCLKSEL | In        | Async           | Selects the PLL clock source to drive the RX datapath:                                                  |

|             |           |                 | RXSYSCLKSEL[0] = 1 'b0 (PLL0)                                                                           |

|             |           |                 | RXSYSCLKSEL[0] = 1 'b1 (PLL1)                                                                           |

|             |           |                 | Selects the reference clock source to drive RXOUTCLK:                                                   |

|             |           |                 | RXSYSCLKSEL[1] = 1 'b0 (reference clock from PLL0)                                                      |

|             |           |                 | RXSYSCLKSEL[1] = 1 'b1 (reference clock from PLL1)                                                      |

| TXSYSCLKSEL | In        | Async           | Selects the PLL clock source to drive the TX datapath:                                                  |

|             |           |                 | TXSYSCLKSEL[0] = 1 'b0 (PLL0)                                                                           |

|             |           |                 | TXSYSCLKSEL[0] = 1 'b1 (PLL1)                                                                           |

|             |           |                 | Selects the reference clock source to drive TXOUTCLK:                                                   |

|             |           |                 | TXSYSCLKSEL[1] = 1 'b0 (reference clock from PLL0)                                                      |

|             |           |                 | TXSYSCLKSEL[1] = 1 'b1 (reference clock form PLL1)                                                      |

| PLL0CLK     | In        | Clock           | PLL0 clock input. The user must connect this port to the PLL0OUTCLK port on the GTPE2_COMMON primitive. |

| PLL1CLK     | In        | Clock           | PLL1 clock input. The user must connect this port to the PLL1OUTCLK port on the GTPE2_COMMON primitive. |

| PLL0REFCLK  | In        | Clock           | The user must connect this port to the PLL0OUTREFCLK port on the GTPE2_COMMON primitive.                |

| PLL1REFCLK  | In        | Clock           | The user must connect this port to the PLL1OUTREFCLK port on the GTPE2_COMMON primitive.                |

#### External Reference Clock Use Model

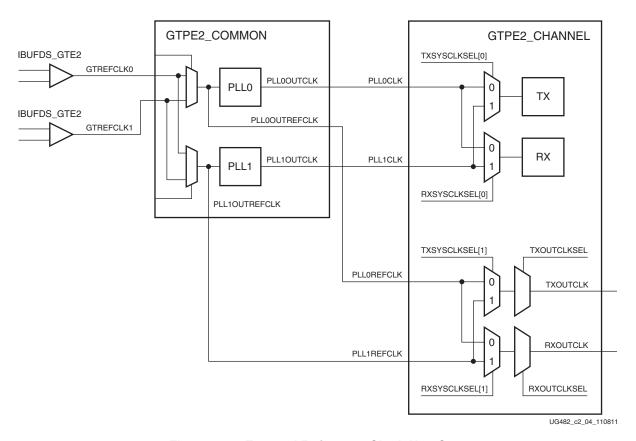

Each Quad has two dedicated differential reference clock inputs that can be connected to external reference clock sources. An IBUFDS\_GTE2 primitive must be instantiated to use these dedicated reference clock pin pairs. The user design connects the IBUFDS\_GTE2 output (O) to the GTREFCLK[0/1], GTEASTREFCLK[0/1] or GTWESTREFCLK[0/1] ports of the GTPE2\_COMMON primitive where the reference clock selection multiplexer is located. Depending on the line rate requirement, the user design has the flexibility to use different combinations of PLL0 or PLL1 to drive the TX and/or RX datapath, as shown in Figure 2-4.

Figure 2-4: External Reference Clock Use Case

## Single External Reference Clock Use Model

In the single external reference clock use model, the user connects the IBUFDS\_GTE2 output (O) to the GTREFCLK0 input port of the GTPE2\_COMMON primitive. The user design can leave the other unused reference clock ports floating. The IBUFDS\_GTE2 input pins can be constrained in the user constraints file (UCF). Figure 2-5 shows a single GTPE2\_COMMON primitive connected to a single IBUFDS\_GTE2 primitive.

Figure 2-5: Single GTP Quad with a Single Local Reference Clock

Figure 2-6 shows a single reference clock connected to two GTP Quads. The user connects the IBUFDS\_GTE2 output (O) to the GTREFCLK0 input port of both GTPE2\_COMMON primitive instances. Such a scenario is only possible in the larger Artix-7 devices that contain east and west GTP Quads adjacent to each other.

Figure 2-6: Two GTP Quads with a Single Shared Reference Clock

When required, as is the case for the design in Figure 2-6, the Xilinx implementation tools make the necessary adjustments to the east/west routing shown in Figure 2-2, page 26, as well as any necessary pin swapping to the GTPE2\_COMMON clock inputs to route the reference clocks between two Quads.

#### Multiple External Reference Clock Use Model

In Figure 2-7 and Figure 2-9, because the reference clock multiplexer structures in the GTPE2\_COMMON have more than one reference clock source, the user design is required to connect the output of the IBUFDS\_GTE2 to the correct clock input ports on the GTPE2\_COMMON primitive. Figure 2-7 shows an example of a single GTP Quad using both of its dedicated differential reference clock inputs. Two IBUFDS\_GTE2 primitives and a single GTPE2\_COMMON primitive are instantiated.

Figure 2-7: Single GTP Quad using Multiple Local Reference Clocks

Figure 2-8 shows two GTP Quads, each utilizing their own dedicated differential reference clock inputs as well as the dedicated differential reference clock inputs of their neighboring GTP Quad. Such a scenario is only possible in the larger Artix-7 devices that contain east and west GTP Quads adjacent to each other. The user is responsible for properly connecting the output of the IBUFDS\_GTE2 to the appropriate GTREFCLK[0/1], GTWESTREFCLK[0/1], and GTEASTREFCLK[0/1] input ports on the GTPE2\_COMMON primitive.

Figure 2-8: Two GTP Quads using Multiple Reference Clocks from Different Quads

For multi-rate designs that require the reference clock to be changed in real time, the PLL0REFCLKSEL and PLL1REFCLKSEL ports are used to dynamically select the reference clock source. When the selection has been made, the user design is responsible for resetting the PLL via PLL0RESET or PLL1RESET.

#### **PLL**

## **Functional Description**

The GTP Quad contains two ring oscillator PLLs (PLL0 and PLL1). The internal clocking architecture is shown in Figure 2-9. When the TX and RX datapaths operate in the same line rate range, PLL0 or PLL1 can be shared between the TX and RX datapaths. The TX and RX clock dividers can individually select the clock from PLL0 or PLL1 to allow the TX and RX datapaths to operate at asynchronous frequencies using different reference clock inputs.

Figure 2-9: Internal Clocking Architecture

The PLL input clock selection is described in Reference Clock Selection and Distribution, page 25. The PLL outputs feed the TX and RX clock divider blocks, which control the generation of serial and parallel clocks used by the PMA and PCS blocks.

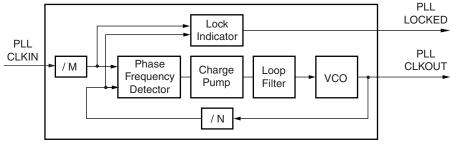

Figure 2-10 illustrates a conceptual view of the PLL architecture. The input clock can be divided by a factor of M before feeding into the phase frequency detector. The feedback divider N determines the VCO multiplication ratio and the PLL output frequency. A lock indicator block compares the frequencies of the reference clock and the VCO feedback clock to determine if a frequency lock has been achieved.

UG482\_c2\_10\_112811

Figure 2-10: PLL Block Diagram

The PLL has a nominal operating range between 1.6 GHz to 3.3 GHz. The 7 Series FPGAs Transceivers Wizard chooses the appropriate PLL settings based on application requirements.

Equation 2-1 shows how to determine the PLL output frequency (GHz).

$$f_{PLLClkout} = f_{PLLClkin} \times \frac{N}{M}$$

Equation 2-1

Equation 2-2 shows how to determine the line rate (Gb/s). D represents the value of the TX or RX clock divider block in the channel.

$$f_{LineRate} = \frac{f_{PLLClkout} \times 2}{D}$$

Equation 2-2

Table 2-7 lists the allowable divider settings.

Table 2-7: PLL Divider Settings

| Factor | Attribute                          | Valid Settings                         |

|--------|------------------------------------|----------------------------------------|

| M      | PLL0_REFCLK_DIV<br>PLL1_REFCLK_DIV | 1, 2                                   |

| N      | PLL0_FBDIV<br>PLL1_FBDIV           | 1, 2, 3, 4, 5, 6, 8, 10, 12,<br>16, 20 |

| D      | RXOUT_DIV<br>TXOUT_DIV             | 1, 2, 4, 8                             |

## Ports and Attributes

Table 2-8 and Table 2-9 defines the ports and attributes for the PLL.

Table 2-8: PLL Ports

| Port                          | Direction | Clock Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL0LOCKDETCLK PLL1LOCKDETCLK | In        | Clock        | Stable reference clock for the detection of the feedback and reference clock signals to the PLL. The input reference clock to the PLL or any output clock generated from the PLL (e.g., TXOUTCLK) must not be used to drive this clock.  This clock is required only when using the PLL[0/1]FBCLKLOST and PLL[0/1]REFCLKLOST ports. It does not affect the PLL lock detection, reset, and power-down functions. |

| PLL0LOCKEN PLL1LOCKEN         | In        | Async        | This port enables the PLL lock detector. It must always be tied High.                                                                                                                                                                                                                                                                                                                                           |

| PLL0PD<br>PLL1PD              | In        | Async        | Active-High signal that powers down the PLL for power savings.                                                                                                                                                                                                                                                                                                                                                  |

Table 2-8: PLL Ports (Cont'd)

| Port                           | Direction | Clock Domain   | Description                                                                                                                                                                                        |

|--------------------------------|-----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL0REFCLKSEL<br>PLL1REFCLKSEL | In        | Async          | Input to dynamically select the input reference clock to the PLL. This input should be set to 3 'b001 when only one clock source is connected to the PLL reference clock selection multiplexer.    |

|                                |           |                | Reset must be applied to the PLL after changing the reference clock input.                                                                                                                         |

|                                |           |                | 000: Reserved                                                                                                                                                                                      |

|                                |           |                | 001: GTREFCLK0 selected                                                                                                                                                                            |

|                                |           |                | 010: GTREFCLK1 selected                                                                                                                                                                            |

|                                |           |                | 011: GTEASTREFCLK0<br>selected                                                                                                                                                                     |

|                                |           |                | 100: GTEASTREFCLK1<br>selected                                                                                                                                                                     |

|                                |           |                | 101: GTWESTREFCLK0 selected                                                                                                                                                                        |

|                                |           |                | 110: GTWESTREFCLK1<br>selected                                                                                                                                                                     |

|                                |           |                | 111: GTGREFCLK0 (PLL0)<br>or GTGREFCLK1 (PLL1)<br>selected                                                                                                                                         |

| PLL0RESET<br>PLL1RESET         | In        | Async          | This active-High port resets the dividers inside the PLL as well as the PLL lock indicator and status block.                                                                                       |

| PLL0FBCLKLOST                  | Out       | PLL0LOCKDETCLK | A High on this signal indicates                                                                                                                                                                    |

| PLL1FBCLKLOST                  |           | PLL1LOCKDETCLK | the feedback clock from the PLL feedback divider to the phase frequency detector of the PLL is lost.                                                                                               |

| PLL0LOCK<br>PLL1LOCK           | Out       | Async          | This active-High PLL frequency lock signal indicates that the PLL frequency is within predetermined tolerance. The transceiver and its clock outputs are not reliable until this condition is met. |

| PLL0REFCLKLOST                 | Out       | PLL0LOCKDETCLK | A High on this signal indicates                                                                                                                                                                    |

| PLL1REFCLKLOST                 |           | PLL1LOCKDETCLK | the reference clock to the phase frequency detector of the PLL is lost.                                                                                                                            |

Table 2-9: PLL Attributes

| Attribute                          | Туре         | Description                                                                                                                    |

|------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| PLL0_CFG<br>PLL1_CFG               | 27-bit Hex   | Reserved. Configuration setting for the PLL. The recommended value from the 7 Series FPGAs Transceivers Wizard should be used. |

| PLL0_FBDIV<br>PLL1_FBDIV           | Integer      | PLL feedback divider setting as shown in Figure 2-10, page 35. Valid settings are 1, 2, 3, 4, 5, 6, 8, 10, 12, 16, and 20.     |

| PLL0_LOCK_CFG PLL1_LOCK_CFG        | 9-bit Hex    | Reserved. The recommended value from the 7 Series FPGAs Transceivers Wizard should be used.                                    |

| PLL0_REFCLK_DIV<br>PLL1_REFCLK_DIV | Integer      | PLL reference clock divider M settings as shown in Figure 2-10, page 35. Valid settings are 1 and 2.                           |

| PLL0_INIT_CFG PLL1_INIT_CFG        | 24-bit Hex   | Reserved. The recommended value from the 7 Series FPGAs Transceivers Wizard should be used.                                    |

| PLL0_DMON_CFG PLL1_DMON_CFG        | 1-bit Binary | Reserved. The recommended value from the 7 Series FPGAs Transceivers Wizard should be used.                                    |

# Loopback

# **Functional Description**

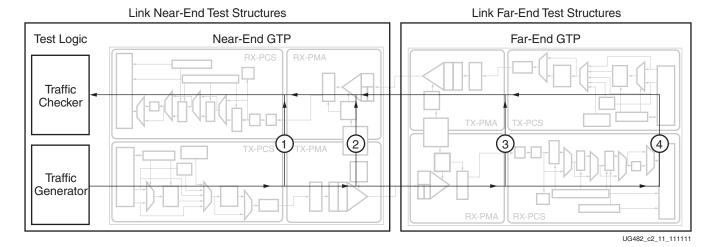

Loopback modes are specialized configurations of the transceiver datapath where the traffic stream is folded back to the source. Typically, a specific traffic pattern is transmitted and then compared to check for errors. Figure 2-11 illustrates a loopback test configuration with four different loopback modes.

Figure 2-11: Loopback Testing Overview

Loopback test modes fall into two broad categories:

- Near-end loopback modes loop transmit data back in the transceiver closest to the traffic generator.

- Far-end loopback modes loop received data back in the transceiver at the far end of the link.

Loopback testing can be used either during development or in deployed equipment for fault isolation. The traffic patterns used can be either application traffic patterns or specialized pseudo-random bit sequences. Each GTP transceiver has a built-in PRBS generator and checker.

Each GTP transceiver features several loopback modes to facilitate testing:

- Near-End PCS Loopback (path 1 in Figure 2-11)

- Near-End PMA Loopback (path 2 in Figure 2-11)

- Far-End PMA Loopback (path 3 in Figure 2-11)

In Far-End PMA loopback, the transmitter internally uses the RX recovered clock to transmit data.

- Far-End PCS Loopback (path 4 in Figure 2-11)

If clock correction is not used, a transceiver in Far-end PCS loopback must use the same reference clock used by the transceiver that is the source of the loopback data.

Regardless of whether clock correction is used or not, the ports TXUSRCLK and RXUSRCLK must be driven by the same clocking resource (BUFG, BUFH, BUFR).

#### Ports and Attributes

Table 2-10 and Table 2-11 define the loopback ports and attributes, respectively.

Table 2-10: Loopback Ports

| Port          | Dir | Clock Domain | Description                                                                                                                                                 |

|---------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOOPBACK[2:0] | In  | Async        | 000: Normal operation 001: Near-End PCS Loopback 010: Near-End PMA Loopback 011: Reserved 100: Far-End PMA Loopback 101: Reserved 110: Far-End PCS Loopback |

Table 2-11: Loopback Attributes

| Attribute        | Туре         | Description                                                                                                                                                                                                  |

|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOOPBACK_CFG     | 1-bit Binary | Reserved.                                                                                                                                                                                                    |

| PMA_LOOPBACK_CFG | 1-bit Binary | For use with Far-End PMA loopback. When this attribute is set to 1 'b1, the loopback path includes the continuous time linear equalizer (CTLE). When set to 1 'b0, the loopback path occurs before the CTLE. |

# **Dynamic Reconfiguration Port**

# **Functional Description**

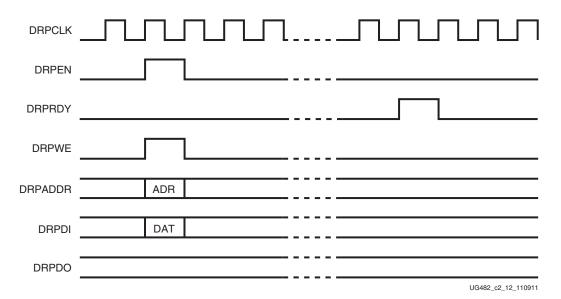

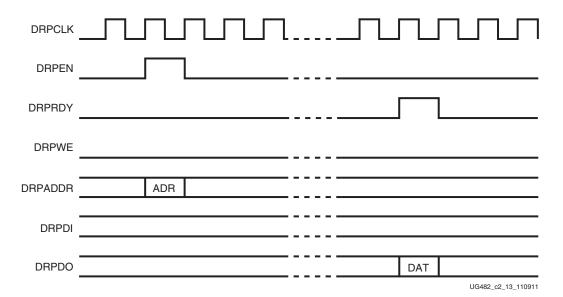

The dynamic reconfiguration port (DRP) allows the dynamic change of parameters of the GTPE2\_CHANNEL and GTPE2\_COMMON primitives. The DRP interface is a processor-friendly synchronous interface with an address bus (DRPADDR) and separated data buses for reading (DRPDO) and writing (DRPDI) configuration data to the primitives. An enable signal (DRPEN), a read/write signal (DRPWE), and a ready/valid signal (DRPRDY) are the control signals that implement read and write operations, indicate operation completion, or indicate the availability of data.

### Ports and Attributes

Table 2-12 shows the DRP related ports for GTPE2\_CHANNEL.

Table 2-12: DRP Ports of GTPE2\_CHANNEL

| Port         | Dir | Clock Domain | Description                                                                                         |

|--------------|-----|--------------|-----------------------------------------------------------------------------------------------------|

| DRPADDR[8:0] | In  | DRPCLK       | DRP address bus.                                                                                    |

| DRPCLK       | In  | N/A          | DRP interface clock.                                                                                |

| DRPEN        | In  | DRPCLK       | DRP enable signal.  0: No read or write operation performed.  1: Enables a read or write operation. |

| DRPDI[15:0]  | In  | DRPCLK       | Data bus for writing configuration data from the FPGA logic resources to the transceiver.           |

| DRPRDY       | Out | DRPCLK       | Indicates operation is complete for write operations and data is valid for read operations.         |

| DRPDO[15:0]  | Out | DRPCLK       | Data bus for reading configuration data from the GTP transceiver to the FPGA logic resources.       |

| DRPWE        | In  | DRPCLK       | DRP write enable.  0: Read operation when DEN is 1.  1: Write operation when DEN is 1.              |

Table 2-13 shows the DRP related ports for GTPE2\_COMMON.

Table 2-13: DRP Ports of GTPE2\_COMMON

| Port         | Dir | Clock Domain | Description                                                                                         |

|--------------|-----|--------------|-----------------------------------------------------------------------------------------------------|

| DRPADDR[7:0] | In  | DRPCLK       | DRP address bus.                                                                                    |

| DRPCLK       | In  | N/A          | DRP interface clock.                                                                                |

| DRPEN        | In  | DRPCLK       | DRP enable signal.  0: No read or write operation performed.  1: Enables a read or write operation. |

| DRPDI[15:0]  | In  | DRPCLK       | Data bus for writing configuration data from the FPGA logic resources to the transceiver.           |

| Port        | Dir | Clock Domain | Description                                                                                   |

|-------------|-----|--------------|-----------------------------------------------------------------------------------------------|

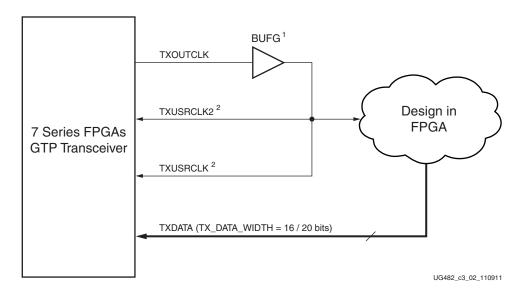

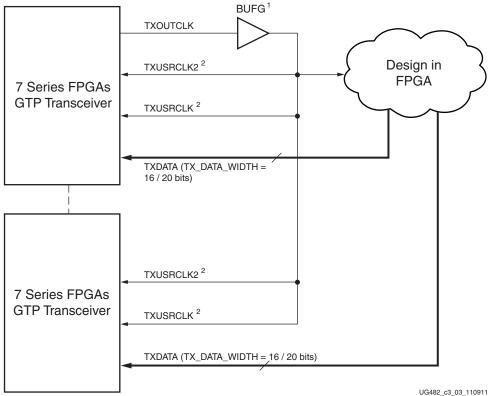

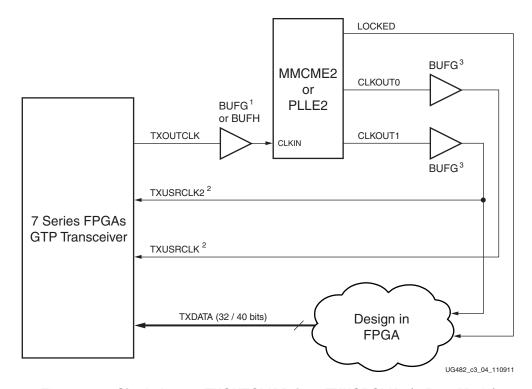

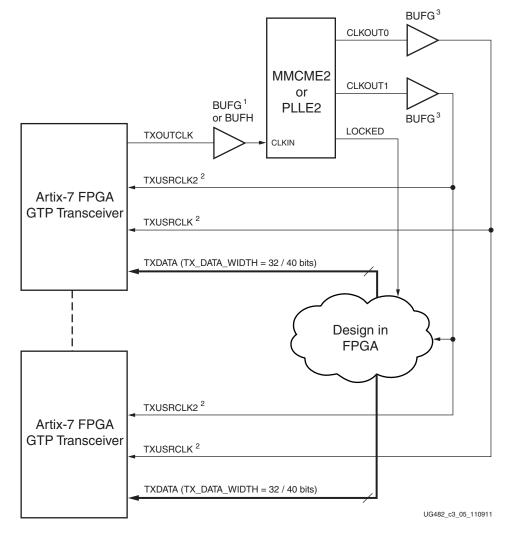

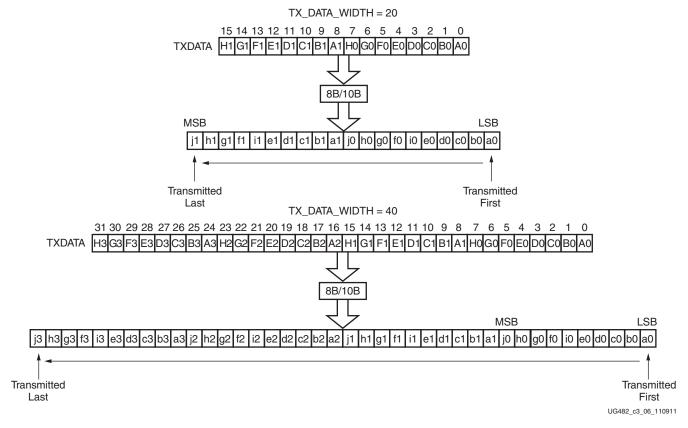

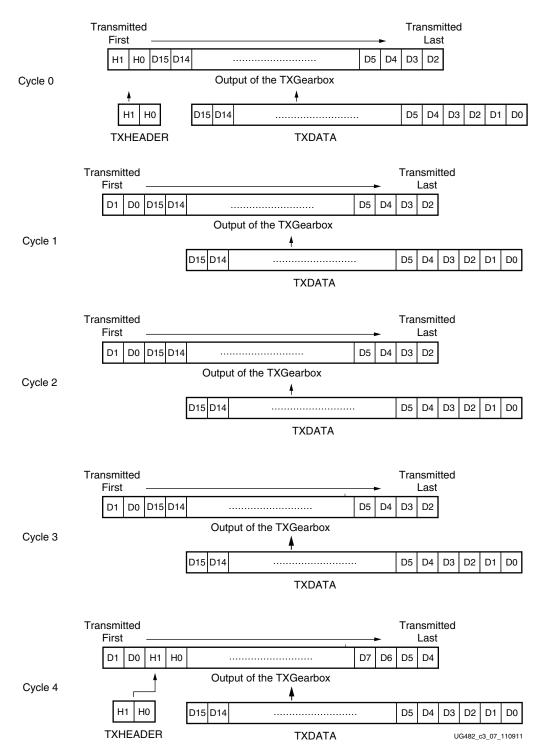

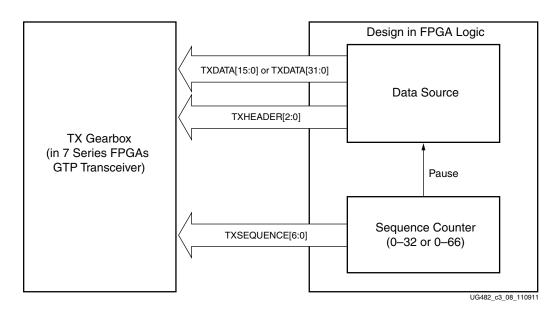

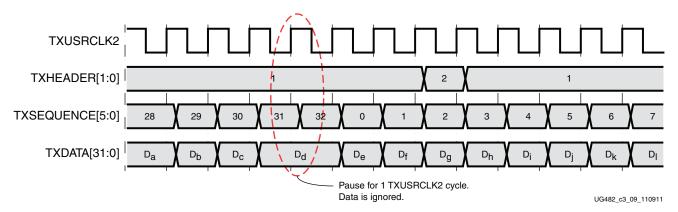

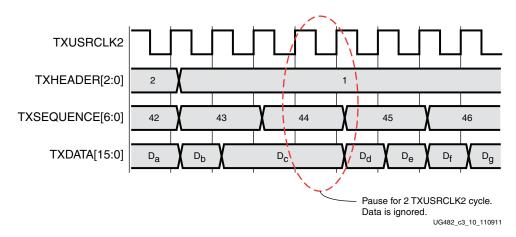

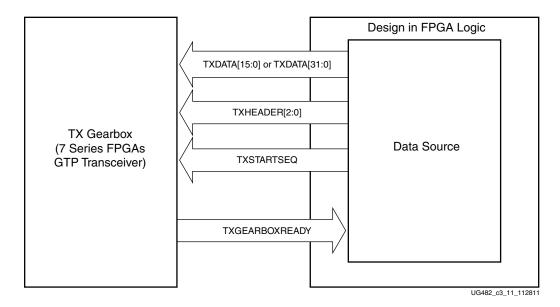

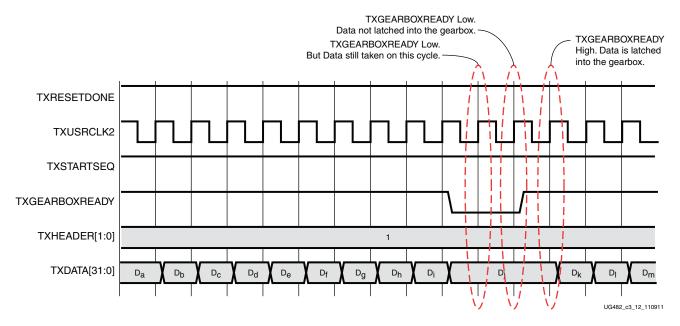

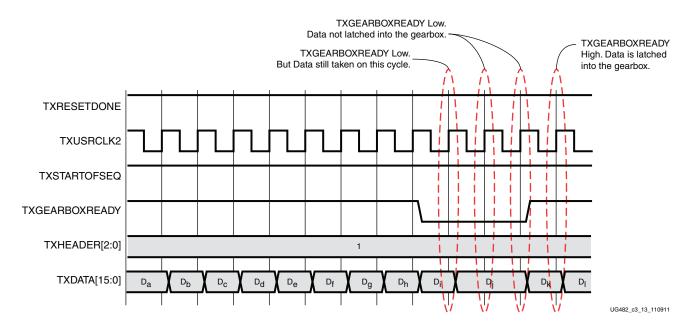

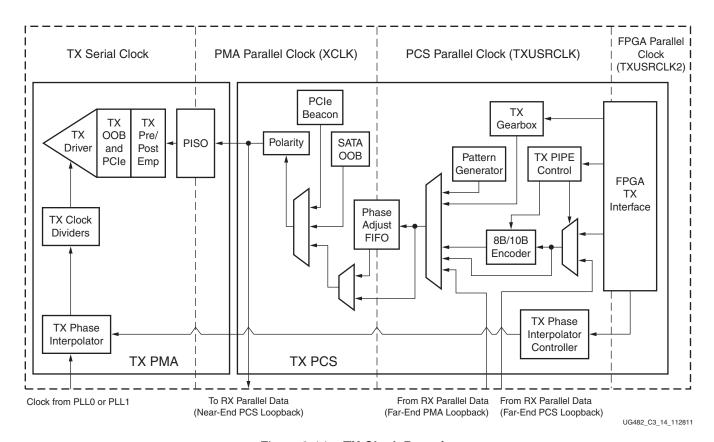

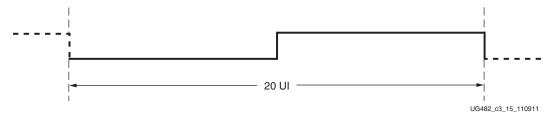

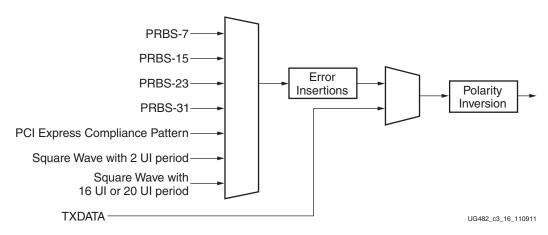

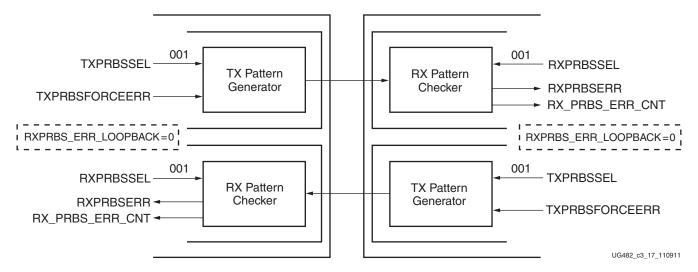

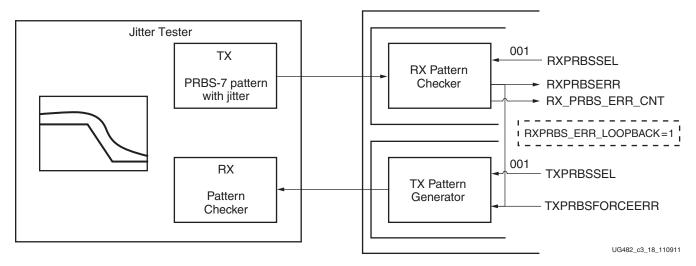

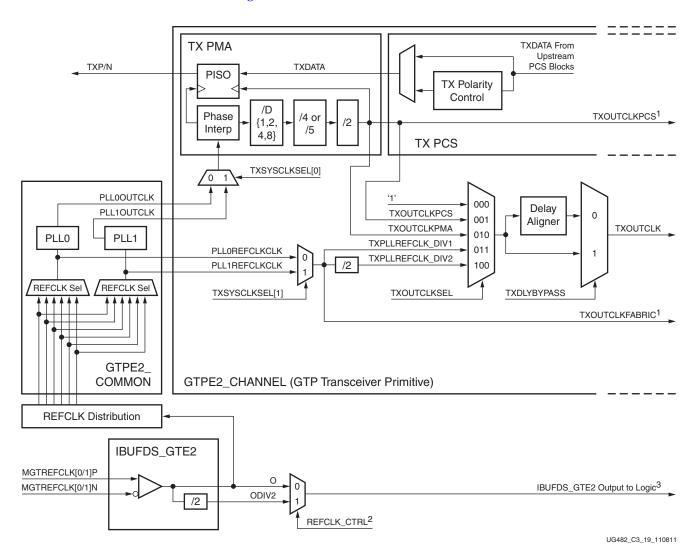

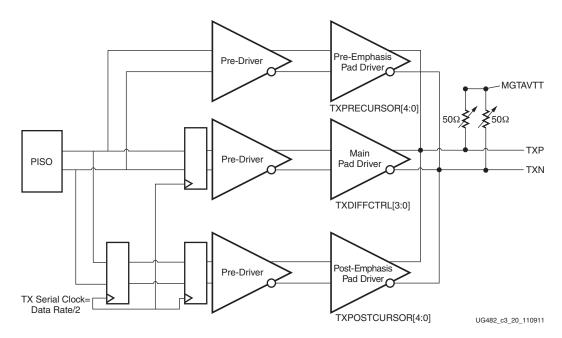

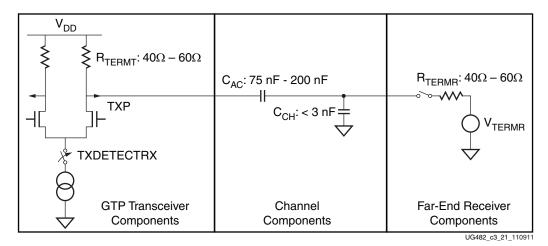

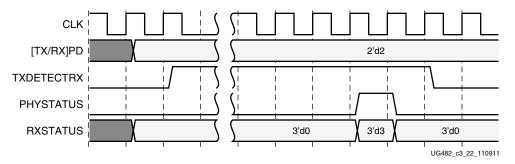

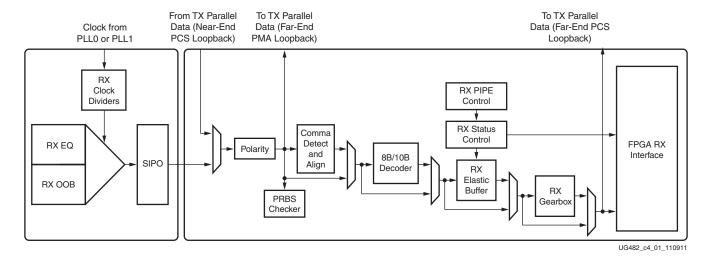

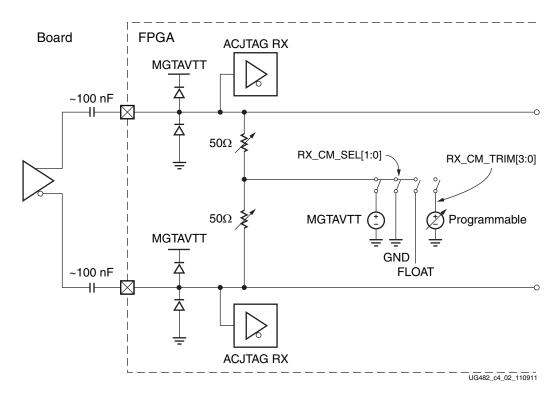

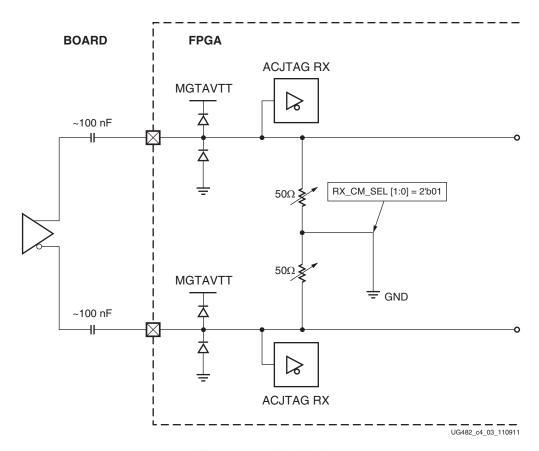

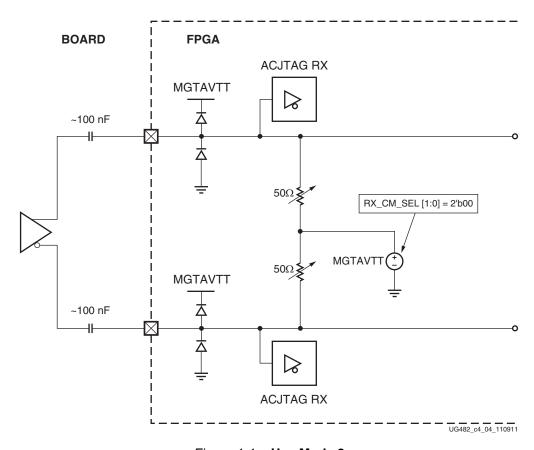

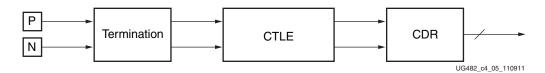

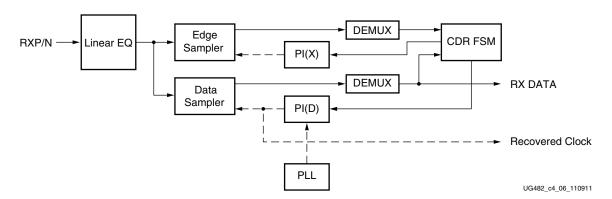

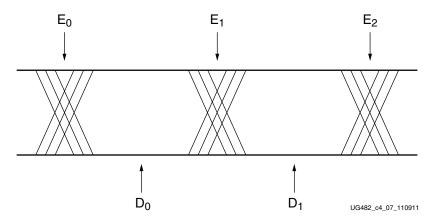

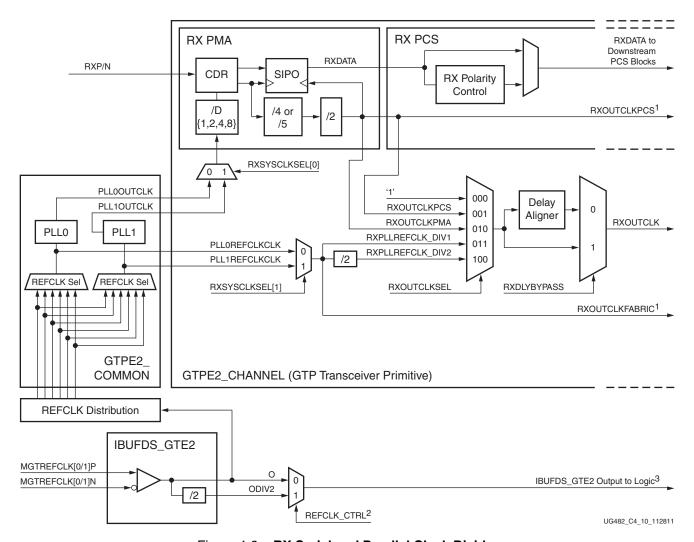

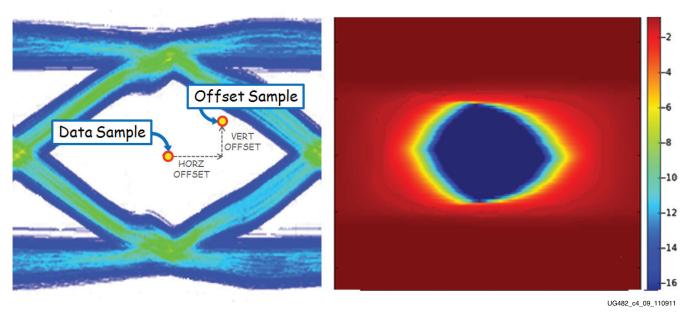

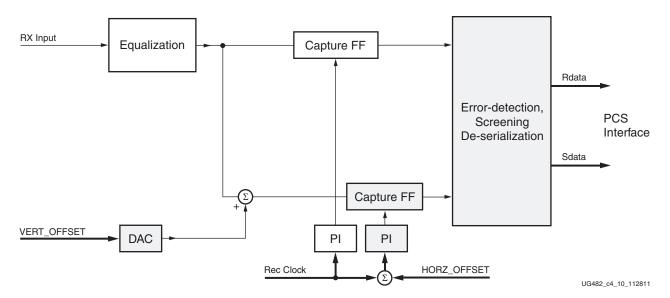

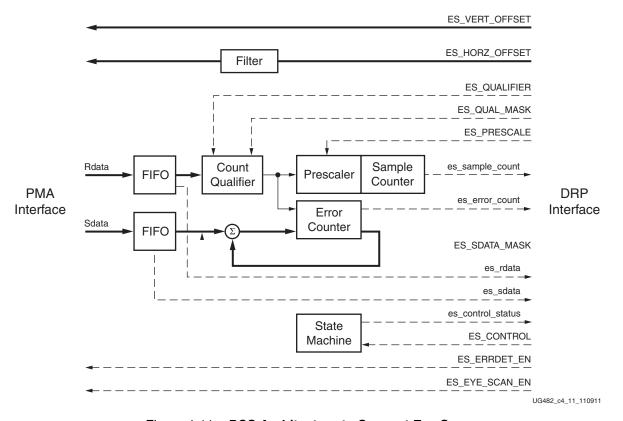

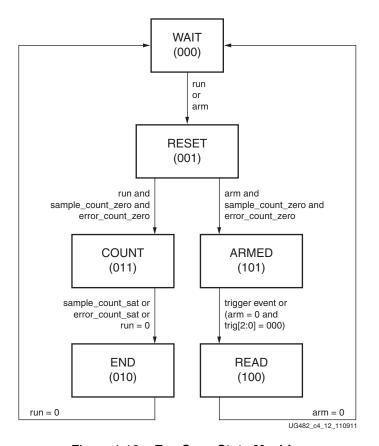

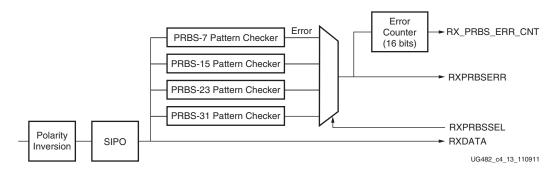

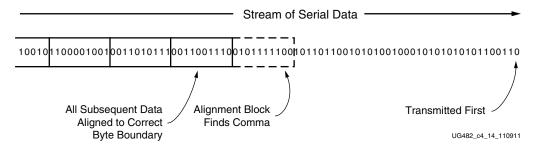

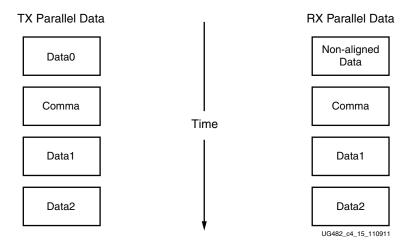

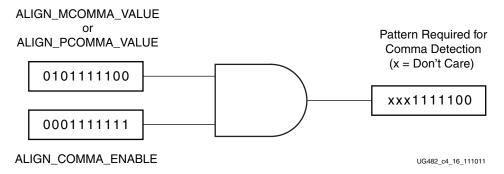

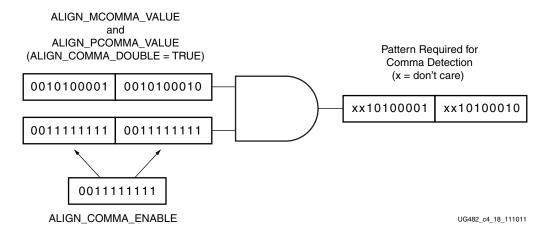

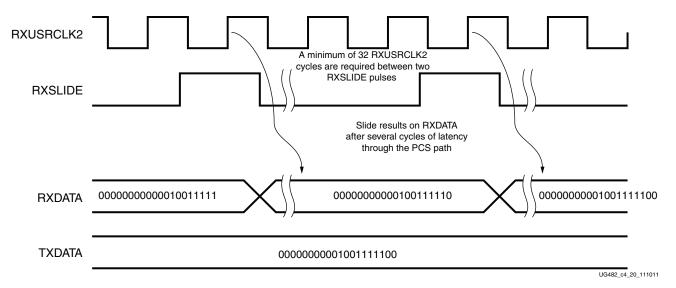

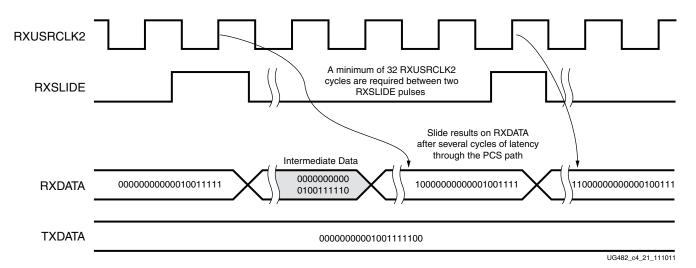

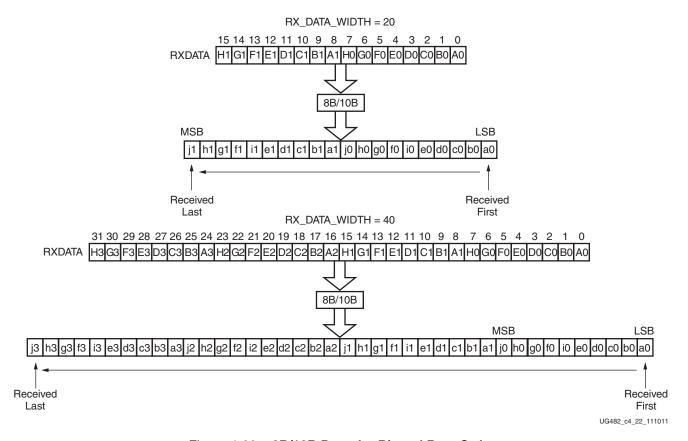

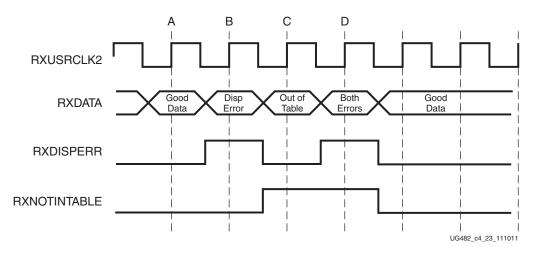

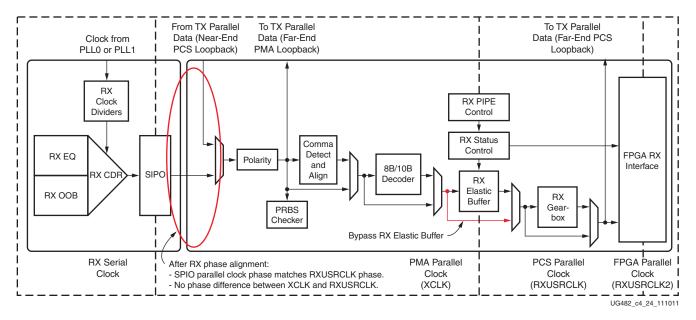

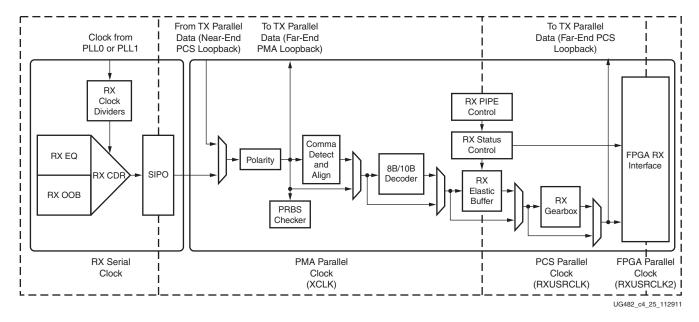

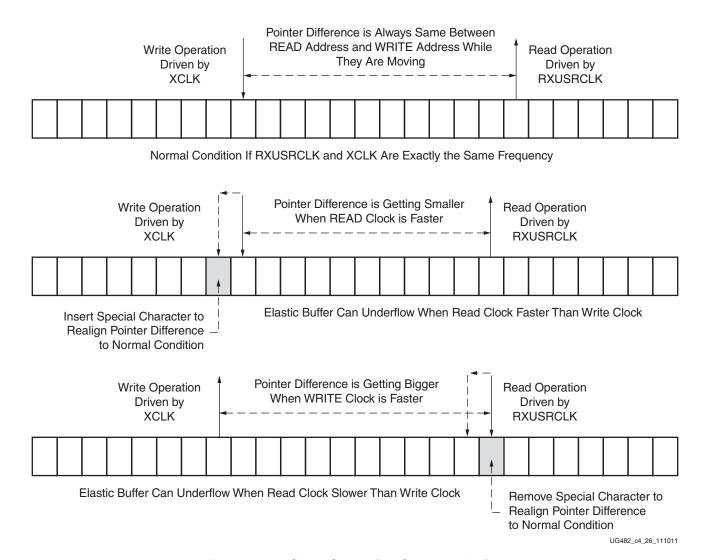

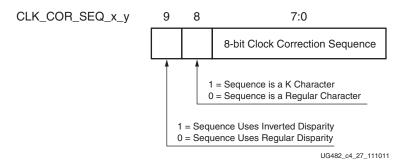

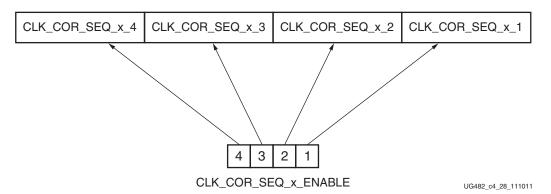

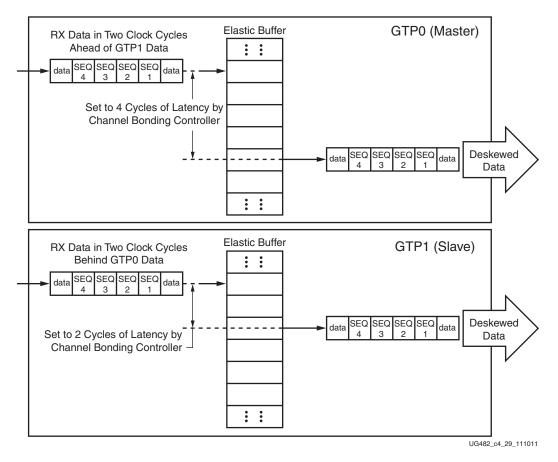

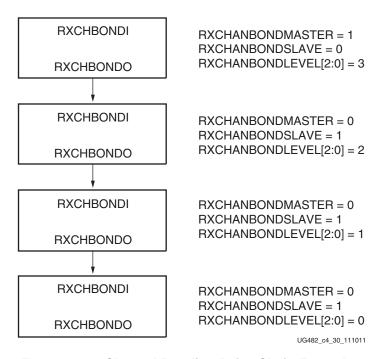

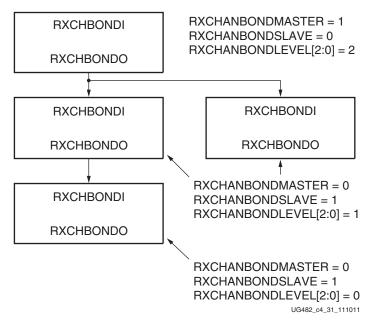

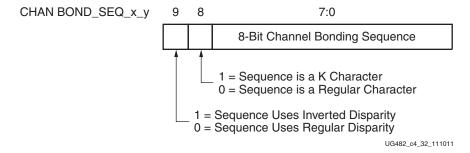

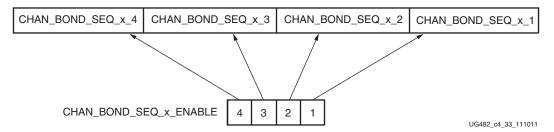

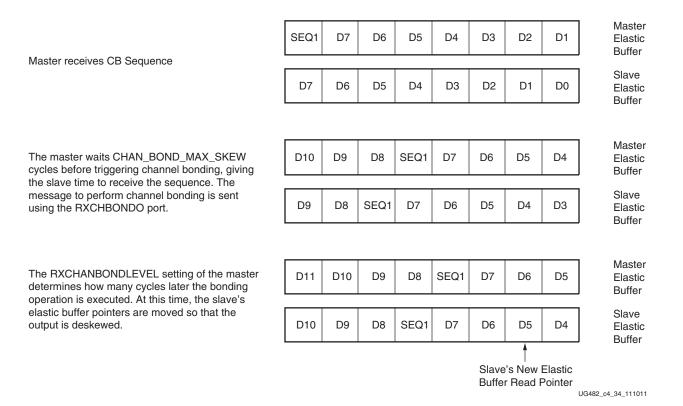

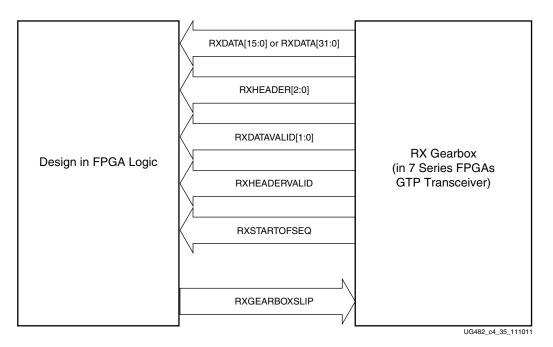

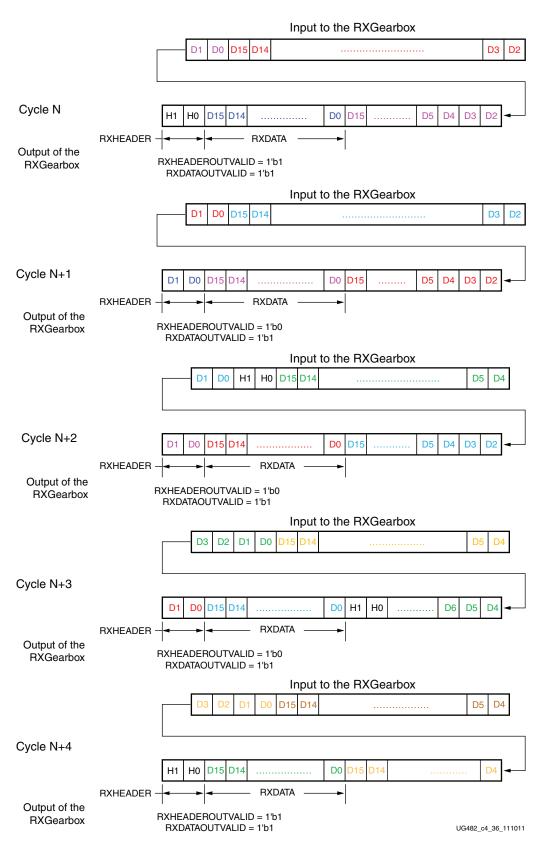

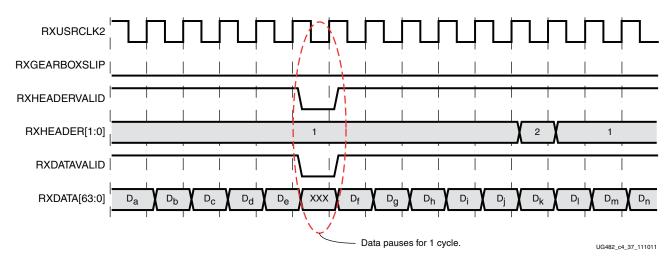

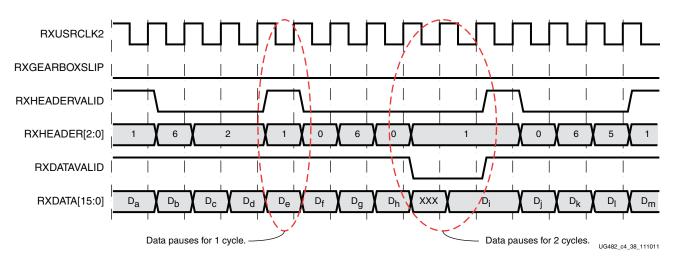

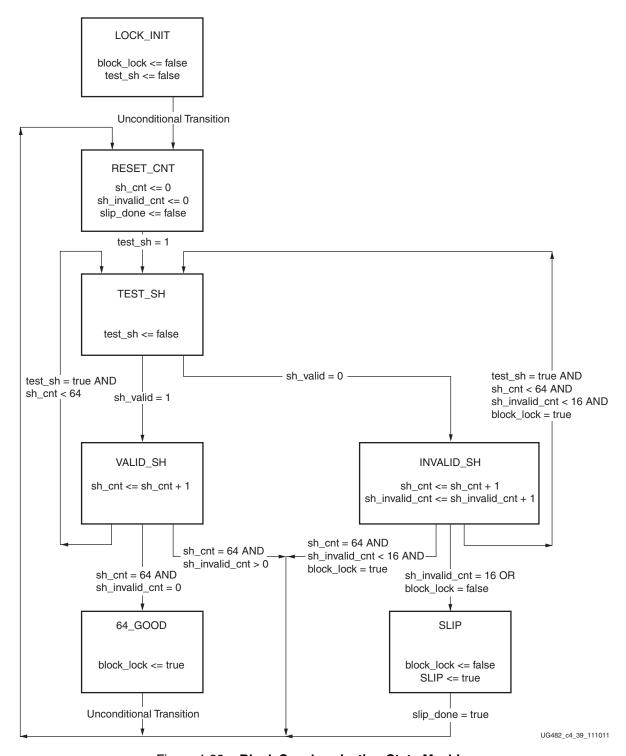

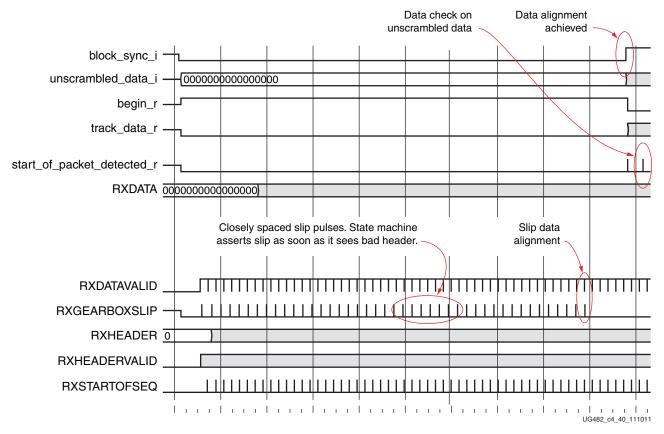

| DRPRDY      | Out | DRPCLK       | Indicates operation is complete for write operations and data is valid for read operations.   |