# **Atmel ATSHA204**

# **Atmel CryptoAuthentication**

#### **DATASHEET**

## **Features**

- Secure authentication and validation device

- Integrated capability for both host and client operations

- Superior SHA-256 hash algorithm, HMAC option

- Best-in-class, 256-bit key length; storage for up to 16 keys

- Guaranteed unique 72-bit serial number

- Internal, high-quality Random Number Generator (RNG)

- 4.5-Kbit EEPROM for keys and data

- 512 OTP (One Time Programmable) bits for fixed information

- Multiple I/O options

- High-speed, single-wire interface

- 1MHz I<sup>2</sup>C interface

- 2.0V 5.5V supply voltage range

- 1.8V 5.5V communications

- <150nA sleep current</p>

- Extended, multi-level hardware security

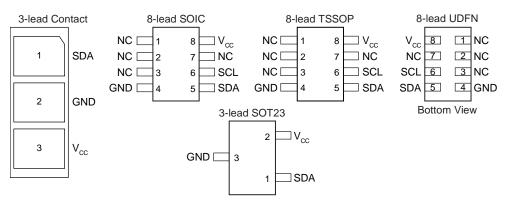

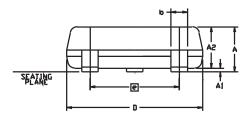

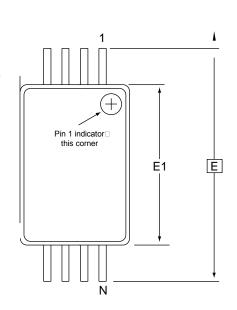

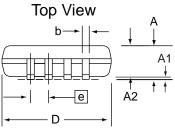

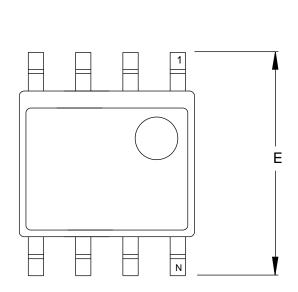

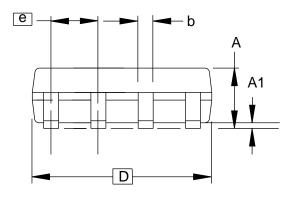

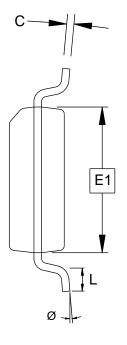

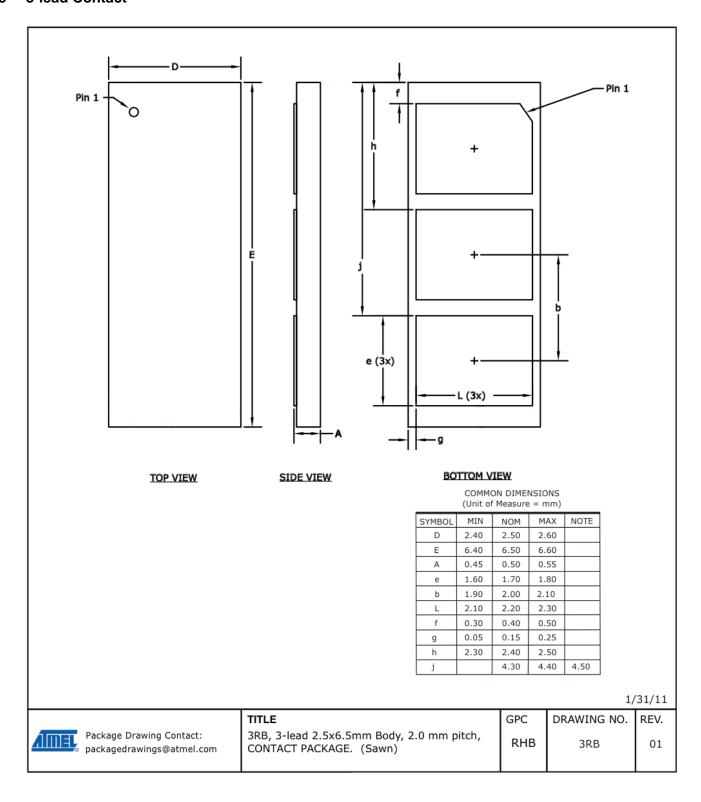

- 8-lead SOIC, 8-lead TSSOP, 3-lead SOT23, 8-pad UDFN, and 3-lead Contact packages

# **Applications**

- Anti-clone protection for accessories, daughter cards, and consumables

- Secure boot validation, software anti-piracy

- Network and computer access control

- Key exchange for encrypted downloads

- Authenticated/encrypted communications for control networks

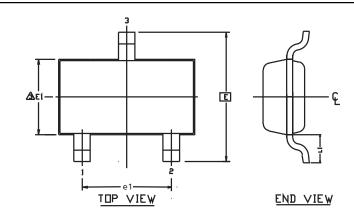

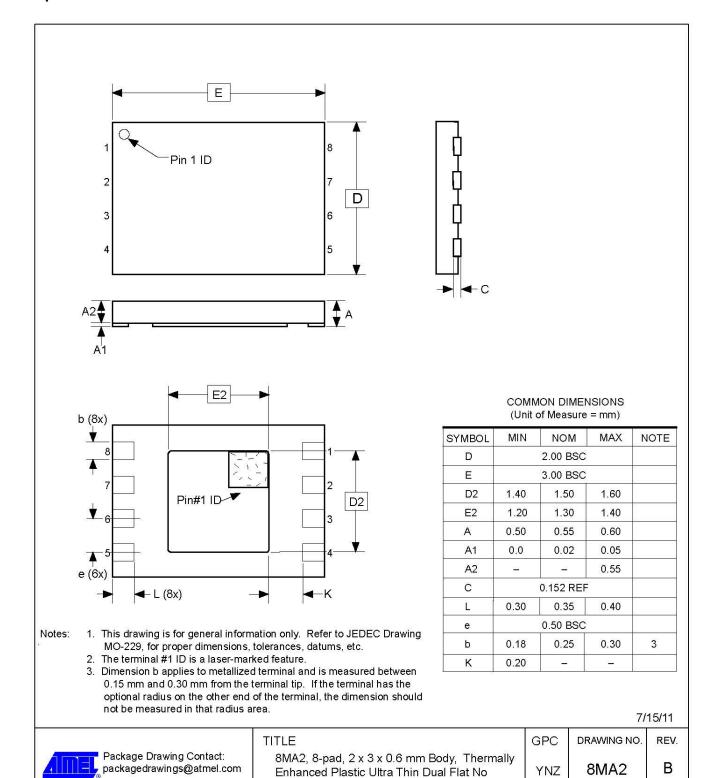

Figure 1. Pin Configurations

| Pin Name        | Function           |

|-----------------|--------------------|

| SDA             | Serial Data        |

| SCL             | Serial Clock Input |

| GND             | Ground             |

| V <sub>CC</sub> | Power Supply       |

## 1. Introduction

The following sections introduce the features and functions of the Atmel® ATSHA204 authentication device.

# 1.1 Applications

The ATSHA204 is a member of the Atmel CryptoAuthentication<sup>™</sup> family of high-security hardware authentication devices. It has a flexible command set that allows use for many applications, including the following:

#### Anti-counterfeiting

Validate that a removable, replaceable, or consumable client is authentic. Example clients could be printer ink tanks, electronic daughter cards, or other spare parts. It can also be used to validate a software/firmware module or memory storage element.

#### Protection for Firmware or Media

Validate code stored in flash memory at boot to prevent unauthorized modifications (aka secure boot), encrypt downloaded media files, and uniquely encrypt code images to be usable on a single system only.

#### Session Key Exchange

Securely and easily exchange stream encryption keys for use by an encryption/decryption engine in the system microprocessor to manage such things as a confidential communications channel or an encrypted download.

#### Secure Data Storage

Store secret keys for use by crypto accelerators in standard microprocessors. It can also be used to store small quantities of data necessary for configuration, calibration, ePurse value, consumption data, or other secrets. Programmable protection up through encrypted/authenticated reads and writes.

#### User Password Checking

Validate user entered passwords without letting the expected value become known, map simple passwords to complex ones, and securely exchange password values with remote system.

## 1.2 Device Features

The ATSHA204 includes an Electrically Erasable Programmable Read-only Memory (EEPROM) array that can be used for storage of keys, miscellaneous read/write, read-only or secret data, consumption logging, and security configuration. Access to the various sections of memory can be restricted in a variety of ways and the configuration then locked to prevent changes. See Section 2.1, "EEPROM Organization," for more details on the EEPROM organization.

The ATSHA204 features a wide array of defensive mechanisms specifically designed to prevent physical attacks on the device itself or logical attacks on the data transmitted between the device and the system (See Section 3.4, "Security Features," for more details). Hardware restrictions on the ways in which keys are used or generated, described in Section 3.3, "Key Values," provide further defense against certain styles of attack.

Access to the device is through a standard I<sup>2</sup>C interface at speeds up to 1Mbit/sec (See Section 6 for details on this interface). It is compatible with standard serial EEPROM I<sup>2</sup>C interface specifications. The device also supports a single-wire interface that can reduce the number of GPIOs required on the system processor and/or reduce the number of pins on connectors. The single-wire interface is described in more detail in Section 5, "Single-wire Interface."

Using either the I<sup>2</sup>C or single-wire interface, multiple ATSHA204 devices can share the same bus, which saves processor GPIO usage in systems with multiple clients such as different color ink tanks or multiple spare parts. See Section 4.2, "Sharing the Interface," and Section 8.10, "Pause Command," for more details on the way in which this is implemented.

Each ATSHA204 ships with a guaranteed unique 72-bit serial number. Using the cryptographic protocols supported by the device, a host system or remote server can prove that the serial number is both authentic and not a copy. Serial numbers are often stored in a standard serial EEPROM, but these can be easily copied, and there is no way for the host to know if the serial number is authentic or a clone.

The Atmel ATSHA204 can generate high-quality random numbers and employ them for any purpose, including as part of the crypto protocols of this device. Because each 256-bit random number is guaranteed to be unique from all numbers ever generated on this or any other device, their inclusion in the protocol calculation ensures that replay attacks (re-transmitting a

previously successful transaction) always fail. Further information is found in Section 3.4.2, "Random Number Generator," and Section 8.11, "Random Command."

System integration is eased with a wide supply voltage range (2.0V through 5.5V) and an ultra-low sleep current of <100nA. Complete DC parameters are found in Section 7, which describes multiple package options, including a tiny SOT23 package with a footprint of only 2.5mm x 3mm. See Section 11, "Package Drawings," for more details and ordering codes.

See Section 9, "Compatibility," for information regarding compatibility with the Atmel AT88SA102S and Atmel AT88SA10HS, previous members of the Atmel CryptoAuthentication family.

## 1.3 Cryptographic Operation

The ATSHA204 supports a standard challenge-response protocol to simplify programming. At its most basic, the host system sends a challenge to the device in the client, which combines that challenge with a secret key via the MAC command from the system, described in Section 8.8, "MAC Command," and sends the response back to the system. The device uses a cryptographic hash algorithm for the combination, which prevents an observer on the bus from deriving the value of the secret key, but allows the recipient to verify that the response is correct by performing the same calculation (combining the challenge with the secret) with a stored copy of the secret.

Due to the flexible command set of the ATSHA204, however, this basic operation can be expanded in many ways. Using the GenDig command (Section 8.5, "GenDig Command") the values in other slots can be included in the response digest, which provides an effective way of proving that a data read really did come from the device, as opposed to being inserted by a manin-the-middle attacker. This same command can be used to combine two keys with the challenge, which is useful when there are multiple layers of authentication to be performed.

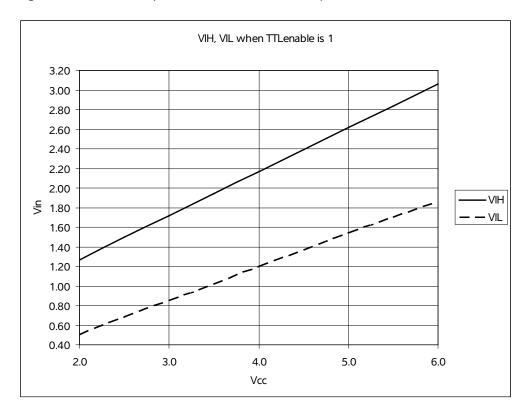

The DeriveKey command (Section 8.3, "DeriveKey Command") implements a key rolling scheme. Depending on the command mode parameter, the resulting operation can be similar to that implemented in a remote-controlled garage door opener. Each time the key is used, the current value of the key is cryptographically combined with a value specific to that system, and the result forms the key for the next cryptographic operation. Even if an attacker gets the value of one key, that key will be gone forever with the next use.

DeriveKey can also be used to generate new random keys that might be valid only for a particular host ID, for a particular time period, or for some other restricted environment. Each generated key is different from any other key ever generated on any device. By "activating" a host-client pair in the field in this manner, a clone of a single client would not work on any other host.

In a host-client configuration where the host (for instance, a mobile phone) needs to verify a client (for instance, an OEM battery), there is a need to store the secret in the host in order to validate the response from the client. The CheckMac command (Section 8.2, "CheckMac Command") allows the host device to securely store the client secret and hide the correct response value from the pins, returning only a yes/no answer to the system.

Where a user-entered password is a requirement, the CheckMac command also provides a way to both verify the password without exposing it on the communications bus as well as map the password to a stored value that can have much higher entropy. See Section 3.3.6 for more details.

Finally, the hash combination of a challenge and secret key can be kept on the device and XORed with the contents of a slot to implement an encrypted read (Section 8.12, "Read Command"), or it can be XORed with encrypted input data to implement an encrypted write (Section 8.14, "Write Command").

Each of these operations can be protected against replay attacks by including a random nonce (Section 8.9, "Nonce Command,") in the calculation.

All security functions are implemented using the industry-standard SHA-256 secure hash algorithm, which is part of the latest set of high-security cryptographic algorithms recommended by various governments and cryptographic experts. Section 3.1, "SHA-256," includes a reference to the algorithm details. If desired, the SHA-256 algorithm can also be included in an HMAC sequence (See Section 3.2, "HMAC/SHA-256," and Section 8.6, "HMAC Command"). The ATSHA204 employs full-sized, 256-bit secret keys to prevent any kind of exhaustive attack.

## 2. Device Organization

The device contains the following memory blocks:

- EEPROM

- SRAM

## 2.1 EEPROM Organization

The EEPROM contains a total of 5312 bits, and is divided into the following zones:

#### Data

A 512-byte (4-Kbit) zone split into 16 general-purpose, read-only, or read/write memory slots of 32 bytes (256 bits) each that can be used to store keys, calibration data, model number, or other information related to the item to which the Atmel ATSHA204 device is attached. Each slot may have different access restrictions based on the values stored in the configuration zone. Within this document the nomenclature slot[yy] indicates the 32-byte value stored in slot yy of the data zone.

#### Configuration

An 88-byte (704-bit) zone that contains serial number and other ID information as well as access permission information for each slot of the data memory. Within this document the nomenclature SN[a:b] indicates a range of bytes within a field of the configuration section. The 88 bytes are accessible from within a three-block address space.

#### OTP (One Time Programmable)

A 64-byte (512-bit) zone which can be used to store read-only data. Prior to locking the OTP zone, the bits may be freely written using the standard Write command. The OTP zone is accessible from within a two-block address space. Within this document the nomenclature OTP[bb] indicates a byte within the OTP zone, while OTP[aa:bb] indicates a range of bytes.

Within this document, the terms "slot" and "block" are used interchangeably to mean a single, 256-bit (32-byte) area of a particular memory zone. The industry SHA-256 documentation uses the term "block" to indicate a 512-bit section of the message input. In addition, the I/O section of this document uses the term "block" to indicate a variable-length aggregate element transferred between the system and the device.

Many sections of this document refer to a keyID, which is equivalent to the slot number for those slots designated to hold key values. Key #1 (sometimes referred to as key[1]) is stored in Slot[1], and so on. While all 16 slots can potentially hold keys, those slots for which clear reads are permitted would not normally be used as keys by the crypto commands.

In this specification, the nomenclature *mode:b* indicates bit b of the parameter mode.

On shipment from Atmel, the EEPROM contains factory test data that can be used for fixed-value board testing. This data must be overwritten with the desired contents prior to locking the configuration and/or data sections of the device. See the Atmel website for the document containing the specific shipment values.

# 2.1.1 Configuration Zone

The 88 bytes in the configuration zone contain manufacturing identification data, general device and system configuration, and access restriction control values for the slots within the data zone. The values of these bytes can always be obtained using the Read command. The bytes of this zone are arranged as shown in Table 2-1.

Table 2-1. Configuration Zone

| Byte #  | Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Write                 | Read   |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|

| 0 → 3   | SN[0:3]      | Part of the serial number value  See the Section 2.1.1.2, "Special Memory Values in the Config Zone (Bytes 0 – 12)"                                                                                                                                                                                                                                                                                                                                                                                                    | Never                 | Always |

| 4 → 7   | RevNum       | Device revision number  See the Section 2.1.1.2, "Special Memory Values in the Config Zone (Bytes 0 – 12)"                                                                                                                                                                                                                                                                                                                                                                                                             | Never                 | Always |

| 8 → 12  | SN[4:8]      | Part of the serial number value  See the Section 2.1.1.2, "Special Memory Values in the Config Zone (Bytes 0 – 12)"                                                                                                                                                                                                                                                                                                                                                                                                    | Never                 | Always |

| 13      | Reserved     | Set by Atmel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Never                 | Always |

| 14      | I2C_Enable   | Bit 0:  0 = the device operates in single-wire interface mode  1 = the device operates in I <sup>2</sup> C interface mode  Bits 1-7 are ignored:  These bits are set at the Atmel factory, depending on the part number, and cannot be changed.                                                                                                                                                                                                                                                                        | Never                 | Always |

| 15      | Reserved     | Set by Atmel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Never                 | Always |

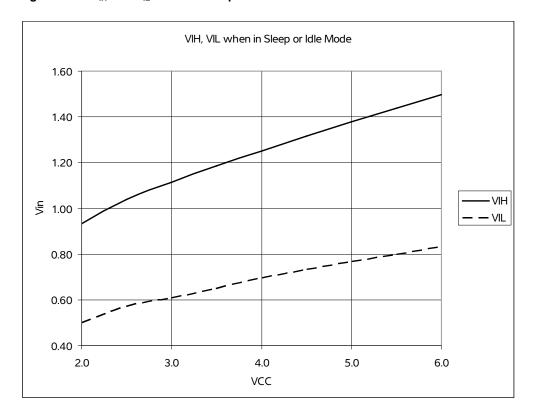

| 16      | I2C_Address  | Bit 0: Ignored Bits 1-7: For $I^2C$ interface parts, the most-significant seven bits of this byte form the device address value to which this device will respond. Bits 1, 2, and 4-7 are ignored for single-wire interface parts. Bit 3 (TTLenable):  1 = the input levels are $V_{CC}$ referenced 0 = the input levels use a fixed reference See Section 7.4.1 for more information. For devices in which the $I^2C$ interface is enabled this byte has a default value of 0xC9 on shipment from Atmel.              | If config<br>unlocked | Always |

| 17      | RFU          | Reserved for future use, must be written to 0x00.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | If config<br>unlocked | Always |

| 18      | OTPmode      | 0xAA (Read-only mode) = Writes to the OTP zone are forbidden when the OTP zone is locked. Reads of all words are permitted.  0x55 (Consumption mode) = Not supported at this time Contact Atmel for more information.  0x00 (Legacy mode) = When the OTP zone is locked, writes to the OTP zone, reads of words 0 and 1, and 32-byte reads are all forbidden. See Section 9 for more information on compatibility with the Atmel AT88SA102S device.  All other values of OTP mode are reserved and should not be used. | If config<br>unlocked | Always |

| 19      | SelectorMode | If 0, then Selector can always be written with UpdateExtra.  If non-zero, Selector can only be written if it currently has a value of zero.  See Section 8.13 for more details.                                                                                                                                                                                                                                                                                                                                        |                       | Always |

| 20 → 51 | SlotConfig   | Two bytes of access and usage permissions and controls for each slot of the data zone. See the SlotConfig (Bytes 20 – 51) section below for more details.                                                                                                                                                                                                                                                                                                                                                              | If config<br>unlocked | Always |

| Byte #                     | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Write                              | Read   |

|----------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------|

| 52,54,56,58<br>60,62,64,66 | UseFlag     | For "single use" keys (Section 3.3), this byte indicates how many times a key may be used before such use is disabled. Applies to keys #0-7 only (byte 52 corresponds to Key0, 54 to Key1, and so on). Initialized to 0xFF. See Section 3.3.                                                                                                                                                                                                                                                                                                                                              | If config<br>unlocked              | Always |

| 53,55,57,59<br>61,63,65,67 | UpdateCount | For keys that can be updated with DeriveKey, these bytes indicate how many times this operation has been performed. Applies to keys #0-7 only, (byte 53 corresponds to Key0, 55 to Key1, and so on).  Initialized to 0x00.  See Sections 3.3 and 8.2.                                                                                                                                                                                                                                                                                                                                     | If config<br>unlocked              | Always |

| 68 → 83                    | LastKeyUse  | 128 bits to control limited use for KeylD 15. Initialized to 0xFF. See Section 3.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | If config<br>unlocked              | Always |

| 84                         | UserExtra   | 1-byte value that can be modified via the UpdateExtra command after the data zone has been locked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Via<br>update<br>extra<br>cmd only | Always |

| 85                         | Selector    | Selects which device will remain in active mode after the execution of the pause command.  See Sections 8.10 and 8.13 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Via<br>update<br>extra<br>cmd only | Always |

| 86                         | LockValue   | Controls the ability to write the OTP and data zones.  0x55 = unlocked  0x00 = locked  On shipment from Atmel, this byte has a value of 0x55 corresponding to the "unlocked" state. After the lock command has been run, this byte will have a value of 0x00, corresponding to "locked." See Sections 2.1.2 and 8.7 for more details.  When locked, the OTP zone can be modified only with the Write command, and slots in the data zone can be modified only if the corresponding WriteConfig field so indicates.  When unlocked, the Read command is prohibited within these two zones. | Via lock<br>command<br>only        | Always |

| 87                         | LockConfig  | Controls the ability to modify the configuration zone.  0x55 = unlocked  0x00 = locked  On shipment from Atmel this byte has a value of 0x55 corresponding to the "unlocked" state. After the lock command has been run, this byte will have a value of 0x00, corresponding to "locked."  See Sections 2.1.2 and 8.7 for more details.                                                                                                                                                                                                                                                    | Via lock<br>command<br>only        | Always |

# 2.1.1.1 SlotConfig (Bytes 20 - 51)

The 16 SlotConfig elements are used to configure the access protections for each of the 16 slots within the ATSHA204. Each configuration element consists of 16 bits, which control the usage and access for that particular slot/key. The SlotConfig field is interpreted according to the following table when the data zone is locked. When the data zone is unlocked, these restrictions do not apply — all slots may be freely written and none may be read.

Table 2-2. SlotConfig Bits (per slot)

| Bit #   | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 → 3   | ReadKey     | Use this keyID to encrypt data being read from this slot using the Read command. If zero, then this slot can be the source for the CheckMac copy operation (see Section 3.3.6). See the description for bit 6 in this table, the Read command description in Section 8.12, and Table 2-3 for more details.  Note: Do <i>not</i> use zero as a default. Do <i>not</i> set this field to zero unless the CheckMac copy operation is explicitly desired, regardless of any other read/write restrictions. |

| 4       | CheckOnly   | <ul> <li>1 = The key stored in the slot can be used only for CheckMac command. It can also be used for GenDig if the subsequent use of TempKey is CheckMac. The key cannot be used by any other command, either directly as KeyID in the input parameter list or via TempKey.</li> <li>0 = The key stored in the slot can be used by all crypto commands.</li> </ul>                                                                                                                                   |

| 5       | SingleUse   | <ul> <li>1 = The key stored in the slot is "single use." See Section 3.3 for more details.</li> <li>Ignored for keys in slots 8-14.</li> <li>0 = There are no usage limitations.</li> </ul>                                                                                                                                                                                                                                                                                                            |

| 6       | EncryptRead | <ul> <li>1 = Reads from this slot will be encrypted using the procedure specified in the Read command description (Section 8.12) using ReadKey (bits 0 – 3 in this table) to generate the encryption key. No input MAC is required. If this bit is set, then IsSecret must also be set (see also Table 2-3).</li> <li>0 = Clear text reads may be permitted.</li> </ul>                                                                                                                                |

| 7       | IsSecret    | <ul> <li>1 = The contents of this slot are secret: Clear text reads are prohibited, and both 4-byte reads and writes are prohibited. This bit <i>must</i> be set if EncryptRead is one or if WriteConfig has any value other than <always> to ensure proper operation of the device.</always></li> <li>0 = The contents of this slot should not contain confidential data or keys.</li> <li>See Table 2-3 for additional information.</li> </ul>                                                       |

| 8 → 11  | WriteKey    | Use this key to validate and encrypt data written to this slot.  See Section 8.14 for additional information.                                                                                                                                                                                                                                                                                                                                                                                          |

| 12 → 15 | WriteConfig | Controls the ability to modify the data in this slot. See Table 2-4 and Section 8.14 for additional information.                                                                                                                                                                                                                                                                                                                                                                                       |

Read operations depend on the state of IsSecret and EncryptRead according to the following table:

Table 2-3. Read Operation Permission

| IsSecret | EncryptRead | Description                                                                                                                                                                                                                       |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0           | Clear text reads are always permitted from this slot. Slots set to this state should never be used as key storage. Either 4 or 32 bytes may be read at a time.                                                                    |

| 0        | 1           | Prohibited. No security is guaranteed for slots using this code.                                                                                                                                                                  |

| 1        | 0           | Reads are never permitted from this slot. Slots set to this state can still be used for key storage.                                                                                                                              |

| 1        | 1           | Reads from this slot are encrypted using the encryption algorithm documented in the Read command description (See Section 8.12).  The encryption key is in the slot specified by ReadKey. 4-byte reads and writes are prohibited. |

The 4-bit WriteConfig field is interpreted by the Write and DeriveKey commands as shown in Table 2-4 and Table 2-5, where X means "don't care."

Note:

The tables overlap. For example, a code of 0110 indicates a slot that can be written in encrypted form using the write command and also can be the target of an unauthorized DeriveKey command with the target as the source.

Table 2-4. Write Configuration Bits – Write Command

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Mode Name | Description                                                                                                                                                                                                                                                 |

|--------|--------|--------|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | 0      | Х      | Always    | Clear text writes are always permitted on this slot. Slots set to<br>"always" should never be used as key storage. Either 4 or 32 bytes<br>may be written to this slot.                                                                                     |

| 0      | 0      | 1      | X      | Never     | Writes are never permitted on this slot using the Write command Slots set to "never" can still be used as key storage.                                                                                                                                      |

| 1      | 0      | Х      | Х      | Never     | Writes are never permitted on this slot using the Write command Slots set to "never" can still be used as key storage.                                                                                                                                      |

| X      | 1      | Х      | X      | Encrypt   | Writes to this slot require a properly computed MAC, and the input data must be encrypted by the system with WriteKey using the encryption algorithm documented in the Write command description (Section 8.13). 4-byte writes to this slot are prohibited. |

Table 2-5. Write Configuration Bits - Derivekey Command

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Source Key <sup>(1)</sup> | Description                                                                                            |

|--------|--------|--------|--------|---------------------------|--------------------------------------------------------------------------------------------------------|

| 0      | X      | 1      | 0      | Target                    | DeriveKey command can be run without authorizing MAC (Roll).                                           |

| 1      | X      | 1      | 0      | Target                    | Authorizing MAC required for DeriveKey command (Roll).                                                 |

| 0      | Х      | 1      | 1      | Parent                    | DeriveKey command can be run without authorizing MAC (Create).                                         |

| 1      | Х      | 1      | 1      | Parent                    | Authorizing MAC required for DeriveKey command (Create).                                               |

| Х      | X      | 0      | Х      | _                         | Slots with this value in the WriteConfig field may not be used as the target of the DeriveKey command. |

Note:

1. The source key for the computation performed by the DeriveKey command can either be the key directly specified in Param2 (the "Target") or the key at slotConfig[Param2].WriteKey (the "Parent") See Section 3.3 for more details.

The IsSecret bit controls internal circuitry necessary for proper security for slots in which reads and/or writes must be encrypted or are prohibited altogether. It must also be set for all slots that are to be used as keys, including those created or modified with DeriveKey. Specifically, to enable proper device operation, this bit must be set unless WriteConfig is "always." 4-byte accesses are prohibited to/from slots in which this bit is set.

Slots used to store key values should always have IsSecret set to one and EncryptRead set to zero (reads prohibited) for maximum security. For fixed key values, WriteConfig should be set to "never." When configured in this way, there is no way to read or write the key after the data zone is locked – it may only be used for crypto operations.

Some security policies require that secrets be updated from time to time. The ATSHA204 supports this capability in the following way: WriteConfig for the particular slot should be set to "Encrypt" and SlotConfig.WriteKey should point back to the same slot by setting WriteKey to the slot ID. A standard Write command can be then used to write a new value to this slot provided that the authentication MAC is computed using the old (current) key value.

## 2.1.1.2 Special Memory Values in the Config Zone (Bytes 0 – 12)

Various fixed information is included in the ATSHA204 that can never be written under any circumstances and can always be read, regardless of the state of the lock bits.

#### SerialNum

Nine bytes (SN[0:8]) which together form a unique value that is never repeated for any device in the CryptoAuthentication family. The serial number is divided into two groups:

#### 1. SN[0:1] and SN[8]

The values of these bits are fixed at manufacturing time in most versions of the Atmel ATSHA204. Their default value is 0x01 23 EE. These 24 bits are always included in the SHA-256 computations made by the Atmel ATSHA204.

### 2. SN[2:3] and SN[4:7]

The values of these bits are programmed by Atmel during the manufacturing process and are different for every die. These 48 bits are optionally included in some SHA-256 computations made by the Atmel ATSHA204.

#### RevNum

Four bytes of information that are used by Atmel to provide manufacturing revision information. These bytes can be freely read as RevNum[0:3], but should never be used by system software, as they may vary from time to time.

## 2.1.2 Device Locking

There are two separate lock states for the device:

- 1. One to lock the configuration zone (controlled by LockConfig, byte 87)

- 2. Second to lock both the OTP and data zones (controlled by LockValue, byte 86)

These lock bits are stored within separate bytes in the configuration zone, and can be modified only through the Lock command. After a memory zone is locked, there is no way to unlock it.

The device should be personalized at the system manufacturer with the desired configuration information, after which the configuration zone should be locked. When this lock is complete, all necessary writes of public and secret information into the EEPROM slots should be performed, using encrypted writes if appropriate. Upon completion of any writes, the data and OTP sections should be locked. Contact Atmel for optional secure personalization services.

It is vital that the data and OTP sections be locked prior to release of the system containing the device into the field. Failure to lock these zones may permit modification of any secret keys and may lead to other security problems.

Any attempt to read or write the data or OTP sections prior to locking the configuration section causes the device to return an error.

#### 2.1.2.1 Configuration Zone Locking

Certain bytes within the configuration zone cannot be modified, regardless of the state of LockConfig. Access to the remainder of the bytes within the zone is controlled using the LockValue byte in the configuration zone, as shown in the following table. Throughout this document, if LockConfig is 0x55, the configuration zone is said to be unlocked; otherwise it is locked.

Table 2-6. Configuration Zone Locking

|                              | Read Access | Write Access    |

|------------------------------|-------------|-----------------|

| LockValue == 0x55 (unlocked) | Read        | Write           |

| LockValue != 0x55 (locked)   | Read        | <never></never> |

### 2.1.2.2 Data Zone Locking

Throughout this document, if LockValue is 0x55, then both the OTP and data zones are said to be unlocked; otherwise they are locked.

Note: There is neither read nor write access to the OTP and data zones prior to locking of the configuration zone.

Table 2-7. Data zone access restrictions

|                              | Read Access     | Write Access |

|------------------------------|-----------------|--------------|

| LockValue == 0x55 (unlocked) | <never></never> | Write        |

| LockValue != 0x55 (locked)   | Read            | Write**      |

## 2.1.2.3 OTP Zone Locking

Reads and writes of the OTP zone depend on the state of the LockConfig, LockValue, and OTPmode bytes in the configuration zone. See Section 2.1.3 for more information.

#### 2.1.3 One Time Programmable (OTP) Zone

This zone of 64 bytes (512 bits) is part of the EEPROM array, and can be used for read-only storage or consumption logging purposes.

Prior to locking the configuration section (using lockConfig), the OTP zone is inaccessible and can be neither read nor written. After configuration locking, but prior to locking of the OTP zone (using lockValue), the entire OTP zone can be written using the Write command. If desired, the data to be written can be encrypted. When unlocked, this zone cannot be read at all.

Once the OTP zone is locked, the OTPmode byte in the configuration zone controls the permissions of this zone, as follows:

#### Read-only Mode

In this mode, the data cannot be modified, and would be used to store fixed model numbers, calibration information, manufacturing history, or other data that should never change. The Write command will always return an error and leave the memory unmodified.

All 64 bytes within the OTP section are always available for reading using either 4- or 32-byte reads.

#### Consumption Mode

This mode is not currently supported. Contact Atmel for further information.

## Legacy Mode

In this mode, the operation of the OTP zone is consistent the fuse array on the Atmel ATSA102S. Reads of words zero and one are always prohibited, while reads of the remaining 14 words are always permitted. Only 32-bit reads are permitted, and any attempt to execute a 256-bit read will result in an error return code. All write operations to the OTP zone are prohibited. See Section 9 or more of the Atmel ATSA102S compatibility details.

All OTP zone bits have a value of one on shipment from the Atmel factory.

## 2.2 Static RAM (SRAM)

The device includes an SRAM array that is used to store the input command or output result, intermediate computation values, and/or an ephemeral key. The entire contents of this memory are always invalidated whenever the device goes into sleep mode or the power is removed. The ephemeral key is named TempKey, and can be used as an input to the MAC, HMAC, CheckMac, GenDig, and DeriveKey commands. It is also used as the data protection (encryption or decryption) key by the Read and Write commands. See below for more details on TempKey.

## 2.2.1 TempKey

TempKey is a storage register in the SRAM array that can be used to store an ephemeral result value from the Nonce or GenDig commands. The contents of this register can never be read from the device (although the device itself can read and use the contents internally).

This register contains the elements shown in Table 2-8.

Table 2-8. TempKey Storage Register

| Name       | Length                 | Description                                                                                                                                                                                                               |

|------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TempKey    | 256 bits<br>(32 bytes) | Nonce (from nonce command) or Digest (from GenDig command)                                                                                                                                                                |

| KeylD      | 4 bits                 | If TempKey was generated by GenDig (see the GenData and CheckFlag bits), these bits indicate which key was used in its computation. The four bits represent one of the slots of the data zone.                            |

| SourceFlag | 1 bit                  | The source of the randomness in TempKey:  0 = Internally generated random number ( <i>Rand</i> ).  1 = Input seed only, no internal random generation ( <i>Input</i> ).                                                   |

| GenData    | 1 bit                  | <ul> <li>0 = TempKey.KeyID is not meaningful, and is ignored.</li> <li>1 = The contents of TempKey were generated by GenDig using one of the slots in the data zone (and TempKey.KeyID will be meaningful).</li> </ul>    |

| CheckFlag  | 1 bit                  | If 1, the contents of TempKey were generated by the GenDig command and at least one of the keys used in that generation is restricted to the CheckMac command (SlotConfig.CheckOnly is 1). Otherwise, this bit will be 0. |

| Valid      | 1 bit                  | 0 = The information in TempKey is invalid.<br>1 = The information in TempKey is valid.                                                                                                                                    |

In this specification, the name "TempKey" refers to the contents of the 256-bit data register. The remaining bit fields are referred to as TempKey.SourceFlag, TempKey.GenData, and so on.

The TempKey. Valid bit is cleared to zero under any of the following circumstances:

- Power up, sleep, brown out, watchdog expiration, or tamper detection. The contents of TempKey, however, are retained when the device enters idle mode.

- After the execution of any command other than Nonce or GenDig, regardless of whether or not the command execution succeeds. It may be cleared by the CheckMac command unless a successful copy takes place. It is not cleared if there is a communications problem, as evidenced by a cyclic redundancy check (CRC) error.

- An error during the parsing or execution of GenDig and/or Nonce.

- Execution of GenDig replaces any previous output of the Nonce command with the output of the GenDig command.

Execution of the Nonce command likewise replaces any previous output of the GenDig command.

# 3. Cryptographic Information

The ATSHA204 implements a challenge-response protocol using either SHA-256 or HMAC/SHA-256, details are below. The response is always a 256-bit digest.

The Nonce command (see Section 8.9) accepts an input challenge from the system and optionally combines it with an internally generated random number to generate a nonce (number used once) for the calculation. This seed is then combined with a secret key as part of the authentication calculation for any of the crypto commands (MAC, HMAC, Read, Write, or GenDig). For compatibility reasons, the input challenge may be passed directly to the MAC command; however, this operation is deprecated.

The device can guarantee the uniqueness of the Nonce only if the device has included the output of its random number generator in the calculation, because the system input may or may not be unique. Every random Nonce is guaranteed to be unique when compared to all previous nonces, ensuring that each transaction is unique over all time.

#### 3.1 SHA-256

The ATSHA204 MAC command calculates the digest of a secret key concatenated with the challenge or nonce. It optionally includes various other pieces of information stored on the device within the digested message.

The ATSHA204 computes the SHA-256 digest based on the algorithm documented here:

http://csrc.nist.gov/publications/fips/fips180-2/fips180-2.pdf

The complete SHA-256 message processed by the ATSHA204 is listed in Sections 8.5 and 8.9 for each of the particular commands (GenDig and Nonce) that use the algorithm. Most standard software implementations of the algorithm automatically add the appropriate number of pad and length bits to this message to match the operation the device performs internally.

The SHA-256 algorithm is also used for encryption by taking the output digest of the hash algorithm and XORing it with the plain text data to produce the ciphertext. Decryption is the reverse – the ciphertext is XORed with the digest, and the result is the plain text.

## 3.2 HMAC/SHA-256

The response to the challenge can also be computed using the HMAC algorithm based on SHA-256 documented here:

http://csrc.nist.gov/publications/fips/fips198/fips-198a.pdf

Because of the increased computation complexity, the HMAC command is not as flexible as the MAC command and the computation time for HMAC is extended. While the HMAC sequence is not necessary to ensure the security of the digest, it is included for compatibility with various software packages.

## 3.3 Key Values

All keys within the CryptoAuthentication family are 256 bits long. The ATSHA204 uses these keys as part of the messages hashed with the MAC, CheckMac, HMAC, and GenDig commands. Any slot in the data zone of the EEPROM can be used to store a key, though the value will be secret only if the read and write permissions are properly set within SlotConfig (including the IsSecret bit).

Except for the GenDig command, all but the least-significant four bits of the KeyID parameter are ignored in determining the source of key data. Only the least-significant four bits are used to select one of the slots of the data zone. See Section 3.3.7, below, for information on how GenDig uses other KeyID values.

In all cases for which a SHA-256 calculation is performed using Param2, the entire 16-bit KeyID as input is included in the message.

## 3.3.1 Diversified Keys

If the host or validating entity has a place to securely store secrets, the key values stored in the EEPROM slot(s) can be diversified with the serial number embedded in the device (SN[0:8]). In this manner, every client device can have a unique key, which can provide extra protection against known plaintext attacks and permit compromised serial numbers to be identified and blacklisted.

To implement this, a root secret is externally combined with the device serial number during personalization using some cryptographic algorithm and the result written to the ATSHA204 key slot.

The ATSHA204 CheckMac command provides a mechanism of securely generating and comparing diversified keys, eliminating this requirement from the host system.

Consult the following application note for more details:

http://www.atmel.com/dyn/resources/prod\_documents/doc8666.pdf

## 3.3.2 Rolled Keys

In order to prevent repeated use of the same key value, the ATSHA204 supports key rolling. Normally, after a certain number of uses (perhaps as few as one), the current key value is replaced with the SHA-256 digest of its current value combined with some offset, which may either be a constant, something related to the current system (for example, a serial number or model number), or a random number.

This capability is implemented using the DeriveKey command. Prior to execution of the DeriveKey command, the Nonce command must be run to load the offset into TempKey. Each time the roll operation is performed on slots 0-7, the UpdateCount field for that slot is incremented.

One use for this capability is to permanently remove the original key from the device, replacing it with a key that is only useful in a particular environment. After the key is rolled, there is no possible way to retrieve the old value, which improves the security of the system.

Note:

Any power interruption during the execution of the DeriveKey command in Roll mode may cause either the key or the UpdateCount to have an unknown value. If writing to a slot is enabled using bit number 14 of SlotConfig, such keys can be written in encrypted and authenticated form using the Write command. Alternatively, multiple copies of the key can be stored in multiple slots so that failure of a single slot does not incapacitate the system.

#### 3.3.3 Created Keys

In order to support unique ephemeral keys for every client, the ATSHA204 also supports key creation. In this mechanism, a "parent" key (specified by slotConfig.writeKey) is combined with a fixed or random nonce to create a unique key, which is then used for any cryptographic purpose.

The ability to create unique keys is especially useful if the parent key has usage restrictions (see "Single-use Keys" and "Limited-use Key" in the following sections). In this mode, the limited use parent key can be employed to create an unlimited use child key. Because the child key is useful only for this particular host-client pair, attacks on its value are less valuable.

This capability is also implemented using the DeriveKey command. Prior to execution of the DeriveKey command, the Nonce command must be run to load the Nonce value into TempKey. Each time the create operation is performed on slots 0-7; the UpdateCount field for that slot is incremented.

#### 3.3.4 Single-use Keys

For the KeyID values corresponding to slots 0-7 in the data section of the EEPROM, repeated usage of the key stored in the slot can be strictly limited. This feature is enabled if the SingleUse bit is set in the SlotConfig field. The SingleUse bit is ignored for slots 8-14. The number of remaining uses is stored as a bit map in the UseFlag byte corresponding to the slot in question.

Prior to execution of any cryptographic command that uses this slot as a key, the following takes place:

- If SlotConfig[keyId].SingleUse is set and UseFlag[KeyID] is 0x00, the device returns an error.

- Starting at bit seven of UseFlag[keyID], clear to zero the first bit that is currently a one.

In practice, this procedure permits SingleUse keys to be used eight times between "refreshes" using the DeriveKey command. If power is lost during the execution of any command referencing a key that has this feature enabled, one of the use bits in UseFlag may still be cleared even though the command did not complete. For this reason, Atmel recommends that the key be used a single time only, with the other bits providing a safety margin for errors.

Under normal circumstances, all eight UseFlag bytes should be initialized to 0xFF. If it is the intention to permit fewer than eight uses of a particular key, these bytes should be initialized to 0x7F (seven uses), 0x3F (six uses), 0x1F (five uses), 0x0F (four uses), 0x07 (three uses), 0x03 (two uses), or 0x01 (one use). Initialization to any other value besides these values or 0xFF is prohibited.

The Read, Write, and DeriveKey commands operate slightly differently:

#### Read and Write

These commands ignore the state of the SingleUse bit and the UseFlag byte does not change as a result of their execution. SingleUse slots in which the UseFlag is exhausted (value of 0x00) can still be read or written (subject to the appropriate SlotConfig limitations) although the value in the slot cannot ever be used as a key for cryptographic commands.

If SlotConfig.WriteKey for slot X points back to X, but UseFlag[X] is exhausted, encrypted writes to the slot will never succeed because the prior GenDig command will have returned an error due to the usage limitation. A similar situation occurs with reads and ReadKey. Slots used as keys should never have IsSecret set to zero or WriteConfig set to Always.

#### DeriveKey

If the parent key is used for either authentication or as the source, then if SingleUse (for the parent) is set and UseFlag (also for the parent) is 0x00, the DeriveKey command returns an error. The SingleUse and UseFlag bits are ignored for the target key. When successfully executed, DeriveKey always resets the UseFlag to 0xFF for the target key – this is the only mechanism to reset the UseFlag bits.

Use of the DeriveKey command is optional – it is legal to be run only if WriteConfig: 13 is set for this slot. In some situations, it may be advantageous to simply have a key that can be used eight times, in which case the other crypto commands will clear the bits in UseFlag one at a time until all are cleared, and at which time the key is disabled.

#### 3.3.5 Limited-use Key

If Slot[15]. SingleUse is set, usage of key number 15 is limited through a different mechanism than the single-use limitation described above, which applies only to slots 0-7.

Prior to any use of key 15 by a cryptographic command, the following takes place:

- If all bytes in LastKeyUse are 0x00, return error.

- Starting at bit seven of the first byte of LastKeyUse (byte 68 in config zone), clear to zero the first bit that is currently

a zero. If byte 68 is 0x00, check bit seven of byte 69, and so on up through byte 83. Only a single bit is cleared each

time prior to using key 15.

There is no reset mechanism for this limitation – after 128 uses (or the number of one bits set in LastKeyUse on personalization), key 15 is permanently disabled. This capability is not susceptible to power interruptions – even if the power is interrupted during execution of the command, only a single bit in LastKeyUse will be unknown; all other bits in LastKeyUse will be unchanged and the key will remain unchanged.

If fewer than 128 uses are desired for key 15, then some of the bytes within this array should not be initialized to 0xFF. As with UseFlag, the only legal values for bytes within this field (besides 0xFF) are 0x7F, 0x3F, 0x1F, 0x0F, 0x07, 0x03, 0x01, or 0x00. The total number of bits set to one indicates the number of uses. One example of how to set 16 uses is as follows: 0xFF, 0x0F, 0x00, 0x00.

The SingleUse bit is ignored by the Read and Write commands, and lastKeyUse does not change as a result of their execution. The SingleUse bit is ignored by the copy function of the CheckMac command. The SingleUse bit is honored for the parent key in the DeriveKey command, but is ignored for the target key.

### 3.3.6 Password Checking

Many applications require a user to enter a password to enable features, decrypt stored data, or some other purpose. Typically, the expected password has to be stored somewhere in memory and is, therefore, subject to discovery. The ATSHA204 can securely store the expected password and perform a number of useful operations on it. The password is never passed in the clear to the device, nor can it be read from the device. It is hashed with a random number in the system software before being passed to the device.

The copy capability of the CheckMac command enables the following types of password checking options:

- 1. CheckMac does an internal comparison with the expected password and returns a Boolean to the system to indicate whether the password was correctly entered or not.

- 2. If the device determines that the correct password has been entered, then the value of the password can optionally be combined with a stored or ephemeral value to create a key that can be used by the system for data protection purposes.

- 3. If the device determines that the correct password has been entered, the device can use this fact to optionally release a secondary, high entropy secret, which can be used for data protection without risk of any exhaustive dictionary attack.

- 4. If the password has been lost, an entity with knowledge of a parent key value can optionally write a new password into the slot. Also optionally, the current value can be encrypted with a parent key and read from the device.

Passwords should be stored in even-numbered slots. If the password is to be mapped to a secondary value (use #3 above), then the target slot containing this value is located in the next higher slot number (the password slot number plus one). Otherwise, the target slot is the same as the password slot.

ReadKey for the target slot must be set to zero to enable this capability. In order to prevent fraudulent or unintended usage of this capability, do not set ReadKey for any slot to zero unless this CheckMac/copy capability is specifically required. In particular, do not assume that other bits in the configuration word for a particular slot override the enablement of this capability specified by ReadKey = 0.

This capability is enabled only if the mode parameter to CheckMac has a value of 0x01, indicating:

- The first 32 bytes of the SHA-256 message are stored in a data slot in the EEPROM (the password).

- b. The second 32 bytes of the SHA-256 message must be a randomly generated nonce in the TempKey register.

If the above conditions are met and the input response matches the internally generated digest, then the contents of the target key are copied to TempKey. The other TempKey register bits are set as follows:

- SourceFlag is set to one (not random)

- GenData is set to zero (not generate by the GenData command)

- CheckFlag is set to zero (TempKey is not restricted to the CheckMac command)

- Valid is set to one

## 3.3.7 Transport Keys

The ATSHA204 device includes an internal hardware array of keys (transport keys) that are intended for secure personalization prior to locking of the data section. The values of the hardware keys are kept secret, and are made available to qualified customers upon request to Atmel. These keys can be used with the GenDig command only, and are indicated by a KeylD value  $\geq 0x8000$ .

This is the intended personalization command flow:

- 1. Write intended values to the configuration zone, and then lock the configuration zone.

- 2. Write non-secret slots and OTP zone, data should be passed to the device in the clear.

- 3. Generate a random personalization key in any one of the secret slots with the following sequence:

- a. Nonce command to generate a random nonce in TempKey

- b. Gendig specifying a transport key ≥ 0x8000

- c. Gendig using the compliance (default) value stored in the slot to be used for personalization

- d. Encrypted Write to that same slot (overwrites the compliance value)

- 4. Use that personalization key to write all the secret slots, ending with the final value of the personalization key slot itself, using the following sequence repeated as necessary:

- a. Nonce command to generate a random nonce in TempKey

- b. Gendig specifying the personalization key

- Encrypted write to the target slot

- 5. Lock the data zone

For GenDig and all other commands, KeyID values less than 0x8000 always reference keys that are stored in the data zone of the EEPROM. In these cases, only the four least-significant bits of KeyID are used to determine the slot number, while the entire 16-bit KeyID as input is used in any SHA-256 message calculation.

## 3.4 Security Features

### 3.4.1 Physical Security

The ATSHA204 incorporates a number of physical security features designed to protect the EEPROM contents from unauthorized exposure. The security measures include:

- An Active Shield over the part

- Internal Memory Encryption

- Secure Test Modes

- Glitch Protection

- Voltage Tamper Detection

Pre-programmed transport keys stored on the ATSHA204 are encrypted in such a way as to make retrieval of their values using outside analysis very difficult.

Both the logic clock and logic supply voltage are internally generated, preventing any direct attack on these two signals using the pins of the device.

#### 3.4.2 Random Number Generator (RNG)

The ATSHA204 includes a high-quality random number generator that returns 32 random bytes to the system. The device combines this generated number with a separate input number to form a nonce that is stored within the device in TempKey and may be used by subsequent commands.

The system may use this random number generator for any purpose. One common purpose would be as the input challenge to the MAC command on a separate CryptoAuthentication device. The device provides a special Random command for such purposes, which does do not affect the internally stored nonce.

To simplify system testing, prior to config locking the random number generator always returns the following value:

ff ff 00 00 ff ff 00 00 ...

where ff is the first byte read from the device and the first byte into the SHA message.

To prevent replay attacks on encrypted data that is passed to or from the ATSHA204, the device requires that a new, internally generated nonce be included as part of the encryption sequence used to protect the data being written or read. To implement this requirement, the data protection key generated by GenDig and used by the Read or Write command must use the internal random number generator during the creation of the Nonce.

Random numbers are generated from a combination of the output of a hardware random number generator and an internal seed value, which is not externally accessible. The internal seed is stored in the EEPROM, and is normally updated once after every power-up or sleep/wake cycle. After the update, this seed value is retained in registers within the device that are invalidated if the devicez enters sleep mode or the power is removed.

Because there is an EEPROM endurance specification that limits the number of times the EEPROM seed can be updated, the host system should manage power cycles to minimize the number of required updates. In certain circumstances, the system may choose to suppress the EEPROM seed update using the mode parameter to the Nonce and Random commands.

Because this may affect the security of the system, it should be used with caution. See Section 8.9 and Section 8.11 for more information about how the EEPROM seed update is controlled.

### 4. General I/O Information

Communications with the ATSHA204 are achieved through one of two different protocols, and selected using the part number that is ordered:

#### Single-wire Interface

This mode uses a single GPIO connection on the system microprocessor connected to SDA on the device. It permits the fewest number of connector pins to any removable/replaceable entity. The bit rate is up to 26-Kbits/sec.

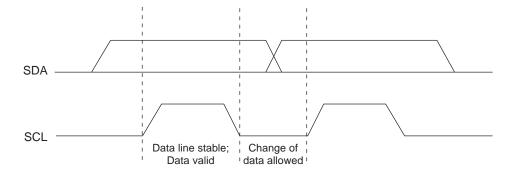

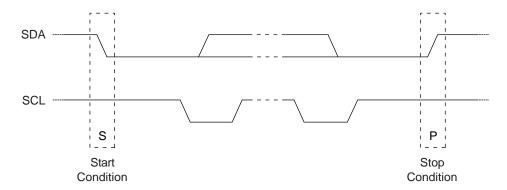

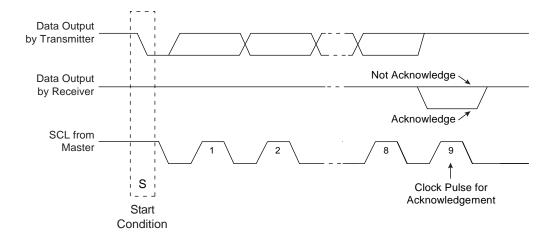

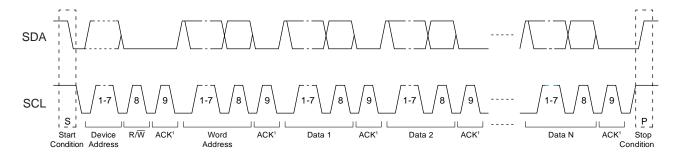

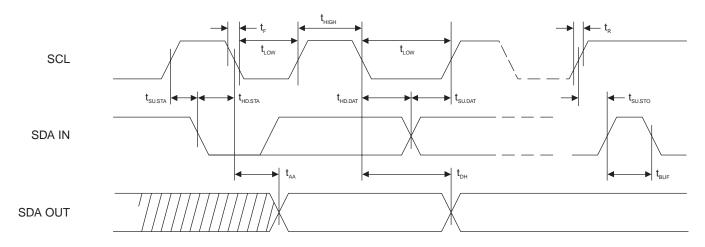

## I<sup>2</sup>C Interface

This mode is compatible with the Atmel AT24C16B Serial EEPROM interface. Two pins, Serial Data (SDA) and Serial Clock (SCL) are required. The I<sup>2</sup>C interface supports a bit rate of up to 1Mbit/sec.

The lowest levels of the I/O protocols are described below in Sections 5 and 6. Above the I/O protocol level, however, exactly the same bytes are transferred to and from the device to implement the cryptographic commands and error codes documented in Section 8.

Note:

The device implements a failsafe internal watchdog timer that forces it into a very low power mode after a certain time interval, regardless of any current activity. System programming must take this into consideration. See Section 8.1.6 for more details.

## 4.1 Byte and Bit Ordering

CryptoAuthentication uses a common ordering scheme for bytes and also for the way in which numbers and arrays are represented in this datasheet:

- All multi-byte aggregate elements are treated as arrays of bytes and are processed in the order received or transmitted with index #0 first.

- 16-bit (2-byte) integers, typically Param2 appear on the bus least-significant byte first.

In this document, the most-significant bit or nibble of a byte or 16-bit word appears towards the left hand side of the page.

The bit order is different depending on the I/O channel used:

- On the one-wire interface, data is transferred to/from the Atmel ATSHA204 least-significant bit first on the bus.

- On the I<sup>2</sup>C interface, data is transferred to/from the Atmel ATSHA204 most-significant bit first on the bus.

#### 4.1.1 Output Example

The following bytes will be returned in this order on the bus by a 32-byte read of the configuration section with an input address of 0x0000:

SN[0], SN[1], SN[2], SN[3], RevNum[0], RevNum[1], RevNum[2], RevNum[3], SN[4], SN[5], SN[6], SN[7], SN[8], reserved, I2C Enable, reserved, I2C\_Address, TempOffset, OTPmode, SelectorMode, SlotConfig[0].Read, SlotConfig[0].Write, SlotConfig[1].Read, SlotConfig[1].Write, SlotConfig[2].Read, SlotConfig[2].Write, SlotConfig[3].Read, SlotConfig[3].Write, SlotConfig[4].Write, SlotConfig[5].Read, SlotConfig[5].Write

## 4.1.2 MAC Message Example

The following bytes will be passed to the SHA engine for a MAC command using a mode value of 0x71 and a KeyID of slot x. In the example below, K[x] indicates the KeyID of slot x in the data zone, with K[0] being the first byte on the bus for a read from or write to that slot. OTP[0] indicates the first byte on the bus for a read of the OTP zone at address zero, and so on.

For more details regarding MAC messages, see Section 8.8, "MAC Command."

## 4.2 Sharing the Interface

Multiple CryptoAuthentication devices may share the same interface, as follows:

- a. System issues a Wake token (see Section 5.1) to wake up all devices.

- b. The system issues the Pause command to put all but one of the devices into idle mode. Only the remaining device then sees any commands the system sends. When the system has completed talking to the one active device, it sends an idle flag, which the idle devices ignore but which puts the single remaining active device into the idle mode. See Section 8.10, "Pause Command," for more details.

Steps a and b are repeated for each device on the wire. If the system has completed communications with the final device, it should wake all the devices up and then put all the devices to sleep to reduce total power consumption.

The device uses the selector byte within the configuration zone to determine which device stays awake – only that device with a selector value that matches the input parameter of the Pause command stays awake. In order to facilitate late configuration of systems that use the multi-device sharing mode, the following three update capabilities for the selector byte are supported:

#### 1. Unlimited Updates

At any time, the UpdateExtra command can be executed to write the value in the selector field of the configuration zone. To enable this mode, set the SelectorMode byte in the configuration zone to zero.

#### 2. One-time Field Update

If the SelectorMode byte is set to a non-zero value and the selector byte is set to a zero value prior to locking the configuration zone, then at any time after the configuration zone is locked the UpdateExtra command can be used one time to set Selector to a non-zero value. The UpdateExtra command is not affected by the LockValue byte.

#### 3. Fixed Selector Value

The selector byte can never be modified after the configuration zone is locked if both SelectorMode and Selector are set to non-zero values. The UpdateExtra command will always return an error code.

# 5. Single-wire Interface

In this mode, communications to and from the ATSHA204 take place over SDA, a single, asynchronously timed wire, and the SCL pin is ignored.

Note: The sleep current specification values are guaranteed only if the SCL pin is held low or left unconnected.

The overall communications structure is a hierarchy:

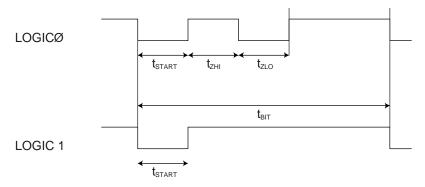

**Tokens** I/O tokens implement a single data bit transmitted on the bus, or the wake-up event.

Flags consist of eight tokens (bits) that convey the direction and meaning of the next group of bits (if any)

that may be transmitted.

**Blocks** Blocks of data follow the command and transmit flags. They incorporate both a byte count and a checksum

to ensure proper data transmission.

Packets Packets of bytes form the core of the block (minus the byte count and CRC). They are either the input or

output parameters of a CryptoAuthentication command or status information from the Atmel ATSHA204.

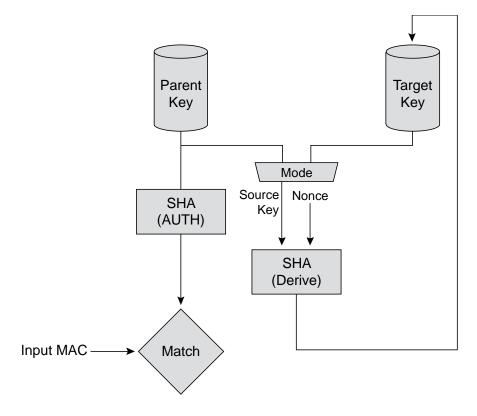

See the Atmel website for the appropriate application notes for more details on how to use any microprocessor to easily generate the signaling necessary to send these elements to the device, including C source code libraries. Also, see Section 10.2, "Wiring Configuration for Single-wire Interface," for more information about how to connect the device in the single-wire interface mode.

#### 5.1 I/O Tokens

There are a number of I/O tokens that may be transmitted over the single-wire interface:

**Input**: (to the Atmel ATSHA204)

Wake Wake the device up from either sleep or idle states.

Zero Send a single bit from the system to the device with a value of zero.One Send a single bit from the system to the device with a value of one.

Output: (from the Atmel ATSHA204)

ZeroOut Send a single bit from the device to the system with a value of zero.OneOut Send a single bit from the device to the system with a value of one.

The waveforms are the same in either direction. There are some differences in timing, however, based on the expectation that the host has a very accurate and consistent clock, while the ATSHA204 has significant part-to-part variability in its internal clock generator, due to normal manufacturing and environmental fluctuations.

The bit timings are designed to permit a standard UART running at 230.4K baud to transmit and receive the tokens efficiently. Each byte transmitted or received by the UART corresponds to a single bit received or transmitted by the device.

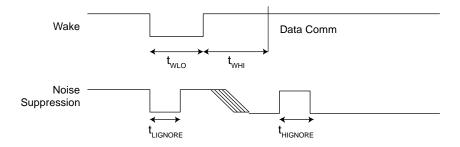

The Wake token is special in that it requires an extra long low pulse on the SDA pin, which cannot be confused with the shorter low pulses that occur during a data token (Zero, One, ZeroOut, OneOut). Devices that are in either the idle or sleep state ignore all data tokens until they receive a legal Wake token. Do not send a Wake token to devices that are awake, as they will lose synchronization because the waveform can be resolved to neither a legal one nor zero. See Section 5.3.2 for the procedure to regain synchronization.

## 5.2 I/O Flags

The system is always the bus master, so before any I/O transaction, the system must send an 8-bit flag to the device to indicate the I/O operation to be subsequently performed, as shown in Table 5-1.

Table 5-1. I/O flags

| Value | Name                                                 | Meaning                                                                                                                                                      |  |  |

|-------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x77  | Command                                              | After this flag, the system starts sending a command block to the device.  The first bit of the block can follow immediately after the last bit of the flag. |  |  |

| 0x88  | Transmit                                             | This command tells the device to wait for a bus turnaround time and then start transmitting its response to the previously transmitted command block.        |  |  |

| 0xBB  | Idle                                                 | Upon receipt of an idle flag, the device goes into the idle mode and remains there until the next wake token is received.                                    |  |  |

| 0xCC  | Sleep                                                | Upon receipt of a sleep flag, the device enters the low-power sleep mode until the next Wake token is received.                                              |  |  |

|       | All other values are reserved and should not be used |                                                                                                                                                              |  |  |

#### 5.2.1.1 Transmit Flag

The transmit flag is used to turn the bus around so that the ATSHA204 can send data back to the system. The bytes that the device returns to the system depend on the current state of the device, and may include either status, error code, or command results.

When the device is busy executing a command, it ignores the SDA pin and any flags sent by the system. See Table 8-4 for execution delays in the device for each command type. The system must observe these delays after sending a command to the device.

#### 5.2.1.2 Idle Flag

The idle flag is used to transition the ATSHA204 to the idle state, which causes the input/output buffer to be flushed. It does *not* invalidate the contents of the TempKey and RNG seed registers. This flag can be sent to the device at any time when it will accept a flag. When the device is in the idle state, the watchdog timer is disabled.