### **MAX20340**

## **General Description**

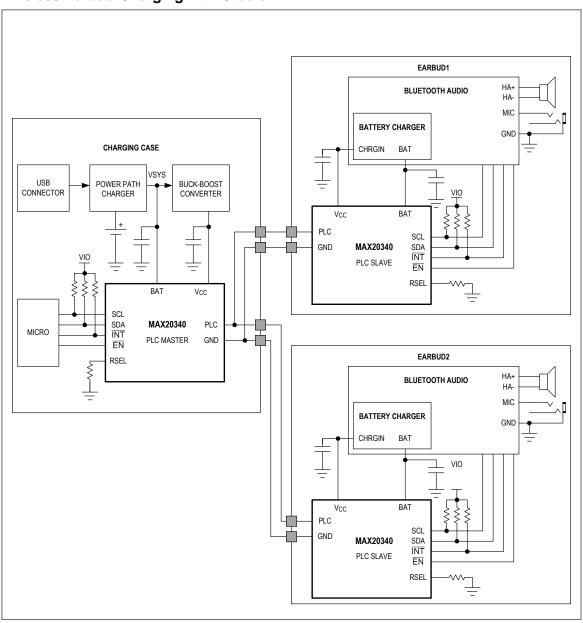

The MAX20340 is a universal bidirectional DC powerline communication (PLC) management IC with a 166.7kbps maximum bit rate. The device is capable of a maximum of 1.2A charge current.

The MAX20340 features a slave detection circuit that flags an interrupt to the system when the PLC master detects

the presence of a PLC slave on the powerline. This function allows the system to remain in a low-power state until a slave device is connected.

Many of the features of the MAX20340, such as master/slave mode, I<sup>2</sup>C address, dual/single PLC slave mode, and PLC slave address, are pin configurable.

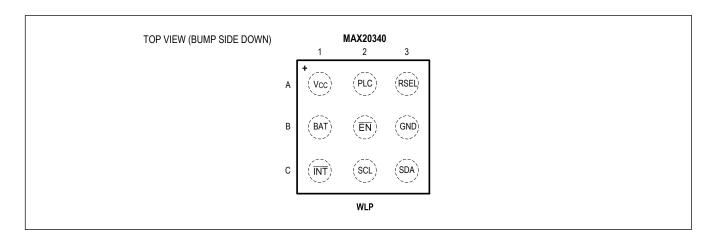

The device is available in a 9-bump, 0.4mm pitch, 1.358mm x 1.358mm wafer-level package (WLP).

## **Applications**

Truly Wireless Earbuds

Tethered Wireless Headphones

Hearing Aids

Wearables

Game Controllers

Handheld Radios

Point of Sales Devices

## **Bidirectional DC Powerline Communication Management IC**

### **Benefits and Features**

- Compact, Simple Solution for PLC

- · Up to 166.7kbps Bit Rate

- 5.7kbps Data Throughput in Automatic Mode

- 1.2A Charge Current

- Automatic Detection of PLC Slave Presence

- Flexible Configuration

- · Single Resistor to Program

- PLC Master or Slave

- Dual or Single Slave Mode (Master Only)

- PLC Slave Address (Slave Only)

- I<sup>2</sup>C Address

- Small Solution Size

- Space-Saving 0.4mm Pitch, 9-Bump, 1.358mm x 1.358mm WLP

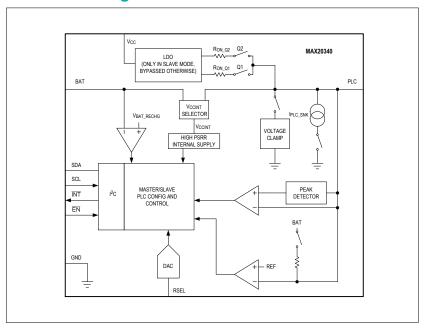

## **Functional Diagram**

## **Absolute Maximum Ratings**

| V <sub>CC</sub> , PLC, SCL, SDA  | 0.3V to +6V                             |                                     |                      |                       |                                |

|----------------------------------|-----------------------------------------|-------------------------------------|----------------------|-----------------------|--------------------------------|

| Continuous Current V             | 1.2A to +1.2A                           |                                     |                      |                       |                                |

| Continuous                       | Current                                 | into                                | Any                  | Other                 |                                |

| Continuous Power Di              | ssipation (Multilayer Board             | d) (T <sub>A</sub> = 70°C, derate 1 | 11.91mW/°C above +70 | )°C)                  | 952.8mW                        |

| Operating Temperatu              | re Range                                |                                     |                      |                       | 40°C to +85°C                  |

| Junction Temperature             | 9                                       |                                     |                      |                       | +150°C                         |

| Storage Temperature              | Range                                   |                                     |                      |                       | 40°C to +150°C                 |

| Soldering Temperatu              | re (reflow)                             |                                     |                      |                       | +260°C                         |

| Others to be a second the second | ada al constant (CA basa loda Massinaco | Datimus!!                           |                      | in There are strong . | estimana ambi amal formatiamal |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### **9 WLP**

| Package Code                                           | W91R1+1                        |

|--------------------------------------------------------|--------------------------------|

| Outline Number                                         | 21-100389                      |

| Land Pattern Number                                    | Refer to Application Note 1891 |

| Thermal Resistance, Four Layer Board:                  |                                |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 83.98°C/W                      |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                            |

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layerboard. For detailed information on package thermal considerations see www.maxim-ic.com/thermal-tutorial.

## **Electrical Characteristics**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \ V_{CC} = +3.4 \text{V to } +5.5 \text{V}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C. \ (\text{Note 1})$

| PARAMETER                                      | SYMBOL                      | CONDITIONS                                                                                                                                                                       | MIN                   | TYP      | MAX | UNITS    |

|------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|-----|----------|

| VCCINT (VCCINT_MASTER                          | R = BAT, V <sub>CCINT</sub> | SLAVE = PLC if V <sub>PLC</sub> > V <sub>PLC_DET</sub> , otherwi                                                                                                                 | ise V <sub>CCIN</sub> | T = BAT) |     | <u> </u> |

| V <sub>CCINT</sub> POR Threshold               | V <sub>CCINT_POR</sub>      | Rising and falling                                                                                                                                                               | 1.7                   | 2.15     | 2.4 | V        |

| V <sub>CCINT</sub> POR Threshold<br>Hysteresis | V <sub>CCINT_PORH</sub>     |                                                                                                                                                                                  |                       | 166      |     | mV       |

| V <sub>CC</sub>                                | 1                           |                                                                                                                                                                                  |                       |          |     | •        |

| Input Supply Voltage<br>Range                  | V <sub>CC</sub>             | Supply range to operate PLC                                                                                                                                                      | 3.4                   |          | 5.5 | V        |

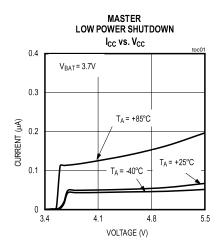

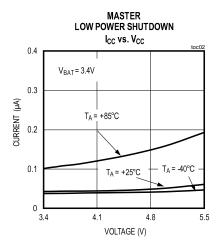

| V <sub>CC</sub> Shutdown Current               | I <sub>CC_SHDN</sub>        | V <sub>CC</sub> = +5.0V, <del>EN</del> = 1                                                                                                                                       |                       |          | 1   | μΑ       |

| V <sub>CC</sub> Supply Current                 | I <sub>CC</sub>             | $V_{CC}$ = +5.0V, $\overline{EN}$ = 0, $V_{BAT}$ = +3.6V, master in slave found charging state, PLC unconnected                                                                  |                       | 28.5     | 50  | μА       |

| BAT                                            |                             |                                                                                                                                                                                  |                       |          |     |          |

| Input Supply Voltage<br>Range                  | V <sub>BAT</sub>            | Master/slave mode                                                                                                                                                                | 2.8                   |          | 5.5 | V        |

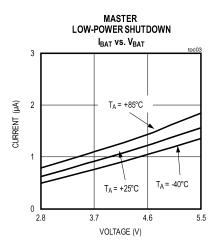

| BAT Shutdown Current                           | IBAT_SHDN                   | $V_{CC}/V_{PLC} = 0$ , $V_{BAT} = +3.6V$ , $\overline{EN} = 1$ , Device in Low Power Shutdown                                                                                    |                       | 0.8      | 2.1 | μA       |

|                                                |                             | $V_{BAT}$ = +3.6V, $\overline{EN}$ = 0, PLC unconnected, master in slave detection state                                                                                         |                       | 4        | 9   |          |

|                                                |                             | PLC = 0, $V_{BAT}$ = +3.6V, $\overline{EN}$ = 0, slave in master detection state                                                                                                 |                       | 0.7      | 2   |          |

| BAT Supply Current                             | I <sub>BAT</sub>            | $V_{CC}$ = +5.0V, $V_{BAT}$ = +3.6V, $\overline{EN}$ = 0, master only, slave found charging state, PLC unconnected                                                               |                       | 75       | 115 | μA       |

|                                                |                             | $V_{PLC}$ = +5.0V, $\overline{EN}$ = 0, slave in master found PLC communication enabled state, LDO enabled                                                                       |                       | 1        | 2   |          |

|                                                |                             | Slave in idle state, V <sub>PLC</sub> = +3.6V, V <sub>BAT</sub> = +4.2V, V <sub>CC</sub> unconnected                                                                             |                       | 0.6      | 1.4 |          |

| Recharge Voltage<br>Threshold Range            | V <sub>BAT_RECHG</sub>      | Programmable in 200mV steps through bits BAT_RECHG[2:0] of register 0x03; if VBAT < VBAT_RECHG, a device in slave idle state automatically transitions to master detection state |                       | 3 to 4.4 |     | V        |

| Recharge Threshold<br>Voltage Accuracy         | V <sub>RECHG_ACC</sub>      |                                                                                                                                                                                  | -8                    |          | +8  | %        |

| PLC                                            | <u>I</u>                    |                                                                                                                                                                                  |                       |          |     | ı        |

| Input Supply Voltage<br>Range                  | V <sub>PLC</sub>            | Supply range to operate PLC                                                                                                                                                      | 3.4                   |          | 5.5 | V        |

| PLC Shutdown Current                           | I <sub>PLC_SHDN</sub>       | Slave only, $\overline{\text{EN}}$ = 1, $V_{\text{PLC}}$ = +3.6V, $V_{\text{BAT}}$ = +3.4V, $V_{\text{CC}}$ unconnected                                                          |                       | 3        | 6.5 | μA       |

| PLC Supply Current                             | I <sub>PLC</sub>            | $V_{PLC}$ = +5.0V, $\overline{EN}$ = 0, slave only, LDO enabled, master found communication                                                                                      |                       | 160      | 270 | μA       |

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \ V_{CC} = +3.4 \text{V to } +5.5 \text{V}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ . (Note 1)

| PARAMETER                                     | SYMBOL                 | CONDITIONS                                                                                                                                                                                                                            | MIN    | TYP   | MAX    | UNITS |  |

|-----------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--|

|                                               |                        | enabled state, PLC communication not ongoing                                                                                                                                                                                          |        | l     | •      |       |  |

| PLC Supply Current                            | I <sub>PLC</sub>       | Slave in slave idle state, $\overline{EN}$ = 0, $V_{PLC}$ = +3.6V, $V_{BAT}$ = +4.2V, $V_{CC}$ unconnected                                                                                                                            |        | 3.4 7 |        |       |  |

| PLC Detection<br>Threshold                    | V <sub>PLC_DET</sub>   | Slave only, V <sub>PLC</sub> rising                                                                                                                                                                                                   |        | 2.5   |        | V     |  |

| Short-Circuit Detection<br>Threshold          | V <sub>PLC_SHT</sub>   | Master only, V <sub>PLC</sub> falling                                                                                                                                                                                                 |        | 2.4   |        | V     |  |

| Short Detection<br>Blanking Time              | tSHT_BLK               |                                                                                                                                                                                                                                       |        | 2.5   |        | ms    |  |

| Vcc - PLC                                     |                        |                                                                                                                                                                                                                                       |        |       |        |       |  |

|                                               |                        | COM_THRS [1:0] = 00                                                                                                                                                                                                                   | 38     | 50    | 62     |       |  |

| PLC Logic Threshold                           | Vacuation              | COM_THRS [1:0] = 01                                                                                                                                                                                                                   | 53     | 65    | 77     | m∨    |  |

| ( V <sub>PLC_PEAK</sub> – V <sub>PLC</sub>  ) | V <sub>COM_DET</sub>   | COM_THRS [1:0] = 10                                                                                                                                                                                                                   | 68     | 80    | 92     | IIIV  |  |

|                                               |                        | COM_THRS [1:0] = 11                                                                                                                                                                                                                   | 88     | 100   | 112    |       |  |

| Q1, Q2 SWITCH                                 |                        |                                                                                                                                                                                                                                       |        |       |        | •     |  |

| Q1, Q2 R <sub>ON</sub>                        | R <sub>ON_Q1Q2</sub>   | V <sub>CC</sub> = 5V                                                                                                                                                                                                                  |        | 72    | 110    | mΩ    |  |

| Q2 R <sub>ON</sub>                            | R <sub>ON_Q2</sub>     | 450mA                                                                                                                                                                                                                                 | 0.46   | 0.53  | 0.65   | Ω     |  |

| Q1 LDO                                        | •                      |                                                                                                                                                                                                                                       |        |       |        | I     |  |

| LDO Output Voltage                            | V <sub>LDO</sub>       | Slave Only, $V_{PLC} = 5V$ , $MAX[V_{BAT} + DV$ , $V_{MIN}]$ , $(DV = 100 \text{mV} \dots 400 \text{mV}$ , $50 \text{mV}$ step; $V_{MIN} = 2.8 V \dots 3.5 V$ , $100 \text{mV}$ step), $V_{BAT} = 3.4 V$ , $I_{LOAD} = 200 \text{mA}$ | -2%    |       | +2%    | V     |  |

| LDO PSRR                                      | PSRR <sub>LDO</sub>    | Ripple induced by a PLC square wave current, minimum LDO drop = 200mV, LDO load current = 200mA, ripple frequency 1/TU min, rising and falling edge at 200ns                                                                          |        | -20   |        | dB    |  |

| LDO Load Regulation                           | LOADR <sub>LDO</sub>   | Load from 0mA to 200mA                                                                                                                                                                                                                |        | 100   |        | μV    |  |

| LDO Input Line<br>Regulation                  | LINER <sub>LDO</sub>   | V <sub>PLC</sub> from 3.4V to 5.5V, load = 200mA                                                                                                                                                                                      |        | 620   |        | μV    |  |

| DEVICE CONFIGURATION                          | ON (R <sub>SEL</sub> ) |                                                                                                                                                                                                                                       |        |       |        | •     |  |

| RSEL Config 1<br>Threshold                    | R <sub>SEL1</sub>      |                                                                                                                                                                                                                                       |        |       | 4.581  | kΩ    |  |

| RSEL Config 2<br>Threshold                    | R <sub>SEL2</sub>      |                                                                                                                                                                                                                                       | 5.864  | 6.65  | 7.677  | kΩ    |  |

| RSEL Config 3<br>Threshold                    | R <sub>SEL3</sub>      |                                                                                                                                                                                                                                       | 9.289  | 10.2  | 11.347 | kΩ    |  |

| RSEL Config 4<br>Threshold                    | R <sub>SEL4</sub>      |                                                                                                                                                                                                                                       | 13.301 | 14.3  | 15.613 | kΩ    |  |

| RSEL Config 5<br>Threshold                    | R <sub>SEL5</sub>      | _                                                                                                                                                                                                                                     | 17.966 | 19.1  | 20.667 | kΩ    |  |

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \ V_{CC} = +3.4 \text{V to } +5.5 \text{V}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ . (Note 1)

| PARAMETER                                              | SYMBOL               | CONDITIONS                                                                           | MIN    | TYP  | MAX    | UNITS |

|--------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------|--------|------|--------|-------|

| RSEL Config 6<br>Threshold                             | R <sub>SEL6</sub>    |                                                                                      | 23.491 | 24.9 | 26.662 | kΩ    |

| RSEL Config 7<br>Threshold                             | R <sub>SEL7</sub>    |                                                                                      | 30.046 | 31.6 | 33.599 | kΩ    |

| RSEL Config 8<br>Threshold                             | R <sub>SEL8</sub>    |                                                                                      | 37.631 |      |        | kΩ    |

| POWERLINE COMMUNIC                                     | CATION               | ,                                                                                    |        |      |        |       |

| Time Unit                                              | t <sub>UNIT</sub>    | I <sup>2</sup> C programmable                                                        |        | 24   |        | μS    |

|                                                        |                      | PLC_SINK = 00                                                                        |        | 200  |        |       |

| PLC Current Sink                                       | las a asses          | PLC_SINK = 01                                                                        |        | 244  |        | m Λ   |

| PLC Current Sink                                       | I <sub>PLC_SNK</sub> | PLC_SINK = 10                                                                        |        | 288  |        | mA    |

|                                                        |                      | PLC_SINK = 11                                                                        |        | 355  |        |       |

| DYNAMIC                                                | I                    | ,                                                                                    |        |      |        |       |

| Device Identification<br>Ready Time                    | t <sub>ID</sub>      | From BAT (master) or PLC (slave) above POR threshold to RSEL_DONEi (0x07[4]) bit set |        | 3    | 3.48   | ms    |

| General Timing<br>Accuracy                             | t <sub>ACC</sub>     |                                                                                      | -16    |      | +16    | %     |

| DIGITAL SIGNALS (SDA                                   | , SCL, ĪNT, ĒN)      | ,                                                                                    |        |      |        |       |

| Input Logic-High                                       | V <sub>IH</sub>      |                                                                                      | 1.4    |      |        | V     |

| Input Logic-Low                                        | V <sub>IL</sub>      |                                                                                      |        |      | 0.4    | V     |

| Input Leakage Current                                  | I <sub>IN_LKG</sub>  | EN, SCL                                                                              | -1     |      | +1     | μΑ    |

| Output Logic-High<br>Leakage Current (Open<br>Drain)   | I <sub>OH_LKG</sub>  | V <sub>IO</sub> = 5.5V, SDA and INT                                                  |        |      | 1      | μΑ    |

| Output Logic-Low                                       | V <sub>OL</sub>      | I <sub>SINK</sub> = 20mA                                                             |        |      | 0.4    | V     |

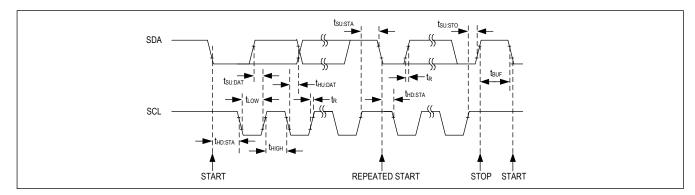

| I <sup>2</sup> C TIMING (Figure 4)                     |                      |                                                                                      |        |      |        |       |

| I <sup>2</sup> C Serial Clock<br>Frequency             | f <sub>SCL</sub>     |                                                                                      |        | 400  |        | kHz   |

| Bus Free Time Between<br>a STOP and START<br>Condition | <sup>t</sup> BUF     |                                                                                      | 1.3    |      |        | μs    |

| START Condition<br>(Repeated) Hold Time                | t <sub>HD:STA</sub>  |                                                                                      | 0.6    |      |        | μs    |

| Low Period of SCL<br>Clock                             | t <sub>LOW</sub>     |                                                                                      | 1.3    |      |        | μs    |

| High Period of SCL<br>Clock                            | <sup>t</sup> HIGH    |                                                                                      | 0.6    |      |        | μs    |

| Setup Time for a<br>Repeated START<br>Condition        | t <sub>SU:STA</sub>  |                                                                                      | 0.6    |      |        | μs    |

| $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = +3.4V \text{ to } +5.5V,$ | unless otherwise noted  | Typical values are at T <sub>4</sub> = ±2 | 5°C (Note 1)    |

|-----------------------------------------------------------------------------------|-------------------------|-------------------------------------------|-----------------|

| (14 - 40 + 60 + 60 + 60 + 60 + 60 + 60 + 60 +                                     | uniess otherwise noted. | Typical values are at $I_A = \pm 2$       | .5 C. (NOIE 1)) |

| PARAMETER                                           | SYMBOL              | CONDITIONS                      | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------|---------------------|---------------------------------|-----|-----|-----|-------|

| Data Hold Time                                      | t <sub>HD:DAT</sub> |                                 | 0   |     | 0.9 | μs    |

| Data Setup Time                                     | t <sub>SU:DAT</sub> |                                 | 100 |     |     | ns    |

| Setup Time for STOP<br>Condition                    | t <sub>SU:STO</sub> |                                 | 0.6 |     |     | μs    |

| Spike Pulse Widths<br>Suppressed by Input<br>Filter | t <sub>SP</sub>     |                                 | 50  |     |     | ns    |

| ESD PROTECTION                                      |                     |                                 | •   |     |     |       |

|                                                     |                     | Human Body Model                |     | ±30 |     |       |

| PLC                                                 |                     | IEC 61000-4-2 Air-Gap           |     | ±3  |     | kV    |

|                                                     |                     | IEC 61000-4-2 Contact Discharge |     | ±10 |     |       |

| All Other Pins                                      |                     | Human Body Model                |     | ±2  |     | kV    |

| THERMAL PROTECTION                                  | N                   |                                 | •   |     |     |       |

| Thermal Shutdown                                    | T <sub>SHDN</sub>   | Low to high                     |     | 130 |     | °C    |

| Thermal Hysteresis                                  | T <sub>HYS</sub>    | High to low                     |     | 20  |     | °C    |

**Note 1:** All devices are production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

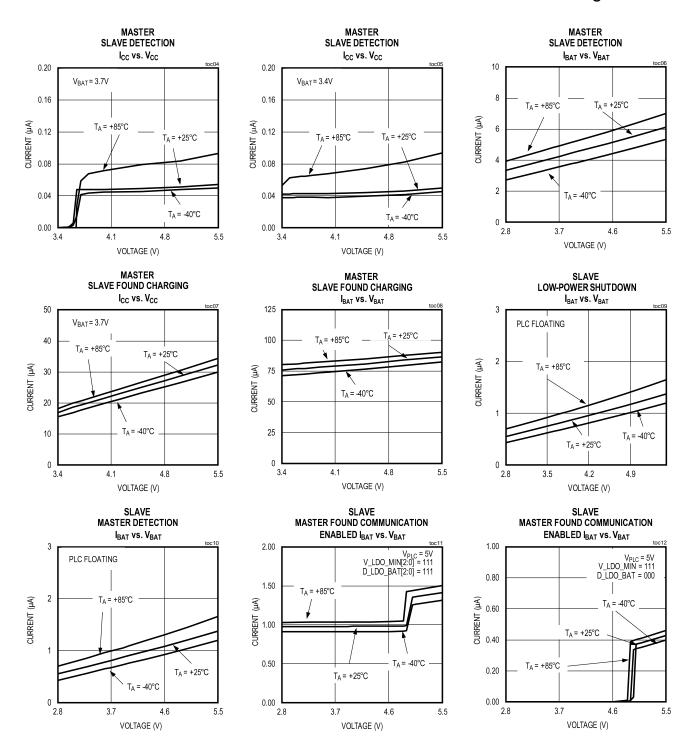

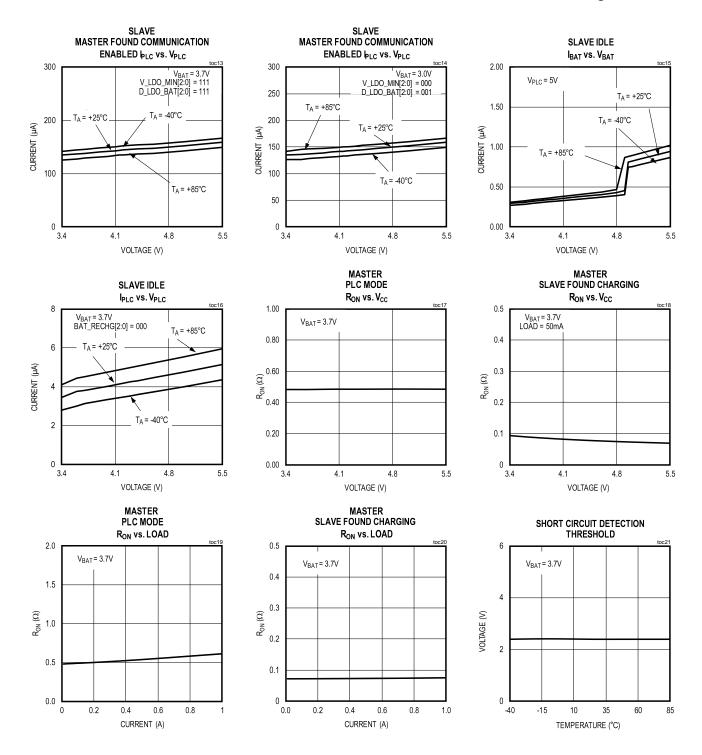

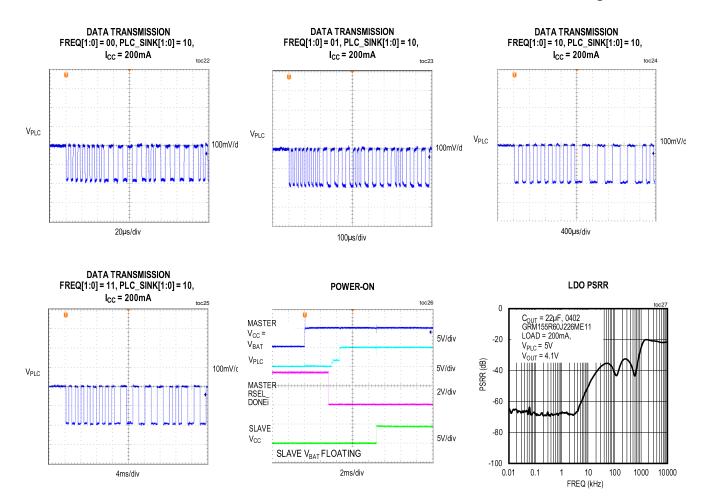

## **Typical Operating Characteristics**

## **Pin Configuration**

## **Pin Descriptions**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                          |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | Vcc  | Supply Voltage Input (Master). LDO output, bypass V <sub>CC</sub> to ground with a 10μF capacitor (Slave).                                                                                                                                                        |

| A2  | PLC  | PLC Master Output or PLC Slave Input                                                                                                                                                                                                                              |

| А3  | RSEL | Resistor Programming Input. Connect a resistor of desired value based on Table 1 to configure I <sup>2</sup> C address, master/slave mode, PLC mode (master only) and PLC slave address (slave only).                                                             |

| B1  | BAT  | Battery Connection. Connect to system battery and bypass with a 1µF capacitor to GND.                                                                                                                                                                             |

| B2  | ĒN   | Active-Low Enable Input. Drive $\overline{\text{EN}}$ pin high to place the MAX20340 in a low-power shutdown mode. Note that the EN bit of register 0x01[0] can still be used to exit the low-power shutdown mode even if the $\overline{\text{EN}}$ pin is high. |

| В3  | GND  | Ground                                                                                                                                                                                                                                                            |

| C1  | ĪNT  | Active-Low Open-Drain Interrupt Output. Connect INT to IO supply through a pullup resistor.                                                                                                                                                                       |

| C2  | SCL  | I <sup>2</sup> C Clock Input                                                                                                                                                                                                                                      |

| C3  | SDA  | I <sup>2</sup> C Data Input/Output                                                                                                                                                                                                                                |

## **Detailed Description**

The MAX20340 is a universal bidirectional DC powerline (PLC) communication management IC with a 166.7kbps maximum bit rate. The device is capable of a maximum of 1.2A charge current.

The MAX20340 features a slave detection circuit that flags an interrupt to the system when the PLC master detects the presence of a PLC slave on the power line. This function allows the system to remain in a low power state until a slave device is connected. Many of the features of the MAX20340, such as master/slave mode, I<sup>2</sup>C address, dual/single PLC slave mode, and PLC slave address, are pin configurable.

#### **Device Configuration**

After power-on reset (POR), the master/slave mode, PLC slave address (slave only), PLC slave address mode (master only) and I<sup>2</sup>C address are configured based on the value of the RSEL resistor. The configuration status can be queried by reading I2C\_ADD and PS\_ADD bits of the register 0x05.

**Table 1. RSEL Configuration**

| RESISTOR VALUE (kΩ) | DEVICE MODE | PLC SLAVE<br>ADDRESSING MODE | PLC SLAVE<br>ADDRESS (PS_ADD) | I <sup>2</sup> C ADDRESS |

|---------------------|-------------|------------------------------|-------------------------------|--------------------------|

| < 4.581             | Master      | Single                       | Х                             | 0010101                  |

| 6.65                | Master      | Single                       | Х                             | 1101010                  |

| 10.2                | Master      | Dual                         | Х                             | 0010101                  |

| 14.3                | Master      | Dual                         | Х                             | 1101010                  |

| 19.1                | Slave       | X                            | 0                             | 0010101                  |

| 24.9                | Slave       | X                            | 0                             | 1101010                  |

| 31.6                | Slave       | X                            | 1                             | 0010101                  |

| > 37.631            | Slave       | X                            | 1                             | 1101010                  |

#### **Device Initialization**

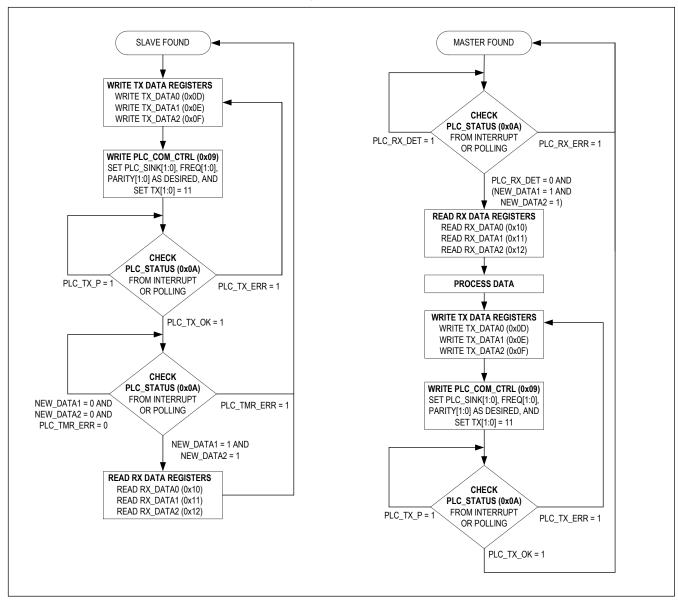

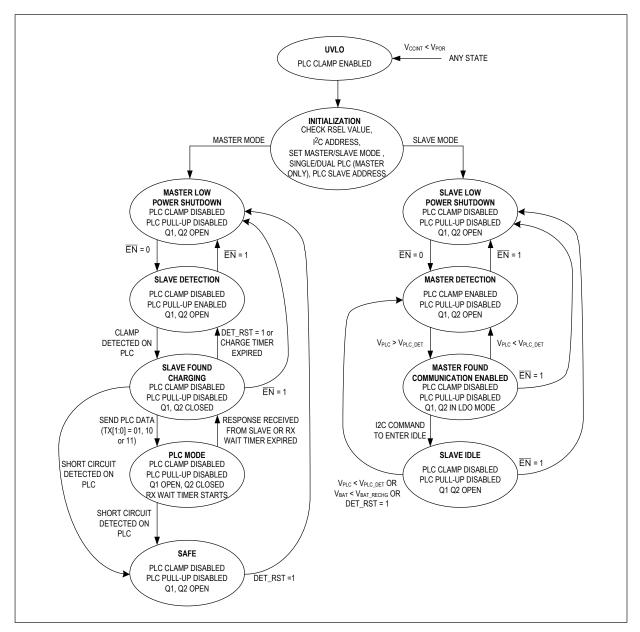

After POR, the device starts by checking the resistor present on the RSEL pin. It is recommended to have the OTP bit RSEL\_DONEm (0x08[4]) default high so that an interrupt occurs at the end of this RSEL identification phase. As an alternative to detecting the interrupt, the user can also choose to wait 3ms or more after POR to give enough time for RSEL to be properly identified. The I<sup>2</sup>C interface cannot be used until RSEL identification is complete because RSEL defines also the I<sup>2</sup>C slave address. With RSEL identified, the PLC master/slave mode, the I<sup>2</sup>C slave address, the number of PLC slaves (master mode), and the PLC slave address (slave mode) are automatically configured. The configuration result can be determined through bit PS\_ADD (0x05[0]). The user can also read bits FSM\_STAT[2:0] (0x05[4:2]) to determine whether the MAX20340 is configured as a master or a slave. If the MAX20340 is configured as a PLC master, see the <u>Master Mode Operation</u> section for more details. Otherwise, see the <u>Slave Mode Operation</u> section for PLC slave operation details. Figure 1 shows the flow chart for transmitting 3 bytes from the PLC master and receiving the response from the PLC slave. It assumes that all relevant interrupts have been unmasked.

Figure 1. Flow Chart for Transmitting 3 Bytes

### **Master Mode Operation**

After the RSEL and master mode identifications, the MAX20340 stays in the master low-power shutdown mode as long as  $\overline{\text{EN}}$  input is high (assuming EN bit of register 0x01[0] is left at 0). When  $\overline{\text{EN}}$  is set low or 0x01[0] = 1, the device transitions to the slave detection state. The user can unmask the FSM\_STATi interrupt (0x08[0]) to be notified of any change of master FSM state through the  $\overline{\text{INT}}$  pin. When a slave is detected, the state machine transitions to the slave found state. In this state, both the Q1 and Q2 switches are on to provide a low-resistance charging path between VCC and PLC pins with a 1.2A maximum charge current on the PLC line. In the slave found state, PLC communication can be initiated by the PLC master using the following procedure:

- Set PLC\_STATm bit of the DEV\_STATUS\_MASK (0x08) register to 1 to unmask the PLC\_STAT interrupts. Then unmask the PLC interrupts in the PLC\_IRQ register (0x0B) and the PLC\_MASK (0x0C) register.

- Load the bytes to be transmitted into TX\_DATAx registers (0x0D, 0x0E, and 0x0F).

- Select the desired slave response time through the TWAIT\_TMR (0x02[1:0]) bit or leave it at the default setting.

- Choose the desired PLC speed through the FREQ[1:0] (0x09[5:4]) bit, the parity through the PARITY[1:0] (0x09[3:2]) bit, and the PLC sink current through the PLC\_SINK[1:0] (0x09[7:6]) bit. Write 01 into TX[1:0] (0x09[1:0]) to send one byte, 10 to send two bytes, or 11 to send three bytes. The checksum is automatically calculated by the MAX20340 and appended after the actual data bytes.

- The master state machine transitions automatically to PLC mode and starts sending data.

- If the transmission is completed without errors, PLC\_TX\_OKi (0x0B[5]) goes high. Otherwise, PLC\_TX\_ERRi (0x0B[6]) goes high instead.

- If the PLC slave responds within the time specified by the Rx wait timer bits 0x02[1:0], the received data are available in the RX\_DATAx registers (0x10, 0x11, and 0x12). The response includes one, two, or three bytes plus the checksum. If the response is received without errors, NEW\_DATA2i (0x0B[1]) or NEW\_DATA1i (0x0B[2]) bits (or both at the same time) are high. In case of parity, checksum or any other error, PLC\_RX\_ERRi (0x0B[3]) goes high and the new data is not be updated in RX\_DATAx.

The master state machine switches automatically between PLC mode and slave found states based on the PLC communication requirements.

#### **Slave Mode Operation**

After RSEL and slave mode identification, the MAX20340 stays in the slave low-power shutdown mode as long as  $\overline{\text{EN}}$  input is high (assuming EN bit of register 0x01[0] is left at 0). When  $\overline{\text{EN}}$  is set low or 0x01[0] = 1, the device transitions to master detection state. The user can unmask the FSM\_STATi interrupt using FSM\_STATm (0x08[0]) to notify through the  $\overline{\text{INT}}$  pin when any change of state occurs. When a master is detected, the state machine switches to master found state. In this state, PLC communication is enabled. The detected PLC master is always the one that initiates the communication by sending one, two or three data bytes. When the PLC slave detects the beginning of a valid PLC communication, PLC\_RX\_DETi (0x0B[0]) becomes high. If the packet is received without errors, NEW\_DATA2i (0x0B[1]) or NEW\_DATA1i (0x0B[2]) bits (or both at the same time) becomes high and the received data are available in the RX\_DATAx registers (0x10, 0x11, and 0x12). The PLC slave can be switched from master found state to slave idle state by setting SLAVE\_TO\_IDLE (0x04[3]) to 1.

In the master found state, use the following procedure to control the PLC slave for PLC communication:

- Set PLC\_STATm bit of the DEV\_STATUS\_MASK (0x08) register to 1 to unmask PLC\_STAT interrupts.

Then unmask the PLC interrupts in the PLC\_IRQ register (0x0B) through the PLC\_MASK (0x0C) register.

- Configure the slave to match the PLC speed (FREQ[1:0]) and parity (PARITY[1:0]) of the master through the PLC\_COM\_CTRL register (0x09).

- When ongoing PLC communication is detected, the PLC slave indicates that by setting PLC\_RX\_DETi (0x0B[0]) to high. After that, wait for the assertion of interrupts NEW\_DATA2i (0x0B[1]) or NEW\_DATA1i (0x0B[2]) indicating that the received data is available in the RX\_DATAx registers. In case of parity,

checksum or any other error, PLC\_RX\_ERRi (0x0B[3]) is high and the new data is not updated in the RX\_DATAx registers.

To respond to the PLC master after processing the received data, load the bytes to be transmitted into the slave's TX\_DATAx registers (0x0D, 0x0E, and 0x0F).

Write 01 into TX[1:0] bits (0x09[1:0]) to send just one byte, 10 to send two bytes, or 11 to send three bytes. The checksum is automatically calculated by the MAX20340 and appended after the actual data bytes.

### **Dual Slave Configuration**

When an MAX20340 PLC master interfaces with two MAX20340 PLC slaves in the dual slave configuration, both PLC slaves should be configured to have a different PLC slave address using different RSEL values according to Table 1. The configured PLC slave address can be determined by reading bit PS\_ADD (0x05[0]). When the PLC master intends to send a packet to one of the PLC slaves, the PLC slave address of the intended recipient should be embedded in the data bytes. The user has the flexibility to assign the PLC slave address to any bit of the data bytes. Since both PLC slaves receive the same data, each slave's application processor is expected to extract the PLC slave address from the user-defined bit location in the PLC frame and compare it with the PLC slave address indicated by PS\_ADD bit to determine which slave is the intended recipient. The intended slave then processes the data accordingly while the other slave simply discards the data.

### **LDO Operation**

When the device is in slave mode (powered from the PLC pin), the  $V_{CC}$  pin becomes the LDO output. In this mode, the output voltage on  $V_{CC}$  follows the battery voltage plus a voltage difference programmable by the D\_LDO\_BAT[2:0] bits (register 0x02[4:2]) until  $V_{CC}$  drops to a threshold programmable by V\_LDO\_MIN[2:0] bits (register 0x02[7:5]), in which case the MAX20340 keeps  $V_{CC}$  regulated at the voltage set by V\_LDO\_MIN[2:0]. In slave mode, the LDO can also be bypassed by setting D\_LDO\_BAT[2:0] to 000.

### **Charge Timer**

When the MAX20340 is configured as a PLC master. The charge timer starts when the master state machine switches from the slave detection state to the slave found state. It continues counting without being interrupted or reset when the state machine switches back and forth between the slave found state and the PLC mode state. The charge timer is reset and stopped in the slave detection state and the master low-power shutdown state. The charge timer setting can be changed by CHG\_TMR\_SET[1:0] bits (0x03[5:4]). The charge timer status is reflected by CHG\_TMRS[1:0] bits (0x05[7:6]).

Figure 2. Master and Slave Mode Operation State Diagram

### **Thermal Shutdown**

When the MAX20340 enters thermal shutdown, the Q1/Q2 switches are open and the THM\_SHDNi interrupt bit (0x07[5]) becomes high while the master/slave state machines are not affected.

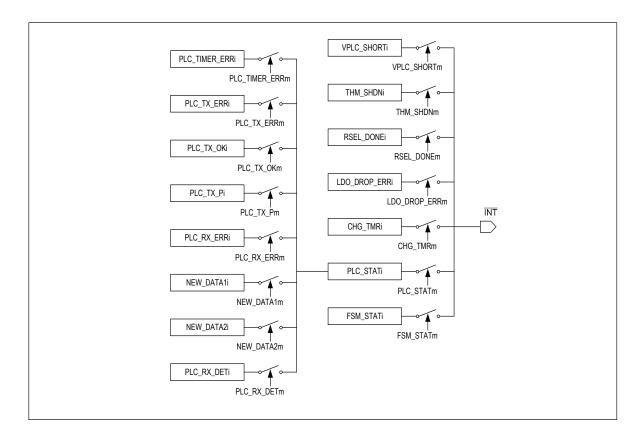

### **INT Interrupt Output**

The MAX20340 interrupts can be unmasked to indicate to the application processor (AP) that the status of the MAX20340 has changed. The INT pin asserts low whenever one or more unmasked interrupts are toggled. The device has two read-only interrupt registers: DEV\_STATUS\_IRQ and PLC\_IRQ. The DEV\_STATUS\_IRQ register indicates that the top-level block has an interrupt generated. PLC\_IRQ is an additional interrupt register dedicated to the PLC block for indicating any change of the PLC communication status. The PLC\_STATI bit in the DEV\_STATUS\_IRQ register goes high if any bit of the register PLC\_IRQ is asserted.

INT goes high (cleared) after the last interrupt register that contains an active interrupt is read. All interrupts can be masked to prevent INT from being asserted through the DEV\_STATUS\_MASK and PLC\_MASK registers. The DEV\_STATUS1, DEV\_STATUS2, and PLC\_STATUS registers can still provide the actual interrupt status of the masked interrupts, but INT is not asserted. The interrupt structure is depicted in *Figure 3*.

Figure 3. Interrupt Structure

#### I<sup>2</sup>C Interface

The device contains an I<sup>2</sup>C-compatible interface for data communication with a host controller (SCL and SDA). The interface supports a clock frequency of up to 400kHz. SCL and SDA require pullup resistors that are connected to a positive supply.

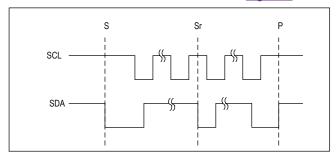

Figure 4. I<sup>2</sup>C Interface Timing

### START, STOP, and REPEATED START Conditions

When writing to the device using I<sup>2</sup>C, the master sends a START condition (S) followed by the device I<sup>2</sup>C address. After the address, the master sends the register address of the register that is to be programmed. The master then ends communication by issuing a STOP condition (P) to relinquish control of the bus, or a REPEATED START condition (Sr) to communicate to another I<sup>2</sup>C slave. See *Figure 5*.

Figure 5. I<sup>2</sup>C START, STOP, and REPEATED START Conditions

### **Slave Address**

Set the  $R/\overline{W}$  bit high to configure the device to read mode. Set the  $R/\overline{W}$  bit low to configure the device to write mode. The address is the first byte of information sent to the device after the START condition.

#### Bit Transfer

One data bit is transferred on the rising edge of each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals. See the START, STOP, and REPEATED START Conditions. Both SDA and SCL remain high when the bus is not active.

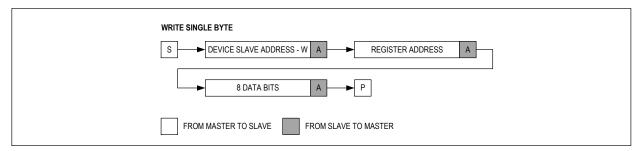

### Single-Byte Write

In this operation, the master sends an address and two data bytes to the slave device (Figure 6). The following procedure describes the single byte write operation:

- 1) The master sends a START condition.

- 2) The master sends the 7-bit slave address plus a write bit (low).

- 3) The addressed slave asserts an ACK on the data line.

- 4) The master sends the 8-bit register address.

- 5) The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6) The master sends 8 data bits.

- 7) The slave asserts an ACK on the data line.

- 8) The master generates a STOP condition.

Figure 6. Write Byte Sequence

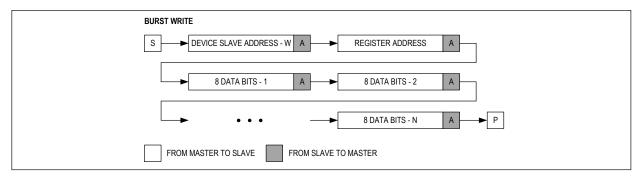

#### **Burst Write**

In this operation, the master sends an address and multiple data bytes to the slave device (*Figure 7*). The slave device automatically increments the register address after each data byte is sent. The following procedure describes the burst write operation:

- 1) The master sends a START condition.

- 2) The master sends the 7-bit slave address plus a write bit (low).

- 3) The addressed slave asserts an ACK on the data line.

- 4) The master sends the 8-bit register address.

- 5) The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6) The master sends eight data bits.

- 7) The slave asserts an ACK on the data line.

- 8) Repeat steps 6 and 7 N 1 times.

- 9) The master generates a STOP condition.

Figure 7. Burst Write Sequence

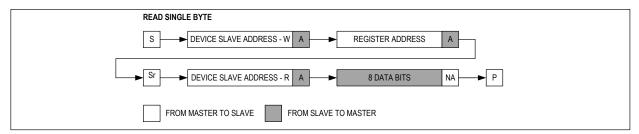

### Single-Byte Read

In this operation, the master sends an address plus two data bytes and receives one data byte from the slave device (*Figure 8*). The following procedure describes the single-byte read operation:

The master sends a START condition.

- 1) The master sends the 7-bit slave address plus a write bit (low).

- 2) The addressed slave asserts an ACK on the data line.

- 3) The master sends the 8-bit register address.

- 4) The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 5) The master sends a REPEATED START condition.

- 6) The master sends the 7-bit slave address plus a read bit (high).

- 7) The addressed slave asserts an ACK on the data line.

- 8) The slave sends eight data bits.

- 9) The master asserts a NACK on the data line.

- 10) The master generates a STOP condition.

Figure 8. Read Byte Sequence

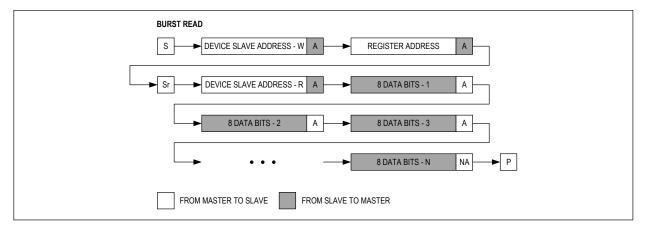

#### **Burst Read**

In this operation, the master sends an address plus two data bytes and receives multiple data bytes from the slave device (*Figure 9*). The following procedure describes the burst-byte read operation:

- 1) The master sends a START condition.

- 2) The master sends the 7-bit slave address plus a write bit (low).

- 3) The addressed slave asserts an ACK on the data line.

- 4) The master sends the 8-bit register address.

- 5) The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6) The master sends a REPEATED START condition.

- 7) The master sends the 7-bit slave address plus a read bit (high).

- 8) The slave asserts an ACK on the data line.

- 9) The slave sends eight data bits.

- 10) The master asserts an ACK on the data line.

- 11) Repeat steps 9 and 10 N 2 times.

- 12) The slave sends the last eight data bits.

- 13) The master asserts a NACK on the data line.

- 14) The master generates a STOP condition.

Figure 9. Burst Read Sequence

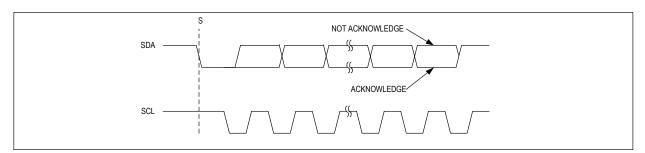

### **Acknowledge Bits**

Data transfers are acknowledged with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the master and the device generate ACK bits. To generate an ACK, pull SDA low before the rising edge of the ninth clock pulse and hold it low during the high period of the ninth clock pulse (Figure 10). To generate a NACK, leave SDA high before the rising edge of the ninth clock pulse and leave it high for the duration of the ninth clock pulse. Monitoring for NACK bits allows for detection of unsuccessful data transfers.

Figure 10. Acknowledge

## **Applications Information**

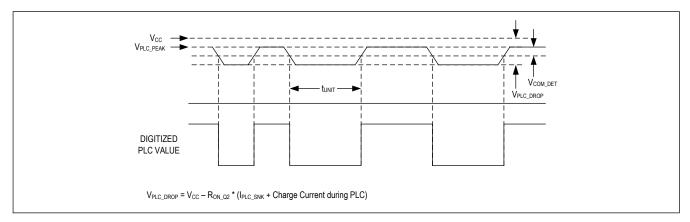

### **Powerline Communication (PLC)**

To communicate reliably over the PLC line, it is critical to keep  $V_{CC}$  of the master stable by minimizing the trace between  $V_{CC}$  and its voltage source. A voltage source with a good load transient, load regulation, and output ripple performance is recommended.

In addition, the capacitance present on the PLC can distort the PLC transmission waveform and therefore should be minimized. This is an important consideration when the LDO of the slave is in the dropout state (LDO\_DROP = 1) or when the LDO is bypassed. In both cases, the output capacitance on the LDO output ( $V_{CC}$  of the PLC slave) is effectively affecting the PLC line and should therefore be minimized as well. Figure 11 illustrates the voltage waveform on the PLC line during a PLC transmission.

The time unit (t<sub>UNIT</sub>) determines the PLC transmission speed. A time unit longer than 24µs can be selected in case the slave device, such as a battery charger in a wireless earbud, has poor PSRR performance.

Figure 11. Powerline Communication Signal Waveform

### **High-ESD Protection**

Electrostatic discharge (ESD)-protection structures are incorporated on all pins to protect against electrostatic discharges up to ±2kV Human Body Model (HBM) encountered during handling and assembly. PLC pin is further protected against ESD up to ±30kV (HBM), ±3kV (Air-Gap Discharge), and ±10kV (Contact Discharge) without damage. The ESD structures withstand high ESD in both normal operation and when the device is powered down. After an ESD event, the MAX20340 continues to function without latchup.

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

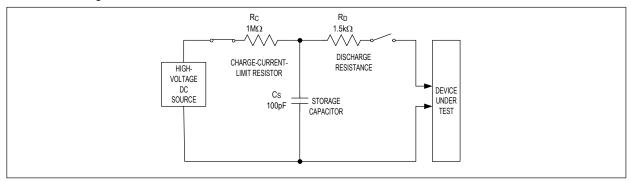

## **Human Body Model**

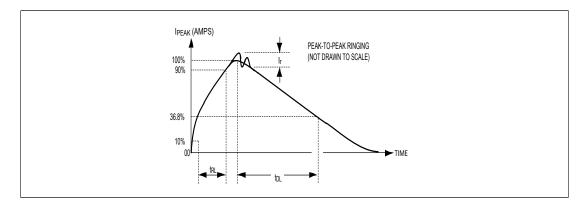

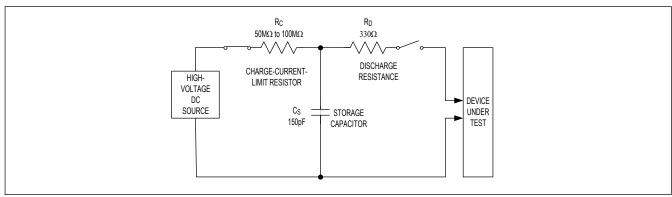

Figure 12 shows the Human Body Model. Figure 13 shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest that is then discharged into the device through a 1.5kΩ resistor.

Figure 12. Human Body ESD Test Model

Figure 13. Human Body Current Waveform

### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. It does not specifically refer to integrated circuits. The MAX20340 is specified for ±3kV Air-Gap and ±10kV Contact Discharge IEC 61000-4-2 on the PLC pin.

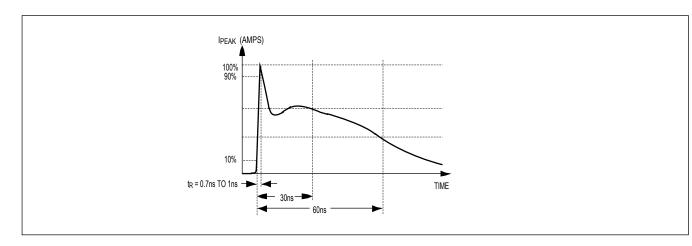

The main difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2. Because series resistance is lower in the IEC 61000-4-2 ESD test model (*Figure 14*), the ESD-withstand voltage measured to this standard is generally lower than that measured using the Human Body Model. *Figure 15* shows the current waveform for the ±6kV IEC 61000-4-2 Level 4 ESD Contact Discharge test. The Contact Discharge method connects the probe to the device before the probe is energized.

Figure 14. IEC61000-4-2 ESD Test Model

Figure 15. IEC61000-4-2 ESD Generator Current Waveform

## **Register Map**

## MAX20340

| ADDRESS | NAME                 | MSB               |                 |               |                    |                       |                   |               | LSB             |

|---------|----------------------|-------------------|-----------------|---------------|--------------------|-----------------------|-------------------|---------------|-----------------|

| I2C MAP |                      |                   |                 |               |                    |                       |                   |               |                 |

| 0x00    | DEVICE_ID[7:0]       |                   | CHIP_           | ID[3:0]       |                    |                       | CHIP_R            | REV[3:0]      |                 |

| 0x01    | CONTROL1[7:0]        | _                 | _               | _             | _                  | -                     | _                 | DET_RST       | EN              |

| 0x02    | CONTROL2[7:0]        | V.                | _LDO_MIN[2:     | 0]            | D.                 | _LDO_BAT[2:           | :0]               | TWAIT_        | TMR[1:0]        |

| 0x03    | CONTROL3[7:0]        | COM_TI            | HRS[1:0]        | CHG_TMF       | R_SET[1:0]         | _                     | BA                | AT_RECHG[2    | :0]             |

| 0x04    | CONTROL4[7:0]        | _                 | ١               | ١             | TXRX_RE<br>SET     | SLAVE_T<br>O_IDLE     |                   |               | TXFILT_E<br>NB  |

| 0x05    | DEV_STATUS1[7:0]     | CHG_TMR           | _STAT[1:0]      | PLC_STA<br>T  | FOM STATISM        |                       | I2C_ADD           | PS_ADD        |                 |

| 0x06    | DEV_STATUS2[7:0]     | LDO_DR<br>OP      | ENb             | _             | _                  | _                     | _                 | THM_SH<br>DN  | PLC_CMP<br>_OUT |

| 0x07    | DEV_STATUS_IRQ[7:0]  | _                 | VPLC_SH<br>ORTi | THM_SH<br>DNi | RSEL_DO<br>NEi     | LDO_DR<br>OP_ERRi     | CHG_TM<br>R_STATi | PLC_STA<br>Ti | FSM_STA<br>Ti   |

| 0x08    | DEV STATUS MASK[7:0] | _                 | VPLC_SH<br>ORTm | THM_SH<br>DNm | RSEL_DO<br>NEm     | LDO_DR<br>OP_ERR<br>m | CHG_TM<br>Rm      | PLC_STA<br>Tm | FSM_STA<br>Tm   |

| 0x09    | PLC_COM_CTRL[7:0]    | PLC_SINK[1:0] FRE |                 |               | Q[1:0] PARITY[1:0] |                       | TX[1:0]           |               |                 |

| 0x0A    | PLC_STATUS[7:0]      | PLC_TMR<br>_ERR   | PLC_TX_<br>ERR  | PLC_TX_<br>OK | PLC_TX_<br>P       | PLC_RX_<br>ERR        | NEW_DA<br>TA1     | NEW_DA<br>TA2 | PLC_RX_<br>DET  |

| ADDRESS     | NAI                 | ME        | MSB                                                                            |                 |                |               |                 |                |                | LSB             |

|-------------|---------------------|-----------|--------------------------------------------------------------------------------|-----------------|----------------|---------------|-----------------|----------------|----------------|-----------------|

| 0x0B        | PLC_IRQ[7:0]        |           | PLC_TMR<br>i                                                                   | PLC_TX_<br>ERRi | PLC_TX_<br>OKI | PLC_TX_<br>Pi | PLC_RX_<br>ERRi | NEW_DA<br>TA1i | NEW_DA<br>TA2i | PLC_RX_<br>DETi |

| 0x0C        | PLC_MASK[7:         | 0]        | PLC_TMR<br>m                                                                   | PLC_TX_<br>ERRm | PLC_TX_<br>OKm | PLC_TX_<br>Pm | PLC_RX_<br>ERRm | NEW_DA<br>TA1m | NEW_DA<br>TA2m | PLC_RX_<br>DETm |

| 0x0D        | TX_DATA0[7:0        | <u>D1</u> |                                                                                |                 |                | TXDAT         | A0[7:0]         |                |                |                 |

| 0x0E        | TX_DATA1[7:0        | 0]        |                                                                                |                 |                | TXDAT         | A1[7:0]         |                |                |                 |

| 0x0F        | TX_DATA2[7:0        | 01        |                                                                                |                 |                | TXDAT         | A2[7:0]         |                |                |                 |

| 0x10        | RX_DATA0[7:         | 0]        |                                                                                |                 |                | RXDAT         | A0[7:0]         |                |                |                 |

| 0x11        | RX_DATA1[7:         | <u>01</u> |                                                                                |                 |                | RXDAT         | A1[7:0]         |                |                |                 |

| 0x12        | RX_DATA2[7:         | <u>01</u> |                                                                                |                 |                | RXDAT         | A2[7:0]         |                |                |                 |

| Register De | tails <u>DEVICE</u> | _ID (0x0) |                                                                                |                 |                |               |                 |                |                |                 |

| BIT         | 7                   | 6         |                                                                                | 5               | 4              | 3             | 2               |                | 1              | 0               |

| Field       |                     |           | CHIP_ID[3:0]                                                                   |                 |                |               | С               | HIP_REV[3      | 0]             |                 |

| Reset       |                     |           | 0x1                                                                            |                 |                |               |                 | 0x0            |                |                 |

| Access Type | •                   |           | Read Only                                                                      |                 |                |               |                 | Read Only      |                |                 |

|             |                     | -         |                                                                                |                 |                |               |                 |                |                |                 |

| BITF        | TELD                | ВІ        | TS                                                                             |                 |                |               | DESCRIPTIO      | N              |                |                 |

| CHIP_ID     |                     | 7         | CHIP_ID[3:0] shows information about the version of the MAX20340.              |                 |                |               |                 |                |                |                 |

| CHIP_REV    |                     | 3         | :0 CHIP_REV[3:0} shows information about the revision of the MAX20340 silicon. |                 |                |               |                 | con.           |                |                 |

| CONTROL1    | I (0x1)             |           |                                                                                |                 |                |               |                 |                |                |                 |

| BIT         | 7                   | 6         |                                                                                | 5               | 4              | 3             | 2               |                | 1              | 0               |

| ·           |                     |           |                                                                                |                 |                |               |                 |                |                |                 |

| CONTROL1 (0 | CONTROL1 (0x1) |             |             |        |      |             |             |             |  |  |

|-------------|----------------|-------------|-------------|--------|------|-------------|-------------|-------------|--|--|

| BIT         | 7              | 6           | 5           | 4      | 3    | 2           | 1           | 0           |  |  |

| Field       | _              | 1           | _           | l      | _    |             | DET_RST     | EN          |  |  |

| Reset       | 0x0            | 0x0         | 0x0         | 0x0    |      | 0x0         | 0x0         | 0x1         |  |  |

| Access Type | Write, Read    | Write, Read | Write, Read | Write, | Read | Write, Read | Write, Read | Write, Read |  |  |

| BITFIELD | BITS | DESCRIPTION                | DECODE |

|----------|------|----------------------------|--------|

| _        | 7    | Reserved. Used internally. |        |

| _        | 6    | Reserved. Used internally. |        |

| _        | 5    | Reserved. Used internally. |        |

| _        | 4:3  | Reserved. Used internally. |        |

| _        | 2    | Reserved. Used internally. |        |

| BITFIELD     | BITS | DESCRIPTION                                                                                                                                                                                                                                     | DECODE                                                                                                         |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| DET_RST      | 1    | Master/Slave Detection Reset                                                                                                                                                                                                                    | Writing a 1 to this bit will reset the FSM to the master/slave detection state.                                |

| EN           | 0    | Device Enable. If the external pin $\overline{EN}$ is low, this bit is ignored. If the external pin $\overline{EN}$ is high, this bit can be used to enter or exit low-power shutdown mode by software rather than by driving $\overline{EN}$ . | 0x0: Device enters low-power shutdown mode (both master and slave). 0x1: Device exits low-power shutdown mode. |

| CONTROL 2 (C | )v2) |                                                                                                                                                                                                                                                 |                                                                                                                |

| BIT         | 7              | 6 | 5              | 4 | 3           | 2              | 1  | 0 |

|-------------|----------------|---|----------------|---|-------------|----------------|----|---|

| Field       | V_LDO_MIN[2:0] |   | D_LDO_BAT[2:0] |   |             | TWAIT_TMR[1:0] |    |   |

| Reset       | 0x0            |   | 0x6            |   |             | 0)             | x1 |   |

| Access Type | Write, Read    |   | Write, Read    |   | Write, Read |                |    |   |

| BITFIELD  | BITS | DESCRIPTION                                                                                                                                       | DECODE                                                                                               |

|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| V_LDO_MIN | 7:5  | LDO Voltage Select. In slave mode, except when D_LDO_BAT[2:0] = 000, this sets the minimum allowed LDO output voltage, overriding D_LDO_BAT[2:0]. | 0x0: 2.8V<br>0x1: 2.9V<br>0x2: 3.0V<br>0x3: 3.1V<br>0x4: 3.2V<br>0x5: 3.3V<br>0x6: 3.4V<br>0x7: 3.5V |

| D_LDO_BAT | 4:2  | Regulated LDO-BAT Difference. In slave mode, this sets the regulated difference between the voltages of LDO output and BAT.                       | 0x0: LDO Bypassed 0x1: 100mV 0x2: 150mV 0x3: 200mV 0x4: 250mV 0x5: 300mV 0x6: 350mV 0x7: 400mV       |

| TWAIT_TMR | 1:0  | PLC Master's Rx Wait Time After Transmission                                                                                                      | 0x0: 2ms<br>0x1: 10ms (default)<br>0x2: 100ms<br>0x3: 800ms                                          |

## CONTROL3 (0x3)

| BIT         | 7      | 6        | 5                | 4 | 3           | 2              | 1 | 0 |

|-------------|--------|----------|------------------|---|-------------|----------------|---|---|

| Field       | COM_TI | HRS[1:0] | CHG_TMR_SET[1:0] |   | _           | BAT_RECHG[2:0] |   |   |

| Reset       | 0)     | «О       | 0x0              |   |             | 0x1            |   |   |

| Access Type | Write, | Read     | Write, Read      |   | Write, Read | Write, Read    |   |   |

| BITFIELD        | BITS | DESCRIPTION                                                               | DECODE                                            |

|-----------------|------|---------------------------------------------------------------------------|---------------------------------------------------|

| COM_THRS        | 7:6  | Communication Detection Threshold                                         | 0x0: 50mV<br>0x1: 65mV<br>0x2: 80mV<br>0x3: 100mV |

| CHG_TMR_SE<br>T | 5:4  | Charge Timer Setting (Master Only and Master/Slave State Machine Active). |                                                   |

Maxim Integrated | 24 www.maximintegrated.com

| BITFIELD  | BITS | DESCRIPTION                                                                                                                                                                                                                                                                         | DECODE                                                        |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|           |      |                                                                                                                                                                                                                                                                                     | 0x0: Charge timer disabled 0x1: 60min 0x2: 120min 0x3: 240min |

| _         | 3    | Reserved                                                                                                                                                                                                                                                                            |                                                               |

| BAT_RECHG | 2:0  | Battery Recharge Threshold. Programmable in 200mV steps (slave mode only and master/slave state machine active). When the voltage on BAT drops below this level, the device automatically transitions from slave idle state to master detection state and applies the clamp on PLC. | 0x0: 3V<br>0x1: 3.2V<br><br>0x7: 4.4V                         |

## CONTROL4 (0x4)

| ВІТ         | 7           | 6           | 5           | 4              | 3                 | 2           | 1           | 0           |

|-------------|-------------|-------------|-------------|----------------|-------------------|-------------|-------------|-------------|

| Field       | _           | _           | _           | TXRX_RESE<br>T | SLAVE_TO_I<br>DLE | _           | _           | TXFILT_ENB  |

| Reset       | 0x0         | 0x0         | 0x0         | 0x0            | 0x0               | 0x0         | 0x0         | 0x0         |

| Access Type | Write, Read | Write, Read | Write, Read | Write, Read    | Write, Read       | Write, Read | Write, Read | Write, Read |

| BITFIELD          | BITS | DESCRIPTION                                                                                                                                                                                                           | DECODE                                                                                                                                                                                                                                                                           |

|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 7    | Reserved. Do not change the default value.                                                                                                                                                                            |                                                                                                                                                                                                                                                                                  |

|                   | 6    | Reserved. Do not change the default value.                                                                                                                                                                            |                                                                                                                                                                                                                                                                                  |

| _                 | 5    | Reserved. Do not change the default value.                                                                                                                                                                            |                                                                                                                                                                                                                                                                                  |

| TXRX_RESET        | 4    | When high, this bit clears asynchronously the PLC transmitter, receiver, and tracking state machines. The I <sup>2</sup> C map and master/slave state machines are not affected.                                      |                                                                                                                                                                                                                                                                                  |

| SLAVE_TO_ID<br>LE | 3    | When high, this bit causes the transition from the master found communication enabled state to slave idle state. It is ignored in the other states or if the MAX20340 is configured as a master. This bit autoclears. |                                                                                                                                                                                                                                                                                  |

| _                 | 2    | Reserved. Do not change the default value.                                                                                                                                                                            |                                                                                                                                                                                                                                                                                  |

| _                 | 1    | Reserved. Do not change the default value.                                                                                                                                                                            |                                                                                                                                                                                                                                                                                  |

| TXFILT_ENB        | 0    | Tx Filter Active-Low Enable.                                                                                                                                                                                          | 0x0: Filter that compares transmitted PLC data to real-<br>time received data is enabled. In case of a mismatch, a<br>counter is incremented. When this counter reaches 15,<br>the PLC_TX_ERR flag is generated and the transmission<br>is interrupted.<br>0x1: Filter disabled. |

## DEV\_STATUS1 (0x5)

| BIT   | 7       | 6          | 5        | 4             | 3 | 2       | 1      | 0 |

|-------|---------|------------|----------|---------------|---|---------|--------|---|

| Field | CHG_TMR | _STAT[1:0] | PLC_STAT | FSM_STAT[2:0] |   | I2C_ADD | PS_ADD |   |

| Reset       | 0x0       | 0x0       | 0x0       | 0x0       | 0x0       |

|-------------|-----------|-----------|-----------|-----------|-----------|

| Access Type | Read Only |

| BITFIELD         | BITS | DESCRIPTION                                                                                 | DECODE                                                                                                                                                                                                                                                                     |

|------------------|------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG_TMR_ST<br>AT | 7:6  | Charge Timer Status                                                                         | 0x0: Timer inactive 0x1: Timer running 0x2: Timer expired 0x3: Reserved                                                                                                                                                                                                    |

| PLC_STAT         | 5    | This bit is set high if one or more bits of the read-<br>only register PLC_STATUS are high. | 0x0: PLC_STATUS register has zero value. 0x1: PLC_STATUS register has nonzero value.                                                                                                                                                                                       |

| FSM_STAT         | 4:2  | FSM State Status                                                                            | 0x0: Initialization (master/slave)/safe state (master) 0x1: Slave low power shutdown 0x2: Master low power shutdown 0x3: Master detection 0x4: Slave detection 0x5: Master found communication enabled 0x6: Slave found charging 0x7: PLC mode (master)/slave idle (slave) |