# Bluetooth® 5.2 System-in-Package (SiP)

# RSL<sub>10</sub> SIP

#### Introduction

RSL10 System-In-Package (RSL10 SIP) is a complete solution that provides the easiest way to integrate the industry's lowest power Bluetooth Low Energy technology into a wireless application.

The RSL10 SIP features an on-board antenna, RSL10 radio SoC, and all necessary passive components in one package to help minimize overall system size. Already fully qualified to FCC, CE, and other regulatory standards; RSL10 SIP removes the need for additional antenna design considerations or RF certifications.

# **Key Features**

- Fully Certified:

- ♦ Bluetooth 5.2

- ODID

- Declaration ID

- FCC, CE, IC, MIC, KCC

- Industry's Lowest Power:

- Peak Rx Current = 5.6 mA (1.25 V VBAT)

- Peak Rx Current = 3.0 mA (3 V VBAT)

- Peak Tx Current (0 dBm) = 8.9 mA (1.25 V VBAT)

- Peak Tx Current (0 dBm) = 4.6 mA (3 V VBAT)

- Deep Sleep Current Consumption (1.25 V VBAT):

- ♦ Deep Sleep, IO Wake-up: 50 nA

- Deep Sleep, 8 kB RAM Retention: 300 nA

- Current Consumption (3 V VBAT):

- Deep Sleep, IO Wake-up: 25 nA

- Deep Sleep, 8 kB RAM Retention: 100 nA

- EEMBC ULPMark Core Profile (3 V): 1090

- EEMBC ULPMark Core Profile (2.1 V): 1360

- Advanced Wireless:

- Bluetooth 5.2 Certified with LE 2-Mbit PHY (High Speed), as well as Backwards Compatibility and Support for Earlier Bluetooth Low Energy Specifications

- Supports FOTA (Firmware Over–The–Air) Updates

- ◆ Rx Sensitivity (Bluetooth Low Energy Mode, 1 Mbps): -93 dB

1

- ◆ Transmitting Power: -17 to +6 dBm

- Range up to 100 Meters

#### Other Key Features

- Arm<sup>®</sup> Cortex<sup>®</sup>-M3 Processor Clocked at up to 48 MHz

- Supply Voltage Range: 1.1 3.3 V

- 384 kB of Flash Memory

- 76 kB of Program Memory

- 88 kB of Data Memory

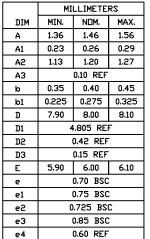

SIP51 8x6 CASE 127EY

XXXXXX = Specific Device Code A = Assembly Location

WL = Wafer Lot Y = Year WW = Work Week G or ■ = Pb-Free Package

#### ORDERING INFORMATION

| Device     | Package   | Shipping <sup>†</sup> |

|------------|-----------|-----------------------|

| NCH-RSL10- | SIP51     | 2500 /                |

| 101S51-ACG | (Pb-Free) | Tape & Reel           |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### **FEATURES**

- Arm Cortex-M3 Processor: A 32-bit core for real-time applications, specifically developed to enable high-performance low-cost platforms for a broad range of low-power applications.

- LPDSP32: A 32-bit Dual Harvard DSP core that efficiently supports intensive signal processing applications. Various codecs are available to customers through libraries that are included in RSL10's development tools.

- Radio Frequency Front-End: Based on a 2.4 GHz RF transceiver, the RFFE implements the physical layer of the Bluetooth Low Energy technology standard and other proprietary or custom protocols.

- **Protocol Baseband Hardware:** Bluetooth 5.2 certified and includes support for a 2 Mbps RF link and custom protocol options. The RSL10 baseband stack is supplemented by support structures that enable implementation of **onsemi** and customer designed custom protocols.

- Highly-Integrated SoC: The dual-core architecture is complemented by high-efficiency power management units, oscillators, flash and RAM memories, a DMA controller, along with a full complement of peripherals and interfaces.

- **Deep Sleep Mode:** RSL10 can be put into a Deep Sleep Mode when no operations are required. Various Deep Sleep Mode configurations are available, including:

- "IO wake-up" configuration. The power consumption in deep sleep mode is 50 nA (1.25 V VBAT).

- Embedded 32 kHz oscillator running with interrupts from timer or external pin. The total current drain is 90 nA (1.25 V VBAT).

- As above with 8 kB RAM data retention. The total current drain is 300 nA (1.25 V VBAT).

- The DC-DC converter can be used in buck mode or LDO mode during Sleep Mode, depending on VBAT voltage.

- Standby Mode: Can be used to reduce the average power consumption for off-duty cycle operation, ranging typically from a few ms to a few hundreds of ms. The typical chip power consumption is 30 μA in Standby Mode.

- Multi-Protocol Support: Using the flexibility provided by LPDSP32, the Arm Cortex-M3 processor, and the RF front-end; proprietary protocols and other custom protocols are supported.

- Flexible Supply Voltage: RSL10 integrates highefficiency power regulators and has a VBAT range of 1.1 to 3.3 V.

- **Highly Configurable Interfaces:** I<sup>2</sup>C, UART, two SPI interfaces, PCM interface, multiple GPIOs. It also supports a digital microphone interface (DMIC) and an output driver (OD).

- Flexible Clocking Scheme: RSL10 must be clocked from the XTAL/PLL of the radio front—end at 48 MHz when transmitting or receiving RF traffic. When RSL10 is not transmitting/receiving RF traffic, it can run off the 48 MHz XTAL, the internal RC oscillators, the 32 kHz oscillator, or an external clock. A low frequency RTC clock at 32 kHz can also be used in Deep Sleep Mode. It can be sourced from either the internal XTAL, the RC oscillator, or a digital input pad.

- Diverse Memory Architecture: 76 kB of SRAM program memory (4 kB of which is PROM containing the chip boot–up program, and is thus unavailable to the user) and 88 kB of SRAM data memory are available. A total of 384 kB of flash is available to store the Bluetooth stack and other applications.

- The Arm Cortex-M3 processor can execute from SRAM and/or flash.

- Security: AES128 encryption hardware block for custom secure algorithms and code protection with authenticated debug port access (JTAG 'lock')

- Ultra-Low Power Consumption Application Examples:

- Low Duty Cycle Advertising: IDD 1.1 μA for advertising at all three channels at 5 second intervals

WBAT 3 V, DCDC converter enabled.

- RoHS Compliant Device

#### **Notice**

All specifications for the RSL10 System-in-Package are based on the RSL10 radio SoC. The RSL10 SIP data sheet only contains key parameters. For a full list of RSL10 parameters and specifications, refer to the RSL10 data sheet.

# **Application Board Connection**

The RSL10 SIP is designed to be reflowed onto low-cost printed circuit boards. The RSL10 SIP connects to the application board via solder pads located on the bottom.

To properly operate the RSL10 SIP an external PCB connection between the RF and ANT pads is required. This connection connects the RF pin on RSL10 to the antenna

inside the SiP. If an external antenna is used instead of the antenna internal to the SiP, this external antenna needs to be connected to PIN E1.

Additionally, an external PCB connection is required for the VDDO pad to ensure that it is not left floating. For example, it can be connected to VBAT so that the logic high level for the digital I/O (DIO) pads is equal to VBAT.

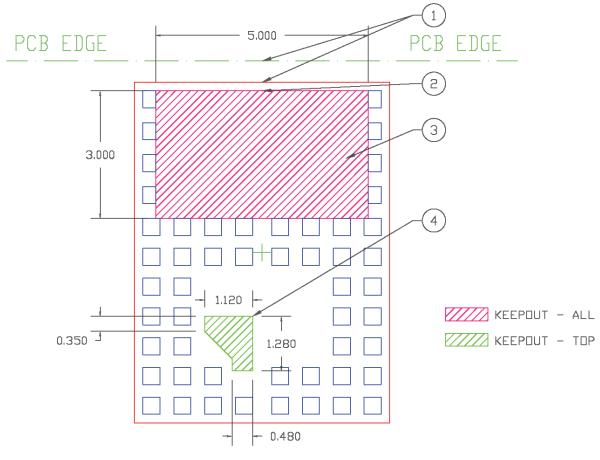

Figures 1 and 2 show proposed layout patterns for the RSL10 SIP. The specific layout pattern used in the application may have to be adjusted to meet certain needs of the PCB manufacturer or assembly house. PCB design files for the RSL10 SIP are available at www.onsemi.com.

#### Notes:

- 1. Align component edge to PCB edge if possible.

- 2. Extend keepout area to PCB edge.

- 3. Keepout area- All layers.

- 4. Keepout area- Top layer only.

- 5. Units = mm.

Figure 1. RSL10 SIP Keepout Area Requirements

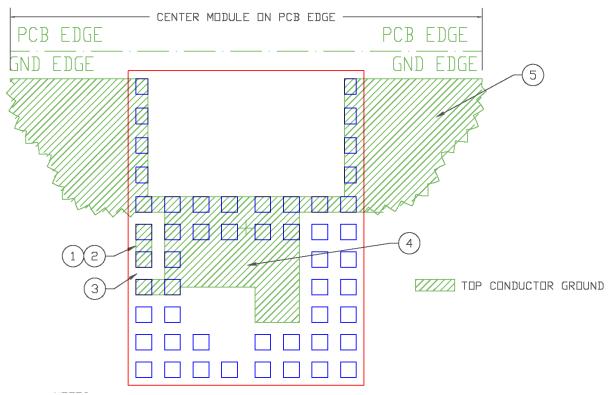

# Notes:

- 1. When incorporating internal antenna, join landing pads using 0.40 x 1.10 shape.

- 2. Establish 50  $\Omega$  impedance to underlying reference plane.

- 3. Maintain minimum 300  $\mu m$  distance from ground plane.

- 4. Area for several vias.

- 5. Refer to radiation efficiency data for applicable ground plane sizing.

- 6. Units = mm.

Figure 2. Minimum Top Layer Ground Structure

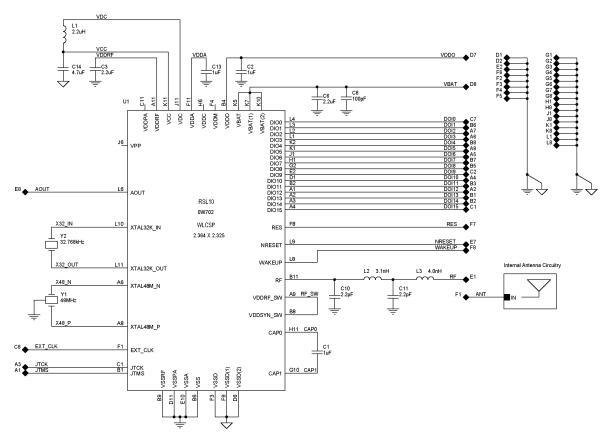

# **RSL10 SiP Schematic**

The schematic for the RSL10 SIP is shown in Figure 3.

Figure 3. RSL10 SIP Schematic

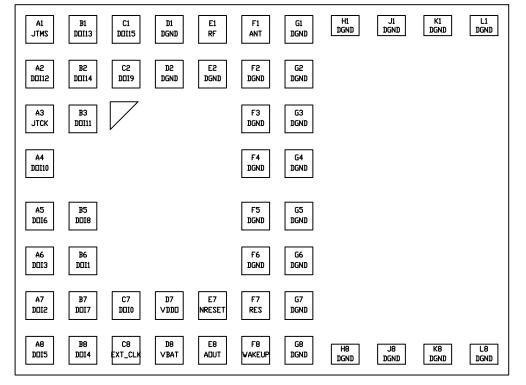

Figure 4. Pin Connection Diagram

# PAD FUNCTION DESCRIPTION

For detailed pad function information see the RSL10 data sheet.

Table 1. PAD LIST

| Pad Identifier | Pad Name | I/O | A/D | Pull | Description                                 |

|----------------|----------|-----|-----|------|---------------------------------------------|

| A1             | JTMS     | I/O | D   | U    | CM3-JTAG Test Mode State                    |

| A2             | DOI12    | I/O | D   | U/D  | Digital input output 12                     |

| А3             | JTCK     | I/O | D   | U    | CM3-JTAG Test Clock                         |

| A4             | DOI10    | I/O | D   | U/D  | Digital input output 10                     |

| A5             | DOI6     | I/O | D   | U/D  | Digital input output 6                      |

| A6             | DOI3     | I/O | A/D | U/D  | Digital input output 3 / ADC 3              |

| A7             | DOI2     | I/O | A/D | U/D  | Digital input output 2 / ADC 2              |

| A8             | DOI5     | I/O | D   | U/D  | Digital input output 5                      |

| B1             | DOI13    | I/O | D   | U/D  | Digital input output/CM3-JTAG Test Reset    |

| B2             | DOI14    | I/O | D   | U/D  | Digital input output/CM3-JTAG Test Data In  |

| В3             | DOI11    | I/O | D   | U/D  | Digital input output 11                     |

| B5             | DOI8     | I/O | D   | U/D  | Digital input output 8                      |

| B6             | DOI1     | I/O | A/D | U/D  | Digital input output 1 / ADC 1              |

| В7             | DOI7     | I/O | D   | U/D  | Digital input output 7                      |

| B8             | DOI4     | I/O | D   | U/D  | Digital input output 4                      |

| C1             | DOI15    | I/O | D   | U/D  | Digital input output/CM3-JTAG Test Data Out |

| C2             | DOI9     | I/O | D   | U/D  | Digital input output 9                      |

| C7             | DOI0     | I/O | A/D | U/D  | Digital input output 0 / ADC 0              |

| C8             | EXT_CLK  | I   | D   | U    | External clock input                        |

| D1             | DGND     | I/O | Р   |      | Ground                                      |

| D2             | DGND     | I/O | Р   |      | Ground                                      |

| D7             | VDDO     | I   | Р   |      | Digital O/I voltage supply                  |

| D8             | VBAT     | I   | Р   |      | Battery input voltage                       |

| E1             | RF       | I/O | Α   |      | RF signal input/output                      |

| E2             | DGND     | I/O | Р   |      | Ground                                      |

| E7             | NRESET   | I   | D   | U    | Reset pin                                   |

| E8             | AOUT     | 0   | Α   |      | Analog test pin                             |

| F1             | ANT      | I/O | Α   |      | Antenna                                     |

| F2             | DGND     | I/O | Р   |      | Ground                                      |

| F3             | DGND     | I/O | Р   |      | Ground                                      |

| F4             | DGND     | I/O | Р   |      | Ground                                      |

| F5             | DGND     | I/O | Р   |      | Ground                                      |

| F6             | DGND     | I/O | Р   |      | Ground                                      |

| F7             | RES      | I   | D   | D    | RESERVED                                    |

| F8             | WAKEUP   | 1   | Α   | _    | Wake-up pin for power modes                 |

| G1             | DGND     | I/O | Р   |      | Ground                                      |

| G2             | DGND     | I/O | Р   |      | Ground                                      |

| G3             | DGND     | I/O | Р   |      | Ground                                      |

| G4             | DGND     | I/O | Р   |      | Ground                                      |

| G5             | DGND     | I/O | Р   |      | Ground                                      |

Table 1. PAD LIST (continued)

| Pad Identifier | Pad Name | I/O | A/D | Pull | Description |

|----------------|----------|-----|-----|------|-------------|

| G6             | DGND     | I/O | Р   |      | Ground      |

| G7             | DGND     | I/O | Р   |      | Ground      |

| G8             | DGND     | I/O | Р   |      | Ground      |

| H1             | DGND     | I/O | Р   |      | Ground      |

| H8             | DGND     | I/O | Р   |      | Ground      |

| J1             | DGND     | I/O | Р   |      | Ground      |

| J8             | DGND     | I/O | Р   |      | Ground      |

| K1             | DGND     | I/O | Р   |      | Ground      |

| K8             | DGND     | I/O | Р   |      | Ground      |

| L1             | DGND     | I/O | Р   |      | Ground      |

| L8             | DGND     | I/O | Р   |      | Ground      |

# **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Symbol    | Parameter                   | Min      | Max                                     | Unit |

|-----------|-----------------------------|----------|-----------------------------------------|------|

| VBAT      | Power supply voltage        |          | 3.63                                    | V    |

| VDDO      | I/O supply voltage (Note 1) |          | 3.63                                    | V    |

| VSSRF     | RF front-end ground         | -0.3     |                                         | V    |

| VSSA      | Analog ground               | -0.3     |                                         | V    |

| VSSD      | Digital core and I/O ground | -0.3     |                                         | V    |

| Vin       | Voltage at any input pin    | VSSD-0.3 | VDDO+0.3<br>(Up to a maximum of 3.63 V) | V    |

| T storage | Storage temperature range   | -40      | 85                                      | °C   |

Caution: Class 2 ESD Sensitivity, JESD22-A114-B (2000 V) The QFN package meets 450 V CDM level

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. VDDO voltage must not be applied before VBAT voltage on cold start.

**Table 3. RECOMMENDED OPERATING CONDITIONS**

| Description                    | Symbol       | Conditions                                | Min  | Тур  | Max | Unit |

|--------------------------------|--------------|-------------------------------------------|------|------|-----|------|

| Supply voltage operating range | VBAT         | Input supply voltage on VBAT pin (Note 2) | 1.18 | 1.25 | 3.3 | V    |

| Functional temperature range   | T functional |                                           | -40  | _    | 85  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

- 2. In order to be able to use a VBAT Min of 1.1 V, the following reduced operating conditions should be observed:

- Maximum Tx power 0 dBm.

- SYSCLK ≤ 24 MHz.

- Functional temperature range limited to 0–50 deg C

The following trimming parameters should be used:

- VCC = 1.10 V

- VDDC = 0.92 V

- VDDM = 1.05 V, will be limited by VCC at end of battery life

- VDDRF = 1.05 V, will be limited by VCC at end of battery life. VDDPA should be disabled

RSL10 should enter in end-of-battery-life operating mode if VCC falls below 1.03 V. VCC will remain above 1.03 V if VBAT ≥ 1.10 V under the restricted operating conditions described above.

**Table 4. ELECTRICAL PERFORMANCE SPECIFICATIONS**Unless otherwise noted, the specifications mentioned in the table below are valid at 25°C for VBAT = VDDO = 1.25 V in LDO mode, or VBAT = VDDO = 3 V in DC-DC (buck) mode.

| Description                                                               | Symbol            | Conditions                                                                                     | Min | Тур  | Max | Unit                |

|---------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------|-----|------|-----|---------------------|

| OVERALL                                                                   |                   |                                                                                                |     |      |     |                     |

| Current consumption RX,<br>V <sub>BAT</sub> = 1.25 V, low latency         | I <sub>VBAT</sub> |                                                                                                |     | 1.8  |     | mA                  |

| Current consumption TX,<br>V <sub>BAT</sub> = 1.25 V, low latency         | I <sub>VBAT</sub> |                                                                                                |     | 1.8  |     | mA                  |

| Current consumption RX,<br>V <sub>BAT</sub> = 1.25 V                      | I <sub>VBAT</sub> |                                                                                                |     | 1.15 |     | mA                  |

| Deep sleep current,<br>example 1, V <sub>BAT</sub> = 1.25 V               | lds1              | Wake up from wake up pin or DIO wake up.                                                       |     | 50   |     | nA                  |

| Deep sleep current,<br>example 2, V <sub>BAT</sub> = 1.25 V               | lds2              | Embedded 32 kHz oscillator running with interrupts from timer or external pin.                 |     | 90   |     | nA                  |

| Deep sleep current,<br>example 3, V <sub>BAT</sub> = 1.25 V               | lds3              | As Ids2 but with 8 kB RAM data retention.                                                      |     | 300  |     | nA                  |

| Standby Mode current,<br>V <sub>BAT</sub> = 1.25 V                        | Istb              | Digital blocks and memories are not clocked and are powered at a reduced voltage.              |     | 30   |     | μΑ                  |

| Current consumption RX,<br>V <sub>BAT</sub> = 3 V                         | I <sub>VBAT</sub> |                                                                                                |     | 0.9  |     | mA                  |

| Current consumption TX,<br>V <sub>BAT</sub> = 3 V                         | I <sub>VBAT</sub> |                                                                                                |     | 0.9  |     | mA                  |

| Deep sleep current,<br>example 1, V <sub>BAT</sub> = 3 V                  | lds1              | Wake up from wake up pin or DIO wake up.                                                       |     | 25   |     | nA                  |

| Deep sleep current,<br>example 2, V <sub>BAT</sub> = 3 V                  | lds2              | Embedded 32 kHz oscillator running with interrupts from timer or external pin.                 |     | 40   |     | nA                  |

| Deep sleep current,<br>example 3, V <sub>BAT</sub> = 3 V                  | lds3              | As Ids2 but with 8 kB RAM data retention.                                                      |     | 100  |     | nA                  |

| Standby Mode current,<br>V <sub>BAT</sub> = 3 V                           | Istb              | Digital blocks and memories are not clocked and are powered at a reduced voltage.              |     | 17   |     | μΑ                  |

| EEMBC ULPMark BENCHMARK,                                                  | CORE PROFIL       | E                                                                                              |     |      |     |                     |

| ULPMark CP 3.0 V                                                          |                   | Arm Cortex–M3 processor running from RAM, VBAT= 3.0 V, IAR C/C++ Compiler for ARM 8.20.1.14183 |     | 1090 |     | ULP<br>Mark         |

| ULPMark CP 2.1 V                                                          |                   | Arm Cortex–M3 processor running from RAM, VBAT= 2.1 V, IAR C/C++ Compiler for ARM 8.20.1.14183 |     | 1260 |     | ULP<br>Mark         |

| EEMBC CoreMark BENCHMARK                                                  | for the Arm Co    | rtex-M3 Processor and the LPDSP32 DSP                                                          | )   |      |     |                     |

| Arm Cortex–M3 processor running from RAM                                  |                   | At 48 MHz SYSCLK. Using the IAR 8.10.1 C compiler, certified                                   |     | 159  |     | Core<br>Mark        |

| LPDSP32 running from RAM                                                  |                   | At 48 MHz SYSCLK<br>Using the 2020.03 release of<br>the Synopsys LPDSP32 C compiler            |     | 174  |     | Core<br>Mark        |

| Arm Cortex-M3 processor and<br>LPDSP32 running from RAM,<br>VBAT = 1.25 V |                   | At 48 MHz SYSCLK                                                                               |     | 123  |     | Core<br>Mark/<br>mA |

| Arm Cortex-M3 processor and LPDSP32 running from RAM, VBAT = 3 V          |                   | At 48 MHz SYSCLK                                                                               |     | 293  |     | Core<br>Mark/<br>mA |

| Arm Cortex-M3 processor<br>running CoreMark from RAM,<br>VBAT = 1.25 V    |                   | At 48 MHz SYSCLK<br>(processor consumption only)                                               |     | 29.1 |     | μ <b>A</b> /MHz     |

**Table 4. ELECTRICAL PERFORMANCE SPECIFICATIONS** (continued)

Unless otherwise noted, the specifications mentioned in the table below are valid at 25°C for VBAT = VDDO = 1.25 V in LDO mode, or VBAT = VDDO = 3 V in DC-DC (buck) mode.

| Description                                                              | Symbol                 | Conditions                                       | Min  | Тур  | Max                     | Unit            |

|--------------------------------------------------------------------------|------------------------|--------------------------------------------------|------|------|-------------------------|-----------------|

| EEMBC CoreMark BENCHMARK                                                 | for the Arm Cor        | tex-M3 Processor and the LPDSP32                 | DSP  |      |                         |                 |

| Arm Cortex-M3 processor<br>running CoreMark from RAM,<br>VBAT = 3 V      |                        | At 48 MHz SYSCLK<br>(processor consumption only) |      | 12.3 |                         | μ <b>A/MHz</b>  |

| Arm Cortex-M3 processor<br>running CoreMark from Flash,<br>VBAT = 1.25 V |                        | At 48 MHz SYSCLK<br>(processor consumption only) |      | 34.3 |                         | μ <b>A/MHz</b>  |

| Arm Cortex-M3 processor<br>running CoreMark from Flash,<br>VBAT = 3 V    |                        | At 48 MHz SYSCLK<br>(processor consumption only) |      | 14.6 |                         | μ <b>A</b> /MHz |

| LPDSP32 running CoreMark<br>from RAM, VBAT = 1.25 V                      |                        | At 48 MHz SYSCLK<br>(processor consumption only) |      | 19.5 |                         | μ <b>A</b> /MHz |

| LPDSP32 running CoreMark<br>from RAM, VBAT = 3 V                         |                        | At 48 MHz SYSCLK<br>(processor consumption only) |      | 8.2  |                         | μ <b>A</b> /MHz |

| INTERNALLY GENERATED VDDC                                                | : Digital Block        | Supply Voltage                                   |      |      |                         |                 |

| Supply voltage: operating range                                          | VDDC                   |                                                  | 0.92 | 1.15 | 1.32<br>(Note 3)        | V               |

| Supply voltage: trimming range                                           | VDDC <sub>RANGE</sub>  |                                                  | 0.75 |      | 1.38                    | V               |

| Supply voltage: trimming step                                            | VDDC <sub>STEP</sub>   |                                                  |      | 10   |                         | mV              |

| INTERNALLY GENERATED VDDN                                                | 1։ Memories Sup        | oply Voltage                                     |      |      |                         |                 |

| Supply voltage: operating range                                          | VDDM                   |                                                  | 1.05 | 1.15 | 1.32<br>(Note 4)        | V               |

| Supply voltage: trimming range                                           | VDDM <sub>RANGE</sub>  |                                                  | 0.75 |      | 1.38                    | V               |

| Supply voltage: trimming step                                            | VDDM <sub>STEP</sub>   |                                                  |      | 10   |                         | mV              |

| INTERNALLY GENERATED VDDF                                                | F: Radio Front         | end supply voltage                               |      |      |                         |                 |

| Supply voltage: operating range                                          | VDDRF                  |                                                  | 1.00 | 1.10 | 1.32 (Notes<br>5 and 6) | V               |

| Supply voltage: trimming range                                           | VDDRF <sub>RANGE</sub> |                                                  | 0.75 |      | 1.38                    | V               |

| Supply voltage: trimming step                                            | VDDRF <sub>STEP</sub>  |                                                  |      | 10   |                         | mV              |

| VDDO PAD SUPPLY VOLTAGE: D                                               | igital Level High      | ı Voltage                                        |      |      |                         |                 |

| Digital I/O supply                                                       | VDDO                   |                                                  | 1.1  | 1.25 | 3.3                     | V               |

| INDUCTIVE BUCK DC-DC CONV                                                | ERTER                  |                                                  |      |      |                         |                 |

| VBAT range when the DC–DC converter is active (Note 7)                   | DCDC<br>IN_RANGE       |                                                  | 1.4  |      | 3.3                     | V               |

| VBAT range when the LDO is active                                        | LDO<br>IN_RANGE        |                                                  | 1.1  |      | 3.3                     | V               |

| Output voltage: trimming range                                           | DCDC<br>OUT_RANGE      |                                                  | 1.1  | 1.2  | 1.32                    | V               |

| Supply voltage: trimming step                                            | DCDC <sub>STEP</sub>   |                                                  |      | 10   |                         | mV              |

| POWER-ON RESET                                                           |                        |                                                  | -    |      |                         |                 |

| POR voltage                                                              | VBAT <sub>POR</sub>    |                                                  | 0.4  | 8.0  | 1.0                     | V               |

| RADIO FRONT-END: General Sp                                              | ecifications           |                                                  |      |      |                         |                 |

| RF input impedance                                                       | Z <sub>in</sub>        | Single ended                                     |      | 50   |                         | Ω               |

| Data rate FSK / MSK / GFSK                                               | R <sub>FSK</sub>       | OQPSK as MSK                                     | 62.5 | 1000 | 3000                    | kbps            |

| Data rate 4–FSK                                                          |                        |                                                  |      |      | 4000                    | kbps            |

| On-air data rate                                                         | bps                    | GFSK                                             | 250  |      | 2000                    | kbps            |

**Table 4. ELECTRICAL PERFORMANCE SPECIFICATIONS** (continued)

Unless otherwise noted, the specifications mentioned in the table below are valid at 25°C for VBAT = VDDO = 1.25 V in LDO mode, or VBAT = VDDO = 3 V in DC-DC (buck) mode.

| Description                                                   | Symbol               | Conditions                                                   | Min  | Тур  | Max             | Unit |

|---------------------------------------------------------------|----------------------|--------------------------------------------------------------|------|------|-----------------|------|

| RADIO FRONT-END: Crystal and                                  | Clock Specific       | ations                                                       |      |      |                 |      |

| Xtal frequency                                                | F <sub>XTAL</sub>    | Fundamental                                                  |      | 48   |                 | MHz  |

| Settling time                                                 |                      |                                                              |      | 0.5  | 1.5             | ms   |

| RADIO FRONT-END: Synthesizer                                  | Specifications       |                                                              |      |      |                 |      |

| Frequency range                                               | F <sub>RF</sub>      | Supported carrier frequencies                                | 2360 |      | 2500            | MHz  |

| RX frequency step                                             |                      | RX Mode frequency synthesizer resolution                     |      |      | 100             | Hz   |

| TX frequency step                                             |                      | TX Mode frequency synthesizer resolution                     |      |      | 600             | Hz   |

| PLL Settling time, RX                                         | t <sub>PLL_RX</sub>  | RX Mode                                                      |      | 15   | 25              | μs   |

| PLL Settling time, TX                                         | t <sub>PLL_TX</sub>  | TX mode, BLE modulation                                      |      | 5    | 10              | μS   |

| RADIO FRONT-END: Receive Mo                                   | de Specificatio      | ns                                                           |      |      |                 |      |

| Current consumption at 1 Mbps, V <sub>BAT</sub> = 1.25 V      | IBAT <sub>RFRX</sub> | VDDRF = 1.1 V, 100% duty cycle                               |      | 5.6  |                 | mA   |

| Current consumption at 2 Mbps, V <sub>BAT</sub> = 1.25 V      | IBAT <sub>RFRX</sub> | VDDRF = 1.1 V, 100% duty cycle                               |      | 6.2  |                 | mA   |

| Current consumption at 1 Mbps, $V_{BAT} = 3 \text{ V, DC-DC}$ | IBAT <sub>RFRX</sub> | VDDRF = 1.1 V, 100% duty cycle                               |      | 3.0  |                 | mA   |

| Current consumption at 2 Mbps, V <sub>BAT</sub> = 3 V, DC–DC  | IBAT <sub>RFRX</sub> | VDDRF = 1.1 V, 100% duty cycle                               |      | 3.4  |                 | mA   |

| RX Sensitivity, 0.25 Mbps                                     |                      | 0.1% BER (Notes 8, 9)                                        |      | -96  |                 | dBm  |

| RX Sensitivity, 0.5 Mbps                                      |                      | 0.1% BER (Notes 8, 9)                                        |      | -95  |                 | dBm  |

| RX Sensitivity, 1 Mbps, BLE                                   |                      | 0.1% BER (Notes 8, 9) Single–ended match to 50 $\Omega$      |      | -93  |                 | dBm  |

| RX Sensitivity, 2 Mbps, BLE                                   |                      | 0.1% BER (Notes 8, 9)                                        |      | -91  |                 | dBm  |

| RSSI effective range                                          |                      | Without AGC                                                  |      | 60   |                 | dB   |

| RSSI step size                                                |                      |                                                              |      | 2.4  |                 | dB   |

| RX AGC range                                                  |                      |                                                              |      | 48   |                 | dB   |

| RX AGC step size                                              |                      | Programmable                                                 |      | 6    |                 | dB   |

| Max usable signal level                                       |                      | 0.1% BER                                                     |      | -10  |                 | dBm  |

| RADIO FRONT-END: Transmit Mo                                  | ode Specification    | ons                                                          |      |      |                 |      |

| Tx peak power consumption at VBAT = 1.25 V (Note 10)          | IBAT <sub>RFTX</sub> | Tx power 0 dBm, VDDRF = 1.07 V,<br>VDDPA: off, LDO mode      |      | 8.9  |                 | mA   |

|                                                               |                      | Tx power 3 dBm, VDDRF = 1.1 V,<br>VDDPA: 1.26 V, LDO mode    |      | 17.4 |                 | mA   |

|                                                               |                      | Tx power 6 dBm, VDDRF = 1.1 V,<br>VDDPA: 1.60 V, LDO mode    |      | 25   |                 | mA   |

| Tx peak power consumption at VBAT = 3 V (Note 10)             | IBAT <sub>RFTX</sub> | Tx power 0 dBm, VDDRF = 1.07 V, VDDPA: off, DC–DC mode       |      | 4.6  |                 | mA   |

|                                                               |                      | Tx power 3 dBm, VDDRF = 1.1 V,<br>VDDPA = 1.26 V, DC-DC mode |      | 8.6  |                 | mA   |

|                                                               |                      | Tx power 6 dBm, VDDRF = 1.1 V,<br>VDDPA = 1.60 V, DC-DC mode |      | 12   |                 | mA   |

| Transmit power range                                          |                      | BLE                                                          | -17  |      | +6<br>(Note 12) | dBm  |

| Transmit power step size                                      |                      | Full band                                                    |      | 1    |                 | dB   |

**Table 4. ELECTRICAL PERFORMANCE SPECIFICATIONS** (continued)

Unless otherwise noted, the specifications mentioned in the table below are valid at 25°C for VBAT = VDDO = 1.25 V in LDO mode, or VBAT = VDDO = 3 V in DC-DC (buck) mode.

| Description                       | Symbol               | Conditions                                                | Min            | Тур   | Max            | Unit |

|-----------------------------------|----------------------|-----------------------------------------------------------|----------------|-------|----------------|------|

| RADIO FRONT-END: Transmit I       | Mode Specification   | ons                                                       |                |       |                |      |

|                                   |                      | Tx power 0 dBm. Full band. Relative to the typical value. | -1.5           |       | 1.5            | dB   |

| Power in 2 <sup>nd</sup> harmonic |                      | 0 dBm mode. 50 $\Omega$ for "Typ" value. (Note 11)        |                | -62   |                | dBm  |

| Power in 3 <sup>rd</sup> harmonic |                      | 0 dBm mode. 50 $\Omega$ for "Typ" value. (Note 11)        |                | -70   |                | dBm  |

| Power in 4 <sup>th</sup> harmonic |                      | 0 dBm mode. 50 $\Omega$ for "Typ" value. (Note 11)        |                | -82   |                | dBm  |

| ADC                               |                      |                                                           |                |       |                |      |

| Resolution                        | ADC <sub>RES</sub>   |                                                           | 8              | 12    | 14             | bits |

| Input voltage range               | ADC <sub>RANGE</sub> |                                                           | 0              |       | 2              | V    |

| INL                               | ADC <sub>INL</sub>   |                                                           | -2             |       | +2             | mV   |

| DNL                               | ADC <sub>DNL</sub>   |                                                           | -1             |       | +1             | mV   |

| Channel sampling frequency        | ADC <sub>CH_SF</sub> | For the 8 channels sequentially,<br>SLOWCLK = 1 MHz       | 0.0195         |       | 6.25           | kHz  |

| 32 kHz ON-CHIP RC OSCILLAT        | OR                   |                                                           |                |       |                |      |

| Untrimmed Frequency               | Freq <sub>UNTR</sub> |                                                           | 20             | 32    | 50             | kHz  |

| Trimming steps                    | Steps                |                                                           |                | 1.5   |                | %    |

| 3 MHz ON-CHIP RC OSCILLATO        | OR                   |                                                           |                |       |                |      |

| Untrimmed Frequency               | Freq <sub>UNTR</sub> |                                                           | 2              | 3     | 5              | MHz  |

| Trimming steps                    | Steps                |                                                           |                | 1.5   |                | %    |

| Hi Speed mode                     | Fhi                  |                                                           |                | 10    |                | MHz  |

| 32 kHz ON-CHIP CRYSTAL OSC        | CILLATOR             |                                                           |                |       |                |      |

| Output Frequency                  | Freq <sub>32k</sub>  | Depends on xtal parameters                                |                | 32768 |                | Hz   |

| Startup time                      |                      |                                                           |                | 1     | 3              | s    |

| Internal load trimming range      |                      | Steps of 0.4 pF                                           | 0              |       | 25.2           | pF   |

| Duty Cycle                        |                      |                                                           | 40             | 50    | 60             | %    |

| DC INPUT CHARACTERISTICS          | OF THE DIGITAL       | PADS - With VDDO = 2.97 V - 3.3 V, nom                    | inal: 3.0 V    | Logic |                |      |

| Voltage level for high input      | V <sub>IH</sub>      |                                                           | 2              |       | VDDO + 0.3     | V    |

| Voltage level for low input       | V <sub>IL</sub>      |                                                           | VSSD -<br>0.3  |       | 0.8            | V    |

| DC INPUT CHARACTERISTICS          | OF THE DIGITAL       | PADS - With VDDO = 1.1 V - 1.32 V, nom                    | inal: 1.2 V    | Logic |                |      |

| Voltage level for high input      | V <sub>IH</sub>      |                                                           | 0.65 *<br>VDDO |       | VDDO + 0.3     | V    |

| Voltage level for low input       | V <sub>IL</sub>      |                                                           | VSSD -<br>0.3  |       | 0.35 *<br>VDDO | V    |

| DC OUTPUT CHARACTERISTIC          | S OF THE DIGIT       | AL PADS                                                   |                |       |                |      |

| Voltage level for high output     | V <sub>OH</sub>      | I <sub>OH</sub> = 2 mA to 12 mA                           | VDDO -<br>0.4  |       |                | V    |

| Voltage level for low output      | V <sub>OL</sub>      | I <sub>OH</sub> = 2 mA to 12 mA                           | 4              |       | 0.4            | V    |

| DIO DRIVE STRENGTH                |                      | 1                                                         | -              | 1     |                | l.   |

| DIO drive strength                | IDIO                 |                                                           | 2              | 12    | 12             | mA   |

#### RSL<sub>10</sub> SIP

# Table 4. ELECTRICAL PERFORMANCE SPECIFICATIONS (continued)

Unless otherwise noted, the specifications mentioned in the table below are valid at 25°C for VBAT = VDDO = 1.25 V in LDO mode, or VBAT = VDDO = 3 V in DC-DC (buck) mode.

| Description                                                    | Symbol | Conditions | Min   | Тур | Max | Unit                      |

|----------------------------------------------------------------|--------|------------|-------|-----|-----|---------------------------|

| FLASH SPECIFICATIONS                                           |        |            |       |     |     |                           |

| Endurance of the 384 kB of flash                               |        |            | 10000 |     |     | write/<br>erase<br>cycles |

| Endurance for sections NVR1,<br>NVR2, and NVR3 (6 kB in total) |        |            | 1000  |     |     | write/<br>erase<br>cycles |

| Retention                                                      |        |            | 25    |     |     | years                     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 3. The maximum VDDC voltage cannot exceed the VBAT input voltage or the VCC output from the buck converter.

- 4. The maximum VDDM voltage cannot exceed the VBAT input voltage or the VCC output from the buck converter.

- 5. The maximum VDDRF voltage cannot exceed the VBAT input voltage or the VCC output from the buck converter.

- 6. The VDDRF calibrated target is 1.07 V (TX power = 0 dBm).

- 7. The LDO can be used to regulate down from VBAT and generate VCC. For VBAT values higher than 1.5 V, the LDO is less efficient and it is possible to save power by activating the DC–DC converter to generate VCC.

- 8. Signal generated by RF tester.

- 9. Single-ended match to 50 ohms, measured at pin E1 including loss of integrated Tx harmonic filter.

- 10. All values are based on evaluation board performance, including the harmonic filter loss.

- 11. The values shown here are including integrated RF filter.

- 12. For optimal performance, charge pump frequency of 125 kHz should be avoided when VDDPA supply is enabled.

#### Table 5. VDDM TARGET TRIMMING VOLTAGE IN FUNCTION OF VDDO VOLTAGE

| VDDM Voltage (V) | DIO_PAD_CFG DRIVE | Maximum VDDO Voltage (V) |

|------------------|-------------------|--------------------------|

| 1.05             | 1                 | 2.7                      |

| 1.05             | 0                 | 3.2                      |

| 1.10             | 0                 | 3.3                      |

NOTE: These are trimming targets at room/ATE temperature 25~30°C.

# Table 6. VDDC TARGET TRIMMING VOLTAGE IN FUNCTION OF SYSCLK FREQUENCY

| VDDC Voltage (V) | Maximum SYSCLK Frequency (MHz) | Restriction                                                                   |

|------------------|--------------------------------|-------------------------------------------------------------------------------|

| 0.92             | ≤ 24                           | The ADC will be functional in low frequency mode and between 0 and 85°C only. |

| 1.00             | ≤ 24                           | Fully functional                                                              |

| 1.05             | 48                             | Fully functional                                                              |

NOTE: These are trimming targets at room/ATE temperature 25~30°C.

# **ANTENNA SPECIFICATIONS**

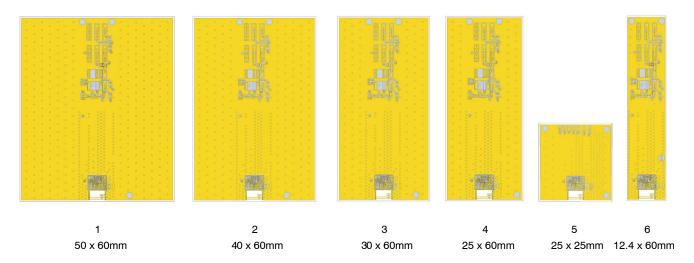

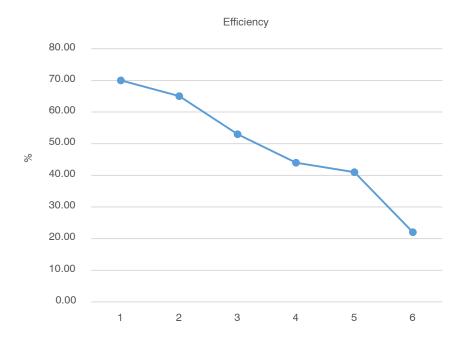

The antenna performance of the RSL10 SIP depends on the size of the ground plane on which it is mounted. Figure 5 shows an overview of different ground plane sizes with expected antenna return losses shown in Figure 6.

Figure 5. PCB ground planes. 1) 50x60, 2) 40x60, 3) 30x60, 4) 25x60, 5) 12.5x60. All sizes in mm

Figure 6. Antenna Efficiency vs. PCB Size

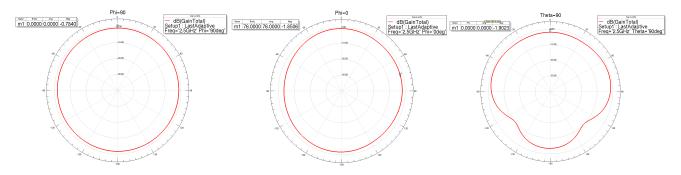

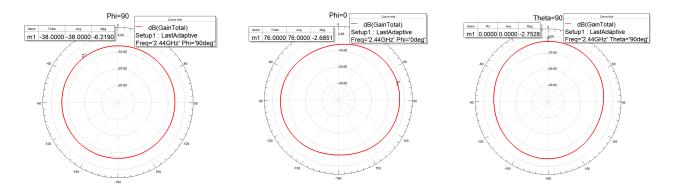

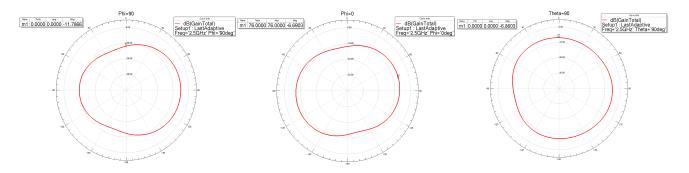

Figure 7. Radiation Pattern for 50 x 60 mm PCB Ground Plane

Figure 8. Radiation Pattern for 40 x 60 mm PCB Ground Plane

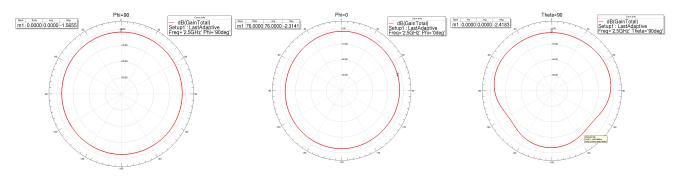

Figure 9. Radiation Pattern for 30 x 60 mm PCB Ground Plane

Figure 10. Radiation Pattern for 25 x 60 mm PCB Ground Plane

Figure 11. Radiation Pattern for 25 x 25 mm PCB Ground Plane

Figure 12. Radiation Pattern for 12.5 x 60 mm PCB Ground Plane

# **ENVIRONMENTAL SPECIFICATIONS**

# Electrostatic Discharge (ESD) Sensitive Device

CAUTION: ESD sensitive device. Permanent damage may occur on devices subjected to high-energy electrostatic discharges.

Proper ESD precautions in handling, packaging and testing are recommended to avoid performance degradation or loss of functionality.

# **Solder Information**

The RSL10 SIP is constructed with all RoHS compliant material and should be reflowed accordingly. This device is Moisture Sensitive Class MSL3 and must be stored and handled accordingly. Re–flow according to IPC/JEDEC standard J–STD–020C, Joint Industry Standard: Re–flow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices. Hand soldering is not recommended for this part.

For more information, see SOLDERRM/D available from www.onsemi.com.

# RSL<sub>10</sub> SIP

#### **REGULATORY INFORMATION**

# **FCC Regulatory and User Information**

#### FCC ID: 2APD9-RSL10SIP

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

(1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Any changes or modifications not expressly approved by onsemi could void the user's authority to operate the equipment.

# **Module Usage Conditions**

Manufacturers of products incorporating the RSL10SIP Bluetooth 5.2 Module are authorized to use the FCC Grant of the RSL10SIP module for their own products according to the conditions referenced in the grant.

A product containing the RSL10SIP module shall bear a label referring to the enclosed module. The label shall use wording such as: "Contains FCC ID:2APD9-RSL10SIP"

The label of the host device shall also contain the following statement. When this is not possible, the information shall be included in the User Manual of the host device:

"This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

(1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Any changes or modifications not expressly approved by onsemi could void the user's authority to operate the equipment."

# **WARNING: RF Exposure Compliance**

In order to comply with FCC RF exposure requirements this device must be installed to provide a separation distance of 5 mm or greater between this device and the user.

#### ISED Regulatory and User Information

# ISED ID 23763-RSL10SIP

#### **HVIN RSL10SIP**

This device contains licence–exempt transmitter(s)/receiver(s) that comply with Innovation, Science and Economic Development Canada's licence–exempt RSS(s). Operation is subject to the following two conditions:

- (1) This device may not cause interference.

- (2) This device must accept any interference, including interference that may cause undesired operation of the device.

L'émetteur/récepteur exempt de licence contenu dans le présent appareil est conforme aux CNR d'Innovation, Sciences et Développement économique Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes: (1) L'appareil ne doit pas produire de brouillage; (2) L'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### **Module Usage Conditions**

A product containing the RSL10SIP module shall bear a label referring to the enclosed module. The label shall use wording such as: "Contains IC: 23763–RSL10SIP"

The label of the host device shall also contain the following statement. When this is not possible, the information shall be included in the User Manual of the host device:

"This device contains licence-exempt transmitter(s)/receiver(s) that comply with Innovation, Science and Economic Development Canada's licence-exempt RSS(s). Operation is subject to the following two conditions:

- (1) This device may not cause interference.

- (2) This device must accept any interference, including interference that may cause undesired operation of the device." The transmitter module may not be co-located with any other transmitter or antenna.

Un produit contenant le module RSL10SIP devra porter une étiquette du dispositif qui fait référence au module inclus. L'étiquette du dispositif devra utiliser un libellé tel que: "Contient IC: 23763-RSL10SIP"

L'étiquette du dispositif devra également inclure la déclaration ci-dessous. Si cela n'est pas possible, cette information devra être précisée dans le manuel de l'utilisateur:

L'émetteur/récepteur exempt de licence contenu dans le présent appareil est conforme aux CNR d'Innovation, Sciences et Développement économique Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes: (1) L'appareil ne doit pas produire de brouillage; (2) L'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

Le module émetteur peut ne pas être coïmplanté avec un autre émetteur ou antenne.

#### **WARNING: RF Exposure Compliance**

In order to comply with ISED RF exposure requirements this device must be installed to provide a separation distance of 7 mm or greater between this device and the user.

Afin de se conformer aux exigences d'exposition ISDE RF, cet appareil doit être installé pour fournir une distance de séparation de 7 mm ou plus entre cet appareil et l'utilisateur.

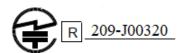

# Korean Regulatory and User Information

특정소출력 무선기기(데이터통신시스템용 무선기기)

제 조 자 (제조자): onsemi

제 조 국 (원산지): 캐나다

제 품 명 (제품): NCH-RSL10-101S51-ACG

모 델 명 (모델): RSL10SIP

제조년월`(생산일자): 계류 중

이 장치는 이동전화, Wi-Fi 또는 블루투스 장치 등 무선통신장치와 매우 근접한 장소에서 사용할 경우 오작동을 일으킬 가능성이 있습니다.

해당 무선설비는 전파혼신 가능성이 있으므로 인명안전과 관련된 서비스는 할 수 없음.

The following ID information needs to be added to the product package (application and user documentation).

Korean KC Mark and Identifier as shown below. Height of KC mark is 5mm minimum. Colour preference is Navy (5PB 2/8 color according to KS A 0062). Acceptable other colours are black, gold and silver. Other colours may only be used if preferred colours are not legible for the mark. The conformity assessment certification number is to be near the KC mark. (usually below).

R-CRM-oNs-RSL10SIP

# **European Regulatory and User Information**

This device complies with the essential requirements of the Radio Equipment Directive 2014/53/EU. The following ID information needs to be added to the product package (application and user documentation).

#### **Japanese Regulatory and User Information**

The following ID information needs to be added to the product package (application and user documentation).

ID (209-J00320) and must be combined with the Giteki (MIC) Mark as specified below.

当該機器には電波法に基づく、技術基準適合証明等を受けた特定無線設備を装着している。

Translation: "This equipment contains specified radio equipment that has been certified to the Technical Regulation Conformity Certification under the Radio Law."

# **Development Tools**

RSL10 is supported by a full suite of comprehensive tools including:

- An easy-to-use development board

- Software Development Kit (SDK) including an Oxygen Eclipse-based development environment, Bluetooth protocol stacks, sample code, libraries, and documentation

# **Export Control Classification Number (ECCN)**

The ECCN designation for RSL10 is 5A991.g.

# **Company or Product Inquiries**

For more information about **onsemi** products or services visit our Web site at <a href="www.onsemi.com">www.onsemi.com</a>.

For sales or technical support, contact your local representative or authorized distributor.

Bluetooth is a registered trademark of Bluetooth SIG. Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries).

PAD A1

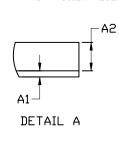

LOCATION

NOTE 4

ח

· D1 ·

-A

В

**DATE 30 JUN 2020**

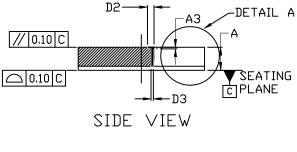

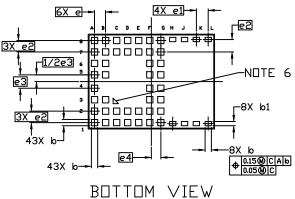

#### NUTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM THE TERMINAL TIP.

- 4. PIN 1 IDENTIFIER IS LOCATED HERE MAY APPEAR AS A CHAMFER, INK MARK, METALLIZED MARK, ETC.

- REFER TO PRODUCT DATASHEET FOR SPECIFIC KEEP-DUT AREA AND GROUND PLANE REQUIREMENTS.

- DRIENTATION MARKER ON BOTTOM SIDE USEABLE BY VISION RECOGNITION EQUIPMENT

TOP VIEW

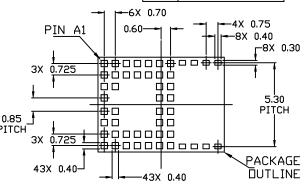

# RECOMMENDED MOUNTING FOOTPRINT

For additional information on our Pb-Free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

# **GENERIC MARKING DIAGRAM\***

XXXXXXX XXXXXXX AWLYW=

= Assembly Location

WL = Wafer Lot = Year

W = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON85298G | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SIP51 8x6   |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMi., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer p

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative