# MP8001, MP8001A

15W Power Over Ethernet PoE Powered Device (PD) Controller

## **DESCRIPTION**

The MP8001/MP8001A are IEEE 802. 3 af POE compliant Powered Device (PD) controllers. they include detection and classification modes as well as a 100V output pass device having a temperature compensated current limit over the specified temperature range. Thermal protection is built in to accommodate both transient and/or overload conditions, shutting the part down and protecting the input source as well as the output load depending on the particular fault conditions. Inrush current limiting is included to slowly charge the input capacitor without interruption due to die heating, a problem encountered without the current limit foldback feature.

## **FEATURES**

- Meets IEEE 802. 3 af Specifications

- 100V, 1Ω Integrate DMOS Device

- 420mA Current Limit for MP8001 810mA Current Limit for MP8001A

- Open Drain Power Good Output

- SOIC-8 Package

# **APPLICATIONS**

- VoIP Telephones

- Network Cards

- Security Camera Systems

- Safety Backup Power

- Remote Internet Power

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

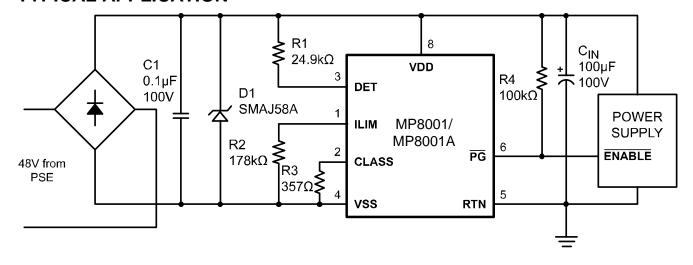

#### TYPICAL APPLICATION

# ORDERING INFORMATION

| Part Number | Package | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|-------------|---------|-------------|----------------------------------------|

| MP8001DS*   | SOIC-8  | MP8001DS    | -40°C to +85°C                         |

| MP8001ADS** | SOIC-8  | MP8001A     | -40°C to +85°C                         |

\* For Tape & Reel, add suffix –Z (e.g. MP8001DS–Z). For RoHS compliant packaging, add suffix –LF (e.g. MP8001DS–LF–Z)

\*\* For Tape & Reel, add suffix –Z (e.g. MP8001ADS–Z). For RoHS compliant packaging, add suffix –LF (e.g. MP8001ADS–LF–Z)

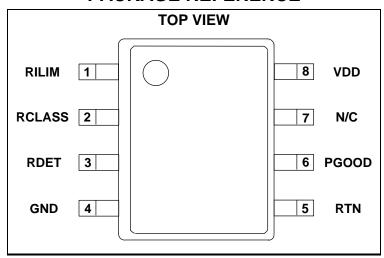

# **PACKAGE REFERENCE**

# **ABSOLUTE MAXIMUM RATINGS (1)**

| V <sub>DD</sub> , RTN           | 0.3V to +100V                               |

|---------------------------------|---------------------------------------------|

| PG, DET                         | 0.3V to +57V                                |

| I <sub>LIM</sub>                | 0.3V to +7V                                 |

| CLASS                           | 0.3V to +12V                                |

| Continuous Power Dissipat       | tion(T <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                 | 1.19W                                       |

| Junction Temperature            | 150°C                                       |

| Lead Temperature                | 260°C                                       |

| Storage Temperature             | 65°C to +150°C                              |

| Recommended Operati             | ing Conditions <sup>(3)</sup>               |

| Supply Voltage V <sub>IN</sub>  | 0V to 57V                                   |

| Output Current I <sub>OUT</sub> | 0 to 0.4A                                   |

| Operating Temperature           | 40°C to +85°C                               |

Junction Temperature .....-40°C to +125°C

# **Thermal Resistance** (4) θ<sub>JA</sub> θ<sub>JC</sub> SOIC-8 ......105 .....50 ... °C/W

#### Notes

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{DD}$  = 48V, all voltages with respect to  $V_{SS},\,V_{SS}$  = 0V;  $R_{DET}$  = 26.1k $\Omega,\,R_{CLASS}$  = 4.42K $\Omega,\,R_{ILIM}$  =178k $\Omega,\,T_A$  = 25°C, unless otherwise noted.

| T <sub>A</sub> = 25°C, unless otherwise noted.        |                       |                                                                                                   |                                 |      |      |      |       |

|-------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|-------|

| Parameter                                             | Symbol                | Condition                                                                                         |                                 | Min  | Тур  | Max  | Units |

| Detection                                             | 1                     | 1                                                                                                 |                                 | 1    | 1    | 1    |       |

| Detection on                                          | V <sub>DET_ON</sub>   | $V_{DD} = V_{RTN} = V_{PG} = 1.9V$                                                                |                                 |      | 1.9  |      | V     |

| Detection off                                         | $V_{DET\_OFF}$        | $V_{DD}=V_{RTN}=V_{PG}=11V$                                                                       |                                 | 11   |      | V    |       |

| Detection on/off<br>Hysteresis                        | V <sub>DET_H</sub>    | Falling below 11V on Threshold                                                                    |                                 |      | 0.2  |      | V     |

| DET Leakage Current                                   | V <sub>DET_LK</sub>   | V <sub>DET</sub> =V <sub>VDD</sub> =57V, Measure I <sub>DET</sub>                                 |                                 |      | 0.1  | 5    | μA    |

|                                                       | I <sub>DET</sub>      | $V_{VDD}$ = $V_{RTN}$<br>$R_{DET}$ =26.1 $k\Omega$ ,<br>Measure $I_{VDD}$ + $I_{RTN}$ + $I_{DET}$ | V <sub>DD</sub> = 3V            | 135  | 140  | 145  | μA    |

| Detection Current                                     |                       |                                                                                                   | V <sub>DD</sub> = 10.1V         | 405  | 420  | 435  | μA    |

| Classification                                        |                       |                                                                                                   |                                 |      |      |      |       |

| V <sub>CLASS</sub> Output Voltage                     | V <sub>CL</sub>       | Over a Load Range of 1                                                                            | mA to 41.2 mA                   | 9.6  | 10   | 10.3 | V     |

|                                                       |                       | R <sub>CLASS</sub> =4420Ω, 13≤V <sub>VDD</sub>                                                    | ≤21V (guar by V <sub>CL</sub> ) | 2.2  | 2.4  | 2.8  |       |

|                                                       |                       | $R_{CLASS}=953\Omega$ , $13\leq V_{VDD}\leq 21V$ (guar by $V_{CL}$ )                              |                                 | 10.3 | 10.6 | 11.3 |       |

| Classification Current                                | I <sub>CLASS</sub>    | $R_{CLASS}$ =549 $\Omega$ , 13 $\leq$ V <sub>VDD</sub> $\leq$ 21V (guar by V <sub>CL</sub> )      |                                 | 17.7 | 18.3 | 19.5 | mA    |

|                                                       |                       | $R_{CLASS}=357\Omega$ , $13 \le V_{VDD} \le 21V$ (guar by $V_{CL}$ )                              |                                 | 27.1 | 28   | 29.5 |       |

|                                                       |                       | $R_{CLASS}=255\Omega$ , $13 \le V_{VDD} \le 21V$ (guar by $V_{CL}$ )                              |                                 | 38   | 39.4 | 41.2 |       |

| Classification Lower<br>Threshold                     | V <sub>CL_ON</sub>    | Regulator Turns on, V <sub>VDD</sub> Rising                                                       |                                 | 10.2 | 11.3 | 13   | V     |

| Classification Upper<br>Threshold                     | V <sub>CU_OFF</sub>   | Regulator Turns off, V <sub>VDD</sub> Rising                                                      |                                 | 21   | 21.9 | 23   | V     |

|                                                       | V <sub>CU_H</sub>     | Hysteresis                                                                                        |                                 |      | 0.4  |      | V     |

| IC Supply Current during Classification               | I <sub>IN_CLASS</sub> | V <sub>DD</sub> = 17.5V, CLASS Floating, RTN Tied to VSS                                          |                                 |      | 300  | 500  | μA    |

| Leakage Current                                       | I <sub>LEAKAGE</sub>  | $V_{CLASS} = 0 \text{ V}, V_{VDD} = 57 \text{V}$                                                  |                                 |      |      | 1    | μA    |

| Pass Device                                           | •                     |                                                                                                   |                                 | •    | •    | •    |       |

| On Resistance                                         | R <sub>DS(ON)</sub>   | I <sub>RTN=</sub> 300mA                                                                           |                                 |      | 1.0  | 1.2  | Ω     |

| Leakage Current                                       | I <sub>SW_LK</sub>    | $V_{VDD}=V_{RTN}=57V$                                                                             |                                 |      | 1    | 15   | μΑ    |

| Current Limit                                         | I <sub>LIMIT</sub>    | V <sub>RTN</sub> =1V                                                                              | MP8001                          | 380  | 420  | 460  | mA    |

| Current Limit                                         |                       |                                                                                                   | MP8001A                         | 720  | 810  | 900  | mA    |

| Inruch Limit                                          | I <sub>INRUSH</sub>   | $V_{RTN}$ =2V, $R_{ILM}$ =178k $\Omega$                                                           | MP8001                          | 120  | 150  | 200  | mA    |

| Inrush Limit                                          |                       |                                                                                                   | MP8001A                         | 290  | 330  | 370  | mA    |

| PG                                                    |                       |                                                                                                   |                                 |      |      |      |       |

| Latch off Voltage<br>Threshold Rising <sup>(5)</sup>  |                       | V <sub>RTN</sub> Rising                                                                           |                                 | 9.5  | 10   | 10.5 | V     |

| Latch off Voltage<br>Threshold Falling <sup>(5)</sup> |                       | V <sub>RTN</sub> Falling                                                                          |                                 |      | 1.2  |      | V     |

| PG Deglitch <sup>(5)</sup>                            |                       | Delay Rising and Falling PDG                                                                      |                                 | 75   | 150  | 225  | μs    |

| Output Low Voltage                                    |                       | I <sub>PG</sub> = 400 μA                                                                          |                                 |      | 0.12 | 0.4  | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{DD}$  = 48V, all voltages with respect to  $V_{SS}$ ,  $V_{SS}$  = 0V;  $R_{DET}$  = 26.1k $\Omega$ ,  $R_{CLASS}$  = 4.42K $\Omega$ ,  $R_{ILIM}$  =178k $\Omega$ ,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                    | Symbol              | Condition                                                             | Min  | Тур  | Max  | Units  |

|----------------------------------------------|---------------------|-----------------------------------------------------------------------|------|------|------|--------|

| Leakage Current                              |                     | V <sub>PG</sub> = 57 V, V <sub>RTN</sub> = 0 V                        |      | 0.1  | 1    | μΑ     |

| UVLO                                         |                     |                                                                       |      |      |      |        |

| Voltage at V <sub>VDD</sub>                  |                     | V <sub>VDD</sub> Rising (including 1.4V Diode drop)                   | 38   | 40   | 42   | V      |

|                                              |                     | V <sub>VDD</sub> Falling (including 1.4V Diode drop)                  | 30.2 | 31.5 | 32.8 |        |

| Thermal Shutdown                             |                     |                                                                       |      |      |      |        |

| Thermal Shut down Temperature                | $T_{RISE}$          | Temperature Rising                                                    | 135  |      |      | ۰C     |

| Hysteresis                                   | T <sub>HYS</sub>    |                                                                       |      | 40   |      | °C     |

| Thermal Shut down<br>Counter <sup>(5)</sup>  | T <sub>COUNT</sub>  | Events Prior to Latch off                                             |      | 8    |      | counts |

| Thermal Counter Reset Voltage <sup>(5)</sup> | $V_{CRST}$          | Must Drop below Classification Range                                  |      | 10.8 |      | V      |

| Bias Current                                 |                     |                                                                       |      |      |      |        |

| Operating Current                            | I <sub>Q(VDD)</sub> | V <sub>DD</sub> = 48V, Pins 5, 6 Floating<br>Measure I <sub>VDD</sub> |      | 240  | 450  | μA     |

#### Notes:

<sup>5)</sup> Guaranteed by Design.

## PIN FUNCTIONS

| Pin# | Name  | Description                                                  |  |  |

|------|-------|--------------------------------------------------------------|--|--|

| 1    | ILIM  | Startup I <sub>LIM</sub> Value Set (optional at this point). |  |  |

| 2    | CLASS | Classification Resistor.                                     |  |  |

| 3    | DET   | 26.1kΩ Detection Resistor.                                   |  |  |

| 4    | VSS   | Negative Power Supply Terminal.                              |  |  |

| 5    | RTN   | Powered Device Negative Power Terminal.                      |  |  |

| 6    | PG    | Power Good Indicator.                                        |  |  |

| 7    | NC    | No Connect. Possible post-package trim input.                |  |  |

| 8    | VDD   | Positive Power Supply Terminal.                              |  |  |

# **OPERATION**

The MP8001/MP8001A operate in the manner described here and in the IEEE 802.3af Powered Device (PD) Specifications. These devices (along with the power sourcing element (PSE)) operate as a safety device to supply potentially lethal voltages only when the power sourcing element recognizes a unique, tightly specified resistance at the end of an unknown length of Ethernet cable.

A 26.1k $\Omega$  resistance is presented as a load to the PSE in Detection Mode, when the PSE applies two "safe" voltages of less than 10.1V each while measuring the change in current drawn in order to determine the load resistance. If the PSE "sees" the correct load, then it may either further increase the applied voltage to enter the "classification" range of operation or switch on the nominal 48V power to the load.

The classification mode can further specify to the PSE the expected load range of the device under power so that the PSE can intelligently distribute power to as many loads as possible (within its maximum current capabilities). If a classification resistance is not present, the PD load is assumed to be the maximum of approximately 13 Watts. The classification mode is active between 14.5V and 20.5V.

The main power switch will pass a limited current above 31V, charging the external DC-to-DC converter's input capacitor in a controlled manner. The charging will continue until the controlled current drops below the either an externally programmed limiting level or 420mA/810mA, depending upon the Rlim current setting resistor. The main power switch is internally thermally protected to 135°C by reducing the output current using a foldback technique. The required power dissipation of the IC drops from the allowed peak value of 24W (420mA x 57V) to 0.18W  $((420mA)^2 \times R_{ON})$ during the normal operation at turn-on. The minimum allowed capacitance of 5µF will charge in 500µs. A larger capacitor will take a proportionally longer time to charge due to the constant current charging method. If a capacitor that is too large will overheat the part and force it into thermal shutdown. The IC will reattempt charging for a number of cycles but ultimately will be shut down until the input voltage from the PSE is recycled. This is the way the IC protects itself under overload and/or shorted conditions.

6/8/2017

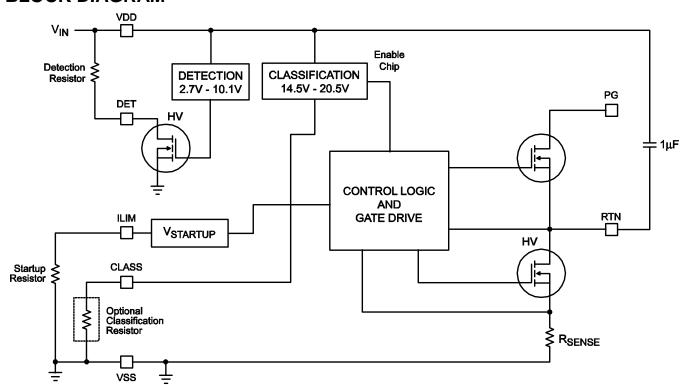

# **BLOCK DIAGRAM**

Figure 1—PD Block Diagram

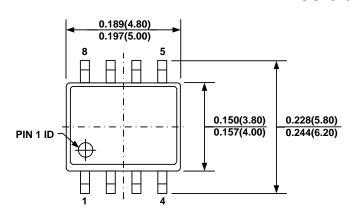

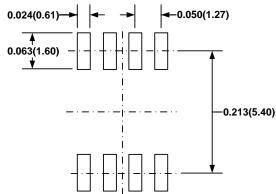

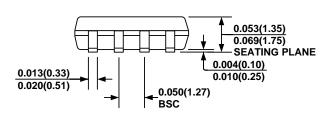

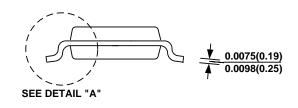

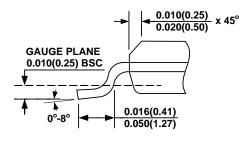

# **PACKAGE INFORMATION**

## SOIC-8

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.