# INTEGRATED CHARGE CONTROLLER FOR LEAD-ACID BATTERIES

Check for Samples: bq24450

#### **FEATURES**

- Regulates Both Voltage and Current During Charging

- Precision Temperature-Compensated Reference:

- Maximizes Battery Capacity Over Temperature

- Ensures Safety While Charging Over Temperature

- Optimum Control to Maximize Battery Capacity and Life

- Supports Different Configurations

- Minimum External Components

- Available in 16-Pin SOIC (DW)

## **APPLICATIONS**

- · Emergency Lighting Systems

- Security and Alarm Systems

- Telecommunication Backup Power

- Uninterruptible Power Supplies

# **DESCRIPTION**

The bq24450 contains all the necessary circuitry to optimally control the charging of valve-regulated lead-acid batteries. The IC controls the charging current as well as the charging voltage to safely and efficiently charge the battery, maximizing battery capacity and life. Depending on the application, the IC can be configured as a simple constant-voltage float charge controller or a dual-voltage float-cum-boost charge controller.

The built-in precision voltage reference is especially temperature-compensated to track the characteristics of lead-acid cells, and maintains optimum charging voltage over an extended temperature range without using any external components. The ICs low current consumption allows for accurate temperature monitoring by minimizing self-heating effects.

The IC can support a wide range of battery capacities and charging currents, limited only by the selection of the external pass transistor. The versatile driver for the external pass transistor supports both NPN and PNP types and provides at least 25mA of base drive.

In addition to the voltage- and current-regulating amplifiers, the IC features comparators that monitor the charging voltage and current. These comparators feed into an internal state machine that sequences the charge cycle. Some of these comparator outputs are made available as status signals at external pins of the IC. These status and control pins can be connected to a processor, or they can be connected up in flexible ways for standalone applications.

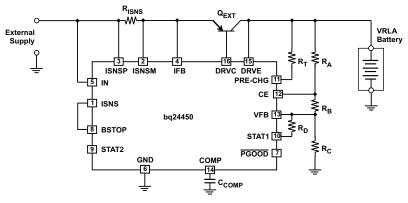

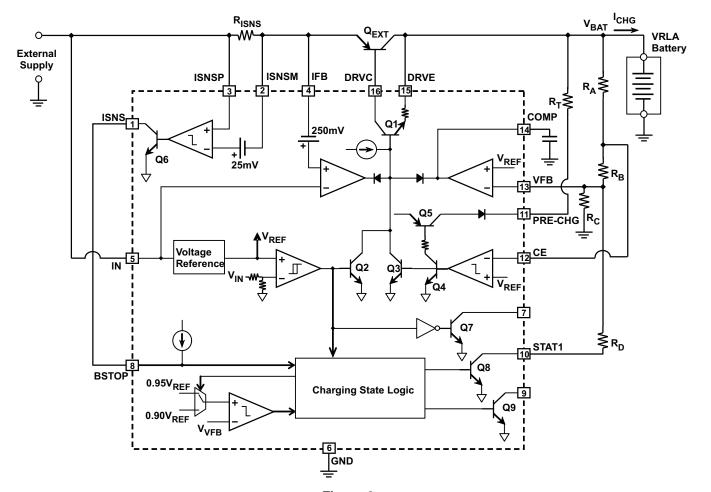

Figure 1. TYPICAL APPLICATION SCHEMATIC

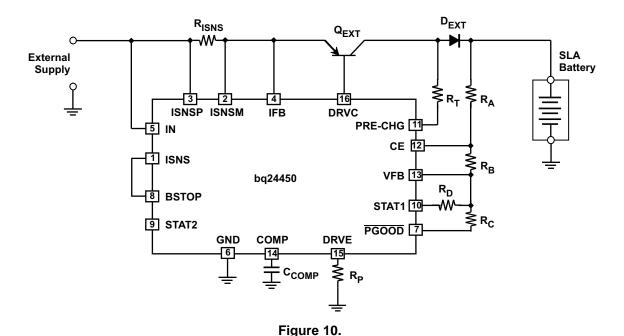

A dual-level Float-cum-Boost Charger with Pre-Charge

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**

| DEVICE PACKAGE | PACKING      | ORDERABLE PART NUMBER | MARKING  |

|----------------|--------------|-----------------------|----------|

| SOIC (D)       | Tube of 50   | bq24450D              | bq24450D |

| SOIC (D)       | Reel of 2500 | bq24450DR             | bq24450D |

# ABSOLUTE MAXIMUM RATINGS(1) (2) (3)

over operating free-air temperature range (unless otherwise noted)

|                                      |                                       | VALUE      | UNIT |

|--------------------------------------|---------------------------------------|------------|------|

|                                      | IN                                    | -0.3 to 40 | V    |

| Innest Valtage                       | PGOOD, STAT1, STAT2, ISNS             | -0.3 to 40 | V    |

| Input Voltage                        | VFB, IFB, ISNSP, ISNSM                | -0.3 to 40 | V    |

|                                      | BSTOP                                 | -0.3 to 40 | V    |

| Voltage                              | PRE-CHG (with respect to IN)          | -32        | V    |

| Input Current                        | ISNS                                  | 80         | mA   |

|                                      | STAT1, STAT2, PGOOD                   | 20         | mA   |

| Output Current                       | PRE-CHG                               | -40        | mA   |

| Input Current                        | DRVC                                  | 80         | mA   |

| Output Current                       | DRVE                                  | -80        | mA   |

| Power Dissipation a                  | at T <sub>A</sub> = 25°C              | 1000       | mW   |

| Junction temperature, T <sub>J</sub> |                                       | -40 to 150 | °C   |

| Storage temperatur                   | Storage temperature, T <sub>STG</sub> |            | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                                                              |                                                      | MIN | MAX | UNITS |

|--------------------------------------------------------------|------------------------------------------------------|-----|-----|-------|

| V <sub>IN</sub>                                              | IN voltage range                                     | 5   | 40  | V     |

| I <sub>STAT1</sub> , I <sub>STAT2</sub> , I <sub>PGOOD</sub> | Input current, open-collector status pins            |     | 5   | mA    |

| I <sub>ISNS</sub>                                            | Input current, open-collector ISNS comparator output |     | 25  | mA    |

| $T_J$                                                        | Junction Temperature                                 | -40 | 70  | °C    |

Submit Documentation Feedback

<sup>(2)</sup> All voltage values are with respect to the ground terminal (pin 6) unless otherwise noted.

<sup>(3)</sup> Positive currents are into, and negative currents out of, the specified terminal.

# **ELECTRICAL CHARACTERISTICS**

Over junction temperature range  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 70^{\circ}\text{C}$ ,  $\text{V}_{\text{IN}} = 10\text{V}$ ,  $\text{T}_{\text{J}} = \text{T}_{\text{A}}$ . (Positive currents are into, and negative currents out of, the specified terminal)

|                                        | PARAMETER                                                        | TEST CONDITIONS                                                                                  | MIN   | TYP   | MAX      | UNIT   |

|----------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|-------|----------|--------|

| INPUT                                  |                                                                  |                                                                                                  |       |       |          |        |

| UVLO                                   | Input power detected threshold                                   | V <sub>IN</sub> increasing from 0V to 5V                                                         | 4.2   | 4.5   | 4.8      | V      |

| V <sub>HYS-UVLO</sub>                  | Hysteresis on UVLO                                               | V <sub>IN</sub> decreasing from 5V to 0V                                                         |       | 200   | 300      | mV     |

| 1113-0120                              | .,,                                                              | V <sub>IN</sub> = 10V                                                                            |       | 1.6   | 3.3      |        |

| I <sub>IN</sub>                        | Operating current                                                | V <sub>IN</sub> = 40V                                                                            |       | 1.8   | 3.6      | mA     |

| -IIN                                   | Speciality of the second                                         | $V_{IN} = 40V$ , $T_A = -40^{\circ}C$ to 85°C                                                    |       | 1.8   | 4        |        |

| INTERNAL R                             | EFERENCE (V <sub>REF</sub> )                                     | 1IN 1017 A 10 0 10 0                                                                             |       |       |          |        |

| V <sub>REF</sub>                       | Reference voltage level                                          | Measured as regulating level on VFB pin when device is in FLOAT mode. $T_J = 25^{\circ}\text{C}$ | 2.275 | 2.300 | 2.325    | V      |

| dV <sub>REF</sub> /dT                  | Temperature coefficient of V <sub>REF</sub>                      |                                                                                                  |       | -3.5  |          | mV/°C  |

| $\Delta V_{REF}$                       | Line regulation of VREF                                          | V <sub>IN</sub> = 5V to 40V                                                                      |       | 3     | 8        | mV     |

| VOLTAGE AN                             | MPLIFIER                                                         |                                                                                                  |       |       | <u> </u> |        |

| I <sub>VFB</sub>                       | Input bias current                                               | V <sub>VFB</sub> = 2.30V                                                                         | -500  | -200  |          | nA     |

| A <sub>OV</sub>                        | Open-loop gain                                                   | Driver current = 1mA                                                                             | 50    | 65    |          | dB     |

| V <sub>O</sub>                         | Output voltage swing (above GND or below V <sub>IN</sub> )       |                                                                                                  |       | 200   |          | mV     |

|                                        | MIT AMPLIFIER                                                    | 1                                                                                                | I.    |       |          |        |

| I <sub>IFB</sub>                       | Input bias current                                               |                                                                                                  |       | 0.2   | 1        | μA     |

| V <sub>ILIM</sub>                      | Threshold voltage (wrt V <sub>IN</sub> )                         |                                                                                                  | 225   | 250   | 275      | mV     |

| ΔV <sub>ILIM</sub>                     | Sensitivity of V <sub>ILIM</sub> to V <sub>IN</sub>              | V <sub>IN</sub> = 5V to 40V                                                                      |       | 0.03  | 0.25     | %/V    |

| DRIVER TRA                             |                                                                  |                                                                                                  |       |       |          |        |

| V <sub>CE</sub>                        | Minimum collector to emitter differential                        | $V_{DRVC} = V_{IN}$ , $I_{DRVE} = 10mA$                                                          |       | 2     | 2.2      | V      |

| I <sub>DRVE-MAX</sub>                  | Maximum output current                                           | $V_{DRVC} - V_{DRVE} = 2 \text{ V}$                                                              | 25    | 40    |          | mA     |

| PRE-CHG                                |                                                                  | DIAVO DIAVE                                                                                      |       |       |          |        |

| I <sub>PRE</sub>                       | Maximum output current VPRE = VIN - 3V                           |                                                                                                  | -40   | -25   |          | mA     |

| V <sub>PRE</sub>                       | Maximum output voltage (V <sub>IN</sub> – V <sub>PRE-CHG</sub> ) | I <sub>PRE</sub> = -10mA                                                                         |       | 2     | 2.6      | V      |

| V <sub>PRE-REV</sub>                   | PRE-CHG reverse hold-off voltage                                 | $V_{IN} = 0 \text{ V, } I_{PRE} = -10 \mu\text{A}$                                               |       | 6.3   | 7        | V      |

| ENABLE COM                             |                                                                  | IN - / FIXE -F                                                                                   |       |       |          |        |

| V <sub>TH-CE</sub>                     | Threshold voltage (x V <sub>RFF</sub> )                          |                                                                                                  | 0.99  | 1.00  | 1.01     | V/V    |

| I <sub>CE</sub>                        | Input bias current                                               |                                                                                                  | -500  | -200  |          | nA     |

|                                        | ENSE COMPARATOR                                                  |                                                                                                  |       |       |          |        |

| I <sub>IB-ISNS</sub>                   | Input bias current                                               |                                                                                                  |       | 100   | 500      | nA     |

| I <sub>OS-ISNS</sub>                   | Input offset current                                             |                                                                                                  |       | 10    | 200      | nA     |

| V <sub>ISNS</sub>                      | Threshold voltage (V <sub>ISNSP</sub> – V <sub>ISNSM</sub> )     |                                                                                                  | 20    | 25    | 30       | mV     |

| $\Delta V_{ISNS}/\Delta V_{IN}$        | Threshold sensitivity to V <sub>IN</sub>                         | V <sub>IN</sub> = 5V to 40V                                                                      | 20    | 0.05  | 0.35     | %/V    |

| $\Delta V_{\rm ISNS}/\Delta_{\rm VCM}$ |                                                                  | $V_{CM} = 2V \text{ to VIN}$                                                                     |       | 0.05  | 0.35     | %/V    |

|                                        | Maximum sink current, ISNS pin                                   | V <sub>ISNS</sub> = 2 V                                                                          |       | 25    | 40       | mA     |

| V                                      | Saturation voltage, ISNS pin                                     | I <sub>ISNS</sub> = 10 mA                                                                        |       | 200   | 450      | mV     |

| VOLTAGE SE                             | ENSE COMPARATOR                                                  | 15NS = 10 H/V                                                                                    |       | 200   | 730      | 1117   |

| VOLTAGE 3E                             | INSE COMPARATOR                                                  | L1 = RESET                                                                                       | 0.94  | 0.95  | 0.96     |        |

| $V_{VSNS}$                             | Threshold voltage (x V <sub>REF</sub> )                          | L1 = SET                                                                                         | 0.895 | 0.90  | 0.910    |        |

| INPLIT I OGIC                          | C LEVELS – BSTOP                                                 | LI = SLI                                                                                         | 0.093 | 0.90  | 0.910    |        |

| V <sub>TH-BS</sub>                     | Threshold voltage                                                |                                                                                                  | 0.7   | 1     | 1.3      | V      |

|                                        | Internal pull-up current                                         | $V_{BSTOP} = V_{TH-BS}$                                                                          | 0.7   | 10    | 1.0      | μA     |

| I <sub>PU-BS</sub>                     | GIC LEVELS – STAT1, STAT2, PGOOD                                 | *R210b = *IH-R2                                                                                  |       | 10    |          | μΛ     |

|                                        | Maximum sink current                                             | V <sub>PIN</sub> = 2V, output transistor ON                                                      | 2.5   | 5     |          | mA     |

| I <sub>SINK-MAX</sub>                  | MAXIIII SIIIK CUITCIII                                           | $V_{PIN} = 2V$ , output transistor ON $I_{SINK} = 1.6 \text{ mA}$                                | 2.5   | 250   | 450      | mV     |

| $V_{SAT}$                              | Output saturation voltage                                        |                                                                                                  |       |       |          |        |

|                                        | Lookago gurront                                                  | I <sub>SINK</sub> = 50 µA                                                                        |       | 30    | 50       | mV<br> |

| l <sub>lkg</sub>                       | Leakage current                                                  | $V_{PIN} = 40V$ , output transistor OFF                                                          | 1     | 1     | 3        | μΑ     |

Submit Documentation Feedback

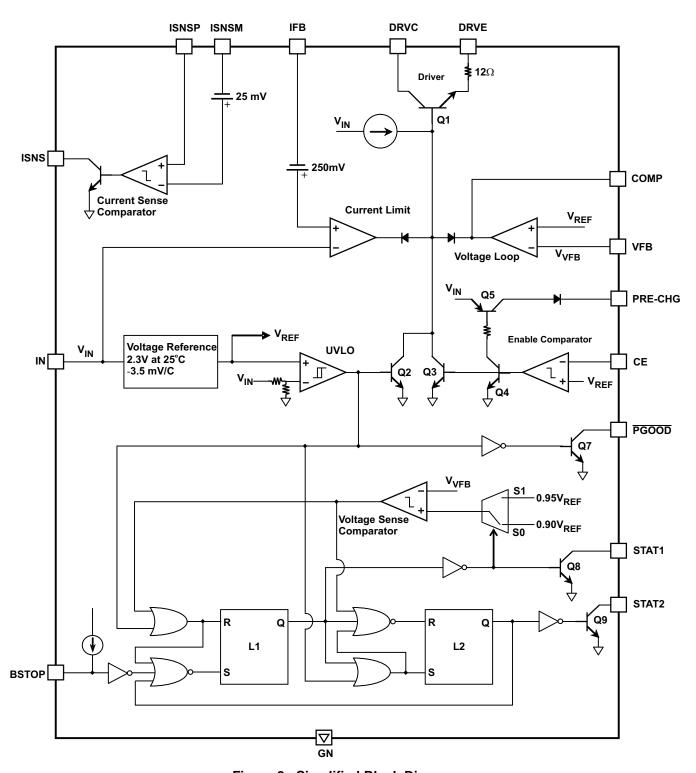

Figure 2. Simplified Block Diagram

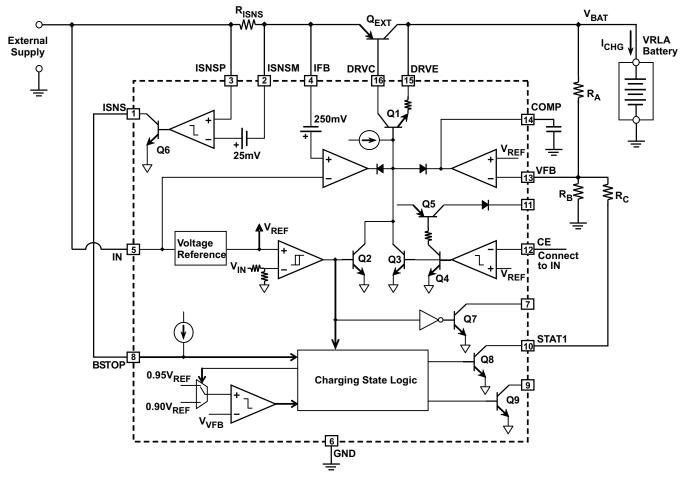

# **PIN FUNCTIONS**

|     | PIN     | 1/0 | DESCRIPTION                                                                                                                                                                                                                            |

|-----|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME    | 1/0 | DESCRIPTION                                                                                                                                                                                                                            |

| 1   | ISNS    | 0   | Output of the current-sense comparator. Open-Collector.                                                                                                                                                                                |

| 2   | ISNSM   | ı   | Negative input of the current-sense comparator.                                                                                                                                                                                        |

| 3   | ISNSP   | _   | Positive input of the current-sense comparator.                                                                                                                                                                                        |

| 4   | IFB     | I   | Input for the current-regulating loop. External resistor between IN and IFB sets the charging current value.                                                                                                                           |

| 5   | IN      | ı   | Supply voltage pin. Connect to external DC source.                                                                                                                                                                                     |

| 6   | GND     | 1   | Ground terminal.                                                                                                                                                                                                                       |

| 7   | PGOOD   | 0   | Open-collector output, indicates supply status at IN pin. Active low.                                                                                                                                                                  |

| 8   | BSTOP   | I   | Control input. Taking this pin from low to high transitions the charger from Boost Mode to Float Mode. Internally pulled up through a 10µA current source.                                                                             |

| 9   | STAT2   | 0   | Ones collector status sutnuts. See table below                                                                                                                                                                                         |

| 10  | STAT1   | 0   | Open-collector status outputs. See table below.                                                                                                                                                                                        |

| 11  | PRE-CHG | 0   | Can be used to trickle-charge the battery till its voltage rises to a safe value. PRE-CHG will source current as long as the control voltage on the CE pin is below VREF. If using, connect to battery pack through external resistor. |

| 12  | CE      | I   | Charge enable control. If the voltage on the CE pin is below VREF, the driver transistor will be off and the PRE-CHG pin will source current.                                                                                          |

| 13  | VFB     | ı   | Voltage feedback pin. Connect to battery through external resistive divider.                                                                                                                                                           |

| 14  | COMP    | I/O | Compensation terminal for voltage loop. Connect a capacitor from this pin to GND.                                                                                                                                                      |

| 15  | DRVE    | 0   | Emitter of the internal (NPN) driver transistor.                                                                                                                                                                                       |

| 16  | DRVC    | I   | Collector of the internal (NPN) driver transistor.                                                                                                                                                                                     |

# **PINOUT**

| STAT1 | STAT2 | CONDITION  |  |  |

|-------|-------|------------|--|--|

| Hi-Z  | Hi-Z  | Float Mode |  |  |

| STAT1 | STAT2 | CONDITION   |

|-------|-------|-------------|

| On    | Hi-Z  | Bulk Charge |

| On    | On    | Boost Mode  |

# **TYPICAL OPERATING PERFORMANCE**

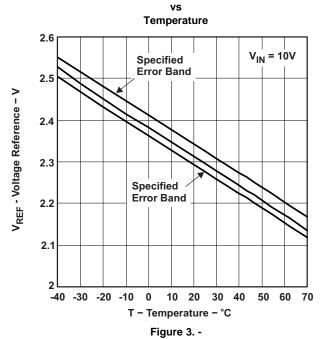

**Compensated Voltage Reference**

#### DETAILED FUNCTIONAL DESCRIPTION

The bq24450 contains all the necessary circuitry to optimally control the charging of sealed lead-acid batteries. The IC controls the charging current as well as the charging voltage to safely and efficiently charge the battery, maximizing battery capacity and life. Depending on the application, the IC can be configured in various ways: examples are a constant-voltage float charger, a dual-voltage float-cum-boost charger or a dual step current charger.

Only an external pass transistor and minimum number of external passive components are required along with the IC to implement a charger for sealed lead-acid batteries. The IC's internal driver transistor Q1 (see Figure 2) supports NPN as well as PNP pass transistors, and provides enough drive current (25mA specified) to support a wide range of charging rates.

The driver transistor is controlled by a voltage regulating loop and a current limiting-limiting loop (see Figure 2). The current-limiting loop reduces drive when the voltage between the IN pin and the IFB pin increases towards  $V_{ILIM}$  (250mV typical). The voltage regulating loop tries to maintain the voltage on the VFB pin at  $V_{REF}$ . Together, these two loops constitute a current-limited precision constant-voltage system, which is the heart of any lead-acid charger. The voltage regulating amplifier needs an external compensation circuit which depends on the type of external pass transistor (see Application Information section).

An important feature of the bq24450 is the precision reference voltage. The reference voltage is specially temperature compensated to track the temperature characteristics of lead-acid cells. Additionally, the IC operates with low supply current, only 1.6mA, minimizing on-chip dissipation and permitting the accurate sensing of the operating environmental temperature by avoiding self-heating effects. To take full advantage of the temperature-compensated reference, the IC should be in the same thermal environment as the battery.

An undervoltage lock-out circuit is also provided (see Figure 2). This circuit disables the driver transistor as long as the input voltage is below UVLO (4.5V typical). The UVLO circuit also drives an open-collector output PGOOD.

Voltage-sense and current-sense comparators are available in the IC. The current-sense comparator is uncommitted. Its open-collector output is OFF when the difference between the ISNSP and ISNSM pins is less than  $V_{\rm ISNS}$  (25mV typical), and ON when the difference is more than  $V_{\rm ISNS}$ . Depending on the application, this comparator may be used to switch to float charging after the boost phase is over. The voltage sense comparator can be used to sense the voltage level of the battery to initiate a new charge cycle.

Latches L1 and L2 constitute a state-machine to control the charging sequence. The internal inputs to the state-machine come from the UVLO circuit and the voltage-sense comparator. One external input is provided, the BSTOP pin. The outputs of the L1 and L2 latches are available at the STAT1 and STAT2 pins. The BSTOP pin is internally pulled up through a 10µA current source. The states of the state-machine are:

| Q(L1) | Q(L2) | STAT1 STAT2 |     | STAT1 STAT2 Condition |         |

|-------|-------|-------------|-----|-----------------------|---------|

| LOW   | HIGH  | ON          | OFF | Bulk Charge           | State 1 |

| LOW   | LOW   | ON          | ON  | Boost Mode            | State 2 |

| HIGH  | HIGH  | OFF         | OFF | Float Mode            | State 3 |

A small bias current source is available at the PRE-CHG pin to provide pre-charge to deeply discharged batteries. The PRE-CHG pin sources current when the voltage at the CE pin is below VREF. Driver transistor Q1 is turned OFF when the PRE-CHG current is ON.

Submit Documentation Feedback

#### **DETAILED OPERATION AND APPLICATION INFORMATION**

## A Simple Dual-Level Float-Cum-Boost Charger

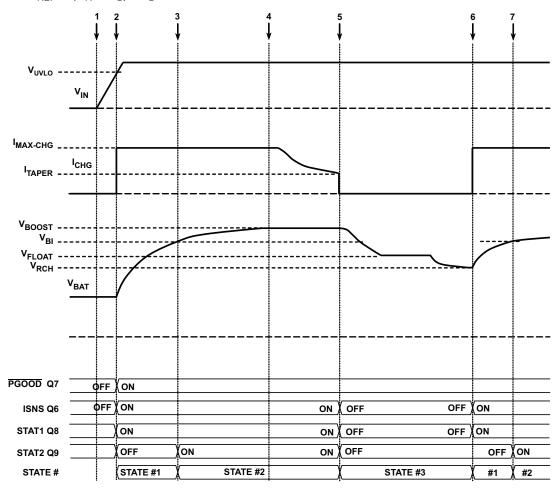

Figure 4 shows the bq24450 configured as a simple dual-level float-cum-boost charger. Figure 5 shows the sequence of events that occur in a normal charge cycle. At (1) in Figure 5, power is switched ON. As long as the input voltage  $V_{IN}$  is below the undervoltage lockout threshold UVLO, Q2 is ON, disabling the driver transistor Q1. As the input voltage  $V_{IN}$  ramps up and rises above UVLO Q2 turns OFF. This enables Q1 and thus the external transistor  $Q_{EXT}$ . At the same time, Q7 turns ON, latch L1 is forced to RESET and latch L2 is SET (see Figure 2 for the internals of the Charging State Logic).

The voltage regulating amplifier tries to force the voltage at the VFB pin to  $V_{REF}$  by turning Q1 and thus  $Q_{EXT}$  fully ON, but the current limiting amplifier limits the charging current  $I_{CHG}$  to  $I_{MAX-CHG}$  such that the voltage across  $R_{ISNS}$  is  $V_{ILIM} - 250$ mV typical. Thus  $I_{MAX-CHG}$  is given by:

$$I_{MAX-CHG} = V_{ILIM} \div R_{ISNS}$$

As  $I_{CHG}$  flows into the battery, the battery terminal voltage increases. The voltage at the VFB pin is the battery voltage scaled by the resistive divider formed by  $R_A$  and  $R_B//R_C$  (because Q8 is ON). At (3), the voltage on the VFB pin exceeds  $0.95V_{REF}$ , and the output of the voltage sense comparator goes HIGH. This forces L2 to RESET, and STAT2 turns ON. The battery voltage  $V_{BI}$  at this point when STAT2 indicates boost is given by:

$$V_{BI} = 0.95 V_{REF} \times (R_A + R_B // R_C) \div R_B // R_C$$

Other than STAT2 changing state at this point, there is no externally observable change in the charging conditions.  $I_{MAX-CHG}$  continues to flow into the battery.

Figure 4.

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

As charging proceeds, the voltage at the VFB pin increases further to  $V_{REF}$ . At this point, the voltage regulating amplifier prevents the voltage at the VFB pin from rising further, maintaining the battery voltage at  $V_{BOOST}$ . [(4) in Figure 4].

$$V_{BOOST} = V_{REF} \times (R_A + R_B//R_C) \div R_B//R_C$$

$I_{CHG}$  keeps flowing into the battery. As the battery approaches full charge, the current into the battery decreases, while the battery terminal voltage is maintained at  $V_{BOOST}$ .

At (5), the charging current  $I_{CHG}$  reduces to a value  $I_{TAPER}$  such that the voltage across  $R_{ISNS}$  becomes less than  $V_{ISNS}$  (25mV typical)

$$I_{TAPER} = V_{ISNS} \div R_{ISNS}$$

Q6 at the output of the current sense comparator turns OFF. The internal current source pulls the BSTOP pin HIGH, latch L1 is forced to SET, in turn forcing L2 to SET. The reference voltage on the voltage sense comparator is now  $0.9V_{REF}$ . STAT1 turns OFF, and the voltage on the battery settles to:

$$V_{FLOAT} = V_{REF} \times (R_A + R_B) \div R_B$$

As long as the peak load current is less than  $I_{MAX-CHG}$ , it will be supplied by  $Q_{EXT}$ , and the voltage across the battery will be maintained at  $V_{FLOAT}$ . But if the peak load current exceeds  $I_{MAX-CHG}$ , the battery will have to provide the excess current, and the battery terminal voltage will drop. Once it drops below  $0.9V_{REF}$ , at (6) in Figure 4, a new charge cycle is initiated. The battery voltage  $V_{BAT}$  at this point,  $V_{RCH}$ , is given by:

$$V_{RCH} = 0.9V_{REF} \times (R_A + R_B) / R_B$$

Figure 5.

Product Folder Link(s): bq24450

# An Improved Dual-Level Float-Cum-Boost Charger with Pre-Charge

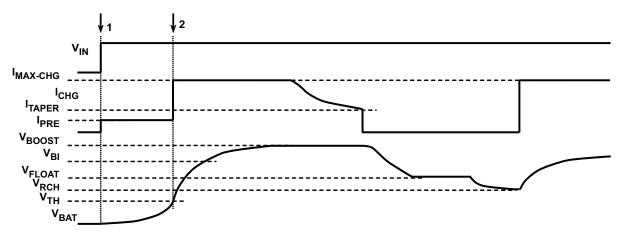

The problem with the charger circuit shown in Figure 4 is that even with deeply discharged batteries, charging starts at full current level  $I_{MAX-CHG}$ . This can sometimes be hazardous, resulting in out-gassing from the battery. The bq24450 can be configured to pre-charge the battery till the voltage levels rise to levels safe enough to permit charging at  $I_{MAX-CHG}$ .

In the circuit of Figure 6, the CE pin is used to detect the battery voltage. As long as the voltage at the CE pin is below  $V_{REF}$ , the enable comparator turns ON Q3 and Q4. This turns OFF Q1 and turns ON Q5, permitting a pre-charge current  $I_{PRE}$  to flow from the PRE-CHG pin through  $R_{T}$  into the battery. In the following equation,  $V_{PRE}$  is the voltage drop across the internal transistor, Q5, and the internal diode.

$$I_{PRE} = (V_{IN} - V_{PRE} - V_{BAT}) \div R_T$$

Once the battery voltage rises above a safe threshold  $V_{TH}$  at (2) in Figure 7, the enable comparator turns OFF Q3 and Q4, thus turning OFF Q5 and enabling Q1.  $Q_{EXT}$  then provides  $I_{MAX-CHG}$ , and the circuit after this performs as described before.

$$V_{TH} = V_{REF} \times (R_A + R_B + R_C / / R_D) \div (R_B + R_C / / R_D)$$

Figure 6.

Figure 7.

# Further Improvements to the Circuit of Figure 6

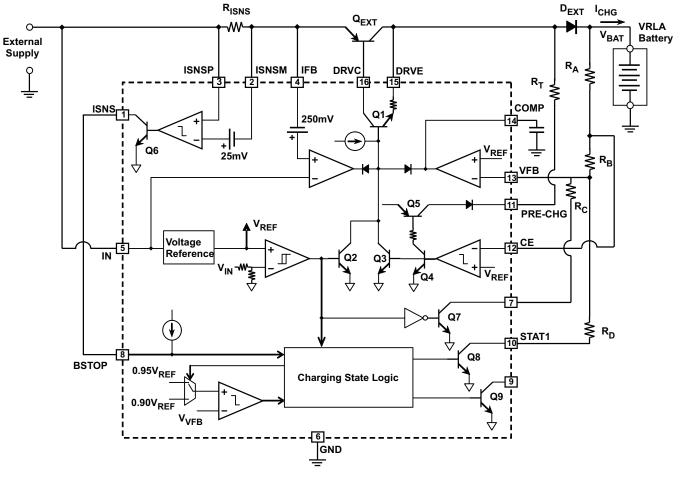

In applications where the load current is low, the current through the  $V_{BAT}$  voltage divider can be a non-negligible proportion of the load current. Current flowing back thorough  $Q_{EXT}$  when the input power is removed constitutes another drainage path. The modifications in Figure 8 fix both these issues.

The addition of  $D_{EXT}$  (see Figure 8) fixes the reverse current problem. Returning the voltage feedback divider chain to the PGOOD pin instead of to GND ensures that the divider does not draw any current when the input supply is not present. (When sinking  $50\mu A$ , the saturation voltage of the PGOOD transistor is typically only 30mV).

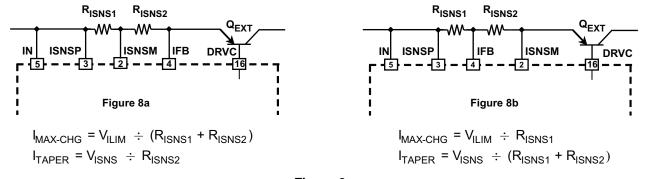

Figure 8.

# Changing the value of $I_{TAPER}$ for a given $I_{MAX-CHG}$

In the examples above,  $I_{TAPER}$  is 10% of  $I_{MAX-CHG}$ , because  $V_{ILIM}$  is 250mV and  $V_{ISNS}$  is 25mV (typical values), and the same resistor is used for both, the taper comparator and the current-loop amplifier. In most applications, setting  $I_{TAPER}$  to 10% of  $I_{MAX-CHG}$  is perfectly fine. But if, for some reason, a different value of  $I_{TAPER}$  is required, it can be achieved, as shown in Figure 9(a) and Figure 9(b).

Figure 9.

## Selecting the External Pass Transistor

All the examples so far have used a PNP transistor for the external pass element. But the driver transistor in the bq24450 can be configured to drive many different types of pass transistors. This section will look at some of the different configurations that are possible. In all configurations, though, these factors hold:

- 1. The external pass device must have sufficient voltage rating for the application, and must have the current and power handling capabilities to charge at the desired rate at the maximum input to output differential in the application.

- 2. The device must have enough current gain at the required charging current to keep the drive current below

The choice of the pass device and the configuration of the internal driver transistor have an effect on the following:

- 1. The minimum and maximum practical charging current.

- 2. The open-loop gains of the current and voltage loops, and hence the value of the compensation capacitor at the COMP pin. In battery charging applications, dynamic response is not a requirement, and the values of C<sub>COMP</sub> given below should give stable operation under all conditions.

- 3. The IC's power dissipation and thus its self-heating. The IC typically has a thermal resistance of 100°C/W. An external resistance R<sub>P</sub> can be added to share some of the power dissipation and reduce the IC's self-heating.

- 4. The minimum differential voltage  $\Delta V$  (from the input to the battery) required to operate.

The next section addresses a few topologies, and gives values for the charge current range, the minimum input to output differential  $\Delta V$ , power dissipation  $P_D$  in the IC,  $R_P$  and  $C_{COMP}$  for each of the topologies. (In the expressions below, h<sub>FE</sub> is the current gain of the external transistor).

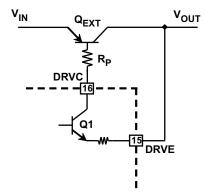

## **Common-Emitter PNP**

I<sub>MAX-CHG</sub> range: 25mA to 1000mA

Minimum ΔV:

$R_P = (V_{IN(MIN)} - 2.0V) \div I_{MAX-CHG} \times h_{FE(MIN)}$

$\begin{aligned} P_D &= \left( V_{IN(MAX)} - 0.7 V \right) \div \overset{\text{i.i.o.}}{h_{FE}} \times \overset{\text{i.i.o.}}{I_{MAX-CHG}} - \left( I_{MAX-CHG} \right)^2 \div (h_{FE})^2 \times R_P \\ C_{COMP} &= 0.1 \ \mu F \end{aligned}$

V<sub>OUT</sub>  $Q_{EXT}$ DRVC Q1 **I** DRVE

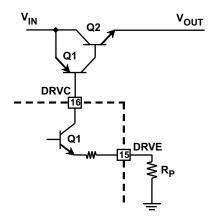

#### PNP in a Quasi-Darlington With Internal Driver

25mA to 1000mA I<sub>MAX-CHG</sub> range:

Minimum ΔV:

$R_P = (V_{IN(MIN)} - V_{OUT(MAX)} - 1.2 \text{ V}) \div I_{MAX\text{-}CHG} \times h_{FE(MIN)}$   $P_D = (V_{IN(MAX)} - V_{OUT} - 0.7 \text{V}) \div h_{FE} \times I_{MAX\text{-}CHG} - (I_{MAX\text{-}CHG})^2 \div (h_{FE})^2 \times R_P$   $C_{COMP} = 0.01 \mu F$  to  $0.047 \mu F$

#### **External Quasi-Darlington**

$I_{MAX-CHG}$  range: 0.6A to 15A

Minimum ΔV:

$R_P = (V_{IN(MIN)} - 0.7 \text{ V}) \div I_{MAX\text{-}CHG} \times h_{FE1(MIN)} h_{FE2(MIN)} \\ P_D = (V_{IN(MAX)} - 0.7 \text{ V}) \div (h_{FE1} \times h_{FE2}) \times I_{MAX\text{-}CHG} - (I_{MAX\text{-}CHG})^2 \div (h_{FE1} \times h_{FE2})^2 \times R_P \\ C_{COMP} = 0.22 \mu F \text{ with } 470 \Omega \text{ series resistor to GND}$

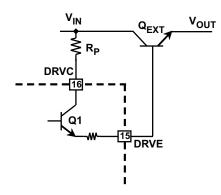

#### **NPN Emitter-Follower**

I<sub>MAX-CHG</sub> range: 25mA to 1000mA

Minimum ΔV: 2.7V

$$\begin{split} R_P &= \left(V_{IN(MIN)} - V_{OUT(MAX)} - 1.2 \text{ V}\right) \div I_{MAX\text{-}CHG} \times h_{FE(MIN)} \\ P_D &= \left(V_{IN(MAX)} - V_{OUT} - 0.7 \text{ V}\right) \div h_{FE} \times I_{MAX\text{-}CHG} - \left(I_{MAX\text{-}CHG}\right)^2 \div \left(h_{FE}\right)^2 \times R_P \end{split}$$

$C_{COMP} = 0.01 \mu F$  to  $0.047 \mu F$

#### **DESIGN EXAMPLE**

This section covers the design of a dual-level charger for a 6V 4Ah sealed lead-acid battery. The application is a system where the battery is used in standby mode, and the load on the battery when it powers the system is 250mA (0.06C).

The battery parameters are (see References 1 and 2)

Final discharge voltage 1.75V per cell 5.25V Float voltage 2.30V per cell 6.9V  $V_{FLOAT}$ Voltage in boost mode 2.45V per cell 7.35V  $V_{ROOST}$ Charge rate 0.05C to 0.3C Use 0.15C = 600 mAI<sub>MAX-CHG</sub>

4V  $V_{BAT(MIN)}$ Trickle charge rate 10 mA

The charger is required to operate from a supply voltage of 9V to 13V. Therefore, the minimum input to output differential is 1.65V. To block reverse current from the battery to the input supply use a blocking diode as in Figure 8. This leaves only 0.65V as the differential across the external transistor, forcing the use of the Common-Emitter PNP topology.

Figure 10 is the schematic for this charger (from Figure 8, with the pass transistor topology changed), with the remaining task being the calculation of all the component values.

Submit Documentation Feedback

Copyright © 2009-2012, Texas Instruments Incorporated

The first step is to decide on the value of the current in the voltage divider resistor string in FLOAT mode. This should be substantially higher than the input bias current in the CE and VFB pins and the leakage current in the STAT1 pin, but low enough such that the voltage on the PGOOD pin does not introduce errors. A value of 50µA is suitable.

In FLOAT mode, STAT1 is OFF, so there is no current in R<sub>D</sub>. The voltage on the VFB pin (V<sub>RFF</sub>) is 2.3V.

$R_C = 2.30V \div 50\mu A = 46k\Omega$ . The closest 1% value is  $46.4k\Omega$ .

$V_{FLOAT} = V_{REF} \times (R_A + R_B + R_C) \div R_C \rightarrow R_A + R_B = 2 \times R_C = 92.8 \text{k}\Omega.$

$V_{BOOST} = V_{REF} \times (R_A + R_B + R_C /\!/ R_D) \div R_C /\!/ R_D \rightarrow R_D = 474.3 k\Omega$ . Pick the closest 1% value of 475k $\Omega$ .

$V_{TH} = V_{REF} \times (R_A + R_B + R_C / / R_D) \div (R_B + R_C / / R_D) \rightarrow R_B = 16.9 k\Omega.$

$R_A = 92.8k\Omega - R_B = 75.9k\Omega$ . The closest standard value is  $75k\Omega$ .

$I_{PRE} = (V_{IN} - V_{PRE} - V_{DEXT} - V_{BAT}) \div R_{T}$ . Select  $R_{T} = 634\Omega$ .

For example:  $I_{PRF} = (13 - 2 - 0.7 - 4) / 634 = 10 \text{ mA}$

$I_{MAX\text{-}CHG} = V_{ILIM} \div R_{ISNS} \rightarrow R_{ISNS} = 250 \text{mV} \div 600 \text{mA} = 0.417 \Omega. \text{ The closest 1\% value is } 0.422 \Omega.$

For  $Q_{EXT}$ , the BD242 is suitable, and a 1N4001 will do for  $D_{EXT}$

$R_P = (V_{IN(MIN)} - 2.0V) \div I_{MAX-CHG} \times h_{FF(MIN)} = 7 \div 0.6 \times 25 = 291.6\Omega$ . Pick 294 $\Omega$  from the standard values.

$P_D = (V_{IN(MAX)} - 0.7V) \div h_{FE} \times I_{MAX-CHG} - (I_{MAX-CHG})^2 \div (h_{FE})^2 \times R_P = 126 \text{mW}$  under worst case conditions.

Choose  $C_{COMP} = 0.1 \mu F$ .

### **REFERENCES**

- 1. Yuasa Battery Co., NP Valve Regulated Lead Acid Battery Manual

- 2. Panasonic, Methods of charging the Valve-Regulated Lead-Acid Battery

# **REVISION HISTORY**

NOTE: Page numbers of previous versions may differ from current version.

| С        | changes from Original (April 2009) to Revision A                                                                                          | Page |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Deleted PDIP package option from Features                                                                                                 |      |

| •        | Deleted PDIP package from Ordering Information table                                                                                      | 2    |

| •        | Changed equations to correct typo/formatting errors (3 equations)                                                                         | 8    |

| •        | Changed equations to correct typo/formatting errors                                                                                       | 9    |

| •        | Changed equation to correct typo/formatting errors                                                                                        | 10   |

| •        | Changed three equations to correct typo/formatting errors                                                                                 | 15   |

| •        | Changed component values in "Design Example" calculations.                                                                                | 15   |

| С        | changes from Revision A (January 2010) to Revision B                                                                                      | Page |

| •        | Added V <sub>PRE</sub> with definition                                                                                                    |      |

| <u>.</u> | Changed compenent values in the I <sub>PRE</sub> calculations                                                                             | 15   |

| С        | changes from Revision B (October 2010) to Revision C                                                                                      | Page |

| •        | Changed compenent values in the I <sub>PRE</sub> calculations in FLOAT mode description FROM "332" TO "5) /332 = 16mA" TO "4)/634 = 10mA" |      |

www.ti.com 16-Jul-2022

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| BQ24450DW        | ACTIVE     | SOIC         | DW                 | 16   | 40             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 70    | BQ24450DW               | Samples |

| BQ24450DWTR      | ACTIVE     | SOIC         | DW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 70    | BQ24450DW               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

www.ti.com

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

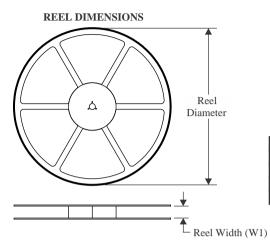

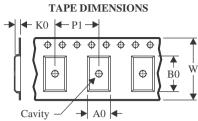

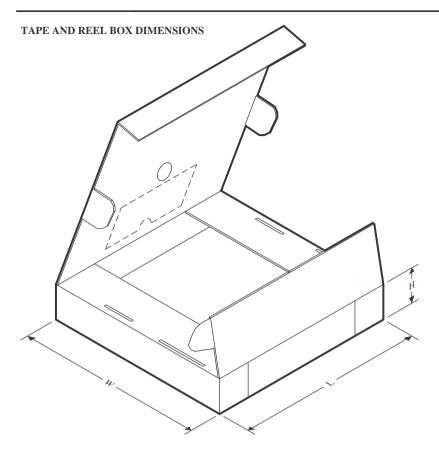

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

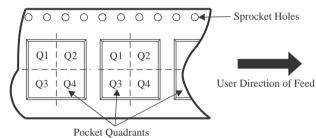

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | U    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| BQ24450DWTR | SOIC | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

## \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ24450DWTR | SOIC         | DW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

# **TUBE**

## \*All dimensions are nominal

| Device    | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-----------|--------------|--------------|------|-----|--------|--------|--------|--------|

| BQ24450DW | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

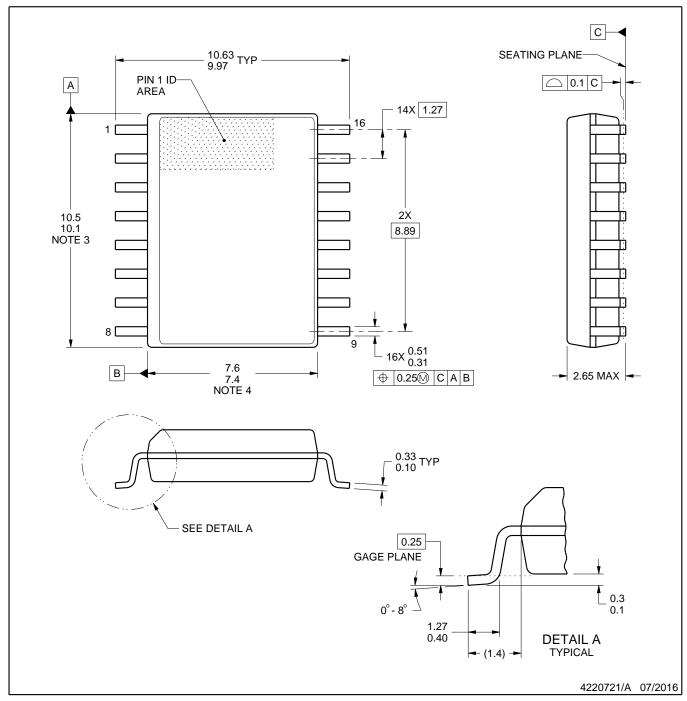

7.5 x 10.3, 1.27 mm pitch

SMALL OUTLINE INTEGRATED CIRCUIT

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

SOIC

### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing

- per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.

- 5. Reference JEDEC registration MS-013.

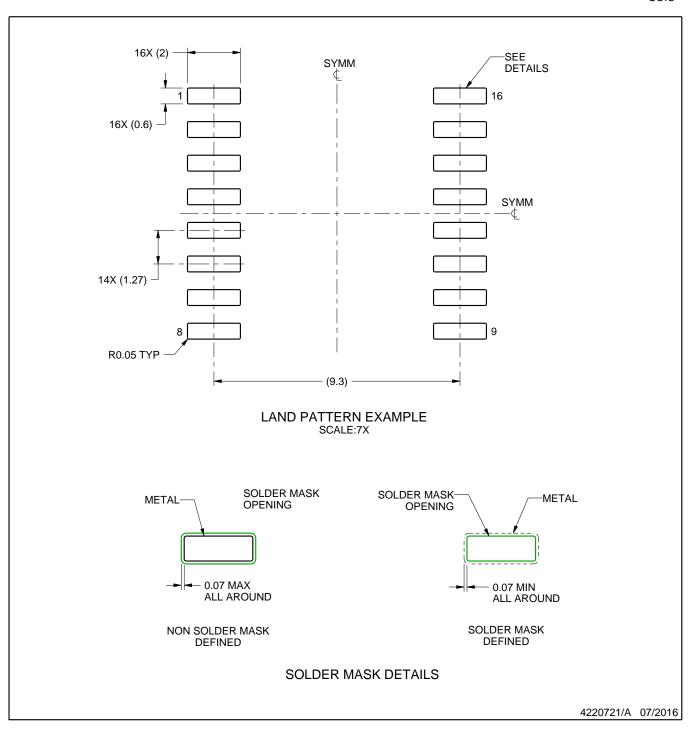

SOIC

## NOTES: (continued)

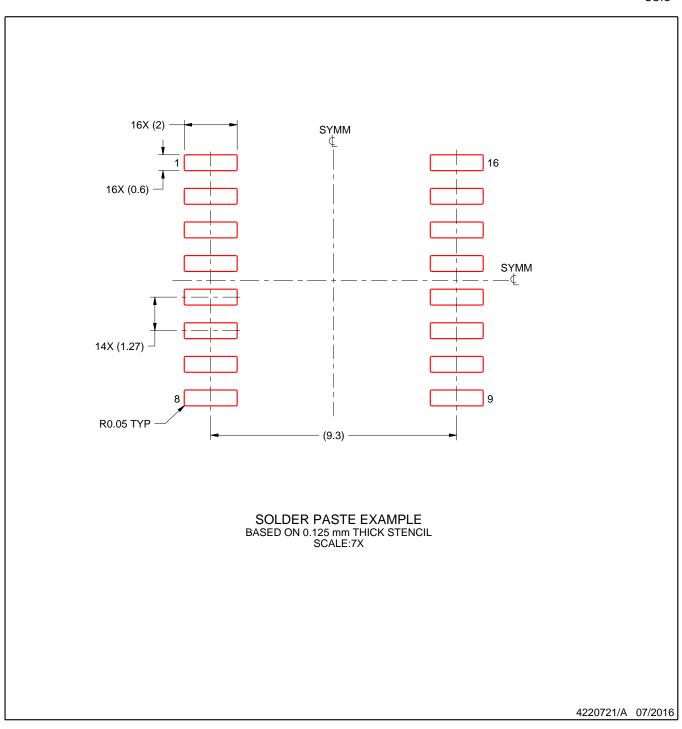

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SOIC

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated