## YT801. Datasheet

100BASE T2 PHY FOR AUTOMOTIVE ETHERNET

苏州裕太车通 | motor-comm

REV VO.1

#### **Revision History**

| 0.1  |                       |

|------|-----------------------|

| 0.12 | Draft                 |

| 1.0  | Update register table |

|      |                       |

|      |                       |

|      | sindulate             |

#### Table of Content

| 內容                                     |    |

|----------------------------------------|----|

| 1. General Description                 | 5  |

| TARGET APPLICATIONS                    | 5  |

| 2. Feature                             | 6  |

| 3 PIN assigment                        | 7  |

| YT8010 QFN36 6x6mm                     | 7  |

| Pin Descriptions                       |    |

| 4 Function Description                 |    |

| Application Diagram                    |    |

| 100Base-t1 application                 |    |

| MII interface                          | 11 |

| RMII interface                         | 11 |

| Management interface                   |    |

| DAC                                    |    |

| ADC                                    |    |

| Adaptive equalizer                     |    |

| Echo-canceller                         |    |

| Clock recovery                         |    |

| Link Monitor                           | 13 |

| Polarity detection and auto correction | 13 |

| 5 Operational Description              | 14 |

| Reset                                  | 14 |

| PF.Y Address                           | 14 |

| XMII interface                         | 14 |

| MII                                    | 14 |

| RMII                                   | 15 |

| RGMII                                  |    |

| REMII interface                        |    |

| SQI                                    |    |

|                                        |    |

|    |                                                         | 10 |

|----|---------------------------------------------------------|----|

|    | Loopback mode                                           |    |

|    | Internal loopback:                                      |    |

|    | External loopback                                       | 19 |

|    | Remote loopback                                         | 19 |

|    | Master-slave configuration                              | 20 |

|    | Interrupt                                               | 20 |

|    | Power saving                                            | 20 |

|    | Application notes about sleep mode                      | 21 |

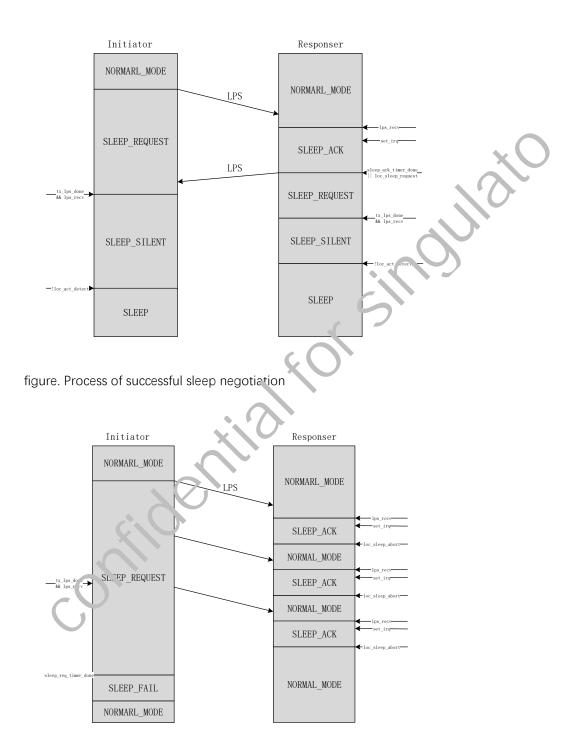

|    | Sleep negotiation process                               |    |

|    | Remote wakeup                                           |    |

| 6  | Register Overview                                       | 26 |

|    | MII Management Interface Clause 22 Register Programming | 26 |

|    | MII REGISTERS                                           | 26 |

| 7  | Timing and AC Characteristics                           | 49 |

| 8  | Power Requirements                                      | 50 |

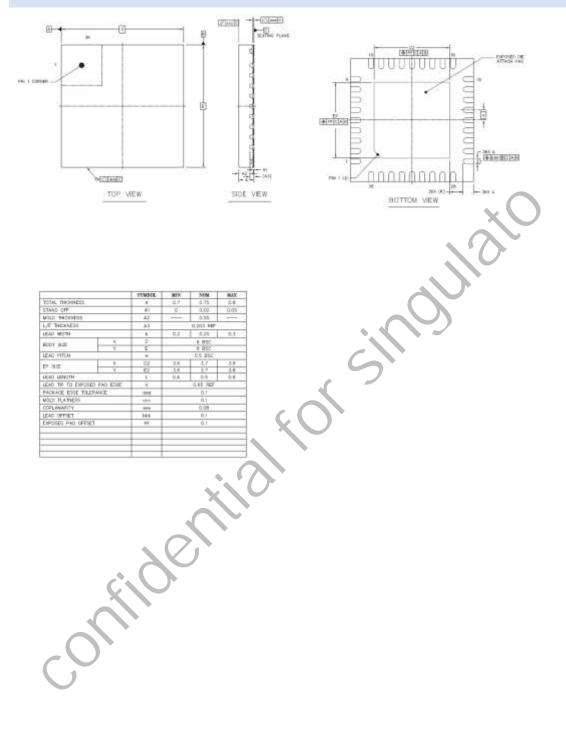

| 9  | Mechanical and Thermal                                  | 51 |

|    | RoHS-Compliant Packaging                                | 51 |

|    | Mechanical Information                                  | 52 |

| 10 | Ordering Information                                    | 53 |

|    |                                                         |    |

#### 1. GENERAL DESCRIPTION

The MotorComm YT8010 is a single pair Ethernet physical layer transceiver (PHY) which implements the Ethernet physical layer portion of the 100BASE-T1 standard as defined by the IEEE 802.3bw task force. Ideally suited for a wide range of automotive applications, it is manufactured using a standard digital CMOS process and contains all the active circuitry required to implement the physical layer functions to transmit and receive data on a single balanced twisted pair.

Based on cutting-edge DSP technology, combing adaptive equalizers, echo canceller, phaselocked, ADCs, phase-locked loops, line drivers, encoders/decoders, echo cancelers and all other required support circuitry at a 100Mbps data rate to achieve robust performance and exceed automotive electromagnetic interference (EMI) requirements in noisy environments with very low power dissipation.

The YT8010 is designed to be fully compliant with RGMII, RMII and Millint interface specifications, allowing compatibility with industry-standard Ethernet media eccuss controllers (MACs) and switch controllers.

The YT8010 delivers the most comprehensive automotive technology solution required by OEM and Tier 1 suppliers, meeting AEC-Q100 Grad. 1 comparature range.

#### TARGET APPLICATIONS

- Automotive infotainment system

- Automotive diagnostics

- Advanced driver as: st s, stems

- Body electronics

#### YT8010 Datasheet

#### 2. FEATURE

- 100BASE-T1 Transceiver

- 100BASE-T1 IEEE 802.3bw

standards

- Full duplex

- Rapid linkup time

- Support auto cable detection and working mode selection.

- MII/RMII/RGMII support

- RMII/RGMII interface EMI enhancement

- Support latency accommodation of RGMII clock

- Support IEEE 802.1AS

- Support Remote Wake up 3.3V analog supply.

- Advanced low-power management with local wake-up support

- Automotive Cable Diagnostics support

- Integrated LDO regulator allowing a single supply

- Internal/external/remote loopback mode for diagnosis

- MDI pins protected against ESD to 6kV HBM and 6kV IEC61000-4-2

- Jumbo frame support up to 16 kB

- Polarity detection and autormanual correction

- Integrated twisted pair termination

resistors

- AEC Q100 Grade 1 (-40~125°C)

- Trace matched output impedance

- Integrated low-pass filter

- Support over Temperature warning.

- Robust cable ESD tolerance

- Package QFN 36, 6x6mm

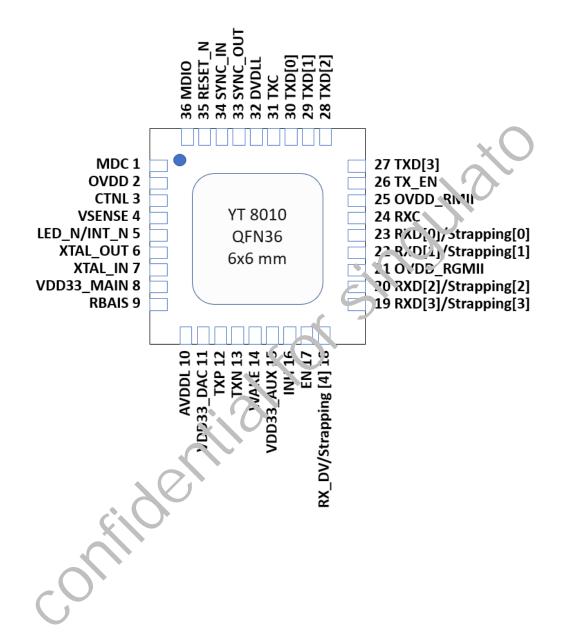

#### 3 PIN ASSIGMENT

#### YT8010 QFN36 6X6MM

#### PIN DESCRIPTIONS

- I = Input

- = Output

- I/O = Bidirectional •

- OD = Open-drain output •

- OT = Tristateable signal

- B = Bias•

- PU = Internal pull-up •

- PD = Internal pull-down •

- SOR = Sample on reset

- CS = Continuously sampled

- ST = Schmitt trigger

- XT = Crystal inputs/outputs pin type

- D = Digital pin type

- G = RGMII pin type •

- A = Analog pin type

| •   | SOR = Sample on reset                |                  |          |                                                                      |  |  |  |  |  |  |

|-----|--------------------------------------|------------------|----------|----------------------------------------------------------------------|--|--|--|--|--|--|

| •   | CS = Continuously sampled            |                  |          |                                                                      |  |  |  |  |  |  |

| •   | ST = Schmitt trigger                 |                  |          |                                                                      |  |  |  |  |  |  |

| •   | XT = Crystal inputs/outputs pin type |                  |          |                                                                      |  |  |  |  |  |  |

| •   | D = D                                | Digital pin type |          |                                                                      |  |  |  |  |  |  |

| •   | G = R                                | GMII pin type    |          |                                                                      |  |  |  |  |  |  |

| •   | A = A                                | nalog pin type   |          |                                                                      |  |  |  |  |  |  |

|     |                                      |                  |          |                                                                      |  |  |  |  |  |  |

|     |                                      |                  |          |                                                                      |  |  |  |  |  |  |

| Pir | n No.                                | Symbol           | Туре     | Description                                                          |  |  |  |  |  |  |

| 1   |                                      | MDC              | I; ST    | Management Dath Clock. Only need to be effect during mdio operation. |  |  |  |  |  |  |

| 2   |                                      | OVDD             | PWR,     | 2.5v or 3.3v for non-RGMII digital pads. When 2.5V is                |  |  |  |  |  |  |

|     |                                      |                  | 10       | selected, RESET, MDIO, and LED pins are not 3.3V                     |  |  |  |  |  |  |

|     |                                      |                  |          | tolerant.                                                            |  |  |  |  |  |  |

| 3   |                                      | VCNTL            | And      | Vcontrol. Output point of an internal error amplifier. This          |  |  |  |  |  |  |

|     |                                      |                  |          | pin shall be connected to the base of an external PNP                |  |  |  |  |  |  |

|     |                                      |                  | $\Delta$ | power transistor.                                                    |  |  |  |  |  |  |

| 4   |                                      | VSENCE           | Ana      | Vsense. Sensing point of the external power transistor.              |  |  |  |  |  |  |

|     |                                      |                  |          | This pin shall be connected to the external 1.2V power.              |  |  |  |  |  |  |

| 5   |                                      | 1/2D_1/11.JT_N   | O,od     | LED_N/INT_N Dual function pin. This pin is a dual                    |  |  |  |  |  |  |

|     | (                                    |                  |          | function pin. It is active low unless programmed through             |  |  |  |  |  |  |

|     |                                      | 9                |          | MDIO.                                                                |  |  |  |  |  |  |

| 6   | V                                    | XTAL_OUT         | O/XT     | 25 MHz Crystal Oscillator Output Pin. A continuous 25                |  |  |  |  |  |  |

|     |                                      |                  |          | MHz reference clock must be supplied to the chip by                  |  |  |  |  |  |  |

|     |                                      |                  |          | connecting a 25 MHz crystal between these two pins or                |  |  |  |  |  |  |

|     |                                      |                  |          | by driving XTAL_IN with an external 25 MHz clock. When               |  |  |  |  |  |  |

|     |                                      |                  |          | using a crystal, connect a loading capacitor from each               |  |  |  |  |  |  |

|     |                                      |                  |          | pin to GND. When using an oscillator, leave XTAL_OUT                 |  |  |  |  |  |  |

|     |                                      |                  |          | unconnected.                                                         |  |  |  |  |  |  |

| 7   |                                      | XTAL_IN          | I/XT     | 25 MHz Crystal Oscillator Input Pin.                                 |  |  |  |  |  |  |

|     |                                      |                  |          |                                                                      |  |  |  |  |  |  |

| 8  | VDD33_MAIN                | PWR,<br>I | 3.3V power for the main core.                                                                                                                                                                                                     |  |

|----|---------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9  | RBIAS                     | Ana       | Bias Resistor. A 2.4 k $\Omega\pm$ 1% resistor is connected between the RBIAS pin and GND                                                                                                                                         |  |

| 10 | AVDDL                     | PWR,<br>I | 1.2V power for the analog.                                                                                                                                                                                                        |  |

| 11 | VDD33_DAC                 | PWR,<br>I | 3.3V power for the DAC.                                                                                                                                                                                                           |  |

| 12 | ТХР                       | Ana       | Transmit/Receive Pairs . Differential data from copper media is transmitted and received on the single TRD± signal pair. There are $50\Omega$ internal terminations on the signal pair.                                           |  |

| 13 | TXN                       | Ana       | <ul> <li>pin. Since this device incorporates voltage driven 2AC, it<br/>does not require a center-tap supply</li> </ul>                                                                                                           |  |

| 14 | WAKE                      | l,pd      | WAKE. Active-high. When in sleep mode, transitioning the WAKE pin from low to high will hause the PHY to exit the sleep mode.                                                                                                     |  |

| 15 | VDD33_AUX                 | PWR,<br>I | 3.3V power for the auxiliar <i>r</i> dumain. This pin supplies power to the passive signal detect circuitry and must remain powered with 3.3V.                                                                                    |  |

| 16 | INH                       | 0         | Inhibit. Output to be connected to the LDO supplying<br>power to the PF.Y. When entering sleep mode, INH will<br>be bulled 'ow and will disable the LDO. When exit sleep<br>mode, INH will be pulled high and will enable the LDO |  |

| 17 | EN                        | l,pd      | EN. This pin is used in conjunction with INH to enable s'eep mode or to provide a local wakeup from sleep mode                                                                                                                    |  |

| 18 | RX_DV/<br>Strapping[4]    | kq.Cr     | Receive Data Valid. Active-high. RX_DV indicates that a<br>receive frame is in progress and that the data present on<br>the RXD output pins is valid.<br>Strapping[4]. Used as power on strapping[4] bit when<br>reset is active. |  |

| 19 | R).[D[3]/<br>Strapping[3] | IO,pd     | Receive Data Outputs. Byte-wide receive data output<br>synchronous with the receive clock. RXD[3] is the most<br>significant bit.<br>Strapping[3]. Used as power on strapping[3] bit when<br>reset is active.                     |  |

| 20 | RXD[2]/<br>Strapping[2]   | IO,pd     | Receive Data Outputs. Byte-wide receive data output<br>synchronous with the receive clock.<br>Strapping[2]. Used as power on strapping[2] bit when<br>reset is active.                                                            |  |

| 21 | OVDD_RGMII    | PWR,     | 2.5V or 3.3V for RGMII IO. This pin is internally shorted  |

|----|---------------|----------|------------------------------------------------------------|

|    |               | I        | with OVDD_RMII.                                            |

| 22 | RXD[1]/       | IO,pd    | Receive Data Outputs. Byte-wide receive data output        |

|    | Strapping[1]  |          | synchronous with the receive clock.                        |

|    |               |          | Strapping[1]. Used as power on strapping[1] bit when       |

|    |               |          | reset is active.                                           |

| 23 | RXD[0]/       | IO,pd    | Receive Data Outputs. Byte-wide receive data output        |

|    | Strapping[0]  |          | synchronous with the receive clock. RXD[0] is the less     |

|    |               |          | significant bit.                                           |

|    |               |          | Strapping[0]. Used as power on strapping[0] bit when       |

|    |               |          | reset is active.                                           |

| 24 | RXC           | IO,pu    | Receive Clock. 2.5M/25M output or input. This clock is     |

|    |               |          | used to synchronize the receive data outputs (XD[3:0].     |

|    |               |          | The direction and frequency depend on MI mode and          |

|    |               |          | link mode.                                                 |

| 25 | OVDD_RMII     | PWR,     | 2.5V or 3.3V for RGMII IO. This pin ( ) internally shorted |

|    |               | I        | with OVDD_RGMII.                                           |

| 26 | TX_EN         | I,ST     | Transmit Enable. Active-high. When TX_EN is asserted,      |

|    |               |          | the data on the TXD pins is encoded and transmitted.       |

| 27 | TXD[3]        | l,pd     | Transmit Data Input. Data is input synchronously with      |

|    |               |          | TXC clo sk.                                                |

| 28 | TXD[2]        | l,pd     | Transmit Lata Input. Data is input synchronously with      |

|    |               |          | TXC clock.                                                 |

| 29 | TXD[1]        | l,pd     | Transmit Data Input. Data is input synchronously with      |

|    |               |          | i. /C clock.                                               |

| 30 | TXD[0]        | l, d     | Transmit Data Input. Data is input synchronously with      |

|    |               | <u> </u> | TXC clock.                                                 |

| 31 | TXC           | iO,pd    | Transmit Clock. 2.5M/25M/50M output or input. This         |

|    | $\mathcal{L}$ |          | clock is used to synchronize the transmit data inputs      |

|    |               |          | TXD[3:0]. The direction and frequency depend on MII        |

|    |               |          | mode and link mode.                                        |

| 32 | D/DDL         | PWR,     | 1.2V input for digital core                                |

|    | 6             | Ι        |                                                            |

| 33 | SYNC_IO       | IO,pd    | 802.1AS Frame Sync event/sync pulse input or output        |

| 34 | SYNC_IN       | I, ST    | 802.1AS Frame Sync event/sync pulse input.                 |

| 35 | RESET_N       | l,pu     | RESET. Active-low, reset pin for chip.                     |

| 36 | MDIO          | IO,pu    | Management Data I/O. This serial input/output bit is       |

|    |               |          | used to read from and write to the MII registers. The      |

|    |               |          | data value on the MDIO pin is valid and latched on the     |

|    |               |          | rising edge of MDC.                                        |

|    |               |          |                                                            |

#### 4 FUNCTION DESCRIPTION

#### APPLICATION DIAGRAM

#### 100BASE-T1 APPLICATION

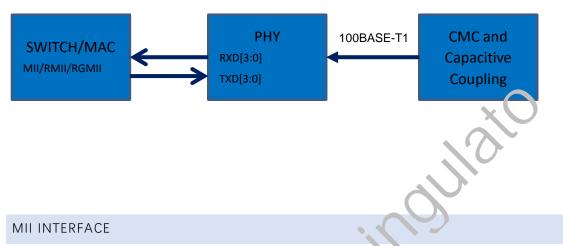

The Media Independent Interface (MII) is the digital data interface between the MAC and the physical layer that can be enabled when the device is functioning in 100BASE-T1 mode. The original MII transmit signals include TX\_EN, TXC,  $T \Delta \nu_L ? \omega_1^{-1}$  and TX\_ER. The receive signals include RX\_DV, RXC, RXD[3:0], and RX\_ER. The media status signals include CRS and COL. Due to pincount limitations, the YT8010 supports a succet of MII signals. This subset includes all MII signals except TX\_ER, RX\_ER, CRS and COL.

#### RMII INTERFAC

Reduced med a-independent interface (RMII) is a standard which was developed to reduce the number of signals required to connect a PHY to a MAC. If this interface is active, the number of data signal pins required to and from the MAC is reduced to half by clocking data on both the rising and falling edge of the transmit clock.

#### MANAGEMENT INTERFACE

The Status and Control registers of the device are accessible through the MDIO and MDC serial interface. The functional and electrical properties of this management interface comply with IEEE 802.3, Section 22 and also support MDC clock rates up to 25 MHz.

#### DAC

The digital-to-analog converter (DAC) transmits PAM3, MLT3, and Manchester coded symbols. The transmit DAC performs signal wave shaping that reduces electromagnetic interference (EMI). The transmit DAC uses voltage driven output with internal terminations and hence does not require external components or magnetic supply for operation.

#### ADC

Each receive channel has its own analog-to-digital converter (ADC) that samples the incoming data on the receive channel and feeds the output to the digital data path.

#### ADAPTIVE EQUALIZER

The digital adaptive equalizer removes inter-symbol interference (ISI) created by the channel. The equalizer eccepts sampled data from the analog-to-digital converter (ADC) on each

channel and produces equalized data. The coefficients of the equalizer are adaptive to accommodate varying conditions of cable quality and cable length.

#### ECHO-CANCELLER

The echo impairment is caused on each channel because of the bidirectional transceiver in 100BASE-T1 mode. An echo canceller is added to remove this impairment from the ADC output. The echo canceler coefficients are adaptive to manage the varying echo impulse responses caused by different channels, transmitters, and environmental conditions.

#### CLOCK RECOVERY

The clock recovery block creates the transmit and receive clocks for 100BASE-T1 the two ends of the link perform loop timing. One end of the link is configured as the master, and the other is configured as the slave. The master transmit and receive clocks are locked to the 25 MHz crystal input. The slave transmit and receive clocks are locked to the incoming receive data stream. Loop timing allows for the cancellation of echo.

#### LINK MONITOR

Description about link status in different vorking mode.

In 100BASE-T1 mode, after receiver synchronizes to link partner's transmit signal and finishes local training process, local receiver status will be good. Phy will monitor local receive status continuously. Local receiver status should be good for at least 1.8us in 100BASE-T1 mode, then link monitor enters link pass status. Accordingly, if Local receive status is bad then link monitor enters link fail status immediately.

Link statut car be read in mii reg address 0x1h, bit2.

#### POLARITY DETECTION AND AUTO CORRECTION

YT8010 can detect and correct two types of cable errors: swapping of pairs within the UTP cable and swapping of wires within a pair.

#### 5 OPERATIONAL DESCRIPTION

#### RESET

YT8010 have a hardware reset pin(RESET\_N) which is low active. RESET\_N should be active for at least 5us to make sure all internal logic is reset to a known state. Hardware reset should be applied after power up including wakeup from sleep mode.

RESET\_N is also used as enable for power on strapping. During RESET\_N is active, YT8010 latches input value on RX\_DV and RXD[3:0] as strapping[4:0]. Strapping[4:0] is used as configuration information which provides flexibility in application without mdio access.

YT8010 also provides two software reset control registers which are used to reset all oternal logic except some mdio configuration registers. For detailed information about what register will be reset by software reset, please refer to register table. Configure bit 15 of Ic's n ii register(address 0x0) or mii register(address 0x0) to 1 to enable software reset. These two bits are self-clear after reset process is done.

#### PHY ADDRESS

For YT8010, Strapping[4] is used to generate provaddress. Phy address is Strapping[4]+1. For example, If strapping[4] is 1'b1, then phy address is 2.

YT8010 and YT8050 always response to phy address 0. It also has another broadcast phy address which is configurable through r ion. bit[4:0] of extended register(address 0x0) is broadcast phy address and its default value is 5 in1111. Bit[5] of extended register(address 0x0) is enable control for broadcast phy address and its default value is 1'b1.

#### XMII INTERFACE

YT8010 support 4 kinds of MII related interfaces: MII, RMII, RGMII and REMII.

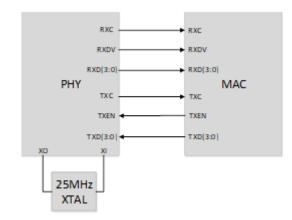

#### МII

The Media Independent Interface (MII) is the digital data interface between the MAC and the physical layer that can be enabled when the device is functioning in 100BASE-T1 mode. The original MII transmit signals include TX\_EN, TXC, TXD[3:0], and TX\_ER. The receive signals include RX\_DV, RXC, RXD[3:0], and RX\_ER. The media status signals include CRS and COL. Due to pin-count limitations, the YT8010 supports a subset of MII signals. This subset includes all MII signals except TX\_ER, RX\_ER, CRS and COL. For 100M application, TXC and RXC are 25MHz; for 10M application, TXC and RXC are 2.5MHz. TXC and RXC are output in this case.

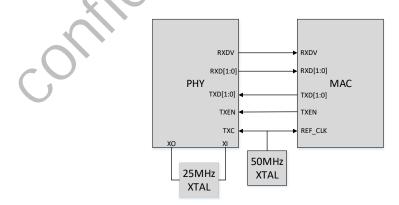

Figure . connection diagram of MII

#### RMII

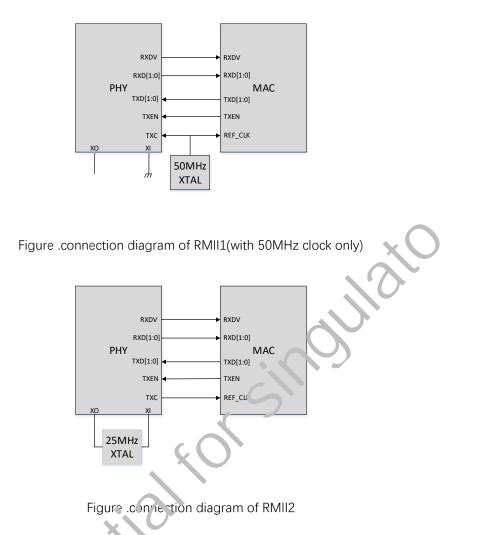

Reduced media-independent interface (RMII) is a standard which was developed to reduce the number of signals required to connect a PHY to a MAC. If this is terface is active, the number of data signal pins required to and from the MAC is reduced to half by doubling clock speed compared to MII. It has 7 signals: REF\_CLK, TX\_EN, TXL [1:0], RX\_DV and RXD[1:0]. In YT8010/YT8050, we use TXC as REF\_CLK. For 100N1 application, REF\_CLK is 50MHz; for 10M application, REF\_CLK is still 50MHz, data will be duplicated for 10 times in 20ns cycles. YT8010/ supports two types of connection method 1. MII1 mode: This is fully conforming to RMII standard. YT8010/YT8050 can use clock from TXC as reference clock for pll. In this case, 25MHz crystal at XI/XO is not needed. Configure bit 6 of extended register(address 0h50) to 1 to enable this feature. 2. RMII2 mode. TXC will be 50MHz output to MAC, this can save one 50MHz clock source.

Figure .connection diagram of RMII1(with 25MHz and 50MHz clock)

#### RGMII

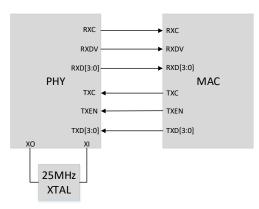

Reduced gigabit med a independent interface is a subset of GMII which is used for gigabit Ethernet. For 100M/1( M a polication, RGMII is similar to MII. The only difference is that tx\_er/rx\_er is tran\_mit\_ed by tx\_en/rx\_dv on the falling edge of clock. TXD[3:0] and RXD[3:0] will be duplicated on coth rising and falling edge of clock. For 100M application, TXC and RXC are 25MHz; for 1cM application, TXC and RXC are 2.5MHz.

Figure .connection diagram of RGMII

#### **REMII INTERFACE**

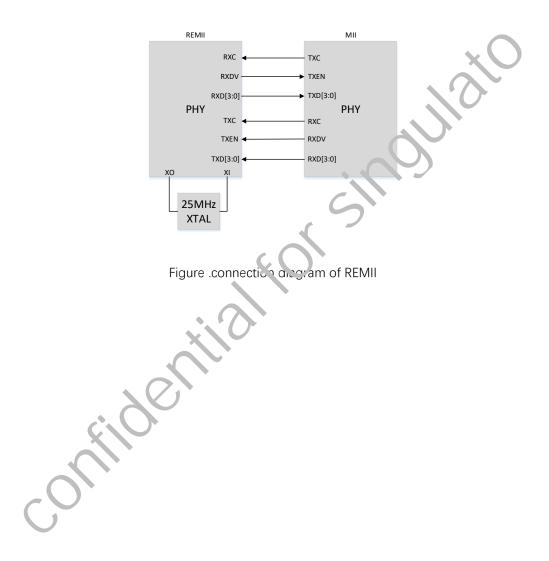

Reverse media independent interface is the opposite of MII interface. The only difference is the direction of tx clock and rx clock. For MII, tx clock and rx clock are output; for REMII, tx clock and rx clock are input. REMII interface are used for back to back connection of two phys.

QUIAT

śľ

#### SQI

YT8010 provides a method to monitor quality of link.

By reading extended register mse(address 0h1005), we can obtain SNR during following steps.

- a) Read register mse[14:0]

- b) Calculate SNR = 10\*log10(32768/(3\*mse))

- c) Average over 200 readings A= avg(SNR)

- d) Rank the link quality

- i. SQI = 5 when A > 23

- ii. SQI = 4 when 18 < A < 23

- iii. SQI = 3 when 15 < A < 18

- iv. SQI = 2 when 15 < A < 18

- v. SQI = 1 when 11 < A < 14

#### LOOPBACK MODE

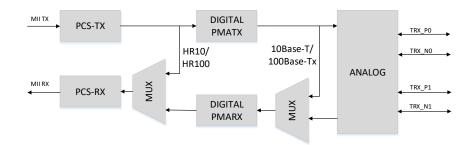

There are three loopback modes in YT8010.

#### INTERNAL LOOPBACK:

In Internal looper ck mode, YT8010 feed transmit data to receive path in chip.

Configure bit . 4 of mii register(address 0h0) to enable internal loopback mode. For 10Base - T and 100Base - Tx, YT8050 feeds digital dac data to adc directly. For HR10/HR100,

YT8010 feeds digital pcs transmit data to pcs receiver directly.

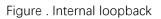

#### EXTERNAL LOOPBACK

In external loopback mode, YT8010 feed transmit data to receive path out of chip. For 100 BASE-T1 configure bit 12 of extended register(address 0h4000) and just leave 12X\_P0/N0 and TRX\_P0/N0 unconnected.

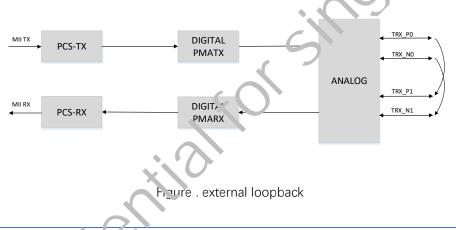

#### REMOTE LOOPBACK

In remote loopback mode. YT8010 feed MII receive data to transmit path in chip. Configure bit 11 of extended register(address 0h4000) and for TRX interface, just connect to link partner normally.

Figure . external loopback

#### MASTER-SLAVE CONFIGURATION

Master and slave configuration is from hardware strapping or in force mode, it comes from bit 3 of lds mii reg(address 0h0).

#### INTERRUPT

Interrupt shares same pin with LED.

Interrupt function can be selected by configuring bit 14 of extended register(address 0h4001). The polarity of interrupt is configurable by accessing bit 4 of mii reg(address 0h10).

Every interrupt has a corresponding mask bit and interrupt bit.

Please refer to mii register map(address 0h12, 0h13, 0h16 and 0h17) for detailed information.

#### POWER SAVING

YT8010 supports standby mode and sleep mode to save power

In standby mode, PHY turn off analog ADC, DAC, and PLL. All digital logic is gated except MDIO register access. INH pin is high and power supply is still on. The link is down in standby mode, YT8010 can recover from standby mode repidly. Write bit 11 of mii address 0x0h to 1'b1 to enter standby mode. To exit standby mode, vrite the same bit to 1'b0. In standby mode, the power consumption of YT8010 is less than mix.

In sleep mode, PHY turn off all power supply except always on 3.3v supply. The only working block is analog INH generation circle and power detect circle. In this mode, INH pin is low. There are three ways to enter sleep mode:

- 1. Pull down local FN pin from high.

- 2. Write b +12 of extended 0x1007 register.

- 3. Use TC10 standard to control remote phy to enter sleep mode.

There are also three ways to exit sleep mode:

- 1. Pull up local En pin from low.

- 2. Pull up local Wake pin from low.

3. Inject wake up signal which amplitude at txp/txn for more than 100us to wake up phy remotely.

Please refer to following chapter for detailed information about remote control. In sleep mode, the power consumption of YT8010 is lower than 50uw.

#### APPLICATION NOTES ABOUT SLEEP MODE

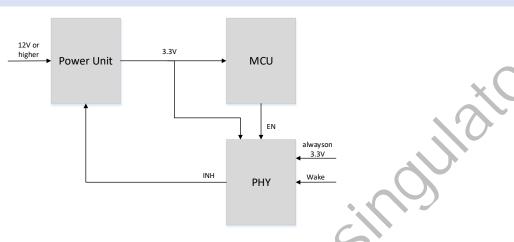

figure. Hardware connection description (MCU don't support Sleep and Wakeup function)

When MCU don't support sleep and wakeup function, YT8010 can take the responsibility of power control. If MCU decides to enter sleep mode, it can pull down EN pin or configure sleep\_mode\_en register through m lio, then INH goes down and power supply for MCU and phy will turn off except always on 3.3 V power supply. The whole system can be wakeup remotely by injecting wakeup pulse on txp/txn or pulling up wake pin.

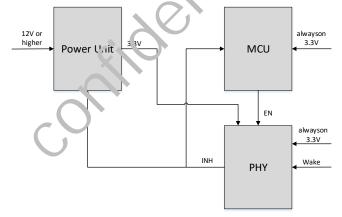

figure. Hardware connection description (MCU support Sleep and Wakeup function)

When MCU support sleep and wakeup function,INH pin only control the power supply of phy<sub>o</sub> If MCU decides to enter sleep mode, it can pull down En pin or configure sleep\_mode\_en register through mdio, then INH goes down and power supply for phy will

turn off except always on 3.3V power supply. MCU can pull up En/Wake pin to wakeup phy or phy will be wakeup remotely and send out a wake interrupt to MCU.

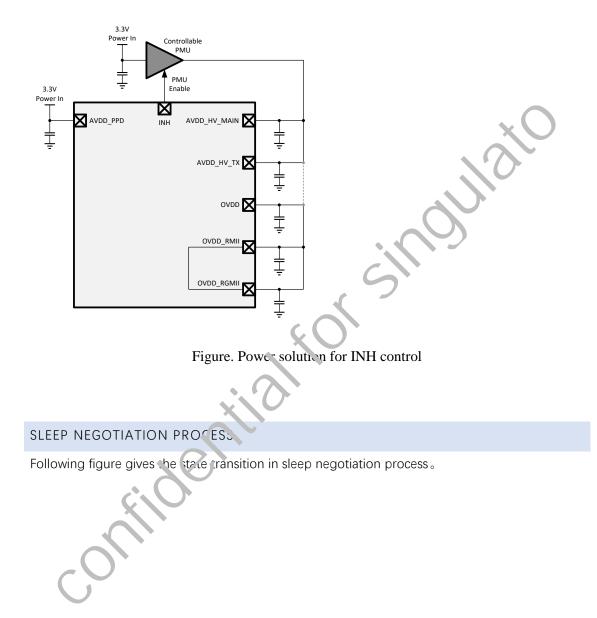

Following is an example of INH control application. Only AVDD\_PPD is connected to always on 3.3V power and other power pins are controlled by INH pin.

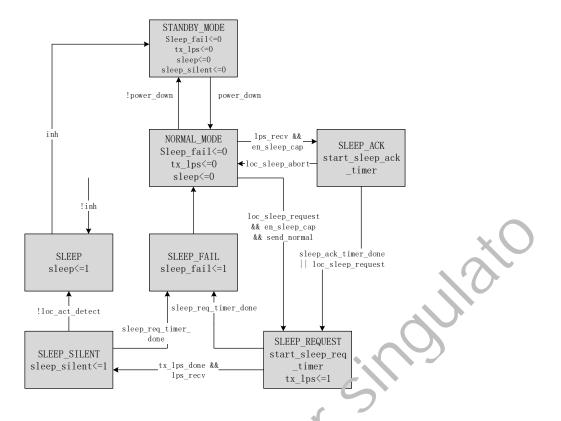

Figure. State diagram in sleep negotiation process

After YT8010 is power up, it enters standby mode. Power down register control the Translation between Standby mode and Normal mode. Default value of Power down register is zero, phy will enter normal mode directly without N1CU.

Phy can start sleep negotiation process after link is set up between two phys.

Initiator configures loc\_arep\_request register to start sleep negotiation process. Then Initiator enter SLEEP\_REQUEST state and send LPS pattern and enable sleep\_req\_timer(16ms). Responder receive LPS pattern and enter SLEEP\_ACK state, enable sleep\_ack\_timer(8ms) and send out interrupt to MCU to inform that sleep request is received. In SLEEP\_ACK state, phy wait response nerve MCU. MCU can accept the sleep request by configuring loc\_sleep\_request or reject by configuring loc\_sleep\_abort. If there is no response from MCU before sleep\_ack\_timer done, Responder will think sleep request is accepted and enter SLEEP\_REQUEST state. If Responder rejects sleep request, Initiator will enter SLEEP\_FAIL state after sleep\_req\_timer done and sleep negotiation process is done. If Responder accepts sleep request, Responder will send LPS pattern to inform initiator. After received LPS pattern from Responder, Initiator enters SLEEP\_SILENT state and stops sending any signal on txp/txn and keeps checking signal energy on txp/txn. After the signal is gone, Initiator enters SLEEP\_MODE state. In the meanwhile, Responser enters SLEEP\_SILENT state after LPS pattern is sent and keeps checking signal energy

on txp/txn. After the signal is gone, Responder enters SLEEP\_MODE state and sleep negotiation process is done.

Following figures give out the process of sleep negotiation.

figure. Process of failed sleep negotiation

#### REMOTE WAKEUP

YT8010 can send wakeup pulse to wakeup link partner remotely if link partner support remote wakeup. YT8010 can also wakeup by wake up pulse sent by link partner.

To send out wakeup pulse to link partner, configure link\_control to 0 and loc\_wake\_req to 1 in NORMARL\_MODE. YT8010 will send 1ms wakeup pulse(IDLE symbol) to wake up link\_partner.

If link is already setup, configure loc\_wake\_req to 1, YT8010 will send 128bits wake up request to link partner. YT8010 will send an interrupt to inform MCU after received wake up request from link partner.

ontidential for singular

#### 6 REGISTER OVERVIEW

#### MII MANAGEMENT INTERFACE CLAUSE 22 REGISTER PROGRAMMING

The YT8010 transceiver is designed to be fully compliant with the MII clause of the IEEE 802.3u Ethernet specification.

The MII management interface registers are written and read serially, using the MDIO and MDC pins.

A clock of up to 25 MHz must drive the MDC pin of the YT8010. Data transferred to and from the MDIO pin is synchronized with the MDC clock. The following sections describe what each MII read or write instruction contains.

#### MII REGISTERS

### MII REGISTER 00H: BASIC CONTROL REGISTER

| Bit | Symbol   | Access | Default | Description                                      |

|-----|----------|--------|---------|--------------------------------------------------|

| 15  | Reset    | RW     | 1'b0    | PHY Software Reset. Writing 1 to this bit causes |

|     |          | SC     |         | in mediate PHY reset. Once the operation is      |

|     |          |        |         | done, this bit is cleared automatically.         |

|     |          |        | 30      | 0: Normal operation                              |

|     |          |        |         | 1: PHY reset                                     |

| 14  | Loopback | PW     | 1'b0    | External loopback control                        |

|     | 2.5      | JWC    |         | 1'b0: disable loopback                           |

|     |          |        |         | 1'b1: enable loopback                            |

|     |          |        |         |                                                  |

| 13 | Speed_Selecti<br>on(LSB) | RW              | 1'b1 | LSB of speed_selection[1:0]. Link speed can be<br>selected via either the Auto-Negotiation process,<br>or manual speed selection speed_selection[1:0].<br>Speed_selection[1:0] is valid when Auto-<br>Negotiation is disabled by clearing bit 0.12 to<br>zero.<br>Bit6 bit13<br>1 1 = Reserved<br>1 0 = 1000Mb/s<br>0 1 = 100Mb/s<br>0 0 = 10Mb/s |

|----|--------------------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 | Autoneg_En               | RW              | 1'b1 | <ol> <li>to enable auto-negotia<sup>*</sup>ion;</li> <li>auto-negotiation is disa_led.</li> </ol>                                                                                                                                                                                                                                                 |

| 11 | Power_down               | RW<br>SWC       | 1'b0 | <pre>1 = Power down<br/>0 = Normal operation<br/>When the port is switched from power down to<br/>honted operation, software reset and Auto-<br/>Negotiation are performed even bit[15] RESET<br/>and bit[9] RESTART_AUTO_NEGOTIATION<br/>are not set by the user.</pre>                                                                          |

| 10 | Isolate                  | RW<br>SWC       | Г'ЬО | Isolate phy from MII/GMII/RGMII: PHY will<br>not respond to RGMII TXD/TX_CTL, and<br>present high impedance on RXD/RX_CTL.<br>1'b0: Normal mode<br>1'b1: Isolate mode                                                                                                                                                                             |

| 9  | Re_Autoneg               | RW<br>SWS<br>SC | 1'b0 | Auto-Negotiation automatically restarts after<br>hardware or software reset regardelss of bit[9]<br>RESTART.<br>1 = Restart Auto-Negotiation Process<br>0 = Normal operation                                                                                                                                                                      |

| 8  | Duplex_Mode              | RW              | 1'b1 | The duplex mode can be selected via either the<br>Auto-Negotiation process or manual duplex<br>selection. Manual duplex selection is allowed                                                                                                                                                                                                      |

|     |                              |           |      | <ul> <li>when Auto-Negotiation is disabled by setting</li> <li>bit[12] AUTO_NEGOTIATION to 0.</li> <li>1 = Full Duplex</li> <li>0 = Half Duplex</li> </ul> |

|-----|------------------------------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Collision_Test               | RW<br>SWC | 1'b0 | Setting this bit to 1 makes the COL signal<br>asserted whenever the TX_EN signal is asserted.<br>1 = Enable COL signal test<br>0 = Disable COL signal test |

| 6   | Speed_<br>Selection(MS<br>B) | RW        | 1'b1 | See bit13.                                                                                                                                                 |

| 5:0 | Reserved                     | RO        | 5'b0 | Reserved. Write as 0, ignore of read                                                                                                                       |

## MII REGISTER 01H: BASIC STATUS RECISTER

| Bit | Symbol          | Access | Default | Dc cription                                     |  |  |  |

|-----|-----------------|--------|---------|-------------------------------------------------|--|--|--|

|     | ×O <sup>×</sup> |        |         |                                                 |  |  |  |

| 15  | 100Base-T4      | RO     | 1'b6    | PHY doesn't support 100BASE-T4                  |  |  |  |

| 14  | 100Base-X_Fd    | RO     | 1 b!    | PHY supports 100BASE-X_FD                       |  |  |  |

| 13  | 100Base-X_Hd    | РО     | 1'b1    | PHY supports 100BASE-X_HD                       |  |  |  |

| 12  | 10Mbps_Fd       | RO     | 1'b1    | PHY supports 10Mbps_Fd                          |  |  |  |

| 11  | 10Mbps_H.       | RO     | 1'b1    | PHY supports 10Mbps_Hd                          |  |  |  |

| 10  | 100Base-T2_Fd   | RO     | 1'b0    | PHY doesn't support 100Base-T2_Fd               |  |  |  |

| 9   | 100Bε se-T2_Hd  | RO     | 1'b0    | PHY doesn't support 100Base-T2_Hd               |  |  |  |

| 8   | Extended_Status | RO     | 1'b1    | Whether support extended status register in 0Fh |  |  |  |

|     |                 |        |         | 0: Not supported                                |  |  |  |

|     |                 |        |         | 1: Supported                                    |  |  |  |

|   |                             |                       |      | Mot                                                                                                                                                                                                                                                   |

|---|-----------------------------|-----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 | Unidirect_Ability           | RO                    | 1'b0 | 1'b0: PHY able to transmit from MII only<br>when the PHY has determined that a valid<br>link has been established<br>1'b1: PHY able to transmit from MII<br>regardless of whether the PHY has<br>determined that a valid link has been<br>established |

| 6 | Mf_Preamble_Su<br>ppression | RO                    | 1'b1 | 1'b0: PHY will not accept management<br>frames with preamble suppressed<br>1'b1: PHY will accept management frames<br>with preamble suppressed                                                                                                        |

| 5 | Autoneg_Complet<br>e        | RO<br>SWC             | 1'b0 | 1'b0: Auto-negotiation process not completed<br>1'b1: Auto-negotiation process completed                                                                                                                                                              |

| 4 | Remote_Fault                | RO<br>RC<br>SWC<br>LH | 1'b0 | 1'b0: no remote fault condition detected<br>1'b1: remote fault condition detected                                                                                                                                                                     |

| 3 | Autoneg_Ability             | RO                    | 1'b1 | 1'b0: PHY not able to perform Auto-<br>negociation<br>1'b1: PHY able to perform Auto-negotiation                                                                                                                                                      |

| 2 | Link_Status                 | RO<br>LL<br>SWC       | 172  | Link status<br>1'b0: Link is down<br>1'b1: Link is up                                                                                                                                                                                                 |

| 1 | Jabber_Detec                | кО<br>RC<br>LH<br>SWC | 1'b0 | 10Baset jabber detected<br>1'b0: no jabber condition detected<br>1'b1: Jabber condition detected                                                                                                                                                      |

| 0 | Extended_Capabil            | RO                    | 1'b1 | To indicate whether support extended registers,<br>to access from address register 1Eh and data<br>register 1Fh<br>1'b0: Not supported<br>1'b1: Supported                                                                                             |

#### MII REGISTER 02H: PHY IDENTIFICATION REGISTER1

| Bit  | Symbol | Access | Default | Description                                               |

|------|--------|--------|---------|-----------------------------------------------------------|

| 15:0 | Phy_Id | RO     | 16'b0   | Bits 3 to 18 of the Organizationally<br>Unique Identifier |

#### MII REGISTER 03H: PHY IDENTIFICATION REGISTER2

| Bit   | Symbol      | Access | Default | Description                                               |

|-------|-------------|--------|---------|-----------------------------------------------------------|

| 15:10 | Phy_Id      | RO     | 6'b0    | Bits 19 to 24 of the Organ'zaconally<br>Unique Identifier |

| 9:4   | Type_No     | RO     | 6'h10   | For motor phy, ?0, for combo phy, 10                      |

| 3:0   | Revision_No | RO     | 4'h1    | 4 bits manufacturer's revision number                     |

### MII REGISTER 04H: AUTO-NEGOTIATION ADVERTISEMENT

| <b>D</b> !/ | a      |        |         |             |

|-------------|--------|--------|---------|-------------|

| Bit         | Symbol | Access | Default | Description |

| 15 | Next_Page | RW | 1'b9 | This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:               |

|----|-----------|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 2         | C  |      | • Software reset is asserted by writing register 0x0 bit[15]                                                                                                 |

|    |           |    |      | • Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]                                                                                       |

| (  |           |    |      | • The port is switched from power down to normal operation by writing register 0x0 bit[11]                                                                   |

|    |           |    |      | • Link goes down                                                                                                                                             |

|    |           |    |      | If 1000BASE-T is advertised, the required next<br>pages are automatically transmitted. This bit<br>must be set to 0 if no additional next page is<br>needed. |

|    |           |    |      | 1 = Advertise                                                                                                                                                |

|    |           |    |      | 0 = Not advertised                                                                                                                                           |

#### YT8010 Datasheet

| 14 | Ack                    | RO | 1'b0 | Always 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----|------------------------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13 | Remote_Fault           | RW | 1'b0 | <ul><li>1 = Set Remote Fault bit</li><li>0 = Do not set Remote Fault bit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12 | Extended_Nex<br>t_Page | RW | 1'b1 | Extended next page enable control bit<br>1 = Local device supports transmission of<br>extended next pages<br>0 = Local device does not support transmission<br>of extended next pages.                                                                                                                                                                                                                                                                                                                          |

| 11 | Asymmetric_P<br>ause   | RW | 1'b1 | <ul> <li>This bit is updated immediat. If a iter the writing operation; however the configuration does not take effect until any of the following occurs:</li> <li>Software reset in asserted by writing register 0x0 bit[15]</li> <li>Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]</li> <li>The port is switched from power down to normal operation by writing register 0x0 bit[11]</li> <li>Link goes down</li> <li>1 = Asymmetric Pause</li> <li>0 = No asymmetric Pause</li> </ul> |

| 10 | Pause                  | EW | 1'b1 | <ul> <li>This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:</li> <li>Software reset is asserted by writing register 0x0 bit[15]</li> <li>Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]</li> <li>The port is switched from power down to normal operation by writing register 0x0 bit[11]</li> <li>Link goes down</li> <li>1 = MAC PAUSE implemented</li> </ul>                               |

|   |                                |    |      | 0 = MAC PAUSE not implemented                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|--------------------------------|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9 | 100BASE-T4                     | RO | 1'b0 | 1 = Able to perform 100BASE-T4<br>0 = Not able to perform 100BASE-T4<br>Always 0                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8 | 100BASE-<br>TX_Full_Dupl<br>ex | RW | 1'b1 | <ul> <li>This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:</li> <li>Software reset is asserted by writing register 0x0 bit[15]</li> <li>Restart Auto-Negoliation is triggered by writing register. 0.0 bit[9]</li> <li>The port is switched from power down to normal operation by writing register 0x0 bit[11]</li> <li>Link goes down</li> <li>1 = Advertise</li> <li>0 = Not advertised</li> </ul> |

| 7 | 100BASE-<br>TX_Half_Dup<br>lex | RW | 1'b1 | <ul> <li>This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:</li> <li>Software reset is asserted by writing register 0x0 bit[15]</li> <li>Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]</li> <li>The port is switched from power down to normal operation by writing register 0x0 bit[11]</li> <li>Link goes down</li> <li>1 = Advertise</li> <li>0 = Not advertised</li> </ul>  |

| 6   | 10BASE-<br>Te_Full_Dupl<br>ex | RW | 1'b1         | <ul> <li>This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:</li> <li>Software reset is asserted by writing register 0x0 bit[15]</li> <li>Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]</li> <li>The port is switched from power down to normal operation by writing register 0x0 bit[11]</li> <li>Link goes down</li> <li>1 = Advertise</li> <li>0 = Not advertised</li> </ul>  |

|-----|-------------------------------|----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | 10BASE-<br>Te_Half_Dupl<br>ex | RW | 1'b1         | <ul> <li>This bit is updated in mediately after the writing operation; howe or the configuration does not take effect until any of the following occurs:</li> <li>Software reset is asserted by writing register 0x0 bit[15]</li> <li>Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]</li> <li>The port is switched from power down to normal operation by writing register 0x0 bit[11]</li> <li>Link goes down</li> <li>1 = Advertise</li> <li>0 = Not advertised</li> </ul> |

| 4:0 | Secotor_Field                 | RW | 5'b0000<br>1 | Selector Field mode.<br>00001 = IEEE 802.3                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **MII REGISTER 05H: AUTO-NEGOTIATION LINK PARTNER**

#### ABILITY

| Bit | Symbol |

|-----|--------|

| DIL | Symbol |

Bit Symbol Access Default Description

|    |                            |           |      | Motor Comm                                                                                                                                                       |

|----|----------------------------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | 1000Base-X_Fd              | RO<br>SWC | 1'b0 | Received Code Word Bit 15<br>1 = Link partner is capable of next page<br>0 = Link partner is not capable of next page                                            |

| 14 | ACK                        | RO<br>SWC | 1'b0 | Acknowledge. Received Code Word Bit 14<br>1 = Link partner has received link code<br>word<br>0 = Link partner has not received link code<br>word                 |

| 13 | REMOTE_FAULT               | RO<br>SWC | 1'b0 | Remote Fault. Received Code Word Bit 13<br>1 = Link partner has acted a remote fault<br>0 = Link partner has not detected remote<br>fault                        |

| 12 | RESERVED                   | RO<br>SWC | 1'b0 | Technology \bility Field. Received Code<br>Word bit 12                                                                                                           |

| 11 | ASYMMETRIC_PAUSE           | RO<br>SWC | 1'b0 | Technology Ability Field. Received Code<br>Word Bit 11<br>1 = Link partner requests asymmetric pause<br>0 = Link partner does not request<br>asymmetric<br>pause |

| 10 | PAUSE                      | RO<br>SWC | 1'b0 | Technology Ability Field. Received Code<br>Word Bit 10<br>1 = Link partner supports pause operation<br>0 = Link partner does not support pause<br>operation      |

| 9  | 00FASE-T4                  | RO<br>SWC | 1'b0 | Technology Ability Field. Received Code<br>Word Bit 9<br>1 = Link partner supports 100BASE-T4<br>0 = Link partner does not<br>support100BASE-T4                  |

| 8  | 100BASE-<br>TX_FULL_DUPLEX | RO<br>SWC | 1'b0 | Technology Ability Field. Received Code<br>Word Bit 8<br>1 = Link partner supports 100BASE-TX<br>full-duplex                                                     |

|     |                            |           |      | 0 = Link partner does not support<br>100BASE-TX full-duplex                                                                                                                    |

|-----|----------------------------|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 100BASE-<br>TX_HALF_DUPLEX | RO<br>SWC | 1'b0 | Technology Ability Field. Received Code<br>Word Bit 7<br>1 = Link partner supports 100BASE-TX<br>half-duplex<br>0 = Link partner does not support<br>100BASE-TX<br>half-duplex |

| 6   | 10BASE-<br>Te_FULL_DUPLEX  | RO<br>SWC | 1'b0 | Technology Ability Field. Received Code<br>Word Bit 6<br>1 = Link pattner supports 10BASE-Te full-<br>duplex<br>0 = Link pattner does not support 10BASE-<br>Te full-duplex    |

| 5   | 10BASE-<br>Te_HALF_DUPLEX  | RO<br>SWC | 1'b0 | Technology Ability Field. Received Code<br>Word Bit 5<br>1 = Link partner supports 10BASE-Te half-<br>duplex<br>0 = Link partner does not support 10BASE-<br>Te half-duplex    |

| 4:0 | SELECTOR_FIFLD             | RO<br>SWC | 5'h0 | Selector Field Received Code Word Bit 4:0                                                                                                                                      |

# SWC MII REGISTER CCH: AUTO-NEGOTIATION EXPANSION REGISTER

| Bit  | Symbol                      | Access          | Default        | Description                                                              |

|------|-----------------------------|-----------------|----------------|--------------------------------------------------------------------------|

| 15:5 | Reserved                    | RO              | 11 <b>'</b> h0 | Always 0                                                                 |

| 4    | Parallel_Detection_fault    | RO RC LH<br>SWC | 1'b0           | <ul><li>1 = Fault is detected</li><li>0 = No fault is detected</li></ul> |

| 3    | Link_partner_next_page able | RO LH SWC       | 1'b0           | 1 = Link partner supports Next page                                      |

|   |                                        |          |      | 0 = Link partner does not support<br>next page                                                                            |

|---|----------------------------------------|----------|------|---------------------------------------------------------------------------------------------------------------------------|

| 2 | Local_Next_Page_able                   | RO       | 1'b1 | <ul><li>1 = Local Device supports Next</li><li>Page</li><li>0 = Local Device does not Next</li><li>Page</li></ul>         |

| 1 | Page_received                          | RO RC LH | 1'b0 | <ul><li>1 = A new page is received</li><li>0 = No new page is received</li></ul>                                          |

| 0 | Link_Partner_Auto_negotiati<br>on_able | RO       | 1'b0 | <ul> <li>1 = Link partner supports autonegotiatic.</li> <li>0 = Link partner does not support auto-negotiation</li> </ul> |

# MII REGISTER 07H: AUTO-NEGOTIATION NEXT PAGE REGISTER

| Bit | Symbol             | Access           | Default | Description                                                            |

|-----|--------------------|------------------|---------|------------------------------------------------------------------------|

| 15  | Next_Page          | RW               | i '50   | Transmit Code Word Bit 15                                              |

|     |                    |                  |         | 1 = The page is not the last page                                      |

|     |                    | $\mathbf{x} < 0$ |         | 0 = The page is the last page                                          |

| 14  | Reserved           | 20               | 1'b0    | Transmit Code Word Bit 14                                              |

| 13  | Message_pare_riode | RW               | 1'b1    | Transmit Code Word Bit 13                                              |

|     | C\O                |                  |         | 1 = Message Page                                                       |

|     |                    |                  |         | 0 = Unformatted Page                                                   |

| 12  | Act 2              | RW               | 1'b0    | Transmit Code Word Bit 12                                              |

| C   | ,                  |                  |         | 1 = Comply with message                                                |

|     |                    |                  |         | 0 = Cannot comply with message                                         |

| 11  | Toggle             | RO               | 1'b0    | Transmit Code Word Bit 11                                              |

|     |                    |                  |         | 1 = This bit in the previously exchanged Code<br>Word is logic 0       |

|     |                    |                  |         | 0 = The Toggle bit in the previously exchanged<br>Code Word is logic 1 |

| 10:0 | Message_Unformatte | RW | 11'h1 | Transmit Code Word Bits [10:0].                                                                                                     |

|------|--------------------|----|-------|-------------------------------------------------------------------------------------------------------------------------------------|

|      | D_Field            |    |       | These bits are encoded as Message Code Field<br>when bit[13] is set to 1, or as Unformatted<br>Code Field when bit[13] is set to 0. |

#### **MII REGISTER 08H: AUTO-NEGOTIATION LINK PARTNER**

#### **RECEIVED NEXT PAGE REGISTER**

| Bit  | Symbol             | Access             | Default | Description                                                                                                                         |

|------|--------------------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Next_Page          | RO                 | 1'b0    | Received Code Word Bit 15                                                                                                           |

|      |                    |                    |         | 1 = This page is not the last page                                                                                                  |

|      |                    |                    |         | 0 = This page is the last page                                                                                                      |

| 14   | Reserved           | RO                 | 1'b0    | Received Code V ord Bit 14                                                                                                          |

| 13   | Message_page_mode  | RO                 | 1'b0    | Received Code Word Bit 13                                                                                                           |

|      |                    |                    |         | 1 - Wie ssage Page                                                                                                                  |

|      |                    |                    |         | 0 = Unformatted Page                                                                                                                |

| 12   | Ack2               | RO                 | 1'b0    | Received Code Word Bit 12                                                                                                           |

|      |                    |                    |         | 1 = Comply with message                                                                                                             |

|      |                    | $\dot{\mathbf{x}}$ |         | 0 = Cannot comply with message                                                                                                      |

| 11   | Toggle             | 20                 | 1'b0    | Received Code Word Bit 11                                                                                                           |

|      |                    |                    |         | 1 = This bit in the previously exchanged Code<br>Word is logic 0                                                                    |

|      |                    |                    |         | 0 = The Toggle bit in the previously exchanged<br>Code Word is logic 1                                                              |

| 10:0 | Message_Unformatte | RO                 | 11'b0   | Received Code Word Bit 10:0                                                                                                         |

|      | D_Field            |                    |         | These bits are encoded as Message Code Field<br>when bit[13] is set to 1, or as Unformatted<br>Code Field when bit[13] is set to 0. |

#### **MII REGISTER 0AH: MASTER-SLAVE STATUS REGISTER**

| Bit | Symbol | Access | Default | Description |

|-----|--------|--------|---------|-------------|

|     |        |        |         |             |

| 15  | Master_Slave_Conf<br>iguration_Fault                       | RO RC<br>SWC<br>LH | 1'b0         | <ul> <li>This register bit will clear on read, rising of MII</li> <li>0.12 and rising of AN complete.</li> <li>1 = Master/Slave configuration fault detected</li> <li>0 = No fault detected</li> </ul> |

|-----|------------------------------------------------------------|--------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | Master_Slave_Conf<br>iguration_Resolutio<br>n              | RO                 | 1'b0         | This bit is not valid unless register $0x1$ bit5 is 1.<br>1 = Local PHY configuration resolved to Master<br>0 = Local PHY configuration resolved to Slave                                              |

| 13  | Local_Receiver_St atus                                     | RO                 | 1'b0         | 1 = Local Receiver OK<br>0 = Local Receiver not OK                                                                                                                                                     |

| 12  | Remote_Receiver_<br>Status                                 | RO                 | 1'b0         | 1 = Remote Receiver CK<br>0 = Remote Receiver not OK                                                                                                                                                   |

| 11  | Link<br>Partner_1000Base-<br>T_Full_Duplex_Ca<br>pability  | RO                 | 1'b0         | This bit is nor valid u iless register 0x1 bit5 is 1.<br>1 = Link Partner supports 1000BASE-T half<br>duplex<br>c = Link Partner does not support 1000BASE-T<br>half duplex                            |

| 10  | Link_Partner_1000<br>Base-<br>T_Half_Duplex_Ca<br>pability | RO                 | <u>л'</u> ьо | This bit is not valid unless register 0x1 bit5 is 1.<br>1 = Link Partner supports 1000Base-T full duplex<br>0 = Link Partner does not support 1000Base-T full<br>duplex                                |

| 9:8 | Reserved                                                   | RO                 | 2'b0         | Always 0                                                                                                                                                                                               |

| 7:0 | Idle_Er.or_Count                                           | RO SC              | 8'b0         | MSB of Idle Error Counter.<br>The register indicates the idle error count since the<br>last read operation performed to this register.<br>The counter pegs at 11111111 and does not roll<br>over.      |

#### MII REGISTER 0DH: MMD ACCESS CONTROL REGISTER

| Bit   | Symbol   | Access | Default | Description                                   |

|-------|----------|--------|---------|-----------------------------------------------|

| 15:14 | Function | RW     | 2'b0    | 00 = Address                                  |

|       |          |        |         | 01 = Data, no post increment                  |

|       |          |        |         | 10 = Data, post increment on reads and writes |

|      |          |    |      | 11 = Data, post increment on writes only |

|------|----------|----|------|------------------------------------------|

| 13:5 | Reserved | RO | 9'b0 | Always 0                                 |

| 4:0  | DEVAD    | RW | 5'b0 | MMD register device address.             |

|      |          |    |      | 00001 = MMD1                             |

|      |          |    |      | 00011 = MMD3                             |

|      |          |    |      | 00111 = MMD7                             |

#### MII REGISTER 0EH: MMD ACCESS DATA REGISTER

| Bit  | Symbol       | Access | Default | Description                                                                                                                                                                                             |

|------|--------------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | Address_data | RW     | 16'b0   | If register 0xD bits [15:14] are 00, this register<br>is used as MMD DEVAD address register.<br>Otherwise, this register is used as MMD<br>DEVAD data register as indicated by its address<br>register. |

## MII REGISTER OFH: EXTENDED STATUS REGISTER

| Bit  | Symbol        | Access | D2fa <sup>-</sup> ilt | Description                               |

|------|---------------|--------|-----------------------|-------------------------------------------|

| 15   | 1000Base-X_Fd | RO     | 1'b0                  | PHY not able to support 1000Base-<br>X_Fd |

| 14   | 1000Base-X_Hd | Ϋ́Ο    | 1'b0                  | PHY not able to support 1000Base-<br>X_Hd |

| 13   | 1000Base-T_F  | RO     | 1'b0                  | PHY not able to support 1000Base-<br>T_Fd |

| 12   | 1000Ba.e-1_Hd | RO     | 1'b0                  | PHY not able to support 1000Base-<br>T_Hd |

| 11:8 | Recerved      | RO     | 1'b0                  | Reserved                                  |

| 7    | 100Base-T1    | RO     | 1'b1                  | PHY able to support 100Base-T1            |

| 6    | 1000Base-T1   | RO     | 1'b0                  | PHY not able to support 1000Base-T1       |

| 5:0  | Reserved      | RO     | 6'b0                  | Reserved                                  |

#### MII REGISTER 10H: PHY SPECIFIC FUNCTION CONTROL

#### REGISTER

| Bit          | Symbol        | Access | Default | Description                                                                                                                                                                                                                                                                                                              |

|--------------|---------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:7         | Reserved      | RO     | 9'b0    | Always 0.                                                                                                                                                                                                                                                                                                                |

| 6:5          | Cross_md      | RW     | 2'b11   | Changes made to these bits disrupt normal<br>operation, thus a software reset is mandatory after<br>the change. And the configuration does not take<br>effect until software reset.<br>00 = Manual MDI configuration<br>01 = Manual MDIX configuration<br>10 = Reserved<br>11 = Enable a tomatic crossover for all modes |

| 4            | Int_polar_sel | RW     | 1'b0    | To control the polarity of interrupt PINs.<br>0 =when used as interrupt, INTn_LED is active<br>LOW;<br>1 = when used as interrupt, INTn_LED is active<br>HIGH.                                                                                                                                                           |

| 3            | Crs_on_tx     | RW     | 4'b0    | This bit is effective in 10BASE-Te half-duplex<br>mode and 100BASE-TX mode:<br>1 = Assert CRS on transmitting or receiving<br>0 = Never assert CRS on transmitting, only assert<br>it on receiving.                                                                                                                      |

| <sup>2</sup> | En_sqe_test   | RW     | 1'b0    | <ul> <li>1 = SQE test enabled</li> <li>0 = SQE test disabled</li> <li>Note: SQE Test is automatically disabled in full-<br/>duplex mode regardless the setting in this bit.</li> </ul>                                                                                                                                   |

| 1            | En_pol_inv    | RW     | 1'b1    | If polarity reversal is disabled, the polarity is<br>forced to be normal in 10BASE-Te.<br>1 = Polarity Reversal Enabled<br>0 = Polarity Reversal Disabled                                                                                                                                                                |

| 0 | Dis_jab | RW | 1'b0 | Jabber takes effect only in 10BASE-Te half-<br>duplex mode. |

|---|---------|----|------|-------------------------------------------------------------|

|   |         |    |      | 1 = Disable jabber function                                 |

|   |         |    |      | 0 = Enable jabber function                                  |

#### MII REGISTER 11H: PHY SPECIFIC STATUS REGISTER

| Bit   | Symbol                        | Access | Default | Description                                                                                                                                                                    |

|-------|-------------------------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:14 | Speed_mode                    | RO     | 2'b00   | These status bits are valid only when any<br>bit in bit9:7 and bit3:2 is 1.<br>11 = Reserved<br>10 = 1000  Mbps<br>$01 = 100^{-1} \text{ Mbps}$<br>$00 = 10^{-1} \text{ Mbps}$ |

| 13    | Duplex                        | RO     | 1'b0    | This status bit is valid only when bit11 is<br>1. Bit11 is set when Auto-Negotiation is<br>completed or Auto-Negotiation is disabled.<br>1 = Full-duplex<br>0 = Half-duplex    |

| 12    | Page_Received<br>_real-time   | RO     | 1'b0    | 1 = Page received<br>0 = Page not received                                                                                                                                     |