# 搭载ARM Cortex-M4/M0和16位ADC的混合信号双核控制处理器

# ADSP-CM411F/412F/413F/416F/417F/418F/419F

### 系统特性

高达240 MHz ARM Cortex-M4,搭载浮点单元、高达160KB零等待状态ECC SRAM

基于安全的独立双核概念

高达1 MB高性能ECC FLASH,可以近SRAM速度执行指令

极高的精度、低延迟31通道模拟前端

100 MHz ARM Cortex-M0监控器内核,带32KB零等待状态 ECC SRAM

3.3 V单电源供电

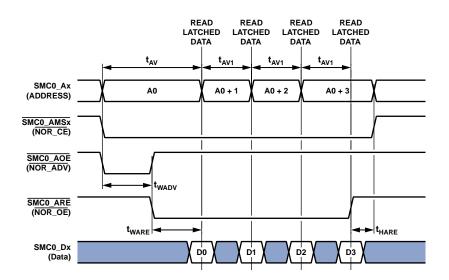

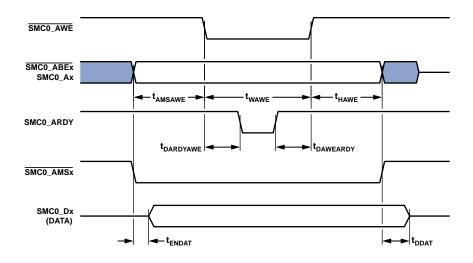

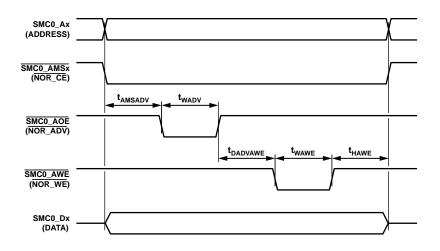

静态存储控制器(SMC)具有异步存储器接口,支持8位和16位 存储器

增强的24通道精密PWM单元

4个3阶或4阶SINC滤波器,可无缝连接Σ-Δ型调制器

基于硬件的谐波分析引擎

逻辑模块阵列(LBA)

FFT信号频谱监控器

#### MATH功能模块

2个CAN 2.0B接口和最多5个UART

2个串行外设接口(SPI兼容)端口

4个编码器接口,其中2个带分频功能

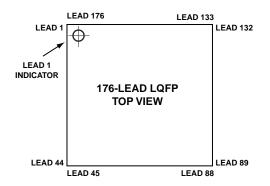

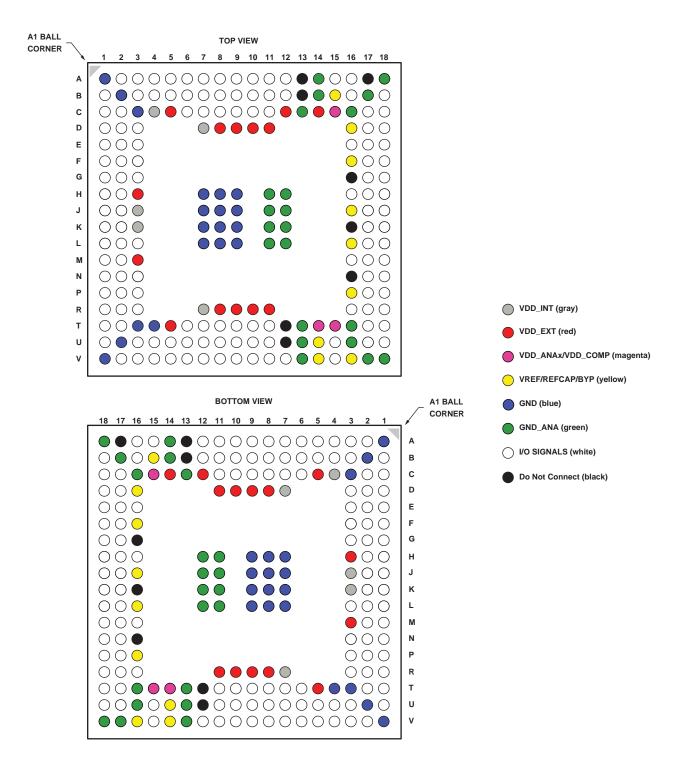

封装选项:

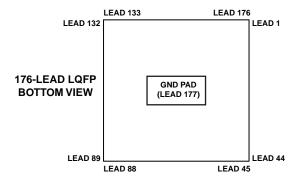

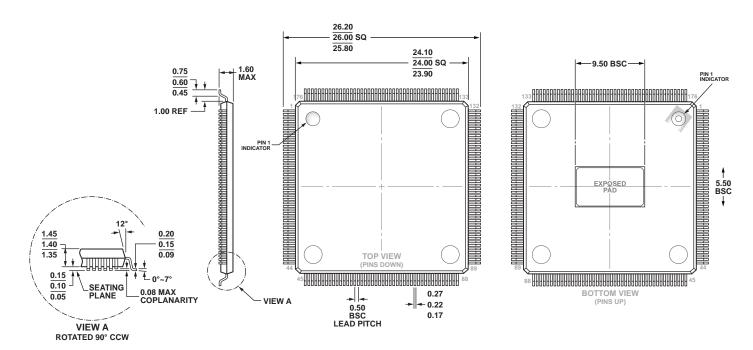

176引脚(24 mm×24 mm)LQFP封装

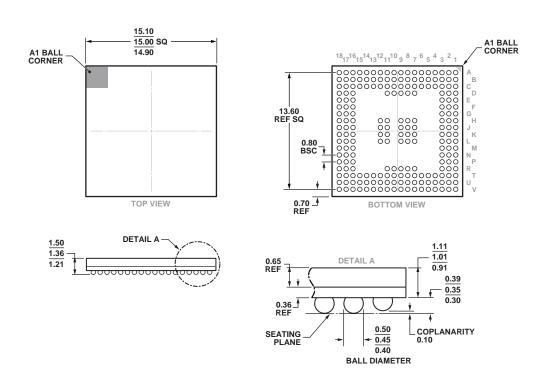

210引脚(15 mm×15 mm)BGA封装

### 模拟前端

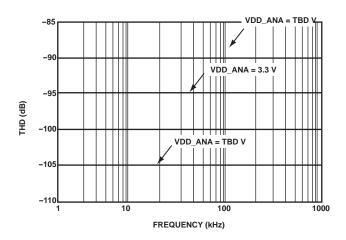

16位模数转换器,带24个多路复用输入,支持6路同步采样和 6通道转换(1.4 μs)

独立、14位、7通道辅助模数转换器,带7个输入 ADC控制器(ADCC0/ADCC1)和DAC控制器(DACC0) 12位DAC 最多3个2.5 V精密基准电压源输入

(详情请参见64页上的ADC/DAC/基准电压源/比较器规格。)

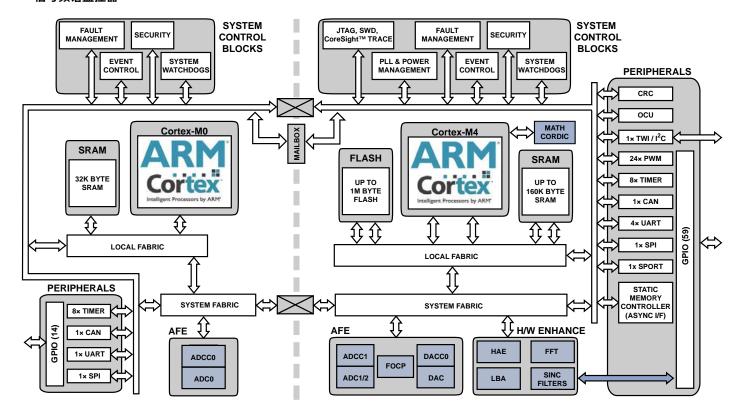

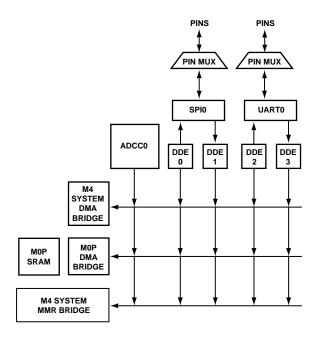

图1. ADSP-CM41xF功能框图

Rev. PrB

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. Tel: 781.329.4700 ©2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# 目录

| 概述3                         |

|-----------------------------|

| 模拟前端4                       |

| 双核系统架构10                    |

| EmbeddedICE                 |

| 处理器基础结构13                   |

| 存储器架构17                     |

| 系统加速19                      |

| 安全特性19                      |

| 功能安全特性19                    |

| 处理器外设21                     |

| 时钟和电源管理24                   |

| 系统调试26                      |

| 开发工具26                      |

| 其它信息26                      |

| 相关信号链27                     |

| 安全特性免责声明27                  |

| ADSP-CM41xF详细信号描述28         |

| ADSP-CM412F/CM413F/CM416F/  |

| CM417F 176引脚LQFP信号描述31      |

| ADSP-CM412F/CM413F/CM416F/  |

| CM417F 176引脚LQFP GPIO多路复用38 |

| ADSP-CM411F/CM418F/         |

| CM419F 210引脚BGA信号描述41       |

|                             |

|                             |

| 修订历史                        |

| 2/16—修订版PrA至修订版PrB          |

| 更新系统特性1                     |

| 更新模拟前端1                     |

| 更新表1、产品特性3                  |

| 修改模拟前端中的图例4                 |

| 增加模拟前端图例4                   |

| 增加时序规格72                    |

| ADSF-CM411F/CM410F/       |     |

|---------------------------|-----|

| CM419F 210引脚BGA GPIO多路复用  | 47  |

| ADSP-CM41xF设计器快速参考        | 50  |

| 技术规格                      | 60  |

| 工作条件                      | 60  |

| 电气特性                      | 62  |

| ADC/DAC/基准电压源/比较器规格       | 64  |

| 闪存规格                      | 70  |

| 绝对最大额定值                   | 71  |

| ESD灵敏度                    | 71  |

| 封装信息                      | 71  |

| 时序规格                      | 72  |

| 环境条件                      | 103 |

| ADSP-CM41xF 176引脚LQFP引脚分配 | 104 |

| 按引脚编号顺序                   | 104 |

| 按引脚名称顺序                   | 106 |

| ADSP-CM41xF 210引脚BGA引脚分配  | 108 |

| 按引脚编号顺序                   | 108 |

| 按引脚名称顺序                   | 110 |

| 外形尺寸                      |     |

| <b>新</b> 发布产品             | 115 |

### 概述

ADSP-CM41xF系列混合信号控制处理器基于ARM® Cortex-M4TM处理器内核,浮点单元工作频率高达240 MHz, ARM® Cortex-M0TM处理器内核工作频率高达100 MHz。处理器集成搭载ECC的最高160KB SRAM存储器、集成ECC的1 MB內存,以及专门针对电机控制和光伏(PV)逆变器控制应用而优化的加速器和外设以及由两个16位SAR型ADC、一个14位M0 ADC和一个12位DAC组成的模拟模块。ADSP-CM41xF系列采用单电源供电,用内部稳压器和一个外部调整管自行生成内部电压源。

ADSP-CM41xF混合信号控制处理器集成了许多业界领先的系统外设和丰富的存储器(如表1所示),在一个集成封装中提供RISC式编程能力和先进的信号处理能力,堪称新一代应用的首选平台。这些应用涵盖众多功率转换市场领域,包括太阳能PV逆变器、电机/功率控制和电池充电/控制应用。

表1列出了各型号的产品特性。

表1.产品特性

| 通用                            |      | SP-<br>111F |       | )SP-<br>412F |        | SP-<br>413F |        | SP-<br>416F |       | SP-<br>41 <i>7</i> F |       | SP-<br>118F |       | SP-<br>419F |

|-------------------------------|------|-------------|-------|--------------|--------|-------------|--------|-------------|-------|----------------------|-------|-------------|-------|-------------|

| 封装类型                          | 210引 | 脚 BGA       |       |              | 1      | 76引脚        | LQFP   |             |       |                      |       | 210引        | 脚 BGA |             |

| 工作温度范围(T <sub>AMBIENT</sub> ) |      |             | •     |              |        |             | -40°C至 | +105°0      | -     |                      |       |             |       |             |

| 处理器                           |      |             |       |              |        |             |        |             |       |                      |       |             |       |             |

| 处理器类型                         |      | 单核          | : ARN | /I Corte     | k-M4   |             |        | 双核:         | ARM C | Cortex-N             | M4、AR | M Cort      | ex-M0 |             |

| M4处理器特性码                      | Α    | В           | Α     | В            | В      | C           | В      | C           | C     | D                    | В     | C           | C     | D           |

| M4 L1 SRAM (KB)               | 128  | 128         | 128   | 128          | 128    | 160         | 128    | 160         | 160   | 160                  | 128   | 160         | 160   | 160         |

| M4 Flash (KB)                 | 256  | 256         | 256   | 256          | 256    | 512         | 256    | 512         | 512   | 1024                 | 256   | 512         | 512   | 1024        |

| M4内核时钟(MHz)                   | 180  | 240         | 180   | 240          | 240    | 240         | 240    | 240         | 240   | 240                  | 240   | 240         | 240   | 240         |

| M0内核时钟(MHz) <sup>1</sup>      | 不适   | 不适          | 不适    | 不适           | 不适     | 不适          | 100    | 100         | 100   | 100                  | 100   | 100         | 100   | 100         |

|                               | 用    | 用           | 用     | 用            | 用      | 用           |        |             |       |                      |       |             |       |             |

| 模拟功能                          |      |             |       |              |        |             |        |             |       |                      | -     |             |       |             |

| 16位ADC同步采样                    |      |             | -     |              | 3路 (2. | 7 Msps)     |        |             | -     |                      | 6     | 5路 (4.3     | Msps) |             |

| 16位ADC输入                      | 2    | 24          | :     | 24           | 2      | 24          | 2      | 24          | 2     | 4                    | 2     | 4           | 2     | 4           |

| 16位ADC ENOB                   | 1    | 1+          | 1     | 1+           | 1      | 3+          | 1      | 1+          | 13    | 3+                   | 1     | 1+          | 1.    | 3+          |

| 14位ADC输入                      |      | 7           |       | 7            |        | 7           |        | 7           |       | 7                    | 7     | 7           |       | 7           |

| DAC输出                         |      | 1           |       | 1            |        | 1           |        | 1           |       | 1                    |       | 1           |       | 1           |

| FOCP(快速过流保护)                  |      | 3           |       | 3            |        | 3           |        | 3           |       | 3                    | 3     | 3           |       | 3           |

| 数字功能                          |      |             |       |              |        |             |        |             |       |                      |       |             |       |             |

| GPIO(通用I/O)                   | 7    | '3          | 7     | 73           | 7      | 73          | 7      | '3          | 7     | <b>'</b> 3           | 7     | '3          | 7     | 73          |

| PWM(脉宽调制器输出)                  | 2    | 24          | ] :   | 24           | 2      | 24          | 2      | 24          | 2     | 4                    | 2     | 4           | 2     | 4           |

| HAE(谐波分析引擎)                   | (    | )           |       | 0            |        | 1           |        | 1           |       | 1                    |       | 1           |       | 1           |

| CORDIC                        |      | 1           |       | 1            |        | 1           |        | 1           |       | 1                    |       | 1           |       | 1           |

| FFT电弧检测                       | (    | )           |       | 0            |        | 0           |        | 1           |       | 1                    |       | 1           |       | 1           |

| SINC3或SINC4滤波器输入              | 4    | 4           |       | 4            |        | 4           |        | 4           |       | 4                    | 4     | 4           |       | 4           |

| CAN                           |      | 2           |       | 2            |        | 2           | ;      | 2           |       | 2                    | 2     | 2           |       | 2           |

| UART                          |      | 3           |       | 3            |        | 5           |        | 5           |       | 5                    | į     | 5           |       | 5           |

| SPI                           |      | 2           |       | 2            |        | 2           | :      | 2           | ] :   | 2                    | :     | 2           |       | 2           |

| $I^2C$                        |      | 1           |       | 1            |        | 1           |        | 1           |       | 1                    |       | 1           |       | 1           |

| GP定时器(通用)                     |      | 8           |       | 8            |        | 8           | 1      | 6           | 1     | 6                    | 1     | 6           | 1     | 16          |

| SPORT(串行端口)                   |      | 1           |       | 1            |        | 1           |        | 1           |       | 1                    |       | 1           |       | 1           |

| 16位EBIU                       |      | 1           |       | 1            |        | 1           |        | 1           |       | 1                    |       | 1           |       | 1           |

<sup>1</sup> NA = 不适用

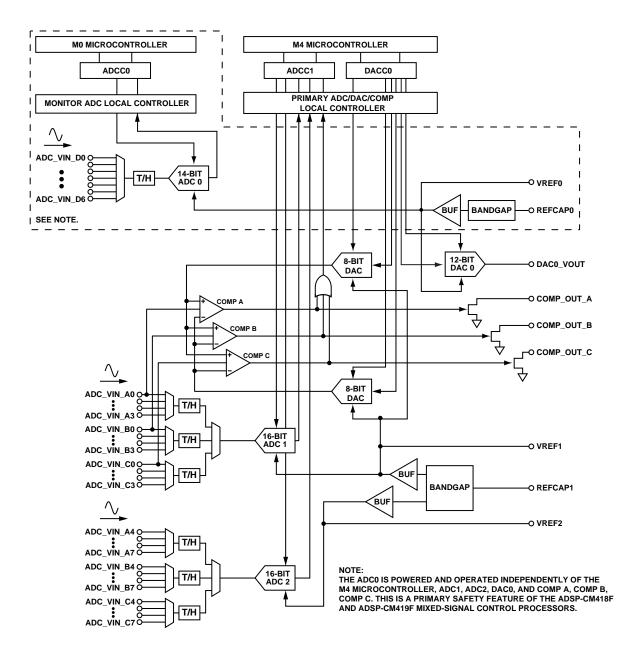

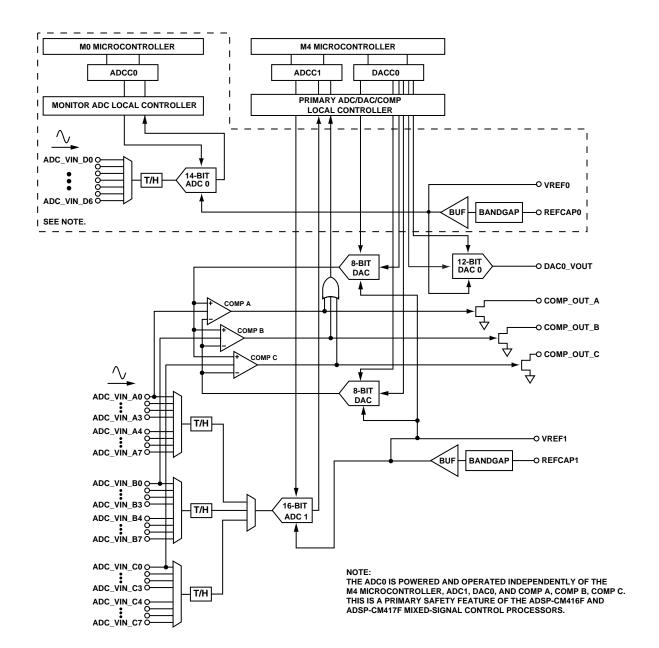

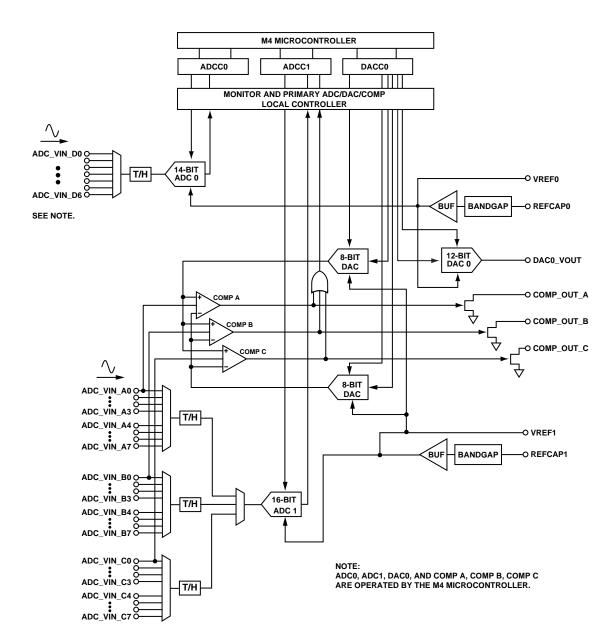

### 模拟前端

处理器集成一个附属于M0内核的ADC,以及附属于M4内核的两个ADC和一个DAC。两个强大的片内模数转换控制器(ADCC)和一个数模转换控制器(DACC)简化了对这些数据转换器的控制。ADCC和DACC无缝集成到软件编程模型中,而且可以高效地管理ADC和DAC的配置和实时运行。

(技术详情请参见64页上的ADC/DAC/基准电压源/比较器规格。)

M4内核的ADCC提供了对ADC上的模拟采样事件时序和执行进行精确控制的机制。ADCC支持最多6通道同步采样(ADC1、ADC2各3通道),可在1.4 μs内向存储器提供6通道同步采样ADC数据,或者在3.0 μs内向存储器提供16通道同步采样对。来自ADC的转换数据既可以通过DMA路由至存储器,也可以通过处理器路由至一个目标寄存器,或者不通过处理器干预而直接写入任何目标寄存器(比如写入FFT)。ADCC可以配置为,使两个ADC同时或不同时对两个模拟输入端进行采样和转换,并且支持异步或同步工作模式。在同步模式下可取得全时匹配性能。

类似地,DACC连接一个外部连接的DAC和两个内部连接 的阈值DAC,其作用是管理这些DAC。以DAC为目标的转 换数据既可能是借道DMA、来自存储器,也可能借道处理 器、来自一个源寄存器。

有关ADCC和DACC的运行和编程情况,详见《搭载ARM Cortex-M4的ADSP-CM41x混合信号控制处理器硬件参考手册》。

ADC和DAC的特性和性能规格因处理器型号而异。 ADCC、DACC以及ADC和DAC的简化框图如图2、图3和图4所示。

### 获得最佳转换器性能的考虑因素

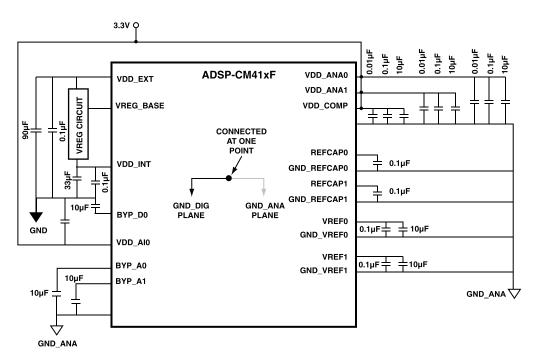

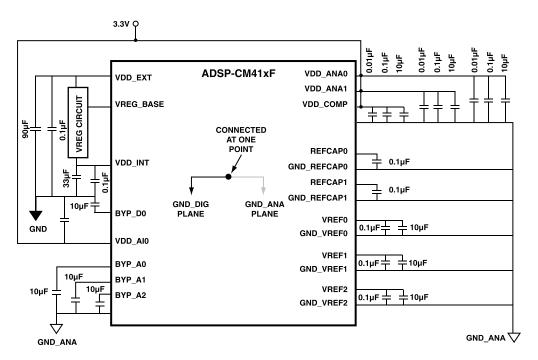

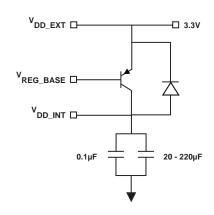

如同任何高性能模拟/数字电路,为了获得最佳性能,应当遵循良好的电路设计和电路板布局实践。电源及其噪声旁路(去耦),接地返回路径和引脚连接,以及模拟/数字路由通道路径和信号屏蔽,这些都是首要考虑因素。有关最佳设计实践的应用提示,请参见图5和图6,以及《搭载ARM Cortex-M4/M0的ADSP-CM41x混合信号控制处理器硬件参考手册》通常情况下不会有硬件参考手册的中文版,所以附上英文标题。有关VREG电路的更多信息,请参见第26页的图18:内部稳压器电路。

### 快速过流保护(FOCP)

对于特定输入,若要满足采样速率要求,则需要使用FOCP模块。FOCP提供三个比较器。每个比较器的输入均内部连接A0、B0和C0的输入。比较器具有公共的上限阈值(LIMIT\_U)和公共的下限阈值(LIMIT\_L),通过内部8位DAC设置。COMP\_OUT\_A/B/C输出为用户可访问。如果一个或多个比较器正在指示"LIMT"—越界(通过可用的COM-P\_OUT\_A/B/C),则AFE向处理器置位一次中断。

### 模拟前端(AFE)模块

ADC模块包含两个主ADC(ADC1和ADC2),每一个ADC都有三个多路复用采样保持(T/H)单元,每个T/H均可采样最多8个模拟输入。此外,ADC模块还集成完全独立的监控器ADC(ADC0),前置一个7通道输入多路复用器。有关性能规格的详情,请参见第64页的ADC规格——ADC0、ADC1、ADC2。

图2. 模拟前端功能框图(ADSP-CM418F/CM419F双核, 6路采样)

图3. 模拟前端功能框图(ADSP-CM416F/CM417F双核, 3路采样)

图4. 模拟前端功能框图(ADSP-CM411F/CM412F/CM413F单核, 3路采样)

图5. 典型电源配置(ADSP-CM411F、ADSP-CM412F、ADSP-CM413F、ADSP-CM416F、ADSP-CM417F)

图6. 典型电源配置(ADSP-CM418F、ADSP-CM419F)

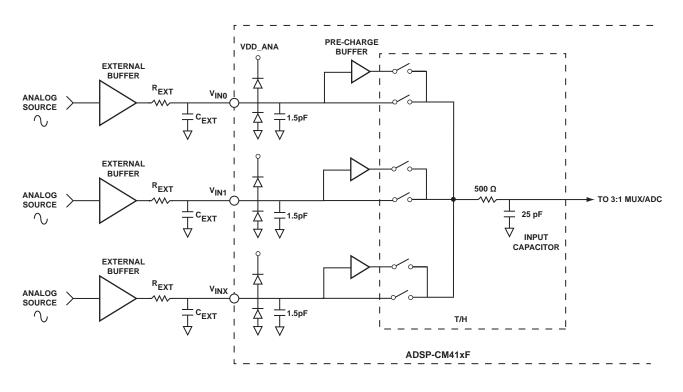

模拟输入的电压输入范围要求为0 V至3.0 V。所有模拟输入都采用相同的单端设计。就如所有单端输入一样,来自高阻抗源的信号是最难控制的,而且根据电气环境的不同,可能需要一个外部缓冲电路来进行信号调理(图7)。集成预充电缓冲器,协助外部缓冲器进行25 pF输入电容充电。可以通过软件禁用预充电特性。

### DAC模块

DAC采用12位、低功耗串式DAC设计。DAC的输出进行了缓冲,可以将R/C负载驱动至地或 $V_{DD\_ANA}$ 。有关性能规格,详见第66页"DAC规格"部分。

图7. 等效单端输入(简化)

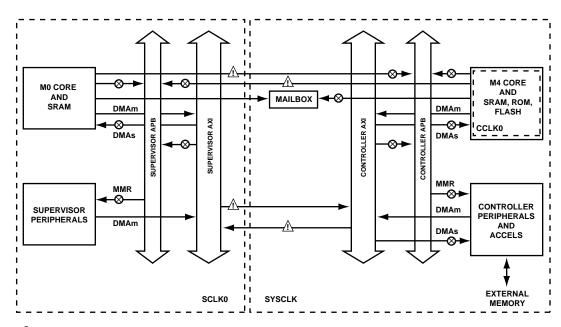

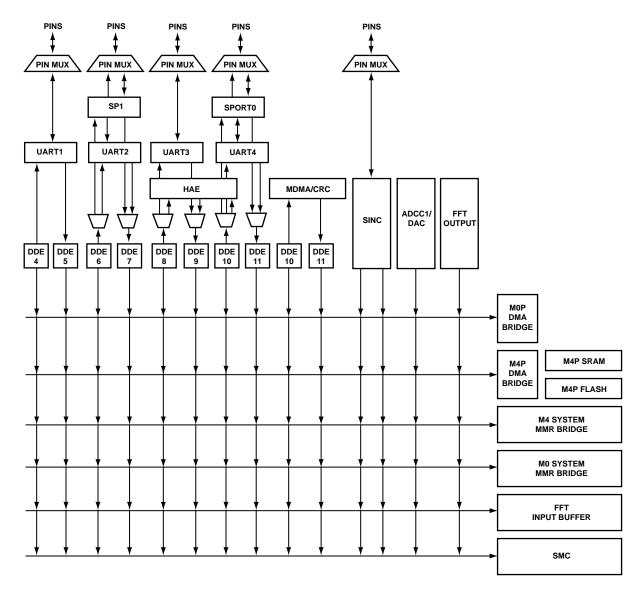

### 双核系统架构

ADSP-CM41xF产品可能集成一个ARM Cortex-M4内核,也可能集成两个ARM Cortex内核——一个M4和一个M0。在双核产品中,系统架构在功能上进行划分,以便每个内核能够可靠、独立地工作(图8)。通过系统保护资源(SPU和SMPU),编程器可以在两个处理器之间分段任意控制系统资源,并可向下直达单个外设和存储器区域。针对DMA从机的访问可以进行类似的调节。可编程总线超时保护保证了内核域之间的确定性访问完成时间,哪怕一个域中存在硬件故障。

每一个处理器均配备了基本的基础设施:本地SRAM、一组通信外设(每个外设至少有一个UART、CAN和SPI)、触发路由单元(TRU)、看门狗定时器(WDT)、系统事件控制器(SEC)、ADC控制器(ADCC)和AFE上的独立ADC,以及本地APB和AXI总线结构。邮箱存储器在两个子系统之间提供共享存储器桥,用于令牌和消息。在子系统之间有多个通用中断和触发,支持选择性通信。

主系统AXI结构提供两个子系统之间的通用存储器互连,显示含有全部系统资源(内部或紧密耦合至ARM内核除外)的两个处理器的统一存储器映射。

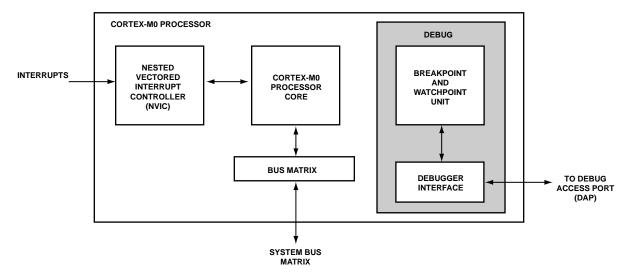

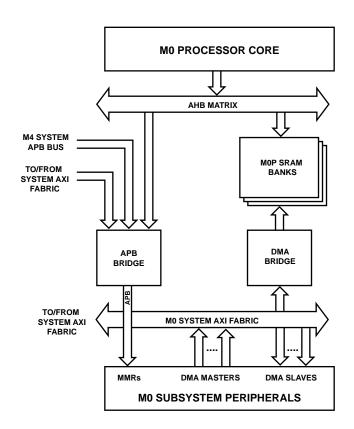

### ARM Cortex-M0内核

ARM Cortex-M0为32位超低门数精简指令集计算机(RISC)。 指令和数据使用32位总线。数据的长度可以是8位、16位或 32位。指令字的长度为16位或32位。

M0子系统(图9)由M0内核(图10)、本地M0P平台SRAM及其通信外设(SPI、UART、CAN)、仪表(ADCC)和基础设施(SEC、TRU、WDT)构成。M0子系统以高达100 MHz的速度工作在其SCLK0时钟域内。本地AXI结构支持本地外设和M0P SRAM之间的DMA,并通过紧密耦合存储器AHB总线矩阵独立于M0处理器的SRAM连接。M0P SRAM由SEC\_DED ECC通过硬件提供保护。SRAM的多模块条状结构支持无模块冲突时的并发内核和DMA访问。M0子系统APB和AXI结构连接ADSP-CM41x系统,支持输入APB和DMA传输(作为DMA从机)以及输出DMA传输(作为DMA主机)。DMA访问延迟受限于固定延迟优先移位机制。多个通用触发和中断信号还可在两个方向上跨越边界。

ARM Cortex-M0控制器特性参见第12页上的章节描述。

⚠ TIMEOUT PROTECTION

图8. ADSP-CM41xF双核ARM架构

图9. ARM Cortex-M0内核

图10. ADSP-CM41xF ARM Cortex-M0内核存储器子系统(SCLK0时钟域)

#### Cortex-M0架构

- Thumb-2 ISA技术

- 向上兼容其余的Cortex系列

- 32周期乘法器,针对低电平区域优化设计

- NVIC中断控制器(32个中断和4个优先级)支持75个中 断源,并带有辅助多路复用

- CoreSight™调试、断点、观察点和交叉触发

#### 微架构

- 3级流水线,带分支预测

- 低延迟中断处理

- 冯诺依曼架构

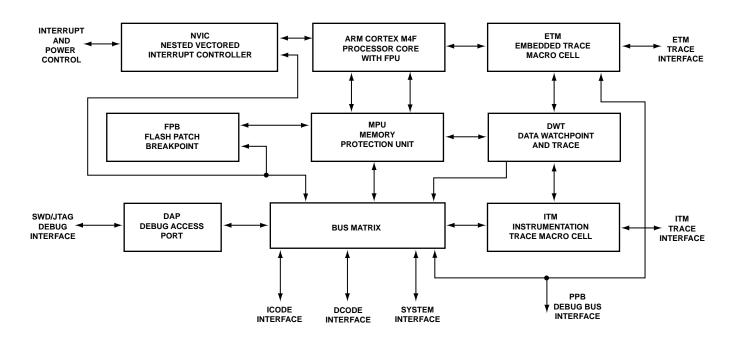

### ARM Cortex-M4内核

ARM Cortex-M4内核(图11)为32位精简指令集计算机(RISC)。 指令和数据使用32位总线。数据的长度可以是8位、16位或 32位。指令字的长度为16位或32位。

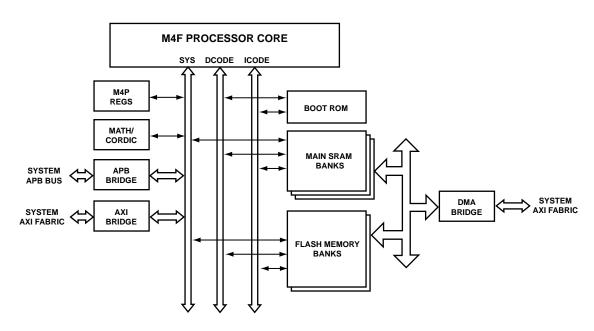

M4F内核存储器子系统(图12)由M4内核(图11)、主存储器组、MATH/CORDIC协处理器和M4P子系统控制/状态寄存器组成。M4F子系统以高达240 MHz的速度工作在其CCLK0时钟域内。主存储器组由ECC保护、20路主SRAM组、引导ROM和两组ECC保护Flash存储器组成。主存储器支持

M4任意三个AHB总线(ICODE、DCODE和SYS)的同时访问,并支持通过系统AXI结构进行DMA从机访问,除非发生模块访问冲突。(然而,系统DMA无法访问引导ROM。) DMA访问延迟受限于可编程优先移位机制。M4F子系统还集成MATH/CORDIC协处理器,能够加速IEEE单精度浮点超越函数。子系统通过APB总线桥接ADSP-CM41x系统外设和基础设施,实现MMR访问;并通过AXI总线桥接实现ADSP-CM41x从机存储器空间(SMC、FFT、HAE和M0P)的访问。

ARM Cortex-M4控制器特性在下节中描述。

#### Cortex-M4架构

- Thumb-2 ISA技术

- DSP和SIMD扩展

- 单周期MAC(最多32×32+64=>64)

- 硬件除法指令

- 单精度FPU

- NVIC中断控制器(129个中断和16个优先级)

- 存储器保护单元(MPU)

- 全面的CoreSight调试、跟踪、断点、观察点和交叉触发

图11. ARM Cortex-M4内核

### 微架构

- 3级流水线,带分支推测

- 低延迟中断处理, 带尾链

### 可配置以支持超低功耗模式

- 深度睡眠模式, 动态电源管理

- 可编程时钟发生器单元

#### **EmbeddedICE**

EmbeddedICE<sup>®</sup>支持内核片內调试。EmbeddedICE模块包含 断点和观察点寄存器,在调试时这些寄存器可使代码中止 执行。这些寄存器可以通过JTAG和SWD测试端口来控制。

当遇到一个断点或观察点时,处理器中断,并进入调试状态。一旦进入调试状态,就可以检查处理器寄存器、Flash/EE、SRAM和存储器映射寄存器的状态。

图12. ADSP-CM41xF ARM Cortex-M4内核存储器子系统(CCLK0时钟域)

### 处理器基础结构

ADSP-CM41xF处理器基础设施支持两种类型的DMA连接: 通用DMA和优化DMA。以下部分说明有关ADSP-CM41xF处理器基本组成的信息。

### 通用DMA控制器(DDE)

处理器包含12个外设DMA通道,每通道使用一个DDE引擎,外加一个存储器间(MDMA)流,带两个DDE控制器和CRC。DDE通道0-3(图13)用于M0子系统中的外设DMA,通道4-11用于M4子系统中的外设DMA,DDE通道12-13用于MDMA(图14)。

DMA基础设施支持DMA主机(外设、内核)针对从机存储器空间(主/M0 SRAM、片外SMC SDRAM,以及加速器内嵌存储器)以完全矩阵的方式进行同步访问(图13、图14)。DMA结构并发支持每个从机存储器空间每次系统时钟周期的无冲突单次访问。

14个DDE引擎每一个都集成独立的数据FIFO。外设DDE中,每个FIFO的一端直接连接外设,另一端独立连接系统结构。这样可以最大程度提升实时外设性能,因为外设至FIFO连接不消耗系统总线带宽即可接受或提供外设数据。

CRC引擎连接MDMA DDE,可在传输时或有数据存在时验证数据缓冲器内容(比如验证Flash存储器)。

为了反映用户的外设引脚多路复用选择,单个DDE可在最多3个外设之间进行相似的多路复用(图14)。这便允许以较少数量的DDE高效支持较大数量的外设DMA端点,同时保证通过引脚多路复用连接引脚的任何外设组都始终有DDE的支持。

所有ADSP-CM41xF处理器DDE均支持一组强大的寻址和控制选项:

- 以32位递增进行32位寻址

- 以独立的X、Y计数和失调进行1-D或2-D寻址

- · X\_row或XY-阵列传输完成时可选择中断

- 系统存储器中通过阵列或描述符链路列表控制描述符 (分散/聚集)DMA模式

- 自动缓冲模式一旦开始便可在无需处理器介入的情况 下连续传输数据

- 根据任意硬件或软件TRU事件触发从机模式进而开启 DMA

- 触发主机模式,可根据X-行或XY-阵列的完成情况发出TRU触发

图13. ADSP-CM41xF ARM Cortex-M0 DMA

### 优化DMA控制器

高性能系统外设和加速器具有不同的存储器处理需求,而中心化的万用DMA控制器无法满足要求。在ADSP-CM41xF处理器中,下列系统元件集成了DMA能力,并根据处理器单元的特定功能进行了定制:

- ADCC: ADC控制器在每一个定时器的多样本帧时将数据结构写入存储器,用户可以任意设计帧内样本布局。可以在循环缓冲器内安排两个或多个样本帧,每N个帧一次中断,或者生成不受限的样本帧输出缓冲器阵列,后跟完成时的一次中断。

- SINC: 类似地,SINC单元为每一个定时器将数据结构写入存储器——每一个均含有滤波器输出样本,用于一个至四个Σ-Δ输入流。这些帧能以循环或线性方式排列,每一个数据帧均有中断。

- FFT: FFT加速度计不仅接受来自系统任意存储器主机(包括ADCC)的输入时域数据,还可在加速度计每一次完成操作时输出频谱数据至M4、M0或SMC存储器。

- DACC: DAC控制器含有DMA控制器,能以线性或循环缓冲器的方式从存储器读出16位或32位步长的数据。可以开启每个数据样本的中断。

#### DMA并发

在处理器架构中,M4和M0存储器和系统结构的设计能够确保高并发操作。SRAM存储器分割为最多20个独立的阵列组,采用4路LSB地址带和最多5路MSB地址带相结合的方式。这表示针对SRAM的寻址可以最多有4路并发进行而不会产生任何停顿,包括M4的一个系统DMA和三个AHB总线,前提是不存在两个寻址操作同时访问一个物理阵列组的情况。MSB地址带意味着对不同的32 KB范围进行寻址永远不会产生停顿。LSB地址带意味着针对这些范围内的并发访问几乎不会互相冲突(例如ICODE与DCODE访问。)

图14. ADSP-CM41xF ARM Cortex-M4 DMA

另外,DMA通常与内核活动有所不同,哪怕出现结构访问冲突也是如此,但采用时间受限的方式。在几乎所有ARM-Mx代码应用中,DMA可在请求的一个或两个周期内完成,不会出现处理器停顿的现象——这是因为部署了存储器组分区。然而,如果一种罕见的Mx应用的访问模式影响DMA的时间超过了可编程阈值,则DMA会使处理器停顿,以便系统内的DMA实时最大延迟能够得到绝对限制。

### 系统事件控制器(SEC)

SEC通过其集成故障管理单元对系统故障源的使能和路由 进行管理。

每一个处理器内核都有独立的SEC(M0有SEC0, M4有SEC1),允许每一个内核保持对所有相关中断和故障源的硬件自主监控。

SEC允许每一个内核使能每一个故障源的通知并对其进行优先级分配,以识别最高优先级有源故障,以及对每一次内核事件进行连贯标记。可编程延迟过后,可以选择非处理事件以使SYS\_FAULT输出置位,以及/或者通过TRU触发通知其它内核发生了事件处理故障。

故障/事件处理机制还可以扩展至片外源,方法是使用双向 开漏SYS\_FAULT引脚。若使能,则当此引脚外部拉低时, 某一个或全部两个内核都可以被通知到。

### 触发路由单元(TRU)

TRU提供系统级序列控制,无需内核干预。TRU将触发主机(触发产生者)映射到触发从机(触发接收者)。从机端点可以通过多种方式响应触发。触发事件还可作为通用触发脉冲(GTP)从一个TRU路由至另一个。TRU支持的常见应用包括:

- 在每一个PWM周期或根据外部事件周期性启动ADC 采样

- 控制功能安全机制

- 一个DMA通道的序列完成后,自动触发另一个DMA 序列开始

- 软件触发

- 同时发生的活动的同步

### 触发时序单元(TTU)

TTU提供了分割、延迟和生成周期性TRU触发模式的灵活机制。8个TRU输出可以关联任意4个触发组,TRU触发输入可以让其工作。触发组可以配置为单次模式,每一个分配的触发输出具有包含SYSCLK分辨率的独立延迟。或者,可以将任意触发组配置为周期性工作,每一个分配的触发输出具有独立的正延迟或负延迟,可超前或滞后于基准定时器。

TTU的一种常见用法是用来精确控制多个外设活动的相对时间。例如,TTU能够以精确的时间偏移获取ADC样本,可用来同步多个PWM单元的周期性操作。

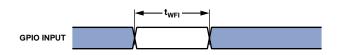

### 引脚中断(PINT)

处理器的每个端口引脚都可以通过边沿敏感或电平敏感方式请求中断,极性可编程。中断功能与GPIO操作分离。6个系统级中断通道(PINT0-5)专门用于此目的。每个中断通道最多可以管理32个中断引脚。中断的引脚分配不是在单个引脚基础上进行,而是以8个引脚为一组(半个端口),灵活地分配给中断通道。

每个引脚中断通道都有一组特殊的32位存储器映射寄存器,用于支持半端口分配和中断管理,包括请求的屏蔽、识别和清除。通过这些寄存器还可以访问相应引脚的状态,并使用中断锁存器,无论中断屏蔽与否。多数控制寄存器具有多个MMR地址条目,以便"写1设置"或"写1清除"。

#### 诵用I/O (GPIO)

每个通用端口引脚都可以通过操纵端口控制、状态和中断 寄存器进行控制:

- GPIO方向控制寄存器 指定各GPIO引脚的方向:输入或输出。

- GPIO控制和状态寄存器 "写1修改"机制支持通过 单一指令来修改GPIO引脚的任意组合,而不会影响 其它GPIO引脚的电平。

- GPIO中断屏蔽寄存器 允许各GPIO引脚用作处理器的中断。定义为输入的GPIO引脚可以用来产生硬件中断,输出引脚则可以由软件中断触发。

- GPIO中断敏感性寄存器——指定各引脚是对电平敏感还是对边沿敏感;如果是对边沿敏感,则还要指定仅信号的上升沿有意义还是上升沿和下降沿均有意义。

- GPIO上拉使能引擎——使能独立引脚的弱上拉。

#### GPIO可编程驱动强度

所选GPIO(包括PWM引脚)支持可编程二级驱动强度能力, 能够进而支持光隔离接口器件的无缝驱动。

### 引脚复用

处理器支持灵活的复用方案,各种外设可以复用GPIO引脚。 最多5个外设加上GPIO功能可以共享一个GPIO引脚。所有 GPIO引脚都有旁路特性——也就是说,当一个GPIO引脚 的输出使能和输入使能均有效时,引脚驱动器之前的数据 信号会被回送到该GPIO引脚的接收路径。

更多信息请参见:

- ADSP-CM411F/CM418F/CM419F 210引脚BGA GPIO 多路复用(第47页)。

- ADSP-CM412F/CM413F/CM416F/CM417F 176引脚LQFP GPIO多路复用(第38页)。

#### GPIO引脚安全状态序列

每一个ADSP-CM41xF GPIO支持检测到一系列故障之后的故障安全机制,引脚可以编程驱动预选的0、1或Z等安全状态。该安全状态事件可以进一步编程为立即或延迟,全局延迟编程设置为大约以1 μs为单位,并以片上RC振荡器定时。这样可以支持任意引脚状态的二步序列故障响应,并以1 μs至15 μs为间隔。故障响应完全独立于处理器、处理器时钟(PLL和晶振),甚至独立于VDDINT电源,仅需3 V VDDEXT电源。

可以选择触发引脚安全状态响应的系列故障包括: VDDINT或VDDEXT上的VMU检测电源故障;系统 SYS\_CLKIN0输入的OSCWDOG检测主要故障(丢失或错误 的谐波码);

系统时钟或PLL故障的OCU检测精确细节故障,以及触发路由单元路由的任意硬件检测故障或软件引起的事件。

由于这些类型的故障可能会影响一个或两个处理器内核的正常工作,因此它们被称为不可恢复故障,只能通过 SYS\_HWRST硬复位引脚置位清除。

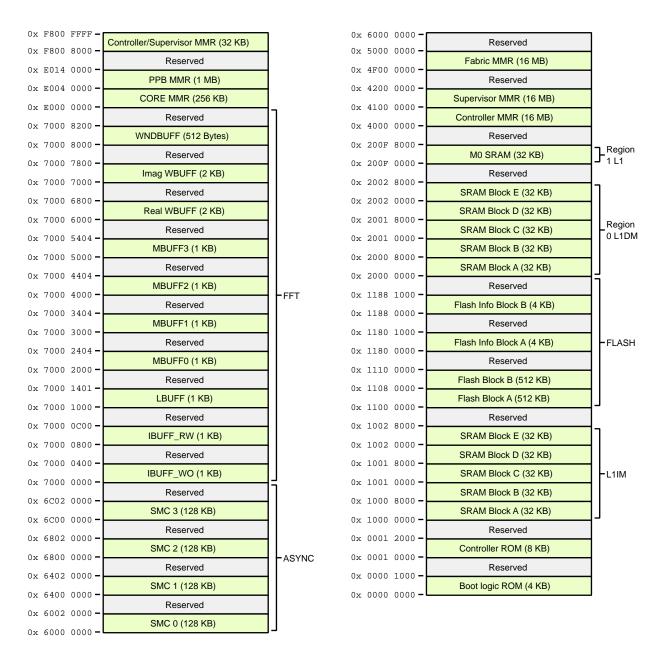

### 存储器架构

ADSP-CM41xF处理器的内外存储器如图15所示,以下各节将对其进行说明。

### ARM Cortex-M4存储器子系统

ADSP-CM41xF系列的存储器映射是以ARM出品的Cortex-M4型号为基础的。若保留标准化存储器映射,则可为M4平台上的端口应用提供方便。该型号与其他供应商产品的唯一区别是其内部存储器的物理实现方式。

ADSP-CM41xF应用开发一般是以跨越CODE/SRAM和外部存储器区域的存储器模块为基础的。通过内部SRAM和内部闪存提供了充足的内置存储器。额外的外部存储器件可以通过SMC异步存储器端口连接,也可通过SPI0串行存储器接口连接。

### 代码区域

该区域(0x0000\_0000至0x1FFF\_FFFF)中的访问操作由内核 在其ICODE和DCODE两个接口上执行,其访问对象是 Cortex-M4F平台集成器件中的存储器资源。

- **引导ROM**。在系统复位时执行的一个8K字节引导 ROM。本空间仅支持M4F内核的只读访问。注意, 用户无法修改ROM存储器内容。

- 内部SRAM代码区域。该存储器空间含有必须实时执行的应用指令和文字(常数)数据。支持M4F内核进行读/写访问,支持系统器件进行读/写DMA访问。内部SRAM可以按32K字节块在CODE和DATA(M4空间中的SRAM区域)之间划分。对该区域的访问速率为内核时钟速率,无等待状态。

- 集成闪存。该存储器空间包括高达1 M字节的Flash存储器,可保存用户程序和常数数据。初始向量表和复位引导向量位于Flash存储器的基址。

对该区域的读取最高能以内核时钟速度进行,并由强大的Flash预取单元优化。(参见:待定)

Flash存储器还包括最多两个4K字节模块,称为信息模块。信息模块中的预定义地址可能含有用户的安全密钥,用来锁定针对器件的调试访问以及控制器件的引导时间初始化。

Flash存储器能够以每页4 KB为单位擦除,或者执行批量擦除操作。存储器为ECC保护,支持以64位(8字节)为单位写入。

### SRAM区域

该区域(0x2000\_0000至0x3FFF\_FFFF)中的访问操作由ARM Cortex-M4F内核在其SYS接口上执行。另外,内核的SRAM 区域可以充当应用的数据区。

• 内部SRAM数据区域。此空间可以包含读/写数据。内部SRAM可以按32K字节块在CODE和DATA(M4空间中的SRAM区域)之间划分。对该区域的访问速率为内核时钟速率,无等待状态。支持M4F内核进行读/写访问,支持系统器件进行读/写DMA访问。通过Cortex-M4F平台中的全局独占访问监控器可以支持独占存储器访问。同时提供位段支持。

### 系统存储器空间

系统MMR。该区域中驻留着各种系统MMR。为 MMR提供了位段支持。

### 外部异步并行闪存/RAM

• L2异步存储器。可以选择性地将最多32M字节×4组外部存储器连接至异步存储器端口(SMC)。同时也可以进行直接R/W数据访问。

#### 系统区域

该区域(0xE000\_0000至0xF7FF\_FFFF)中的访问操作由ARM Cortex-M4F内核在其SYS接口上执行,并在Cortex-M4F平台内部进行处理。可以对MPU进行编程,将对该空间的访问限制为仅优先模式。

- CoreSight ROM。ROM表条目指向处理器的调试器件。

- ARM PPB外设。该空间由ARM定义,占据着SYS区域 末端的256K字节(0xE000\_0000至0xE004\_0000)。该空 间支持M4F内核对ARM内核的内部外设(MPU、ITM、 DWT、FPB、SCS、TPIU、ETM)和CoreSight ROM进 行读/写访问。系统DMA无法访问。

- 平台控制寄存器。该空间拥有Cortex-M4F平台集成器件中的寄存器,这些寄存器控制着ARM内核、其存储器和Flash存储器控制器。M4F内核可以通过其SYS端口进行访问(但系统DMA无法进行访问)。

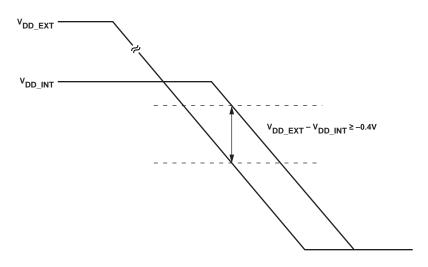

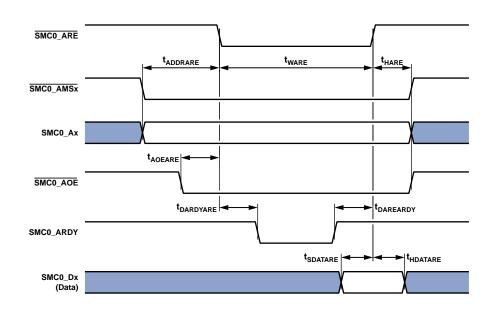

### 静态存储控制器(SMC)

SMC可以用来控制最多4组外部存储器或存储器映射设备, 其时序参数非常灵活。在ADSP-CM41xF处理器上,每一组 都占用32M字节区段,与所用器件的大小无关。

图15. ADSP-CM41xF ARM Cortex-M4存储器映射

### 引류

复位后,处理器可以通过两种机制自动加载内部和外部存储器。引导模式由专用SYS\_BMODE输入引脚决定。有两种引导模式,即从Flash存储器引导或从UART串行端口加载Flash。

由于M0子系统没有ROM, M4必须将M0应用程序载入M0 SRAM, 才能启动M0。M0应用程序可以方便地保存在 Flash存储器中,也可以从ADSP-CM41x系统中任何目标源 或通信接口载入。

引导模式如表2所示。这些模式由RCU\_CTL寄存器的 SYS\_BMODE位实现,在上电复位和软件启动的复位期间 采样。

### 表2. 引导模式

| SYS_BMODE[0]<br>设置 | 描述                |

|--------------------|-------------------|

| 0                  | 从集成Flash存储器直接执行代码 |

| 1                  | 基于UART的Flash固件更新  |

### 系统加速

下节内容说明ADSP-CM41xF处理器的系统加速度模块。

### 谐波分析引擎(HAE)

谐波分析引擎(HAE)模块从两个源信号接收8 kHz输入样本, 这两个源信号的频率在45 Hz和65 Hz之间。然后, HAE将处 理输入采样, 并生成输出结果。输出结果由对基波进行的 电能质量测量值和最多12个额外谐波构成。

### FFTB信号频谱监控器

FFTB信号频谱监控器加速度计提供背景输入信号频谱分析,内置针对各种传感器输入格式的数据转换、频谱均值、平方幅度计算以及频段功率限幅检测。FFTB单元可为存储器或DMA的输入信号数据提供高达512点16位FFT,并具有可选输入格式转换、梳状滤波、窗口、可编程FFT尺寸、平方幅度计算、频谱平均和频谱限幅检查。

FFTB单元可以配置为直接接受来自信号源的数据——比如 ADC或SINC滤波器,而无需处理器的干预,并且无需 DMA输入/输出SRAM。FFT能直接将结果写入任意存储器 空间,包括M0或M4上的SRAM。

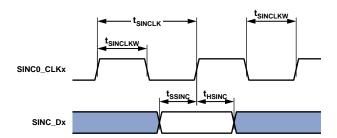

### SINC滤波器单元

SINC模块处理4个位流,为每个位流使用一对可配置的 SINC滤波器。每对初级SINC滤波器用来产生该对的滤波和 抽取输出。输出的抽取速率可以是比输入速率低8至256倍 的任意整数速率。抽取越高,就越能消除噪声,因而 ENOB也越高。

还可在SINC模块之外选用额外的滤波装置来进一步增加 ENOB。主SINC滤波器输出可通过借道DMA传输至处理器 存储器或传输至另一外设的方式进行访问。

四个通道中的每一个都有一个低延迟辅助滤波器,其中含有可编程的正、负超量程检测电容。这些限值检测事件可以用于使内核中断,生成触发信号,或者指示系统故障。

### 安全特性

处理器提供了软硬件相结合的多种保护机制,可在安全模式下阻止对器件的访问,在开放模式下允许访问。这些机制包括密码保护的UART Flash加载器,以及密码保护的JTAG/SWD调试接口。

本产品内置安全特性,可保护嵌入式非易失存储器内容并防止执行未经授权的代码。当订购方或后续接收方使能该器件的安全特性后,ADI公司对退回器件执行故障分析的能力会受到限制。关于该器件的故障分析限制详情,请联系ADI公司。

### 功能安全特性

处理器提供了以下特性,可以增强或者帮助实现一定程度 的系统安全性和可靠性。虽然安全性水平主要由系统考虑 因素决定,但下列特性有助于增强鲁棒性。

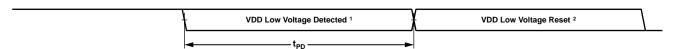

### 电压监控单元(VMU)

电压监控单元是一个片上集成式电源监控模块,用来检测 VDD\_EXT以及 VDD\_INT电源上的欠压和过压。 VMU负责控制 GPIO引脚安全状态机制及其时序。 VMU还负责在检测到电源故障时将 Flash置于安全状态。

### 振荡器比较器单元(OCU)

处理器还集成振荡比较器单元,用于检测SYSCLK时钟线路上的故障。它使用外部辅助时钟或晶振输入SYS\_CLKIN1来检测各种条件,比如时钟死区和违反时钟频率限值。它能生成数个事件,通知处理器有关违反情况。检测到故障事件时,可以配置时钟不良信号(CLKNG),将芯片置于复位状态。它还能初始化GPIO引脚安全状态机制。

### ECC保护L1存储器

M4和M0处理器L1 SRAM、Flash存储器和邮箱存储器均采用 零等待状态SEC-DED ECC加以保护,并原生保护32位存储 器元件。在适当的地方写入8位或16位数据可导致自动背 景读取-修改-写入ECC更新,通常不存在可观察到的处理 器停顿。刷新辅助硬件可周期性处理单个位错误。多位错 误检测还可用来表示中断和/或故障。

### 循环冗余校验(CRC)

CRC是用来计算数据块CRC的硬件模块。它基于CRC32引擎,可计算传递给它的32b数据字的CRC值。若数据字尺寸小于32b,则内核/外部源有责任将数据装入32b数据单元中。

特别地,可以使用CRC单元来验证Flash存储器内容,即 SRAM中常数数据块(文字或代码)。CRC外设的主要特性 如下:

- 存储器扫描模式

- 存储器传输模式

- 数据验证模式

- 数据填充模式

- 32b CRC多项式(可编程多项式)

- 位/字节镜像选项

- 故障/错误中断机制

#### Cortex-M4 MPU

MPU将存储器映射分为几个区域,允许系统程序员定义每个区域的位置、大小、访问权限和存储器属性。支持为每个区域配置独立的属性设置,还支持重叠区域,以及将存储器属性导出到系统等。

更多信息,请参考ARM信息中心网页。

### 系统保护单元(SPU)

所有系统资源和L2存储器组都可以由处理器内核、存储器到存储器DMA或调试单元控制。系统保护单元(SPU)支持对锁定到给定主机的特定资源进行写入访问。

提供两个SPU单元来管理外设组以及相关APB总线。SPU0管理M0的本地外设,SPU1管理M4系统外设。

提供三个SMPU单元,每个存储器空间一个: M4 SRAM、M0 SRAM、片外L2。

SPU和SPMU可以编程检测访问超时,并返回控制,初始化主机。这样可以保护系统免于无限停顿故障。

通过全局锁定概念——大部分系统关键模块均提供——某些模块支持更小粒度的系统保护。一组外设初始化之后,每一个所需外设都可通过写入其LOCK位而标记为保护。然后,当SPU设置了全局锁定后,整个配置都会受到保护。那些之前已设置了LOCK位的外设可以受到保护,免于一切写操作,直至全局SPU锁定再次解锁。

### 观察点保护

观察点和硬件断点主要用于仿真器。使能时,只要访问用户定义的系统资源或者内核从用户定义的地址执行操作,这些点就会通知仿真器。可以配置看门狗事件,以便把这些事件告知处理器或SEC。

### 看门狗定时器(WDOG)

每个内核关联一个32位定时器,可用来部署软件看门狗功能。软件看门狗可以提高系统可用性,如果定时器在软件复位之前超时,它将通过产生通用中断迫使处理器进入已知状态。编程人员初始化定时器计数值,使能适当中断,然后使能定时器。此后,在计数器从编程值计数到0之前,软件必须重新加载计数器。这样在软件(正常情况下会复位定时器)由于外部噪声条件或软件错误而停止运行时,可以防止系统一直处于未知状态。或者,故障管理单元(FMU)可在看门狗超时事件时,直接启动处理器复位。

### 信号看门狗

8个通用定时器可以通过两种模式来监控片外信号。看门 狗周期模式监控外部信号是否以预期范围内的周期切换。 看门狗宽度模式监控外部信号的脉冲宽度是否在预期范围 内。两种模式均有助于检测系统级信号的错误/不需要的切 换(或缺少系统信号)。

#### 振荡器看门狗

振荡器看门狗监控外部时钟振荡器,可以检测到时钟缺失和谐波振荡错误。振荡器看门狗检测信号被路由至系统事件控制器的故障管理部分,同时还被路由至GPIO pin\_safe\_state 机制。

### 低延迟Sinc滤波器超量程检测

SINC滤波器单元为每个输入通道提供一个搭载可编程正、 负限幅检测器的低延迟辅助滤波器。这些滤波器可以用于 监控隔离ADC位流中的超量程或欠量程条件,对于10 MHz 的位流,滤波器组延迟低至0.7 μs。辅助SINC滤波器事件可 以用来中断内核,借助触发路由单元(TRU)直接在硬件中 触发其他事件,或者指示系统故障的故障管理单元。

### 升/降计数不匹配检测

GP计数器可以监控外部信号对,如请求/授权选通等。如果边沿计数不匹配超过预期范围,升/降计数器可以将此信息告知处理器或SEC。

#### 故障管理

故障管理单元是系统事件控制器(SEC)的一部分。多数系统事件都可以定义为故障。如果如此定义,SEC将把事件转送到其故障管理单元,它可能会自动复位整个器件以重新启动,或者仅切换SYS\_FAULT输出引脚以告知片外硬件。此外,故障管理单元可以通过键控序列延迟所采取的操作,为内核提供最后一个机会来解决危机,防止采取故障操作。

### 处理器外设

ADSP-CM41xF处理器包含丰富的外设集,用来将外部系统与处理器相连,提供实时检测(ADC、GPIO、CNT)、控制(定时器、LBA、MATH、MBOX)、执行(PWM、GPIO)以及与外部器件的通信(CAN、SPI、SPORT、UART和TWI)。这些外设通过多条并行高带宽总线连接内核,提供灵活的系统配置和出色的整体系统性能(参见第1页的框图)。

处理器基础设施含有高速串行和并行端口、用于灵活管理 片内外设或外部来源中断事件的中断控制器,以及根据不 同应用情况调整处理器和系统的性能与功耗特性的电源管 理控制功能。

#### 定时器

处理器包括多个定时器, 以下部分将说明这些定时器。

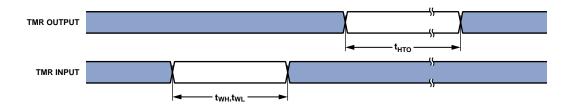

### 通用定时器

ADSP-CM41xF处理器提供两组8个通用定时器,每组主要与每一个处理器内核相连。每个定时器具有外部引脚,可以将其配置为脉宽调制器(PWM)、定时器输出、定时器的时钟输入或用于测量脉宽和外部事件周期的机制。这些定时器可以与TM0\_ACLKx引脚上的外部时钟输入、TM0\_CLK输入引脚上的外部信号或内部SCLK同步。

定时器单元可以与UART和CAN控制器一起使用,测量数据流的脉冲宽度,为相应的串行通道提供软件自动波特率检测功能。

该定时器可以产生处理器内核中断,提供用于与系统时钟或外部信号同步的周期性事件。定时器事件也可以通过TRU触发其他外设(例如产生故障信号)。

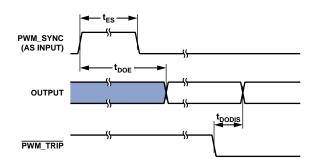

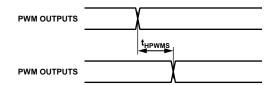

### 脉宽调制器单元(PWM)

脉冲宽度调制器(PWM)单元提供分辨率为一个系统时钟周期(SCLK)的占空比和相位控制能力。处理器提供24个PWM输出,组成三个PWM单元,每一个单元具有4个PWM输出对。

增强精度PWM (HPPWM)模块将其分辨率提高了几位,从 而增强了各PWM单元的性能,结果导致更高的精度水平。 其他特性包括:

- · 以中心为基准的16位PWM发生单元

- 可编程PWM脉冲宽度

- 单倍/双倍更新模式

- 可编程死区时间和开关频率

- 二进制补码实现方案支持平滑过渡到全开和全关状态

- 专用异步PWM关断信号

各PWM模块集成了一个灵活且可编程的三相PWM波形发生器,可用来产生所需的开关信号,以驱动用于交流感应电机(ACIM)或永磁同步电机(PMSM)控制的三相电压源逆变器。此外,PWM模块具有特殊功能,可大幅简化用于控制电子换向电机(ECM)或无刷直流电机(BDCM)所需PWM开关信号的产生。利用软件可以实现开关磁阻电机(SRM)的特殊模式。

8个PWM输出信号(每个PWM单元一个)包括4个高端驱动信号和4个低端驱动信号。产生的PWM信号极性可通过软件设置,从而产生有源HI或有源LO PWM图案。

多种PWM断路(TRIP)机制中的任意一种都可立即关断PWM单元。同步软件断路寄存器可同时关断任意PWM输出组合。同步TRU触发机制支持任意片上TRU主机以可编程序列方式关断所选PWM输出,以支持多级逆变器拓扑。可将3个异步通用PWM\_TRIP输入(低电平有效)路由至3个PWM模块的任意组合,并立即导致PWM关断任意选中的PWM输出。类似地,3个FOCP模拟比较器可以连接任意PWM\_TRIP输入组合。

最后,使用GPIO引脚安全状态机制——包括时钟或电压监控单元、振荡器看门狗和振荡器比较器单元的故障检测——一组内部异步监控器同样可以导致PWM输出关断。

### 去抖单元

所选GPIO信号和来自AFE的异步内部芯片信号连接可编程 去抖单元的独立通道。这样可以消除外部硬件,并可对关 键信号的高频毛刺干扰进行过滤。连接去抖通道的信号包 括:三个PWM\_TRIP信号、FOCP比较器检测信号以及 AFE\_OK状态信号。

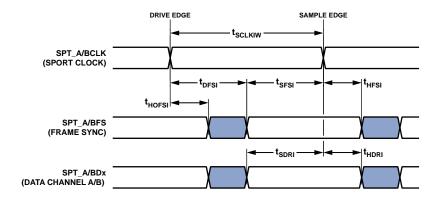

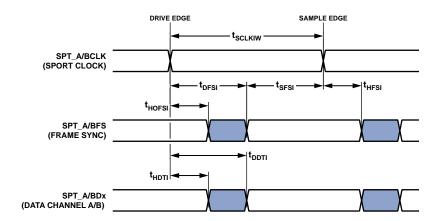

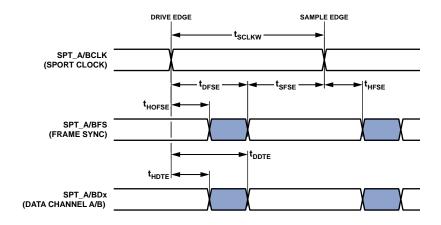

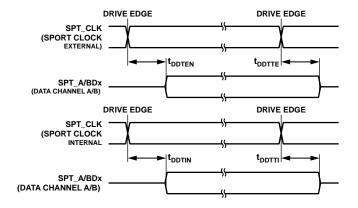

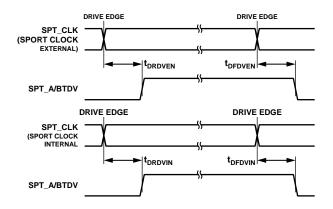

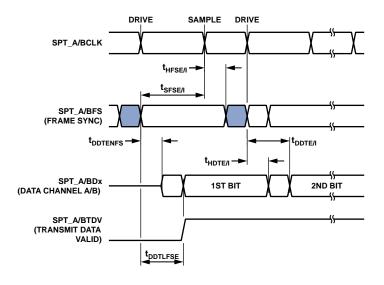

### 串行端口(SPORT)

利用同步串行端口,处理器可以低成本地连接到各种数字和混合信号外设,如ADI公司的音频编解码器、ADC和DAC。这些串行端口由两条数据线、一条时钟线和一条帧同步线组成。数据线可以编程为发送或接收数据,各数据线有一个专用DMA通道。

串行端口数据可以通过专用DMA通道自动写入和读取片内存储器/外部存储器。对于全双工操作,可以采用两个半SPORT与时钟和帧同步信号一同使用;这些信号通过SPMUX模块在内部共享。某些工作模式下,SPORT支持栅极时钟。

串行端口有六种工作模式:

- 标准DSP串行模式

- 多通道(TDM)模式

- I<sup>2</sup>S模式

- · 包装I2S模式

- 左对齐模式

- 右对齐模式

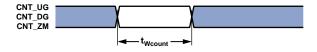

### 通用计数器(CNT)

该32位计数器可以在通用升/降计数模式下工作,检测通常由工业驱动器或手动拇指滚轮发送的2位正交或二进制码。 计数方向由电平敏感型输入引脚或两个边沿检测器控制。

第三个计数器可以提供灵活的零标记支持,或者也可以用 于输入拇指滚轮的按钮信号。所有三个引脚都具有可编程 去抖电路。

通用计数器还支持在正交编码模式下,以可编程M/N频率 方式将CNT\_CUD和CNT\_CDG引脚缩放到输出引脚上。

转送到各通用定时器的内部信号可以使能这些定时器来测量计数事件之间的时间间隔。边界寄存器支持自动调零操作,或者在超过可编程的计数值时通过中断发出简单的系统警告。

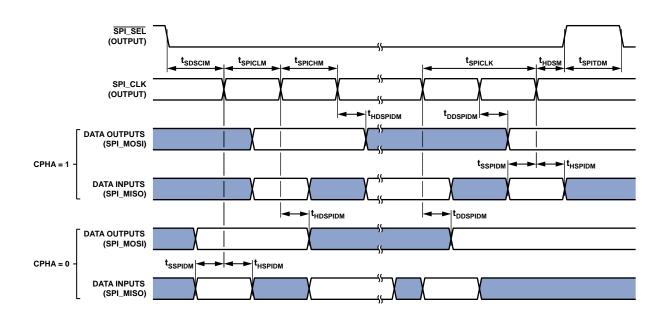

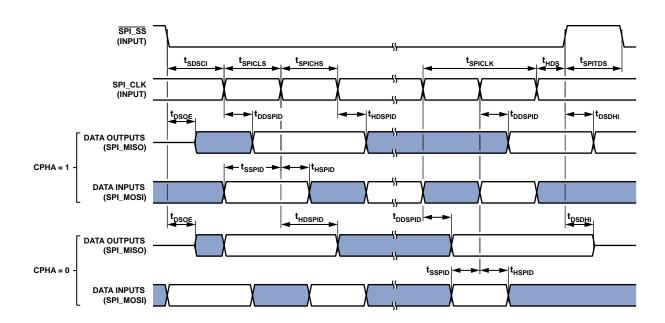

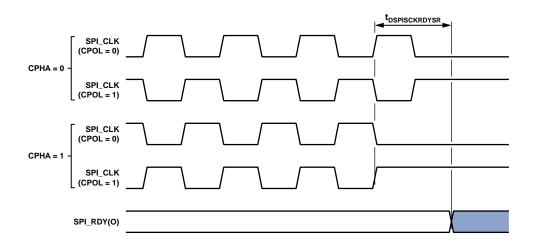

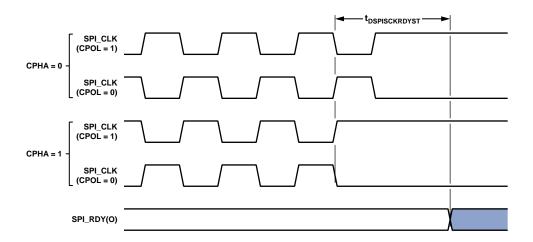

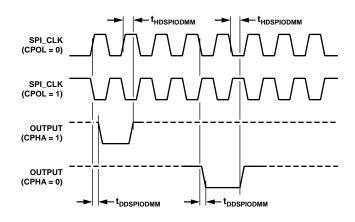

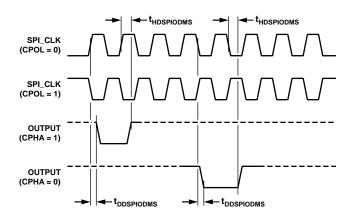

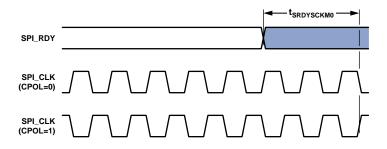

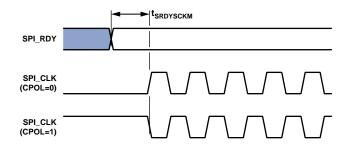

### 串行外设接口(SPI)端口

提供两个SPI兼容端口,每一个端口都主要关联一个处理器, 允许处理器与多个SPI兼容器件通信。 在最简单的模式中,SPI接口使用三个引脚传输数据:2个数据引脚(主机输出-从机输入和主机输入-从机输出,即SPI\_MOSI和SPI\_MISO)和1个时钟引脚(即SPI\_CLK)。其它SPI器件利用一个SPI片选输入引脚(SPI\_SS)选择处理器,处理器利用三个SPI片选输出引脚(SPI\_SELn)选择其它SPI器件。SPI选择引脚是重新配置的通用I/O引脚。利用这些引脚,SPI提供一个全双工、同步串行接口,支持主机模式、从机模式和多主机环境。

在一个多主机或多从机SPI系统中,MOSI和MISO数据输出引脚可配置为开漏输出(使用ODM位),可防止冲突,以及可能对引脚驱动器造成的损坏。选择此选项时,MOSI和MISO引脚各需要一个外部上拉电阻。

若ODM置位且SPI配置为主机时,则当MOSI上的驱动数据输出为逻辑高电平时,MOSI引脚为三态。当驱动数据为逻辑低电平时,MOSI引脚为非三态。类似地,若ODM置位且SPI配置为从机时,则当MISO上的驱动数据输出为逻辑高电平时,MISO引脚为三态。

SPI端口的波特率和时钟相位/极性是可编程的,而且它集成了DMA通道,支持发送和接收数据流。

### 通用异步接收器/发送器端口(UART)

ADSP-CM41xF处理器提供五个全双工通用异步接收器/发送器(UART)端口,四个主要与M4关联,一个主要与M0关联,完全兼容PC标准UART。每个UART端口提供一个简化的UART接口用于连接其他外设或主机,支持全双工、DMA、异步串行数据传输。UART端口支持5到8个数据位,不支持奇偶校验。在多分支总线(MDB)系统中,可以传输一个额外的地址位,以便仅中断寻址的节点。帧由一个、一个半、两个或两个半停止位终止。

UART端口通过允许发送(CTS)输入和请求发送(RTS)输出支持自动硬件流程控制,并提供可编程的置位FIFO级。

为了帮助支持本地互连网络(LIN)协议,可以使用一个特殊命令让发送器将一个位长可编程的中断命令排队输入发送缓冲器。同样,停止位的数量可以由可编程的帧间空间扩展。

UART还支持红外数据协会(IrDA®)串行红外物理层链路规范(SIR)协议。

### TWI控制器接口(TWI)

处理器包括一个双线接口(TWI)模块,用于在多个器件之间进行简单的控制数据交换。

TWI模块兼容广泛使用的I<sup>2</sup>C总线标准。TWI模块能够同时以主机和从机工作,支持7位寻址和多媒体数据仲裁。TWI接口利用两个引脚传输时钟(TWI\_SCL)和数据(TWI\_SDA),支持最高速度为400 kb/s的协议。TWI接口引脚兼容5 V逻辑电平。

此外,TWI模块完全兼容串行相机控制总线(SCCB)功能,可轻松控制各种CMOS相机传感器。

### 控制器区域网络(CAN)

ADSP-CM41xF处理器具有两个CAN控制器,一个主要与M4有关,另一个主要与M0有关。每一个CAN控制器都部署了CAN 2.0B(有源)协议。此协议是异步通信协议,用于工业和汽车控制系统。CAN协议能够可靠地通过网络通信,非常适合控制应用,这是因为该协议具有CRC校验、消息错误跟踪和故障节点限制等机制。

CAN控制器提供如下特性:

- 32个邮箱(8个仅用于接收,8个仅用于发射,16个可配置为接收或发射)

- 每个邮箱具有专用接受屏蔽

- 对前两个字节的补充数据滤波

- 支持标准(11位)和扩展(29位)识别符(ID)消息格式

- 支持远程帧

- 支持有源或无源网络

- 中断,包括: TX完成、RX完成、错误和全局

不需要额外晶振来提供CAN时钟,因为CAN时钟是通过可 编程分频器从系统时钟获得。

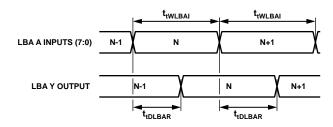

### 逻辑模块阵列(LBA)

逻辑模块阵列包含多个逻辑模块,可编程执行各种逻辑或算术功能。可以在查找表(LUT)模式或乘法项模式下定义逻辑或算术功能。每一个逻辑模块能够产生一个输出,该输出是多达8路或16路输入的函数,具体取决于所选模式。确切的函数通过编程8个32位函数寄存器定义,它们映射至处理器寄存器空间。总共有8个独立逻辑模块,它们组成逻辑模块阵列。LBA有如下特性:

- 各输出可配置为LUT或PTA模式

- LUT(查找表)模式允许任意8路输入组合逻辑函数

- PTA(乘法项阵列)模式支持8个乘法项,最多16路输入

- 通常可扩展至8个独立输出

- 系统输入可连接系统专用信号(比如定时器输出、 TRU从机)

- 系统输出可连接系统专用信号(比如TRU主机、内核中断)

### 数学单元

数学功能单元是一个加速器,通过单个MMR接口执行一般超越函数的高度精确的单精度浮点计算。这些函数包括: 三角函数、反三角函数、双曲线函数、指数函数、对数函数、平方根函数和互反函数。

数学单元支持矩形和极坐标函数的单操作数和双操作数转换。函数的精度在IEEE-754单精度格式的23.50位误差内。 该紧密耦合加速器的大部分操作可在每个函数的设定内核 时钟周期数内完成,相比那些Cortex-M4软件库提供的更 具有竞争力。

### 邮箱(MBOX)

MBOX(邮箱)模块是共享系统资源,用来在Cortex-M4和Cortex-M0处理器域之间建立通信。MBOX模块有两个访问端口。每个访问端口均连接一个系统主机模块。MBOX存储器大小为4 KB。为了协助部署内部处理器令牌,MBOX存储器支持M4端口的原生独占式存储器操作,并可仿真执行来自M0的独占式操作。MBOX存储器还支持M4位绑定操作。MBOX包含解码逻辑,可以在两个处理器之间切换。访问端口在同一个时钟域内。

在ADSP-CM41xF处理器中, MBOX的目标用途如下:

- PORT1连接Cortex-M4

- PORT0连接Cortex-M0

有两个寄存器模块。PORT1寄存器模块包含:

- PORT1、自动刷新逻辑和ECC测试逻辑的控制寄存器

- PORT1和自动刷新逻辑的状态寄存器

PORT0寄存器模块包含:

- PORT0控制字段

- PORT0状态寄存器

每一个端口只能访问自己的寄存器模块。

### 时钟和电源管理

处理器提供三种工作模式,各种模式具有不同的性能/功耗特征。控制各处理器外设的时钟也可以降低功耗。表3总结了各种模式的电源设置。

表3. 电源设置

| 模式   | CGU PLL | CGU PLL<br>旁路 | f <sub>CCLK</sub> | <b>f</b> <sub>SCLK</sub> | 内核<br>电源 |

|------|---------|---------------|-------------------|--------------------------|----------|

| 全开   | 使能      | 否             | 使能                | 使能                       | 开        |

| 有效   | 使能      | 是             | 使能                | 使能                       | 开        |

|      | 禁用      | 是             | 使能                | 使能                       | 开        |

| 深度休眠 | 禁用      | 不适用           | 禁用                | 禁用                       | 开        |

<sup>1</sup> NA = 不适用

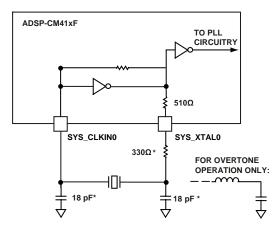

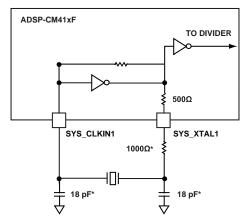

### 晶振(SYS\_XTALO/1)

处理器的时钟可以来自外部晶振(图16)、正弦波输入或源于外部时钟振荡器的缓冲整形时钟。如果使用外部时钟,它应为TTL兼容信号,而且在正常工作期间不得暂停、改变或以低于额定频率的频率工作。 此信号连接到处理器的 SYS\_CLKIN0引脚。使用外部时钟时,SYS\_XTAL0引脚保持断开。此外,由于处理器含有片内振荡器电路,因此也可以使用外部晶振。

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED, DEPENDING ON THE CRYSTAL AND LAYOUT. ANALYZE CAREFULLY. FOR FREQUENCIES ABOVE 33 MHz, THE SUGGESTED CAPACITOR VALUE OF 18pF SHOULD BE TREATED AS A MAXIMUM, AND THE SUGGESTED RESISTOR VALUE SHOULD BE REDUCED TO 0  $\Omega$ .

#### 图16. CLKIN0外部晶振连接

出于功能安全性目的,可将辅助时钟输入(图17)连接至 SYS\_CLKIN1和SYS\_XTAL1。其频率可用来监控OCU单元的 主SYS\_CLKIN0频率。如果未使用,则必须将SYS\_CLKIN1 接地,并将SYS\_XTAL1保持在未连接状态。

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED, DEPENDING ON THE CRYSTAL AND LAYOUT. FOR FREQUENCIES ABOVE 22 MHz, THE SUGGESTED RESISTOR VALUE SHOULD BE REDUCED (~450 Ω).

图17. CLKIN1外部晶振连接

欲以基频工作,请为每一个连接的晶振使用图16所示的电路。一个并行谐振、基频、微处理器级晶振连接在SYS\_CLKIN和XTAL引脚上。SYS\_CLKIN引脚与XTAL引脚之间的片内电阻在500 kΩ范围内。通常情况下,建议不要使用其它并联电阻。

图16所示的两个电容和串联电阻用于精调正弦频率输入的相位和幅度。图16所示的电容和电阻值仅为典型值。电容值取决于晶振制造商的负载电容建议和PCB物理布局。电阻值取决于晶振制造商规定的驱动电平。用户应在整个温度范围内细致考察多个器件,验证所用的元件值是否合适。

针对25 MHz以上的频率,可以使用三次谐波晶体振荡器。此时需要修改图16所示电路,增加一个调谐电感电路,确保晶振仅在第三泛音工作。第三泛音工作的设计程序详见应用笔记(EE-168): "三次谐波晶体振荡器用于ADSP-218x DSP"(www.analog.com/ee-168)。

### 振荡器看门狗

提供了一个可编程振荡器看门狗单元,以便对外部晶振的 正确启动和谐波模式进行验证。允许用户指定预期振荡频 率,并启用对非振荡和振荡错误故障的检测。这些事件可 以路由至SYS\_FAULT输出引脚和/或使器件复位。

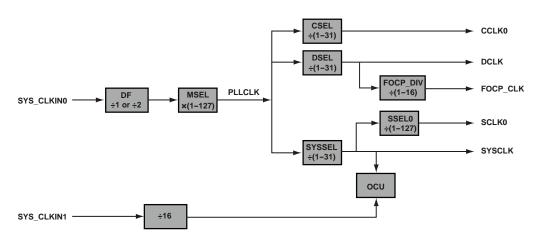

#### 时钟产生(CGU)

时钟发生单元(CGU)产生所有片内时钟和同步信号。乘法系数写入PLL以定义PLLCLK频率。

可编程值将PLLCLK频率分频,产生内核时钟(CCLK)、系统时钟(SCLK)和输出时钟(OCLK),如第61页的图19所示。

写入CGU控制寄存器不会立即影响PLL的行为。寄存器首 先写入新值,然后PLL逻辑执行变更,以便从当前状态平 稳过渡到新状态。

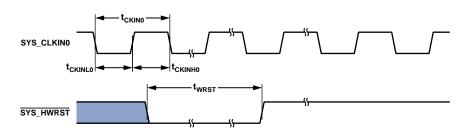

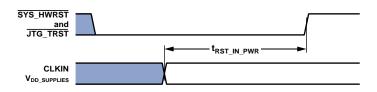

VDD\_EXT引脚通电时, SYS\_CLKIN开始振荡。所有电压源都在额定范围内(参见第60页的工作条件), 并且SYS\_CLKIN振荡稳定后,便可以施加SYS\_HWRST的上升沿。

### 时钟输出/外部时钟

SYS\_CLKOUT输出引脚具有可编程选项,可以输出片内时钟的分频版本。SYS\_CLKOUT引脚可编程驱动时钟输入的缓冲版本,或者驱动ADSP-CM41x系统中的任意一组可用时钟。默认情况下,SYS\_CLKOUT驱动至低电平。时钟产生故障(例如PLL未锁定)可能会触发硬件复位。

SYS\_CLKOUT可以用于输出处理器上使用的几种不同时钟中的一种。表4所示的时钟可以从SYS\_CLKOUT输出。

表4. SYS\_CLKOUT源和分频器选项

| <b>以</b> |                        |  |  |  |

|----------|------------------------|--|--|--|

| 时钟源      | 分频器                    |  |  |  |

| GND      | 逻辑低电平                  |  |  |  |

| CLKBUF0  | 缓冲SYS_CLKIN0           |  |  |  |

| CLKBUF1  | 缓冲SYS_CLKIN1           |  |  |  |

| CCLK0    | M4控制器时钟,4分频            |  |  |  |

| SCLK0    | M0监控器时钟,2分频            |  |  |  |

| SYSCLK   | 系统时钟,2分频               |  |  |  |

| DCLK     | CGU DCLK输出用作AFE FOCP时钟 |  |  |  |

|          | 生成,位于FOCP_DIV分频器之前     |  |  |  |

| FOCP_CLK | AFE FOCP时钟,位于FOCP_DIV分 |  |  |  |

|          | 频器之后                   |  |  |  |

| OUTCLK   | 可编程                    |  |  |  |

| MORST    | 缓冲M0监控器复位              |  |  |  |

| SYSRST   | 缓冲系统从RCU复位             |  |  |  |

### 电源管理

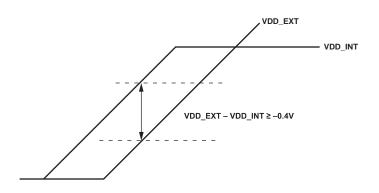

如第8页的表5和图5所示,处理器支持三个不同的电源域,即VDD\_INT、VDD\_EXT和VDD\_ANA。通过将处理器的内部逻辑与其他I/O隔离并划入其自己的电源域,处理器便可以利用动态电源管理,而不会影响其他I/O器件。所有电源域都必须按照处理器"工作条件"中的相应技术规格表来通电,即使不使用某一特性/外设。

处理器的动态电源管理功能可以动态控制处理器的内核时钟频率( $\mathbf{f}_{\text{CLK}}$ )。

### 表5. 电源域

| 电源域    | 引脚            |

|--------|---------------|

| 所有内部逻辑 | $V_{DD\_INT}$ |

| 数字I/O  | $V_{DD\_EXT}$ |

| 模拟     | $V_{DD\_ANA}$ |

处理器的功耗在很大程度上与其时钟频率和工作电压的平方成比例。例如,工作频率降低25%,动态功耗也会降低25%。有关电源引脚的更多信息,请参见第60页"工作条件"部分。

#### 全开工作模式--最高性能

在全开模式下,PLL使能且未被旁路,能够以最高频率工作。这是可以实现最高性能的执行状态。处理器内核和所有使能的外设以全速工作。

有关PLL控制的更多信息,请参见《搭载ARM Cortex-M4/M0的ADSP-CM41x混合信号控制处理器硬件参考手册》的"动态电源管理"一章。

### 深度睡眠工作模式—最大动态省电

深度睡眠模式通过禁用处理器内核的时钟和所有同步外设 的时钟来最大程度地降低动态功耗。异步外设仍然可以运 行,但不能访问内部资源或外部存储器。

### VDD INT电压调节

输入ADSP-CM41xF处理器的内部电压VDD\_INT可通过片内稳压器产生,也可通过外部稳压器产生。

VDD\_INT电源可以通过外部I/O电源VDD\_EXT产生。图18显示可正常工作的电源管理系统所需的外部元件。有关元件选择的更多信息,请参阅应用笔记(EE-TBD)"ADSP-CM41x电源晶体管选型指南"(www.analog.com/ee-TBD)。

可旁路内部稳压器,并使用外部调节器提供VDD\_INT。 使用外部调节器时,VREG\_BASE必须接地,以便最大程度 降低功耗。

图18. 内部稳压器电路

### 复位控制单元(RCU)

复位是整个处理器或内核的初始状态,并且是硬件或软件触发事件的结果。在此状态下,所有控制寄存器都设为默认值,功能单元空闲。要退出某一内核复位,此内核必须准备就绪以执行引导。

复位控制单元(RCU)控制所有功能单元如何进入和退出复位状态。功能要求和时钟约束条件的不同决定了复位信号的产生方式。程序必须保证任何复位功能都不会将系统置于不明状态或引起资源停转。

从系统角度来看,复位由复位目标和复位源定义,如下 所示。

#### 目标定义:

- 硬件复位——所有功能单元都复位到默认状态,无一 例外。历史记录丢失。

- 系统复位——除RCU以外的所有功能单元都复位到默 认状态。

#### 来源定义:

- 硬件复位——SYS\_HWRST输入信号置位有效(下拉)。

- 系统复位——可以由软件(写入RCU\_CTL寄存器)或另一功能单元触发,例如动态电源管理(DPM)单元、任一系统事件控制器(SEC)、触发路由单元(TRU)或仿真器输入。

- 触发请求(外设)。

### 系统调试

处理器包括多种用于简化系统调试的特性,下面说明这些 特性。

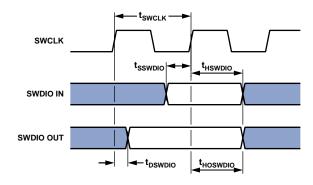

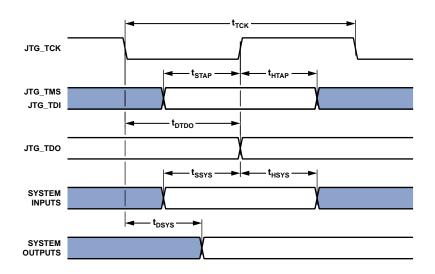

#### JTAG调试和串行线调试端口(SWJ-DP)

SWJ-DP是JTAG-DP与SW-DP的结合,通过它可以将串行线调试(SWD)或JTAG探针连接到目标。SWD信号与JTAG共

用相同的引脚。有一种自动检测机制,可在JTAG-DP和SW-DP之间切换,具体取决于仿真器Pod传输至JTAG引脚时使用的是哪个特殊数据序列。当收到正常JTAG序列时,SWJ-DP表现为一个JTAG目标,如果发送的是SW\_DP序列,则表现为一个单线目标。

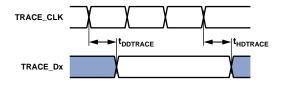

### 嵌入式跟踪宏单元(ETM)和仪表跟踪宏单元(ITM)

ADSP-CM41xF处理器支持嵌入式跟踪宏单元(ETM)和仪表跟踪宏单元(ITM)。这两种宏单元都提供了一个可选调试器件,可以记录CPU内核中的实时指令和数据流。这些数据通过具有跟踪功能的特殊调试器Pod读取。ITM是一种单数据引脚特性,ETM则是一种4数据引脚特性。

### 系统观察点单元(SWU)

系统观察点单元(SWU)是单一模块,连接到单条系统总线以监控处理。进入各系统从机的总线都连有一个SWU。SWU为所有系统总线地址通道信号提供端口。每个SWU包含4组匹配的寄存器和相关硬件。这四个SWU匹配组独立工作,但共享事件(中断和触发)输出。

### 闪存补丁和断点单元(FPB)

FPB部署了硬件断点,并通过将特定代码或文字地址重定向至 R/W系统存储器位置而实现块代码和数据。ADSP-CM41xF处理器部署了完整的FPB,具有8个比较器(6个代码/断点和2个文字数据)。

#### 开发工具

与ADSP-CM41xF处理器配套的是一组高度完善、易于使用的嵌入式应用开发工具。有关更多信息,请访问ADI公司网站。

### 其它信息

下列描述ADSP-CM41xF处理器(及其相关处理器)的文件可以通过ADI公司办事处订购,或者查看ADI公司网站上的电子版本:

- 搭载ARM Cortex-M4/M0的ADSP-CM41x混合信号控制 处理器硬件参考手册

- 搭载ARM Cortex-M4/M0的ADSP-CM41x混合信号控制 处理器异常表

本数据手册描述ADSP-CM41xF处理器的ARM Cortex-M4和ARM Cortex-M0内核和存储器架构,但不提供ARM处理器的详细编程信息。有关ARM处理器编程的更多信息,请访问ARM信息中心网页:

与编程ARM Cor-tex-M4处理器相关的文档有:

- Cortex®-M0器件通用用户指南

- CoreSight™ETMTM-M0技术参考手册

- Cortex®-M0技术参考手册

- Cortex®-M4器件通用用户指南

- CoreSight<sup>™</sup>ETM<sup>™</sup>-M4技术参考手册

- Cortex®M4技术参考手册

### 相关信号链

信号链指一系列信号调理电子器件,它们相继接收输入(通过采样实时现象获得的数据或存储的数据),信号链一部分的输出作为下一部分的输入。信号处理应用常常使用信号链来采集和处理数据,或者根据对实时现象的分析应用系统控制。

ADI公司提供能够完美配合工作的信号处理器件来简化信号处理系统的开发。ADI公司网站www.analog.com提供了一款工具,用于显示特定应用与相关器件之间的关系。

参考电路Circuits from the Lab<sup>®</sup>网站(http:\\www.analog.com\-circuits)的应用信号链页面提供如下内容:

- 各种电路类型和应用的信号链电路图

- 各信号链中的器件均有选型指南和应用信息链接

- 采用最佳设计技术的参考设计

### 安全特性免责声明

据我们所知,当按照数据手册和硬件参考手册的规定使用时,安全特性能够提供安全的代码和数据保护实现方法。然而,ADI公司不保证该技术绝对安全。因此,ADI公司特此声明,ADI公司并未明示或默示保证安保特性无法被破坏、削弱或以其它方式绕过,对于数据、信息、财产、知识产权的损失、毁坏或泄漏,ADI公司概不负责。

# ADSP-CM41xF详细信号描述

该表提供各引脚的详细说明。

表6. ADSP-CM41xF详细信号描述

| 表6. ADSP-CM41xF详约<br>信号名称 | 方向                                     | 描述                                                                                  |

|---------------------------|----------------------------------------|-------------------------------------------------------------------------------------|

| ADC_VIN_A[n]              | カロ<br>输入输出                             | ADC通道n单端模拟输入                                                                        |

| ADC_VIN_B[n]              | 十十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十 | ADC通道n单端模拟输入                                                                        |

| ADC_VIN_C[n]              | 十十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十 | ADC通道n单端模拟输入                                                                        |

| ADC_VIN_D[n]              | 十十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十 | ADC通道n单端模拟输入                                                                        |

| BYP_A2                    | 十十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十 | ADC通道   草圳侯]城桐八<br>  用于ADC的片内模拟电源调节旁路滤波器节点                                          |

| BYP_A[n]                  | 十十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十 | 用于ADC的片内模拟电源调节旁路滤波器节点                                                               |

| BYP_D0                    | 输入输出                                   | 用于ADC的片内模拟电源调节旁路滤波器节点                                                               |

| CAN_RX                    | 输入                                     | 接收。通常是外部CAN收发器的RX输出。                                                                |

| CAN_TX                    | 输出                                     | 发送。通常是外部CAN收发器的TX输入。                                                                |

| CNT_DG                    | 输入                                     | <b>递减计数和门控</b> 。取决于工作模式,该输入用作递减计数信号或栅极信号。<br>递减计数:该输入导致GP计数器递减。<br>栅极:停止GP计数器递增或递减。 |

| CNT_OUTA                  | 输入输出                                   | 输出分频器A                                                                              |

| CNT_OUTB                  | 输入输出                                   | 输出分频器B                                                                              |

| CNT_UD                    | 输入                                     | <b>递增计数和方向。</b> 取决于工作模式,该输入用作递增计数信号或方向信号。<br>递增计数:该输入导致GP计数器递增。<br>方向:选择GP计数器递增或递减。 |

| CNT_ZM                    | 输入                                     | 零计数标记。连接零标记的输入将输出旋转器件信号,或检测按钮动作。                                                    |

| COMP_OUT_A                | 输入输出                                   | 快速过流保护比较器A输出                                                                        |

| COMP_OUT_B                | 输入输出                                   | 快速过流保护比较器B输出                                                                        |

| COMP_OUT_C                | 输入输出                                   | 快速过流保护比较器C输出                                                                        |

| CPTMR_IN[n]               | 输入                                     | 输入                                                                                  |

| DAC0_VOUT                 | 输入输出                                   | 模拟电压输出n                                                                             |

| GND_ANA4_COMP             | 输入输出                                   | 比较器模拟地                                                                              |

| GND_ANA5_DAC              | 输入输出                                   | DAC模拟地                                                                              |

| GND_ANA[n]                | 输入输出                                   | VDD_ANA[n]模拟地返回                                                                     |

| GND_REFCAP0               | 输入输出                                   | REF_INOUT0模拟地返回                                                                     |

| GND_REFCAP1               | 输入输出                                   | VREF旁路电容                                                                            |

| GND_VREF2                 | 输入输出                                   | 模拟VREF接地                                                                            |

| JTG_TCK                   | 输入                                     | <b>JTAG时钟。</b> JTAG测试访问端口时钟。                                                        |

| JTG_TDI                   | 输入                                     | JTAG串行数据输入。JTAG测试访问端口数据输入。                                                          |

| JTG_TDO                   | 输出                                     | JTAG串行数据输出。JTAG测试访问端口数据输出。                                                          |

| JTG_TMS                   | 输入输出                                   | JTAG模式选择。JTAG测试访问端口模式选择。                                                            |

| JTG_TRST                  | 输入                                     | JTAG复位。JTAG测试访问端口复位。                                                                |

| LBA_PIN[n]                | 输入输出                                   | LBA数据输入或逻辑输出                                                                        |

| PWM_AH                    | 输出                                     | 通道A高端。高端驱动信号。                                                                       |

| PWM_AL                    | 输出                                     | 通道A低端。低端驱动信号。                                                                       |

| PWM_BH                    | 输出                                     | <b>通道B高端。</b> 高端驱动信号。                                                               |

| PWM_BL                    | 输出                                     | <b>通道B低端。</b> 低端驱动信号。                                                               |

| PWM_CH                    | 输出                                     | <b>通道C高端。</b> 高端驱动信号。                                                               |

| PWM_CL                    | 输出                                     | <b>通道C低端。</b> 低端驱动信号。                                                               |

### 表6. ADSP-CM41xF详细信号描述(续)

| 信号名称          | 方向   | 描述                                                                                                                |

|---------------|------|-------------------------------------------------------------------------------------------------------------------|

| PWM_DH        | 输出   | <b>通道D高端。</b> 高端驱动信号。                                                                                             |

| PWM_DL        | 输出   | <b>通道D低端。</b> 低端驱动信号。                                                                                             |

| PWM_SYNC      | 输入输出 | 同步信号。此输入用于外部产生的同步信号。如果同步信号由内部产生,则无需连接。                                                                            |

| PWM_TRIPA     | 输入   | 多路复用PWM断路A中断                                                                                                      |

| PWM_TRIPB     | 输入   | 多路复用PWM断路B中断                                                                                                      |

| PWM_TRIPC     | 输入   | 多路复用PWM断路C中断                                                                                                      |

| P_[nn]        | 输入输出 | 位置n。通用输入/输出。有关编程信息,参见硬件参考手册中的通用端口章节。                                                                              |

| REFCAP0       | 输入输出 | 带隙发生器滤波器节点输出。                                                                                                     |

| REFCAP1       | 输入输出 | 带隙发生器滤波器节点输出。                                                                                                     |

| REF_BUFOUT[n] | 输入输出 | 基准电压源缓冲输出                                                                                                         |

| SINC_CLK0     | 输入输出 | 时钟0                                                                                                               |

| SINC_D0       | 输入输出 | 数据0                                                                                                               |

| SINC_D1       | 输入输出 | 数据1                                                                                                               |

| SINC_D2       | 输入输出 | 数据2                                                                                                               |

| SINC_D3       | 输入输出 | 数据3                                                                                                               |

| SMC_ABE[n]    | 输出   | 字节使能n。指示访问存储器的低位字节或是高位字节。针对16位存储器执行高位字节异步写入时,SMC_ABE1b=0且SMC_ABE0b=1。针对16位存储器执行低位字节异步写入时,SMC_ABE1b=1且SMC_ABE0b=0。 |

| SMC_AMS[n]    | 输出   | 存储器选择n。通常连接存储器件的片选信号。                                                                                             |

| SMC_AOE       | 输出   | 输出使能。在读访问的建立周期起始时置位。                                                                                              |

| SMC_ARDY      | 输入   | 异步就绪。存储器件使用的流量控制信号,用来向SMC指示何时进行下一步处理。                                                                             |

| SMC_ARE       | 输出   | <b>读取使能。</b> 读访问起始时置位。                                                                                            |

| SMC_AWE       | 输出   | <b>写入使能</b> 。写访问周期期间置位。                                                                                           |

| SMC_A[nn]     | 输出   | 地址n。地址总线。                                                                                                         |

| SMC_D[nn]     | 输入输出 | 数据n。双向数据总线。                                                                                                       |

| SPI_CLK       | 输入输出 | 时钟。从机模式下为输入,主机模式下为输出。                                                                                             |

| SPI_D2        | 输入输出 | 数据2。用于四通道模式下的串行数据传输。ODM模式使能时为开漏。                                                                                  |

| SPI_D3        | 输入输出 | 数据3。用于四通道模式下的串行数据传输。ODM模式使能时为开漏。                                                                                  |

| SPI_MISO      | 输入输出 | <b>主机输入,从机输出。</b> 用于传输串行数据。工作方向与双通道和四通道模式下的SPI_MOSI相同。ODM模式使能时为开漏。                                                |

| SPI_MOSI      | 输入输出 | <b>主机输出,从机输入。</b> 用于传输串行数据。工作方向与双通道和四通道模式下的SPI_MISO相同。ODM模式使能时为开漏。                                                |

| SPI_RDY       | 输入输出 | 就绪。可选流信号。从机模式下为输出,主机模式下为输入。                                                                                       |

| SPI_SEL[n]    | 输出   | 从机选择输出n。用于主机模式,使能所需从机。                                                                                            |

| SPI_SS        | 输入   | <b>从机选择输入。</b> 从机模式: 用作从机选择输入。主机模式: 可选,用作多主机时的SPI错误检测输入。                                                          |

| SPT_ACLK      | 输入输出 | <b>通道A时钟。</b> 数据和帧同步相对于此时钟驱动/采样。该信号可以由内部或外部产生。                                                                    |

| SPT_AD0       | 输入输出 | <b>通道A数据0。</b> 主要双向数据I/O。该信号可配置为输出以发送串行数据,或者配置为输入以接收串行数据。                                                         |

| SPT_AD1       | 输入输出 | <b>通道A数据1。</b> 辅助双向数据I/O。该信号可配置为输出以发送串行数据,或者配置为输入以接收串行数据。                                                         |

| SPT_AFS       | 输入输出 | <b>通道A帧同步。</b> 帧同步脉冲启动串行数据移位。该信号可以由内部或外部产生。                                                                       |

### 表6. ADSP-CM41xF详细信号描述(续)

| 信号名称          | 方向   | 描述                                                          |

|---------------|------|-------------------------------------------------------------|

| SPT_ATDV      | 输出   | <b>通道A发送数据有效。</b> 该信号为可选,且仅当SPORT配置为多通道发送模式时激活。它在已使能的时隙间置位。 |

| SPT_BCLK      | 输入输出 | 通道B时钟。数据和帧同步相对于此时钟驱动/采样。该信号可以由内部或外部产生。                      |

| SPT_BD0       | 输入输出 | <b>通道B数据0</b> 。主要双向数据I/O。该信号可配置为输出以发送串行数据,或者配置为输入以接收串行数据。   |

| SPT_BD1       | 输入输出 | <b>通道B数据1。</b> 辅助双向数据I/O。该信号可配置为输出以发送串行数据,或者配置为输入以接收串行数据。   |

| SPT_BFS       | 输入输出 | 通道B帧同步。帧同步脉冲启动串行数据移位。该信号可以由内部或外部产生。                         |

| SPT_BTDV      | 输出   | <b>通道B发送数据有效。</b> 该信号为可选,且仅当SPORT配置为多通道发送模式时激活。它在已使能的时隙间置位。 |

| SYS_BMODE0    | 输入   | 引导模式控制n。选择处理器的引导模式。                                         |

| SYS_CLKIN0    | 输入   | 时钟/晶振输入                                                     |

| SYS_CLKIN1    | 输入   | 时钟/晶振输入                                                     |

| SYS_CLKOUT    | 输出   | <b>处理器时钟输出。</b> 输出内部时钟。可对时钟进行分频。详情参见硬件参考手册中的CGU部分。          |

| SYS_DSWAKE[n] | 输入输出 | 深度休眠唤醒n                                                     |

| SYS_FAULT     | 输入输出 | <b>高电平有效故障输出。</b> 指示内部故障或检测外部故障,取决于工作模式。                    |

| SYS_HWRST     | 输入   | <b>处理器硬件复位控制。</b> 置位时,复位器件。                                 |

| SYS_NMI       | 输入   | <b>不可屏蔽的中断。</b> 更多详情请参见硬件和编程参考手册。                           |

| SYS_RESOUT    | 输出   | <b>复位输出。</b> 表示器件处于复位状态。                                    |

| SYS_XTAL0     | 输出   | 晶振输出                                                        |

| SYS_XTAL1     | 输出   | 晶振输出                                                        |

| TM_ACI[n]     | 输入   | <b>备选捕捉输入n。</b> 在WIDCAP、WATCHDOG和PININT模式下提供额外输入。           |

| TM_ACLK[n]    | 输入   | <b>备选时钟n。</b> 提供额外的时基,用于独立定时器。                              |

| TM_CLK        | 输入   | 时钟。提供额外的全局时基,用于所有通用定时器。                                     |

| TM_TMR[n]     | 输入输出 | 定时器n。各定时器的主输入/输出信号。                                         |

| TRACE_CLK     | 输出   | <b>跟踪时钟。</b> 时钟输出。                                          |

| TRACE_D[nn]   | 输出   | <b>跟踪数据n</b> 。单向数据总线。                                       |

| TWI_SCL       | 输入输出 | <b>串行时钟。</b> 主机时为时钟输出,从机时为时钟输入。                             |

| TWI_SDA       | 输入输出 | <b>串行数据。</b> 接收或发送数据。                                       |

| UART_CTS      | 输入   | <b>清除发送。</b> 流控制信号。                                         |

| UART_RTS      | 输出   | <b>发送请求位。</b> 流控制信号。                                        |

| UART_RX       | 输入   | 接收。接收输入。通常连接至满足通信器件电气要求的收发器。                                |

| UART_TX       | 输出   | 发送。发送输出。通常连接至满足通信器件电气要求的收发器。                                |

| VDD_ANA[n]    | 输入输出 | 模拟电源电压                                                      |

| VDD_COMP      | 输入输出 | 过流比较器电源                                                     |

| VDD_EXT       | 输入输出 | 外部电压域                                                       |

### ADSP-CM412F/CM413F/CM416F/CM417F 176引脚LQFP信号描述

处理器引脚定义如表所示。该表中的列提供下列信息:

- 信号名称: 表中的"信号名称"列包含各引脚的信号 名称,以及每一个引脚的GPIO多路复用引脚功能(如 适用)。

- 描述: 表中的"描述"列提供信号的详细(描述性) 名称。

- 通用端口: 表中的"端口"列显示信号是否与其他信号多路复用至通用I/O端口引脚。

- 引脚名称: 表中的"引脚名称"列表示封装引脚(上电复位时)的名称,信号位于这些引脚上(单功能引脚)或多路复用(通用I/O引脚)。

| 信号名称       | 描述                    | 端口    | 引脚名称       |

|------------|-----------------------|-------|------------|

| ADC_VIN_A0 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_A0 |

| ADC_VIN_A1 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_A1 |

| ADC_VIN_A2 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_A2 |

| ADC_VIN_A3 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_A3 |

| ADC_VIN_A4 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_A4 |

| ADC_VIN_A5 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_A5 |

| ADC_VIN_A6 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_A6 |

| ADC_VIN_A7 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_A7 |

| ADC_VIN_B0 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_B0 |

| ADC_VIN_B1 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_B1 |

| ADC_VIN_B2 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_B2 |

| ADC_VIN_B3 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_B3 |

| ADC_VIN_B4 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_B4 |

| ADC_VIN_B5 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_B5 |

| ADC_VIN_B6 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_B6 |

| ADC_VIN_B7 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_B7 |

| ADC_VIN_C0 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_C0 |

| ADC_VIN_C1 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_C1 |

| ADC_VIN_C2 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_C2 |

| ADC_VIN_C3 | ADC1通道n单端模拟输入         | 未多路复用 | ADC_VIN_C3 |

| ADC_VIN_C4 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_C4 |

| ADC_VIN_C5 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_C5 |

| ADC_VIN_C6 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_C6 |

| ADC_VIN_C7 | ADC2通道n单端模拟输入         | 未多路复用 | ADC_VIN_C7 |

| ADC_VIN_D0 | ADC0通道n单端模拟输入         | 未多路复用 | ADC_VIN_D0 |

| ADC_VIN_D1 | ADC0通道n单端模拟输入         | 未多路复用 | ADC_VIN_D1 |

| ADC_VIN_D2 | ADC0通道n单端模拟输入         | 未多路复用 | ADC_VIN_D2 |

| ADC_VIN_D3 | ADC0通道n单端模拟输入         | 未多路复用 | ADC_VIN_D3 |

| ADC_VIN_D4 | ADC0通道n单端模拟输入         | 未多路复用 | ADC_VIN_D4 |

| ADC_VIN_D5 | ADC0通道n单端模拟输入         | 未多路复用 | ADC_VIN_D5 |

| ADC_VIN_D6 | ADC0通道n单端模拟输入         | 未多路复用 | ADC_VIN_D6 |

| BYP_A0     | 用于ADC的片内模拟电源调节旁路滤波器节点 | 未多路复用 | BYP_A0     |

| BYP_A1     | 用于ADC的片内模拟电源调节旁路滤波器节点 | 未多路复用 | BYP_A1     |

| BYP_D0     | 用于DAC的片内模拟电源调节旁路滤波器节点 | 未多路复用 | BYP_D0     |

| CAN0_RX    | CAN0接收                | Α     | PA_06      |

| CAN0_TX    | CAN0发送                | Α     | PA_07      |

| 信号名称                | 描述                | 端口         | 引脚名称          |

|---------------------|-------------------|------------|---------------|

| CAN1_RX             | CAN1接收            | E          | PE_12         |

| CAN1_TX             | CAN1发送            | E          | PE_13         |

| CNT0_DG             | CNTO递减计数和栅极       | С          | PC_13         |

| CNT0_OUTA           | CNTO输出分频器A        | В          | PB_08         |

| CNT0_OUTB           | CNTO输出分频器B        | В          | PB_10         |

| CNT0_UD             | CNT0递增计数和方向       | В          | PB_09         |

| CNT0_ZM             | CNT0零标记           | c          | PC_14         |

| COMP_OUT_A          | 快速过流保护比较器A输出      | 未多路复用      | COMP_OUT_A    |

| COMP_OUT_B          | 快速过流保护比较器B输出      | 未多路复用      | COMP_OUT_B    |

| COMP_OUT_C          | 快速过流保护比较器C输出      | 未多路复用      | COMP_OUT_C    |

| CPTMR0_IN0          | CPTMRO输入          | E          | PE_02         |

| _<br>CPTMR0_IN1     | CPTMRO输入          | E          | PE_04         |

| CPTMR0_IN2          | CPTMRO输入          | F          | PF_06         |

| DAC0_VOUT           | 模拟电压输出n           | 未多路复用      | DAC0_VOUT     |

| GND_ANA0            | VDD_ANA[n]模拟地返回   | 未多路复用      | GND_ANA0      |

| GND_ANA1            | VDD_ANA[n]模拟地返回   | 未多路复用      | GND_ANA1      |

| GND_ANA2            | VDD_ANA[n]模拟地返回   | 未多路复用      | GND_ANA2      |

| GND_ANA3            | VDD_ANA[n]模拟地返回   | 未多路复用      | GND_ANA3      |

| GND_ANA4_COMP       | AFE_GND_COMP_ANA4 | 未多路复用      | GND_ANA4_COMF |

| GND_ANA5_DAC        | AFE_GND_DAC_ANA5  | 未多路复用      | GND_ANA5_DAC  |

| GND_REFCAP0         | REF_INOUTO模拟地返回   | 未多路复用      | GND_REFCAP0   |

| GND_REFCAP1         | GND_REFCAP1       | 未多路复用      | GND_REFCAP1   |

| GND_VREF0           | REF_BUFOUT[n]接地返回 | 未多路复用      | GND_VREF0     |

| GND_VREF1           | REF_BUFOUT[n]接地返回 | 未多路复用      | GND_VREF1     |

| JTG_TCK             | JTAG时钟            | 未多路复用      | JTG_TCK/SWCLK |

| JTG_TDI             | JTAG串行数据输入        | 未多路复用      | JTG_TDI       |

| JTG_TDO             | JTAG串行数据输出        | 未多路复用      | JTG_TDO/SWO   |

| JTG_TMS             | JTAG模式选择          | 未多路复用      | JTG_TMS/SWDIO |

| JTG_TMS<br>JTG_TRST | JTAG复位            | 未多路复用      | JTG_TRST      |

|                     |                   | 不多斑及用<br>F | PF_03         |

| LBAO_PINO           | LBAOLBA数据输入或逻辑输出  | F          | PF_04         |

| LBAO_PIN1           | LBAOLBA牧村林人工型相输出  |            |               |

| LBAO_PIN2           | LBA0 LBA数据输入或逻辑输出 | F<br>  r   | PF_05         |

| LBAO_PIN3           | LBA0 LBA数据输入或逻辑输出 |            | PF_06         |

| LBAO_PIN4           | LBAO LBA数据输入或逻辑输出 | F          | PF_07         |

| LBAO_PIN5           | LBAO LBA数据输入或逻辑输出 | F          | PF_08         |

| LBA0_PIN6           | LBAO LBA数据输入或逻辑输出 | C          | PC_02         |

| LBA0_PIN7           | LBAO LBA数据输入或逻辑输出 | C          | PC_04         |

| PWM0_AH             | PWM0通道A高端         | В          | PB_00         |

| PWM0_AL             | PWM0通道A低端         | В          | PB_01         |

| PWM0_BH             | PWM0通道B高端         | В          | PB_02         |

| PWM0_BL             | PWMO通道B低端         | В          | PB_03         |

| PWM0_CH             | PWMO通道C高端         | В          | PB_04         |

| PWM0_CL             | PWM0通道C低端         | В          | PB_05         |

| PWM0_DH             | PWM0通道D高端         | В          | PB_06         |

| PWM0_DL             | PWM0通道D低端         | В          | PB_07         |

| PWM0_SYNC           | PWM0 同步信号         | D          | PD_00         |

| 信号名称        | 描述                 | 端口    | 引脚名称    |

|-------------|--------------------|-------|---------|

| PWM1_AH     | PWM1通道A高端          | В     | PB_08   |

| PWM1_AL     | PWM1通道A低端          | В     | PB_09   |

| PWM1_BH     | PWM1通道B高端          | В     | PB_10   |

| PWM1_BL     | PWM1通道B低端          | В     | PB_11   |

| PWM1_CH     | PWM1通道C高端          | В     | PB_12   |

| PWM1_CL     | PWM1通道C低端          | В     | PB_13   |

| PWM1_DH     | PWM1通道D高端          | В     | PB_14   |

| PWM1_DL     | PWM1通道D低端          | В     | PB_15   |

| PWM1_SYNC   | PWM1 同步信号          | E     | PE_09   |

| PWM2_AH     | PWM2通道A高端          | E     | PE_00   |

| PWM2_AL     | PWM2通道A低端          | Е     | PE_01   |

| PWM2_BH     | PWM2通道B高端          | Е     | PE_02   |

| PWM2_BL     | PWM2通道B低端          | Е     | PE_03   |

| PWM2_CH     | PWM2通道C高端          | Е     | PE_04   |

| PWM2_CL     | PWM2通道C低端          | E     | PE_05   |

| PWM2_DH     | PWM2通道D高端          | E     | PE_06   |

| PWM2_DL     | PWM2通道D低端          | Е     | PE_07   |

| PWM2_SYNC   | PWM2 同步信号同步信号      | Е     | PE_08   |

| PWM_TRIPA   | 多路复用PWM断路A信号       | D     | PD_01   |

| PWM_TRIPB   | 多路复用PWM断路B信号       | E     | PE_10   |

| PWM_TRIPC   | 多路复用PWM断路C信号       | Е     | PE_11   |

| REFCAP0     | 带隙发生器滤波器节点输出。      | 未多路复用 | REFCAP0 |

| REFCAP1     | 带隙发生器滤波器节点输出。      | 未多路复用 | REFCAP1 |

| REF_BUFOUT0 | 基准电压源ADC0和DAC0     | 未多路复用 | VREF0   |

| REF_BUFOUT1 | 基准电压源ADC1和过流比较器DAC | 未多路复用 | VREF1   |

| SINC0_CLK0  | SINCO时钟0           | С     | PC_15   |

| SINC0_D0    | SINC0数据0           | С     | PC_05   |

| SINC0_D1    | SINC0数据1           | С     | PC_06   |

| SINC0_D2    | SINC0数据2           | F     | PF_00   |

| SINC0_D3    | SINC0数据3           | F     | PF_01   |

| SMC0_A01    | SMC0地址n            | В     | PB_13   |

| SMC0_A02    | SMC0地址n            | В     | PB_15   |

| SMC0_A03    | SMC0地址n            | D     | PD_00   |

| SMC0_A04    | SMC0地址n            | D     | PD_01   |

| SMC0_A05    | SMC0地址n            | E     | PE_14   |

| SMC0_A06    | SMC0地址n            | F     | PF_00   |

| SMC0_A07    | SMC0地址n            | F     | PF_01   |

| SMC0_A08    | SMC0地址n            | F     | PF_02   |

| SMC0_A09    | SMC0地址n            | F     | PF_03   |

| SMC0_A10    | SMC0地址n            | E     | PE_15   |

| SMC0_A11    | SMC0地址n            | E     | PE_06   |

| SMC0_A12    | SMC0地址n            | E     | PE_07   |

| SMC0_A13    | SMC0地址n            | F     | PF_04   |

| SMC0_A14    | SMC0地址n            | E     | PE_05   |

| SMC0_A15    | SMC0地址n            | E     | PE_03   |

| SMC0_A16    | SMC0地址n            | Е     | PE_11   |

| 信号名称      | 描述            | 端口 | 引脚名称  |

|-----------|---------------|----|-------|

| SMC0_ABE0 | SMC0字节使能n     | Е  | PE_13 |

| SMC0_ABE1 | SMC0字节使能n     | E  | PE_12 |

| SMC0_AMS0 | SMC0存储器选择n    | В  | PB_04 |

| SMC0_AMS1 | SMC0存储器选择n    | E  | PE_01 |

| SMC0_AMS2 | SMC0存储器选择n    | E  | PE_02 |

| SMC0_AMS3 | SMC0存储器选择n    | E  | PE_08 |

| SMC0_AOE  | SMC0输出使能      | В  | PB_02 |

| SMC0_ARDY | SMC0异步就绪      | В  | PB_00 |

| SMC0_ARE  | SMC0读取使能      | В  | PB_03 |

| SMC0_AWE  | SMC0写入使能      | В  | PB_01 |

| SMC0_D00  | SMC0数据n       | В  | PB_05 |

| SMC0_D01  | SMCO数据n       | В  | PB_06 |

| SMC0_D02  | SMC0数据n       | В  | PB_07 |

| SMC0_D03  | SMC0数据n       | В  | PB_08 |

| SMC0_D04  | SMC0数据n       | В  | PB_09 |

| SMC0_D05  | SMC0数据n       | В  | PB_10 |

| SMC0_D06  | SMC0数据n       | В  | PB_11 |

| SMC0_D07  | SMC0数据n       | В  | PB_12 |

| SMC0_D08  | SMC0数据n       | С  | PC_09 |

| SMC0_D09  | SMCO数据n       | С  | PC_10 |

| SMC0_D10  | SMC0数据n       | С  | PC_11 |

| SMC0_D11  | SMC0数据n       | С  | PC_12 |

| SMC0_D12  | SMC0数据n       | С  | PC_13 |

| SMC0_D13  | SMC0数据n       | С  | PC_14 |

| SMC0_D14  | SMC0数据n       | С  | PC_05 |

| SMC0_D15  | SMC0数据n       | С  | PC_06 |

| SPIO_CLK  | SPIO时钟        | Α  | PA_08 |

| SPI0_D2   | SPIO数据2       | Α  | PA_02 |

| SPI0_D3   | SPIO数据3       | Α  | PA_03 |

| SPI0_MISO | SPIO主机输入、从机输出 | Α  | PA_10 |

| SPI0_MOSI | SPIO主机输出、从机输入 | Α  | PA_09 |

| SPI0_RDY  | SPIO就绪        | A  | PA_01 |

| SPI0_SEL1 | SPIO从机选择输出n   | Α  | PA_11 |

| SPI0_SEL2 | SPIO从机选择输出n   | Α  | PA_00 |

| SPI0_SEL3 | SPIO从机选择输出n   | Α  | PA_01 |

| SPI0_SEL4 | SPIO从机选择输出n   | Α  | PA_06 |

| SPI0_SEL5 | SPIO从机选择输出n   | Α  | PA_07 |

| SPI0_SEL6 | SPIO从机选择输出n   | Α  | PA_02 |

| SPI0_SEL7 | SPIO从机选择输出n   | Α  | PA_03 |

| SPI0_SS   | SPIO从机选择输入    | Α  | PA_00 |

| SPI1_CLK  | SPI1时钟        | С  | PC_09 |

| SPI1_D2   | SPI1数据2       | F  | PF_06 |

| SPI1_D3   | SPI1数据3       | F  | PF_07 |

| SPI1_MISO | SPI1主机输入、从机输出 | С  | PC_10 |

| SPI1_MOSI | SPI1主机输出、从机输入 | С  | PC_11 |

| SPI1_RDY  | SPI1就绪        | С  | PC_14 |

| 信号名称                  | 描述                             | 端口    | 引脚名称           |

|-----------------------|--------------------------------|-------|----------------|

| SPI1_SEL1             | SPI1从机选择输出n                    | С     | PC_12          |

| SPI1_SEL2             | SPI1从机选择输出n                    | C     | PC_13          |

| SPI1_SEL3             | SPI1从机选择输出n                    | C     | PC_14          |

| SPI1_SEL4             | SPI1从机选择输出n                    | F     | PF_02          |

| SPI1_SEL5             | SPI1从机选择输出n                    | F     | PF_05          |

| SPI1_SEL6             | SPI1从机选择输出n                    | F     | PF_03          |

| SPI1_SEL7             | SPI1从机选择输出n                    | F     | PF_08          |

| SPI1_SS               | SPI1从机选择输入                     | c     | PC_12          |

| SPT0_ACLK             | SPORTO通道A时钟                    | C     | PC_09          |

| SPT0_AD0              | SPORTO通道A数据0                   | В     | PB_09          |

| SPT0_AD1              | SPORTO通道A数据1                   | C     | PC_06          |

| SPTO_AFS              | SPORTO通道A帧同步                   | C     | PC_11          |

| SPT0_ATDV             | SPORTO通道A发送数据有效                | C     | PC_15          |

| SPTO_BCLK             | SPORTO通道A及达数路有效<br>SPORTO通道B时钟 | C     | PC_13          |

| SPT0_BCEK<br>SPT0_BD0 |                                | C     | PC_14          |

| SPT0_BD0<br>SPT0_BD1  | SPORT0通道B数据0<br>SPORT0通道B数据1   | C     | PC_14<br>PC_10 |

|                       |                                | C     |                |

| SPTO_BFS              | SPORTO通道B帧同步                   |       | PC_13          |

| SPT0_BTDV             | SPORTO通道B发送数据有效                | C     | PC_05          |

| SYS_BMODE0            | 引导模式控制n                        | 未多路复用 | SYS_BMODE0     |

| SYS_CLKIN0            | 时钟/晶振输入                        | 未多路复用 | SYS_CLKIN0     |

| SYS_CLKIN1            | 时钟/晶振输入                        | 未多路复用 | SYS_CLKIN1     |

| SYS_CLKOUT            | 处理器时钟输出                        | 未多路复用 | SYS_CLKOUT     |

| SYS_DSWAKE0           | 深度休眠唤醒n                        | C     | PC_05          |

| SYS_DSWAKE1           | 深度休眠唤醒n                        | D     | PD_00          |

| SYS_DSWAKE2           | 深度休眠唤醒n                        | F     | PF_08          |

| SYS_DSWAKE3           | 深度休眠唤醒n                        | A     | PA_11          |

| SYS_FAULT             | 故障输出                           | 未多路复用 | SYS_FAULT      |

| SYS_HWRST             | 处理器硬件复位控制                      | 未多路复用 | SYS_HWRST      |

| SYS_NMI               | 不可屏蔽的中断                        | 未多路复用 | SYS_NMI        |

| SYS_RESOUT            | 复位输出                           | 未多路复用 | SYS_RESOUT     |

| SYS_XTAL0             | 晶振输出                           | 未多路复用 | SYS_XTAL0      |

| SYS_XTAL1             | 晶振输出                           | 未多路复用 | SYS_XTAL1      |

| TM0_ACI0              | TIMERO备选捕获输入n                  | A     | PA_04          |

| ΓM0_ACI1              | TIMERO备选捕获输入n                  | A     | PA_06          |

| TM0_ACI2              | TIMERO备选捕获输入n                  | A     | PA_01          |

| ΓM0_ACI3              | TIMERO备选捕获输入n                  | A     | PA_02          |

| TM0_ACI4              | TIMERO备选捕获输入n                  | A     | PA_03          |

| TM0_ACLK0             | TIMERO备选时钟n                    | A     | PA_09          |

| TM0_ACLK1             | TIMERO备选时钟n                    | A     | PA_10          |

| TM0_ACLK2             | TIMERO备选时钟n                    | A     | PA_07          |

| TM0_ACLK3             | TIMERO备选时钟n                    | A     | PA_08          |

| _<br>TM0_ACLK4        | TIMERO备选时钟n                    | A     | PA_05          |

| TM0_CLK               | TIMERO时钟                       | A     | PA_00          |

| TM0_TMR0              | TIMERO定时器n                     | A     | PA_12          |

| TM0_TMR1              | TIMERO定时器n                     | A     | PA_13          |

| гмэ_тмит<br>ГМ1_ACI0  | TIMER1备选捕获输入n                  | E     | PE_12          |

| 信号名称       | 描述            | 端口    | 引脚名称     |

|------------|---------------|-------|----------|

| TM1_ACI2   | TIMER1备选捕获输入n | С     | PC_08    |

| TM1_ACI4   | TIMER1备选捕获输入n | C     | PC_09    |

| TM1_ACI5   | TIMER1备选捕获输入n | E     | PE_09    |

| TM1_ACI6   | TIMER1备选捕获输入n | F     | PF_05    |

| TM1_ACLK3  | TIMER1备选时钟n   | c     | PC_15    |

| TM1_ACLK4  | TIMER1备选时钟n   | С     | PC_00    |

| TM1_ACLK5  | TIMER1备选时钟n   | E     | PE_08    |

| TM1_CLK    | TIMER1时钟      | C     | PC_06    |

| TM1_TMR0   | TIMER1定时器n    | E     | PE_14    |

| TM1_TMR0   | TIMER1定时器n    | В     | PB_14    |

| TM1_TMR1   | TIMER1定时器n    | В     | PB_15    |

|            |               | E     | PE_15    |

| TM1_TMR1   | TIMER1定时器n    |       |          |

| TM1_TMR2   | TIMER1定时器n    | В     | PB_13    |

| TM1_TMR3   | TIMER1定时器n    | C     | PC_10    |

| TM1_TMR4   | TIMER1定时器n    | E     | PE_04    |

| TM1_TMR5   | TIMER1定时器n    | F _   | PF_06    |

| TM1_TMR6   | TIMER1定时器n    | E     | PE_02    |

| TM1_TMR7   | TIMER1定时器n    | C     | PC_12    |

| TRACEO_CLK | TRACE0跟踪时钟    | C     | PC_00    |

| TRACEO_D00 | TRACE0跟踪数据n   | C     | PC_03    |

| TRACE0_D01 | TRACEO跟踪数据n   | C     | PC_01    |

| TRACE0_D02 | TRACEO跟踪数据n   | C     | PC_04    |

| TRACE0_D03 | TRACEO跟踪数据n   | C     | PC_02    |

| TWI0_SCL   | TWI0串行时钟      | 未多路复用 | TWI0_SCL |

| TWI0_SDA   | TWI0串行数据      | 未多路复用 | TWI0_SDA |

| UARTO_CTS  | UART0允许发送     | A     | PA_03    |

| UARTO_RTS  | UARTO请求发送     | A     | PA_02    |

| UARTO_RX   | UART0接收       | A     | PA_04    |

| UARTO_TX   | UART0发送       | A     | PA_05    |

| UART1_CTS  | UART1允许发送     | c     | PC_05    |

| UART1_RTS  | UART1请求发送     | c     | PC_15    |

| UART1_RX   | UART1接收       | E     | PE_09    |

| UART1_TX   | UART1发送       | E     | PE_10    |

| UART2_CTS  | UART2允许发送     | C     | PC_06    |

| UART2_RTS  | UART2请求发送     | В     | PB_09    |

| UART2_RX   | UART2接收       | C     | PC_09    |

| UART2_TX   | UART2发送       | C     | PC_11    |

|            | UART3允许发送     |       | PB_07    |

| UART3_CTS  |               | В     |          |

| UART3_RTS  | UART3请求发送     | E     | PE_08    |

| UART3_RX   | UART3接收       | C     | PC_08    |

| UART3_TX   | UART3发送       | C     | PC_07    |

| UART4_CTS  | UART4允许发送     | E _   | PE_03    |

| UART4_RTS  | UART4请求发送     | E     | PE_01    |

| UART4_RX   | UART4接收       | F     | PF_05    |

| UART4_TX   | UART4发送       | F     | PF_04    |

| VDD_ANA0   | 模拟电源电压        | 未多路复用 | VDD_ANA0 |

### 表7. ADSP-CM412F/CM413F/CM416F/CM417F 176引脚LQFP信号描述(续)

| 信号名称     | 描述      | 端口    | 引脚名称     |

|----------|---------|-------|----------|

| VDD_ANA1 | 模拟电源电压  | 未多路复用 | VDD_ANA1 |

| VDD_COMP | 过流比较器电源 | 未多路复用 | VDD_COMP |

| VDD_EXT  | 外部电压域   | 未多路复用 | VDD_EXT  |

# ADSP-CM412F/CM413F/CM416F/CM417F 176引脚LQFP GPIO多路复用

表8至表13列出了多路复用至176引脚LQFP封装上通用I/O引脚的引脚功能。

### 表8. 端口A信号多路复用

| 信号名称  | 多路复用功能0   | 多路复用功能1   | 多路复用功能2   | 多路复用功能3 | 多路复用功能输入<br>抽头 |

|-------|-----------|-----------|-----------|---------|----------------|

| PA_00 | SPI0_SEL2 | TM0_CLK   |           |         | SPIO_SS        |

| PA_01 | SPI0_SEL3 | SPI0_RDY  |           |         | TM0_ACI2       |

| PA_02 | SPI0_D2   | UARTO_RTS | SPIO_SEL6 |         | TM0_ACI3       |

| PA_03 | SPI0_D3   | UARTO_CTS | SPI0_SEL7 |         | TM0_ACI4       |

| PA_04 | UARTO_RX  |           |           |         | TM0_ACI0       |

| PA_05 | UARTO_TX  |           |           |         | TM0_ACLK4      |

| PA_06 | CAN0_RX   | SPI0_SEL4 |           |         | TM0_ACI1       |

| PA_07 | CAN0_TX   | SPI0_SEL5 |           |         | TM0_ACLK2      |

| PA_08 | SPI0_CLK  |           |           |         | TM0_ACLK3      |

| PA_09 | SPI0_MOSI |           |           |         | TM0_ACLK0      |

| PA_10 | SPI0_MISO |           |           |         | TM0_ACLK1      |

| PA_11 | SPI0_SEL1 |           |           |         | SYS_DSWAKE3    |

| PA_12 | TM0_TMR0  |           |           |         |                |

| PA_13 | TM0_TMR1  |           |           |         |                |

### 表9. 端口B信号多路复用

| 信号名称  | 多路复用功能0 | 多路复用功能1   | 多路复用功能2   | 多路复用功能3  | 多路复用功能输入<br>抽头 |

|-------|---------|-----------|-----------|----------|----------------|

| PB_00 | PWM0_AH |           | SMC0_ARDY |          |                |

| PB_01 | PWM0_AL |           | SMC0_AWE  |          |                |

| PB_02 | PWM0_BH |           | SMC0_AOE  |          |                |

| PB_03 | PWM0_BL |           | SMC0_ARE  |          |                |

| PB_04 | PWM0_CH |           | SMC0_AMS0 |          |                |

| PB_05 | PWM0_CL |           | SMC0_D00  |          |                |

| PB_06 | PWM0_DH |           | SMC0_D01  |          |                |

| PB_07 | PWM0_DL | UART3_CTS | SMC0_D02  |          |                |

| PB_08 | PWM1_AH | CNT0_OUTA | SMC0_D03  |          |                |

| PB_09 | PWM1_AL | UART2_RTS | SMC0_D04  | SPT0_AD0 | CNT0_UD        |

| PB_10 | PWM1_BH | CNT0_OUTB | SMC0_D05  |          |                |

| PB_11 | PWM1_BL |           | SMC0_D06  |          |                |

| PB_12 | PWM1_CH |           | SMC0_D07  |          |                |

| PB_13 | PWM1_CL | TM1_TMR2  | SMC0_A01  |          |                |

| PB_14 | PWM1_DH |           |           | TM1_TMR0 |                |

| PB_15 | PWM1_DL |           | SMC0_A02  | TM1_TMR1 |                |

### 表10. 端口C信号多路复用

| 信号名称  | 多路复用功能0    | 多路复用功能1   | 多路复用功能2  | 多路复用功能3   | 多路复用功能输入<br>抽头 |

|-------|------------|-----------|----------|-----------|----------------|

| PC_00 | TRACEO_CLK |           |          |           | TM1_ACLK4      |

| PC_01 | TRACE0_D01 |           |          |           |                |

| PC_02 | TRACE0_D03 |           |          | LBA0_PIN6 |                |

| PC_03 | TRACE0_D00 |           |          |           |                |

| PC_04 | TRACE0_D02 |           |          | LBA0_PIN7 |                |

| PC_05 | SINC0_D0   | UART1_CTS | SMC0_D14 | SPT0_BTDV | SYS_DSWAKE0    |

| PC_06 | SINC0_D1   | UART2_CTS | SMC0_D15 | SPT0_AD1  | TM1_CLK        |

| PC_07 | UART3_TX   |           |          |           |                |

| PC_08 | UART3_RX   |           |          |           | TM1_ACI2       |

| PC_09 | SPI1_CLK   | UART2_RX  | SMC0_D08 | SPT0_ACLK | TM1_ACI4       |

| PC_10 | SPI1_MISO  | TM1_TMR3  | SMC0_D09 | SPT0_BD1  |                |

| PC_11 | SPI1_MOSI  | UART2_TX  | SMC0_D10 | SPT0_AFS  |                |

| PC_12 | SPI1_SEL1  | TM1_TMR7  | SMC0_D11 | SPT0_BCLK | SPI1_SS        |

| PC_13 | SPI1_SEL2  |           | SMC0_D12 | SPT0_BFS  | CNT0_DG        |

| PC_14 | SPI1_SEL3  | SPI1_RDY  | SMC0_D13 | SPT0_BD0  | CNT0_ZM        |

| PC_15 | SINC0_CLK0 | UART1_RTS |          | SPT0_ATDV | TM1_ACLK3      |

## 表11. 端口D信号多路复用

| 信号名称  | 多路复用功能0   | 多路复用功能1 | 多路复用功能2  | 多路复用功能3 | 多路复用功能输入<br>抽头 |

|-------|-----------|---------|----------|---------|----------------|

| PD_00 | PWM0_SYNC |         | SMC0_A03 |         | SYS_DSWAKE1    |

| PD_01 | PWM_TRIPA |         | SMC0_A04 |         |                |

### 表12. 端口E信号多路复用

| <del></del> |           |           |           |         | 多路复用功能输入   |

|-------------|-----------|-----------|-----------|---------|------------|

| 信号名称        | 多路复用功能0   | 多路复用功能1   | 多路复用功能2   | 多路复用功能3 | 抽头         |

| PE_00       | PWM2_AH   |           |           |         |            |

| PE_01       | PWM2_AL   | UART4_RTS | SMC0_AMS1 |         |            |

| PE_02       | PWM2_BH   | TM1_TMR6  | SMC0_AMS2 |         | CPTMR0_IN0 |

| PE_03       | PWM2_BL   | UART4_CTS | SMC0_A15  |         |            |

| PE_04       | PWM2_CH   | TM1_TMR4  |           |         | CPTMR0_IN1 |

| PE_05       | PWM2_CL   |           | SMC0_A14  |         |            |

| PE_06       | PWM2_DH   |           | SMC0_A11  |         |            |

| PE_07       | PWM2_DL   |           | SMC0_A12  |         |            |

| PE_08       | PWM2_SYNC | UART3_RTS | SMC0_AMS3 |         | TM1_ACLK5  |

| PE_09       | PWM1_SYNC | UART1_RX  |           |         | TM1_ACI5   |

| PE_10       | PWM_TRIPB | UART1_TX  |           |         |            |

| PE_11       | PWM_TRIPC |           | SMC0_A16  |         |            |

| PE_12       | CAN1_RX   |           | SMC0_ABE1 |         | TM1_ACI0   |

| PE_13       | CAN1_TX   |           | SMC0_ABE0 |         |            |

| PE_14       | TM1_TMR0  |           | SMC0_A05  |         |            |

## 表12. 端口E信号多路复用(续)

| 信号名称  | 多路复用功能0  | 多路复用功能1 | 多路复用功能2  | 多路复用功能输入<br>抽头 |

|-------|----------|---------|----------|----------------|

| PE_15 | TM1_TMR1 |         | SMC0_A10 |                |

## 表13.端口F信号多路复用

| 信号名称  | 多路复用功能0   | 多路复用功能1   | 多路复用功能2  | 多路复用功能3   | 多路复用功能输入<br>抽头 |

|-------|-----------|-----------|----------|-----------|----------------|

| PF_00 | SINC0_D2  |           | SMC0_A06 |           |                |

| PF_01 | SINC0_D3  |           | SMC0_A07 |           |                |

| PF_02 | SPI1_SEL4 |           | SMC0_A08 |           |                |

| PF_03 | SPI1_SEL6 |           | SMC0_A09 | LBA0_PIN0 |                |

| PF_04 | UART4_TX  |           | SMC0_A13 | LBA0_PIN1 |                |