# **Automotive Audio Bus A<sup>2</sup>B Transceiver**

## **Data Sheet**

## AD2421W/AD2422W/AD2425W

#### **A2B BUS FEATURES**

Line topology

Single master, multiple slave

Up to 15 m between nodes and up to 40 m overall cable length

Communication over distance

Synchronous data

Multichannel I<sup>2</sup>S/TDM to I<sup>2</sup>S/TDM

Clock synchronous, phase aligned in all nodes

Low latency slave to slave communication

Control and status information I<sup>2</sup>C to I<sup>2</sup>C

**GPIO** over distance

Phantom power or local power slave nodes Configurable with SigmaStudio graphical software tool Qualified for automotive applications

## **ADDITIONAL TRANSCEIVER FEATURES**

Configurable as  $A^2B$  bus master or slave (AD2425W)  $I^2C$  interface

8-bit to 32-bit multichannel I<sup>2</sup>S/TDM interface I<sup>2</sup>S/TDM/PDM programmable data rate Up to 32 upstream and 32 downstream channels PDM inputs for 4 high dynamic range microphones

## **APPLICATIONS**

Automotive audio communication link

Active noise cancellation

Microphone arrays for hands free and in car communication

microphone arrays for namus free and in car communication

### **GENERAL DESCRIPTION**

The Automotive Audio Bus ( $A^2B^{\otimes}$ ) provides a multichannel,  $I^2S/TDM$  link over distances of up to 15 m between nodes. It embeds bidirectional synchronous data (for example digital audio), clock, and synchronization signals onto a single differential wire pair.  $A^2B$  supports a direct point to point connection and allows multiple, daisy-chained nodes at different locations to contribute or consume time division multiplexed channel content.  $A^2B$  is a single-master, multiple-slave system where the transceiver chip at the host controller is the master. The master generates clock, synchronization, and framing for all slave nodes. The master  $A^2B$  chip is programmable over a control bus ( $I^2C$ ) for configuration and read back. An extension of this control bus is embedded in the  $A^2B$  data stream, which grants direct access of registers and status information on slave transceivers as well as  $I^2C$  to  $I^2C$  communication over distance.

**Table 1. Product Comparison Guide**

| Feature                           | AD2421W | AD2422W | AD2425W |

|-----------------------------------|---------|---------|---------|

| Master capable                    | No      | No      | Yes     |

| Functional TRX blocks             | A only  | A + B   | A + B   |

| I <sup>2</sup> S/TDM support      | No      | No      | Yes     |

| PDM microphone inputs             | 4 mics  | 4 mics  | 4 mics  |

| Maximum node to node cable length | 15 m    | 15 m    | 15 m    |

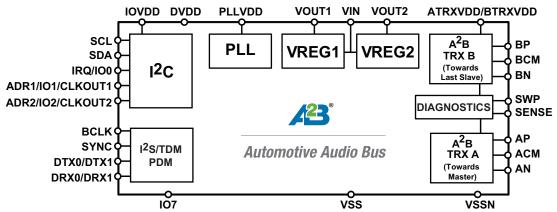

### **FUNCTIONAL BLOCK DIAGRAM**

The A<sup>2</sup>B and the A<sup>2</sup>B logos are registered trademarks of Analog Devices, Inc.

Rev. SpA

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

I<sup>2</sup>C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

©2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

D14853-0-6/17(SpA)

www.analog.com