Page

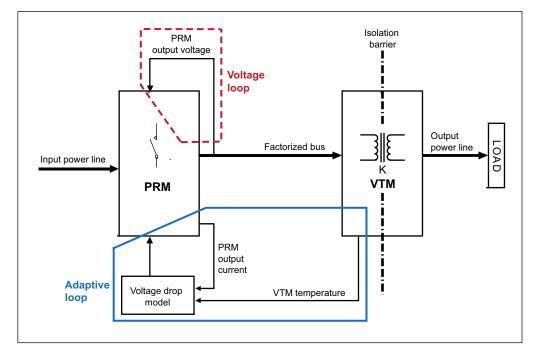

Figure 1

Adaptive loop regulation conceptual diagram

# Accurate Point-of-Load Voltage Regulation Using Simple Adaptive Loop Feedback

By Maurizio Salato Principal Engineer, V-I Chip Applications Engineering

#### Contents

#### Introduction

| Introduction                                          | 1  |

|-------------------------------------------------------|----|

| Adaptive Loop<br>Regulation Concept                   | 1  |

| PRM-AL Block Diagram                                  | 2  |

| DC Set Point<br>Calculation                           | 4  |

| Considerations                                        | 8  |

| Adaptive Loop with<br>Half-Chip VTMs                  | 9  |

| Design Example with<br>V•I Chip <sup>™</sup> Customer |    |

| Boards                                                | 13 |

| Conclusion                                            | 17 |

Accurate point-of-load (POL) voltage control is essential for highly dynamic electronic loads. 'Adaptive loop' is a technique for efficient, feed-forward compensation of isolated power management systems based on PRM<sup>™</sup> Regulator and VTM<sup>™</sup> Voltage Transformer combinations. This application note describes the design methodology for optimal DC set point compensation of PRM and VTM combinations<sup>[a]</sup>, including small arrays of two identical VTMs driven by one PRM.

For your reference, an automated spreadsheet version of the following procedure is available at http://cdn.vicorpower.com/documents/calculators/dcaldesign.xls.

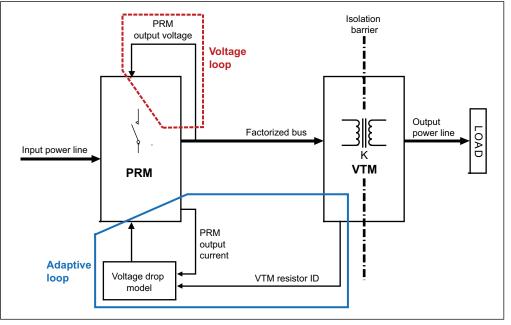

### Adaptive Loop Regulation Concept

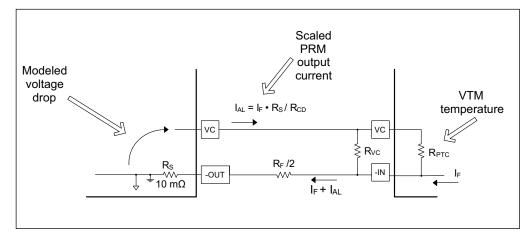

Adaptive loop is a model-based, positive-feedback compensation technique that can easily complement negative feedback, voltage mode regulation. Figure 1 shows the conceptual block diagram.

While the local voltage feedback loop maintains regulation at the PRM output, the adaptive loop (AL) provides compensation for the voltage drops that occur from the PRM output to the actual load. As stated before, AL is based on a model that requires VTM temperature and factorized bus current as inputs. The resistive behavior of power lines (factorized bus and output line) as well as the VTM, enables accurate modeling of their voltage drops.

<sup>[a]</sup> The calculations represented in this application note apply to 24 V, 36 V and 48 V input PRMs. Though the same methodology applies to 28 V input MIL-COTS PRMs, care should be taken to apply the correct values. For further assistance, please contact a Field Applications Engineer via your local Technical Support Center.

| vicorpower.com | 800-735-6200 | Rev. 1.3 | 01/2011 | FACTORIZED POWER |

|----------------|--------------|----------|---------|------------------|

|                |              |          |         | Page 1 of 18     |

Major benefits of this approach are:

- No signals need to be transmitted across VTM's isolation barrier

- Simpler circuit, lower component count

Regulation accuracy is affected by the accuracy of this model; this application note explains how to optimize the model for a given system, and how to estimate the obtained accuracy.

Standard regulation techniques are based on direct observation and integral error compensation of POL voltage, and the steady state error (compared to the reference) is therefore forced to be zero. AL only asymptotically approaches the zero error state, therefore widening the total distribution of the POL voltage.

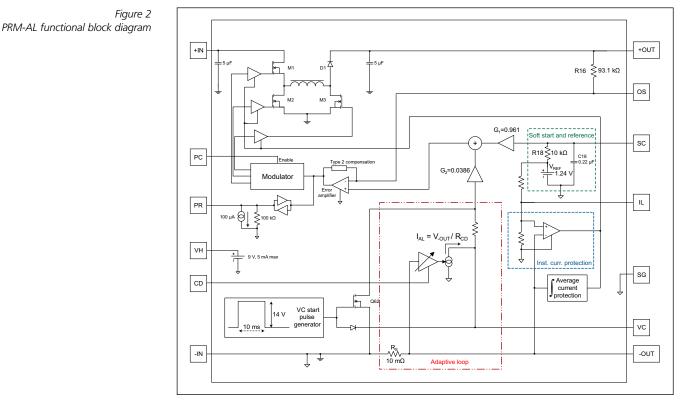

### PRM-AL Block Diagram

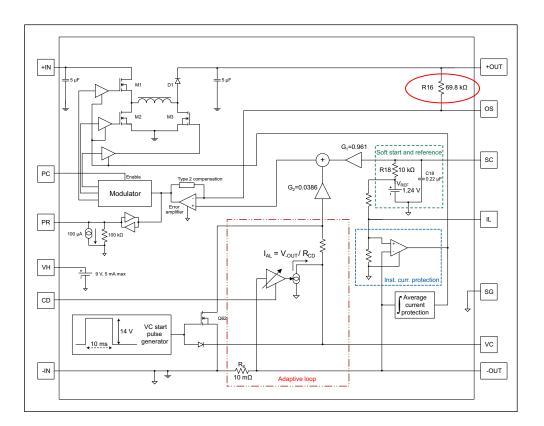

Figure 2 shows the functional block diagram for a full-chip PRM-AL regulator (e.g. P045F048T32AL). The OS and SC pins provide for local voltage feedback loop setting, while the VC and CD pins provide for settings and connections of the downstream system model.

In summary:

- Local voltage feedback loop:

- V<sub>REF</sub>, through R18, provides a reference voltage source on the SC pin. This is routed to the non-inverting input of the error amplifier, through the gain stage G1.

- The factorized bus (+OUT) voltage is fed back to the inverting input of the error amplifier through R16.

- SC and OS provide for the connection of the external resistor dividers.

VICOR vicorpower.com 800-735-6200 Rev. 1.3 01/2011

- Adaptive loop circuit:

- The voltage controlled current source has variable gain, controlled by the resistance connected between CD and signal ground (SG) pins. The current injected on the VC line by the variable gain transconductance amplifier is:

- directly proportional to the voltage across the sense resistor  $R_S$

- inversely proportional to the resistor connected between CD and SG

according to the following relationship:

Equation 1

$$I_{AL} = \frac{V_{-OUT}}{R_{CD}} = \frac{R_S I_F}{R_{CD}}$$

where  $I_F$  is the factorized bus (PRM output) current and  $V_{-OUT}$  is the voltage drop across  $R_S$ .

- The VC pin voltage is added to the reference pin voltage SC through the gain stage G<sub>2</sub>.

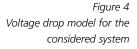

A PRM and VTM system is considered, as shown in the block diagram in Figure 3. The system PCB adds further voltage drops from the PRM output to the load: the factorized bus resistance,  $R_F$ , and the output line resistance,  $R_O$ , which are assumed to be constant and equally divided on the positive and negative trace / wire. In order to account for them, these resistances must be estimated or measured.

It is important to correctly identify the total voltage drop parameters, which are  $R_F$ ,  $R_{OUT}$  and  $R_O$  in this specific case. Their compensation model must therefore be resistive, and temperature dependent.

Such a model is easy to implement, thanks to:

- The PTC resistor embedded in the VTM module, which will change its value according to the VTM temperature.

- R<sub>VC</sub> resistor, which allows precise match of R<sub>PTC</sub> to VTM R<sub>OUT</sub> temperature characteristic.

Figure 3 Factorized Power Architecture (FPA<sup>™</sup>) system with adaptive loop control block diagram

The parallel of  $R_{VC}$  and  $R_{PTC}$  resistors, in series with  $R_F/2$  and  $R_S$  resistors constitutes the voltage drop model. The AL circuitry forces a scaled version of the PRM output current ( $I_{AL}$ ) in the VC line, which then merges with the factorized bus current  $I_F$  on its return path (as shown in Figure 4).

The voltage obtained on the VC pin, with some scale factor, is the model of the total voltage drop in the system.

# **DC Set Point Calculation**

The necessary inputs to the procedure are shown in Table 1.

| Table 1                   |

|---------------------------|

| Adaptive loop calculation |

| procedure inputs          |

| Standard Full-Chip VTM Characteristics                                                     | Power System Characteristics                                                              |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| • R <sub>OUT_25</sub> : 25°C output resistance                                             | • V <sub>F_NOM</sub> : nominal factorized bus voltage                                     |

| • R <sub>OUT_100</sub> : 100°C output resistance                                           | at no load                                                                                |

| • K: transformer ratio                                                                     | <ul> <li>I<sub>OUT</sub>: maximum system (VTM) output<br/>current</li> </ul>              |

| • R <sub>PTC_25</sub> : PTC resistance at 25°C                                             | • R <sub>F</sub> : factorized bus (PRM to VTM) total                                      |

| • R <sub>PTC_100</sub> : PTC resistance at 100°C                                           | resistance                                                                                |

| <ul> <li>P<sub>NL</sub>: no load power dissipation at<br/>nominal input voltage</li> </ul> | <ul> <li>R<sub>0</sub>: output bus (VTM to point of load)<br/>total resistance</li> </ul> |

Table 2 summarizes the data for standard full-chip VTM transformers. It is important to note that the internal resistors in the PRM have 1% tolerance.

Table 2 Standard full-chip VTM data required (typical)

|                 | Output Resistance   |                      |           | Temperature Sensor  |                      |           |

|-----------------|---------------------|----------------------|-----------|---------------------|----------------------|-----------|

| VTM Part Number | R <sub>OUT_25</sub> | R <sub>OUT_100</sub> | Tolerance | R <sub>PTC_25</sub> | Temp.<br>Coeff.(TCR) | Tolerance |

|                 | [mΩ]                | <b>[m</b> Ω]         | [%]       | <b>[</b> Ω <b>]</b> | [%/°C]               | [%]       |

| V048F015T100    | 0.99                | 1.17                 | 11        | 3000                |                      |           |

| V048F020T080    | 1.31                | 1.56                 | 10        | 2000                |                      |           |

| V048F030T070    | 1.61                | 1.97                 | 10        |                     | 0.39                 | 5         |

| V048F040T050    | 2.76                | 3.29                 | 8         | 1000<br>560         |                      |           |

| V048F060T040    | 5.76                | 6.73                 | 5         |                     |                      |           |

| V048F080T030    | 7.54                | 8.76                 | 8         |                     |                      |           |

| V048F096T025    | 9.84                | 11.97                | 10        | 200                 |                      |           |

| V048F120T025    | 10.85               | 13.39                | 6         |                     |                      |           |

| V048F160T015    | 29.76               | 32.80                | 7         |                     |                      |           |

| V048F240T012    | 48.11               | 57.17                | 4         | 510                 |                      |           |

| V048F320T009    | 79.48               | 96.10                | 6         |                     |                      |           |

| V048F480T006    | 177.44              | 215.63               | 5         |                     |                      |           |

With reference to Figure 3:

A.Calculate the maximum voltage drop (at 25°C and 100°C) due to VTM output resistance R<sub>OUT</sub>.

Equation 2

$$\Delta V_{ROUT_{25}} = R_{OUT_{25}} \cdot I_{OUT}$$

Equation 3

$$\Delta V_{ROUT \ 100} = R_{OUT \ 100} \cdot I_{OUT}$$

B. Calculate the maximum current flowing on the factorized bus.

Equation 4

$$I_F = K \cdot I_{OUT} + \frac{P_{NL}}{V_{F NOM}}$$

Although the no load power (P<sub>NL</sub>) required by the VTM is input voltage dependent, the variation has only a minor influence on the AL compensation, and will therefore be neglected in the following steps.

C.Calculate the total PRM output voltage increase that will compensate all the drops (factorized bus resistance, VTM output resistance and output bus resistance).

Equation 5

$$\Delta V_{F_25} = \frac{\Delta V_{ROUT_25} + R_0 I_{OUT}}{K} + (R_F + R_S) \cdot I_F$$

$$\Delta V_{F_{-}100} = \frac{\Delta V_{ROUT_{-}100} + R_{O}I_{OUT}}{K} + (R_{F} + R_{S}) \cdot I_{F}$$

Rev. 1.3

Equation 6

vicorpower.com

800-735-6200

01/2011

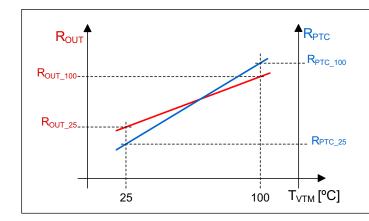

Figure 5

temperature

ROUT and RPTC vs. VTM internal

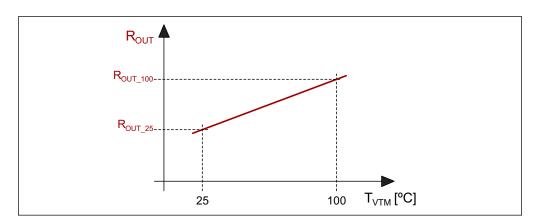

D.Calculate the total temperature coefficient of the power circuit and the  $R_{VC}$  resistor needed to match it.

The PTC resistor and the VTM  $R_{OUT}$  resistance are subject to the same temperature, but they have different rates of change, as shown in Figure 5.

In order for the model to precisely match the voltage drop over temperature, its slope must match the system slope. The  $R_{VC}$  resistor in parallel to  $R_{PTC}$  can be calculated in order to meet this condition.

$$\Delta R_{TOT} = \frac{\Delta V_{F\_100}}{\Delta V_{F\_25}} = \frac{\frac{R_{VC} \cdot R_{PTC\_100}}{R_{VC} + R_{PTC\_100}}}{\frac{R_{VC} \cdot R_{PTC\_25}}{R_{VC} + R_{PTC\_25}}} \Longrightarrow$$

Equation 7

$$R_{VC} = (1 - \Delta R_{TOT}) \frac{R_{PTC_{25}} \cdot R_{PTC_{100}}}{\Delta R_{TOT} \cdot R_{PTC_{25}} - R_{PTC_{100}}}$$

There is an important reason for choosing a parallel rather than a series resistor to match the system temperature coefficient. At start-up, the PRM issues a 14 V, 10 ms pulse on the VC line to synchronously start the VTM. A series resistor would cause significant amplitude change on this signal, avoided by the parallel arrangement. However, the designer should exercise judgment and avoid extreme cases, where the temperature dependency might be so low as to cause the R<sub>VC</sub> value to fall below 200  $\Omega$  (which would cause overload during the 14 V, 10 ms startup pulse).

E. Calculate the maximum VC pin voltage for the given system at 25°C (100°C should provide the same value, given the temperature dependency has been taken care of through  $R_{VC}$ , [7]):

$$V_{C_{MAX_{25}}} = I_{AL} \cdot \frac{R_{PTC_{25}} \cdot R_{VC}}{R_{PTC_{25}} + R_{VC}} + (I_F + I_{AL}) \cdot \left(\frac{R_F}{2} + R_S\right) =$$

Equation 8

$$= R_{S} \frac{I_{F}}{R_{CD_{MIN}}} \cdot \frac{R_{PTC_{25}} \cdot R_{VC}}{R_{PTC_{25}} + R_{VC}} + (I_{F} + R_{S} \frac{I_{F}}{R_{CD_{MIN}}}) \cdot \left(\frac{R_{F}}{2} + R_{S}\right)$$

Minimum allowable  $R_{CD}$  value for current products is 20  $\Omega.$

F. Calculate the needed (if any) V<sub>SC</sub> trim that allows enough AL dynamic range under the worst case:  $V_{C\_MAX_{25}}$  and  $\Delta V_{F_{100}}$  (this will allow enough design margin).

The voltage on VC, through the gain stage  $G_2$ , is summed to the reference voltage SC in order to compensate for the voltage drop  $\Delta V_F$ . Because the VC voltage dynamic range is set,  $V_{SC}$  might be reduced in order to match the relative changes of factorized bus and adaptive loop compensation.

Equation 9

$$\frac{\Delta V_{F\_100}}{V_{F\_NOM}} \leq \frac{G_2 \cdot V_{C\_MAX\_25}}{G_1 \cdot V_{SC}} \implies V_{SC} \leq \frac{G_2 \cdot V_{C\_MAX\_25}}{G_1 \frac{\Delta V_{F\_100}}{V_{F\_NOM}}}$$

G<sub>1</sub> and G<sub>2</sub> gains are 0.961 and 0.0386 respectively.

If  $V_{SC} \leq V_{ref} = 1.24$  V, the external resistor to be connected on SC will be easily calculated as following:

Equation 10

$$R_{SC} = R_{18} \frac{V_{SC}}{V_{ref} - V_{SC}}$$

The absolute minimum value for V<sub>SC</sub> is 0.25 V, because of the characteristic of the internal error amplifier. The minimum resistance value for  $R_{SC}$  is therefore 2550  $\Omega$ .

G.Calculate the voltage feedback divider resistor needed to set the nominal output voltage.

Equation 11

$$V_{F_{NOM}} = G_1 \cdot V_{SC} \frac{R_{16} + R_{OS}}{R_{OS}} \implies R_{OS} = G_1 \cdot R_{16} \frac{V_{SC}}{V_{F_{NOM}} - G_1 \cdot V_{SC}}$$

$R_{OS}$  defines the gain on the voltage feedback, which accommodates for the chosen reference voltage  $V_{SC}$ . It is recommended to calculate its value using the  $V_{SC}$  voltage obtained with a standardized value resistor as  $R_{SC}$ . Moreover, if a standard value resistor is not available to match (within 0.2%) the calculated  $R_{OS}$  value, it is strongly recommended to use a parallel configuration.

H. Calculate the  $R_{CD}$  resistor that allows AL to compensate for the drops (25°C or 100°C will give the same result, because of  $R_{VC}$ ).

First, substitute the VC line voltage at full  $I_F$  current (room temperature):

Equation 12

$$V_{C_25} = \frac{R_s \cdot I_F}{R_{CD}} \cdot \frac{R_{PTC_25} \cdot R_{VC}}{R_{PTC_25} + R_{VC}} + \left(\frac{R_s \cdot I_F}{R_{CD}} + I_F\right) \cdot \left(\frac{R_F}{2} + R_s\right)$$

into the expression for the related factorized bus increase:

$$\begin{split} \Delta V_{F_{25}} &= G_2 \cdot V_{C_{25}} \frac{R_{16} + R_{OS}}{R_{OS}} = \\ &= G_2 \cdot \frac{R_s \cdot I_F}{R_{CD}} \cdot \frac{R_{PTC_{25}} \cdot R_{VC}}{R_{PTC_{25}} + R_{VC}} + \left(\frac{R_s \cdot I_F}{R_{CD}} + I_F\right) \cdot \left(\frac{R_F}{2} + R_s\right) \frac{R_{16} + R_{OS}}{R_{OS}} \end{split}$$

Then solve for  $R_{CD}$ :

Equation 13

$$R_{CD} = \frac{G_2 \frac{R_{16} + R_{OS}}{R_{OS}} R_S I_F \left( \frac{R_{PTC_2 25} \cdot R_{VC}}{R_{PTC_2 25} + R_{VC}} + \frac{R_F}{2} + R_S \right)}{\Delta V_{F_2 25} - G_2 \frac{R_{16} + R_{OS}}{R_{OS}} \left( \frac{R_F}{2} + R_S \right) I_F}$$

## Considerations

In order to improve regulation accuracy, the following guidelines should be followed:

- Discrepancy between the model and the system will directly affect regulation accuracy. System characterization is strongly recommended during the design phase, specifically factorized bus  $(R_F)$  and output line  $(R_O)$  resistances.

- Statistical distribution of components values plays also a key role on accuracy distribution.

To this end, 'Monte Carlo' (or similar) analysis and optimization is strongly encouraged.

It should include all the components directly affecting regulation, i.e. setting resistors, model resistors and component characteristics. Any extra component designed in the system,

i.e. filter inductors, connectors, etc., should also be included if affected by variability.

- While the impact of  $R_S$  and  $R_F$  on VC voltage may be neglected in a few cases, it normally affects accuracy distribution. In order to evaluate it, both resistors should be included in the analysis.

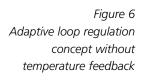

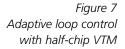

# Adaptive Loop with Half-Chip VTMs

The major difference between full- and half-chip VTMs is the absence of temperature feedback. While the full-chip VTMs implement a PTC resistor, the half-chip modules use a simple precision resistor, as shown in Figure 6.

The absence of temperature feedback slightly degrades the regulation accuracy; however, the half-chip units have tighter parameter distributions, which partially compensate for the reduced model accuracy. The control configuration in this case is shown in Figure 7.

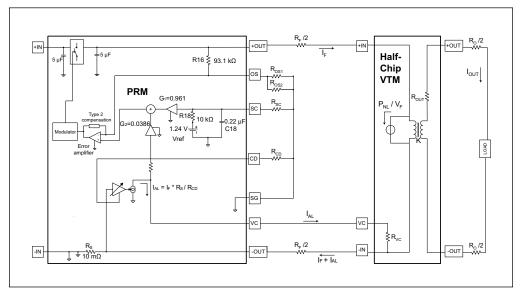

The voltage drop model also differs with the one for the full-chip version (Figure 3), resulting in the simpler one shown in Figure 8.

Figure 8 Voltage drop model in systems with half-chip VTMs

Having explained the differences, it is now possible to revise the design procedure in this specific case. Table 3 shows the necessary inputs.

Table 3 Adaptive loop calculation procedure inputs for half-chip VTMs

| Half-Chip VTM Characteristics                                    | Power System Characteristics                                                              |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| • R <sub>OUT_25</sub> : 25°C output resistance                   | • V <sub>F_NOM</sub> : nominal factorized bus voltage                                     |

| <ul> <li>R<sub>OUT 100</sub>: 100°C output resistance</li> </ul> | at no load                                                                                |

| • K: transformer ratio                                           | <ul> <li>I<sub>OUT</sub>: maximum system (VTM) output<br/>current</li> </ul>              |

| • R <sub>VC</sub> : VTM VC pin internal resistance               | • R <sub>F</sub> : factorized bus (PRM to VTM) total                                      |

| <ul> <li>P<sub>NL</sub>: no load power dissipation at</li> </ul> | resistance                                                                                |

| nominal input voltage                                            | <ul> <li>R<sub>O</sub>: output bus (VTM to point of load)<br/>total resistance</li> </ul> |

Table 4 summarizes the data for the half-chip VTMs.

Table 4 Half-chip VTM data required (typical)

|                 | Output Resistance   |                      |           | ID Resistor         |           |

|-----------------|---------------------|----------------------|-----------|---------------------|-----------|

| VTM Part Number | R <sub>OUT_25</sub> | R <sub>OUT_100</sub> | Tolerance | R <sub>vc</sub>     | Tolerance |

|                 | [mΩ]                | [mΩ]                 | [%]       | <b>[</b> Ω <b>]</b> | [%]       |

| VIV0102THJ      | 2.72                | 3.22                 | 8         | 1430                |           |

| VIV0103THJ      | 3.03                | 3.78                 | 11        | 9310                |           |

| VIV0104THJ      | 6.86                | 8.07                 | 8         | 8870                | 1.0       |

| VIV0105THJ      | 13.80               | 16.24                | 7         | 4640                |           |

| VIV0101THJ      | 44.32               | 57.65                | 6         | 2050                |           |

For sake of clarity, only the steps that differ from the procedure already explained for the full-chip VTMs are reported.

Step(s):

A., B., C.: unchanged

D.Calculate the total temperature coefficient of the power circuit at the estimated VTM working temperature.

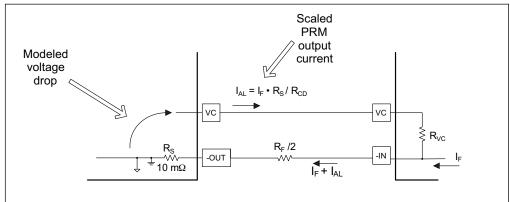

The VTM R<sub>OUT</sub> resistance is temperature dependent, as shown in Figure 9.

Figure 9 Half-chip VTM R<sub>OUT</sub> vs. module internal temperature

In order for the model to match the system voltage drop better, the VTM operating temperature should be estimated. In cases where temperature is unknown, a conservative approach would be to assume the module will operate at half of its temperature range, for example 75°C:

Equation 14

$$\Delta V_{F_{-}75} = \Delta V_{F_{-}25} + \frac{\Delta V_{F_{-}100} - \Delta V_{F_{-}25}}{75} \cdot 50$$

Linear interpolation used in [14] is acceptable in this case, as  $R_{\text{OUT}}$  temperature dependency is linear.

E. Calculate the maximum VC pin voltage for the given system.

$$V_{C_{-}MAX} = I_{AL} \cdot R_{VC} + (I_F + I_{AL}) \cdot \left(\frac{R_F}{2} + R_S\right) =$$

$$= R_S \frac{I_F}{R_{CD_{-}MIN}} \cdot R_{VC} + (I_F + R_S \frac{I_F}{R_{CD_{-}MIN}}) \cdot \left(\frac{R_F}{2} + R_S\right)$$

Equation 15

F., G.: unchanged

Rev. 1.3

H. Calculate the  $R_{\text{CD}}$  resistor that allows AL to compensate for the drops.

First, substitute the VC line voltage at full I<sub>F</sub> current (ambient temperature):

Equation 16

$$V_C = \frac{R_S \cdot I_F}{R_{CD}} \cdot R_{VC} + \left(\frac{R_S \cdot I_F}{R_{CD}} + I_F\right) \cdot \left(\frac{R_F}{2} + R_S\right)$$

into the expression for the related factorized bus increase:

$$\Delta V_{F_{-75}} = G_2 \cdot V_C \frac{R_{16} + R_{OS}}{R_{OS}} =$$

=  $G_2 \cdot \frac{R_S \cdot I_F}{R_{CD}} \cdot R_{VC} + \left(\frac{R_S \cdot I_F}{R_{CD}} + I_F\right) \cdot \left(\frac{R_F}{2} + R_S\right) \frac{R_{16} + R_{OS}}{R_{OS}}$

Then solve for  $R_{\mbox{\scriptsize CD}}$ :

Equation 17

$$R_{CD} = \frac{G_2 \frac{R_{16} + R_{OS}}{R_{OS}} R_S I_F \left( R_{VC} + \frac{R_F}{2} + R_S \right)}{\Delta V_{F_2 75} - G_2 \frac{R_{16} + R_{OS}}{R_{OS}} \left( \frac{R_F}{2} + R_S \right) I_F}$$

# Design Example with V•I Chip Customer Boards

System requirements:

Input: 36-75 V Output: 5 V, 36 A, 180 W

V•I Chip selection:

PRM: P048F048T24AL (due to the wide range input voltage and the power level).

VTM: V048F060T040 (due to output voltage and current requirements).

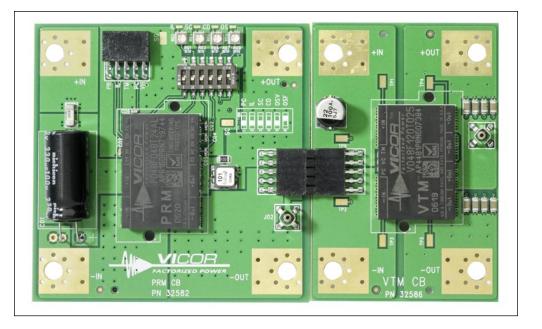

Corresponding customer boards are P048F048T24AL-CB and V048F060T040-CB respectively. They come with a connector which routes factorized bus and VC line, as explained in the User Guide UG:003. Figure 10 shows the two selected boards once connected.

Figure 10 PRM and VTM customer boards

First, collect the characteristics from the VTM's data sheet and from Table 2:

- R<sub>OUT 25</sub>: 5.76 mΩ

- R<sub>OUT\_100</sub>: 6.73 mΩ

- K: 1/8

- R<sub>PTC\_25</sub>: 1000 Ω

- $R_{PTC_{100}}$ : 1000·(1+0.0039·75) = 1293  $\Omega$

- P<sub>NL</sub>: 2.7 W

800-735-6200

Rev. 1.3

Second, calculate or measure the power system characteristics:

- V<sub>F\_NOM</sub>: V<sub>OUT</sub>/K = 40 V

- I<sub>OUT</sub>: 36 A

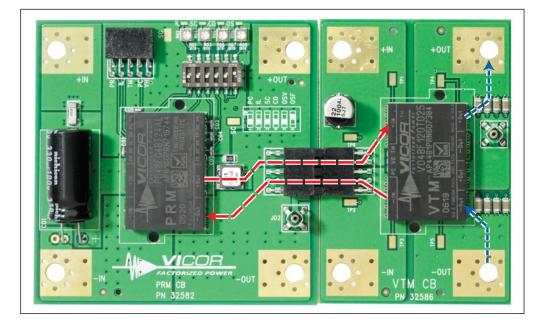

- R<sub>F</sub> and R<sub>O</sub>: these values are strictly related to the board traces or cables used to route power. A convenient way to obtain these values is to identify the current paths of interest, as shown in Figure 11.

Figure 11 Factorized bus current path (long-dash red) and output current path (short-dash blue)

Then, a simple DC impedance measurement from terminal to terminal will provide  $R_F$  and  $R_O$  values. In this particular case:

- $\succ$  R<sub>F</sub>= 10 m $\Omega$

- $\succ$  R<sub>0</sub>= 80 u $\Omega$

It is now possible to apply the proposed procedure.

A.Calculate the maximum voltage drop (at 25°C and 100°C) due to VTM output resistance,  $R_{\text{OUT}}.$

$$\Delta V_{ROUT 25} = R_{OUT 25} \cdot I_{OUT} = 0.00576 \cdot 36 = 0.207 V$$

$$\Delta V_{_{ROUT\_100}} = R_{_{OUT\_100}} \cdot I_{_{OUT}} = 0.00673 \cdot 36 = 0.242 V$$

B. Calculate the maximum current flowing on the factorized bus.

$$I_F = K \cdot I_{OUT} + \frac{P_{NL}}{V_{F_{-}NOM}} = \frac{1}{8} \cdot 36 + \frac{2.7}{40} = 4.568 A$$

Rev. 1.3

n 800-735-6200

735-6200

C.Calculate the total PRM output voltage increase that will compensate all the drops (factorized bus resistance, VTM output resistance and output bus resistance).

$$\Delta V_{F_{-25}} = \frac{\Delta V_{ROUT_{-25}} + R_0 I_{OUT}}{K} + (R_F + R_S) \cdot I_F = \frac{0.207 + 80 \,\mu \cdot 36}{1/8} + (10 \,m + 10 \,m) \cdot 4.568 = 1.77 \,V$$

$$\Delta V_{F_{-100}} = \frac{\Delta V_{ROUT_{-100}} + R_{O}I_{OUT}}{K} + (R_{F} + R_{S}) \cdot I_{F} = \frac{0.242 + 80\,\mu \cdot 36}{1/8} + (10\,m + 10\,m) \cdot 4.568 = 2.05\,V_{-100} + 10\,m + 10$$

D.Calculate the total temperature coefficient of the power circuit and the  $R_{VC}$  resistor needed to match it.

$$\Delta R_{TOT} = \frac{\Delta V_{F_{-100}}}{\Delta V_{F_{-25}}} = \frac{2.05}{1.77} = 1.158 \qquad \Longrightarrow$$

$$R_{VC} = (1 - \Delta R_{TOT}) \frac{R_{PTC_{25}} \cdot R_{PTC_{100}}}{\Delta R_{TOT} \cdot R_{PTC_{25}} - R_{PTC_{100}}} = (1 - 1.158) \frac{1000 \cdot 1293}{1.158 \cdot 1000 - 1293} = 1513 \ \Omega$$

The R<sub>VC</sub> value is greater than 200  $\Omega$ , therefore valid. The nearest available 1% resistor value chosen for R<sub>VC</sub> is 1500  $\Omega$ .

E. Calculate the maximum VC pin voltage for the given system at 25°C. From the PRM-AL data sheet,  $R_{CD\_MIN}$  = 20  $\Omega$ :

$$V_{C\_MAX\_25} = R_S \frac{I_F}{R_{CD\_MIN}} \cdot \frac{R_{PTC\_25} \cdot R_{VC}}{R_{PTC\_25} + R_{VC}} + (I_F + R_S \frac{I_F}{R_{CD\_MIN}}) \cdot \left(\frac{R_F}{2} + R_S\right) =$$

= 10 m  $\frac{4.568}{20} \cdot \frac{1000 \cdot 1500}{1000 + 1500} + (4.568 + 10 m \frac{4.568}{20}) \cdot \left(\frac{10 m}{2} + 10 m\right) = 1.44 V$

F. Calculate the needed (if any) V<sub>SC</sub> trim that allows enough AL dynamic range under the worst case: V<sub>C\_MAX\_25</sub> and  $\Delta$ V<sub>F\_100</sub>.

$$V_{SC} \le \frac{G_2 \cdot V_{C_{-M4X_{-}25}}}{G_1 \frac{\Delta V_{F_{-}100}}{V_{F_{-}NOM}}} = \frac{0.0386 \cdot 1.44}{0.961 \frac{2.05}{40}} = 1.12 V$$

As  $V_{SC} \leq V_{ref} = 1.24$  V,  $R_{SC}$  must be installed:

$$R_{SC} = R_{18} \frac{V_{SC}}{V_{ref} - V_{SC}} = 10 k \frac{1.12}{1.24 - 1.12} = 93.3 k\Omega$$

Rev. 1.3

5-6200

01/2011

$R_{SC}$  is greater than 2550  $\Omega$ , therefore acceptable. The closest 1% tolerance value is chosen,  $R_{SC}$  = 93.1 k $\Omega$ , which provides for an obtained  $V_{SC}$  = 1.12 V

G.Calculate the voltage feedback divider resistor needed to set the nominal output voltage.

$$R_{OS} = G_1 \cdot R_{16} \frac{V_{SC}}{V_{F_NOM} - G_1 \cdot V_{SC}} = 0.961 \cdot 93.1 k \frac{1.12}{40 - 0.961 \cdot 1.12} = 2574 \,\Omega$$

The closest standard value would be 2550  $\Omega$ , which is almost 1% off the target. In order to gain accuracy, the highest standard value is chosen, 2610  $\Omega$ , and a parallel resistor is used in order to closely match the required value:

$R_{OS1}$  = 2610  $\Omega\,$  and  $\,R_{OS2}$  = 187  $k\Omega\,$

H.Calculate  $R_{\text{CD}}$  resistor that allows AL to compensate for the drops.

$$R_{CD} = \frac{G_2 \frac{R_{16} + R_{OS}}{R_{OS}} R_S I_F \left( \frac{R_{PTC_25} \cdot R_{VC}}{R_{PTC_25} + R_{VC}} + \frac{R_F}{2} + R_S \right)}{\Delta V_{F_25} - G_2 \frac{R_{16} + R_{OS}}{R_{OS}} \left( \frac{R_F}{2} + R_S \right) I_F} = -\frac{1}{2} \frac{R_{CD}}{R_{CD}} \frac{R_{CD}}{R_{CD}} \left( \frac{R_{CD}}{R_{CD}} + \frac{R_{CD}}{R_{CD}} + \frac{R_{CD}}{R_{CD}} \right)}{\frac{R_{CD}}{R_{CD}} \frac{R_{CD}}{R_{CD}} \left( \frac{R_{CD}}{R_{CD}} + \frac{R_{CD}}{R_{CD}} + \frac{R_{CD}}{R_{CD}} \right)} = -\frac{1}{2} \frac{R_{CD}}{R_{CD}} \frac{R_{CD}}{R_{CD}} \frac{R_{CD}}{R_{CD}} \frac{R_{CD}}{R_{CD}} + \frac{R_{CD}}{R_{CD}} \frac{R_{CD}}{R_{CD}} + \frac{R_{CD}}{R_{CD}} \frac{R_{C$$

$$=\frac{0.0386\frac{93.1\,k+2574}{2574}10\,m\cdot4.568\left(\frac{1\,k\cdot1.5\,k}{1\,k+1.5\,k}+\frac{10\,m}{2}+10\,m\right)}{1.77-0.0386\frac{93.1\,k+2574}{2574}\left(\frac{10\,m}{2}+10\,m\right)\cdot4.568}=23.5\,\Omega$$

The nearest standard value is chosen,  $R_{CD}$  = 23.7  $\Omega$ .

The design is now complete, the calculated resistors:  $R_{SC} = 93.1 \text{ k}\Omega$ ,  $R_{OS1} = 2610 \Omega$ ,  $R_{OS2} = 187 \text{ k}\Omega$ ,  $R_{VC} = 1500 \Omega$  and  $R_{CD} = 23.7 \Omega$ can be implemented in the two customer boards and regulation accuracy verified.

## Conclusion

This procedure highlights the adaptive loop regulation concept and the design procedure to achieve good voltage regulation for a simple PRM/VTM combination.

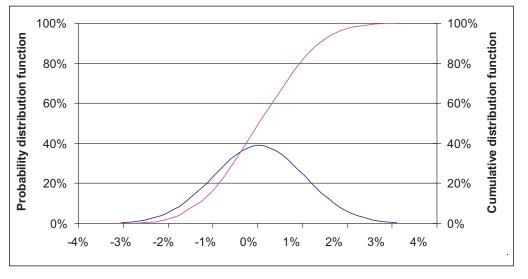

Monte Carlo analysis shows that 1% regulation accuracy over line, load and temperature can be statistically achieved 82% (or greater) of the time. Figure 12 shows accuracy distribution for the design example previously illustrated.

Figure 12 Accuracy distribution over line, load and temperature for the design example

The same design concepts are directly applicable to arrays of V-I Chips if proper modeling applied. It is recommended to contact V-I Chip Application Engineering for any array involving 2 or more PRMs and 3 or more VTMs. The automated spreadsheet version of the procedure is available at <a href="http://cdn.vicorpower.com/documents/calculators/dcaldesign.xls">http://cdn.vicorpower.com/documents/calculators/dcaldesign.xls</a>.

Appendix A – Changes applicable to MIL-COTS versions of VI Chips.

MIL-COTS VTMs: parameters and modeling of MIL-COTS VTMs are identical to the commercial counterparts with the same K factor. The AL design procedure can be applied directly.

MIL-COTS PRM: parameters and modeling of MP028F036M12AL are identical to the commercial parts as with the only exception of R16 which changes to  $69.8k\Omega$ , as shown in Figure XX.

## Appendix A

Changes applicable to MIL-COTS versions of VI Chips.

MIL-COTS VTMs: parameters and modeling of MIL-COTS VTMs are identical to the commercial counterparts with the same K factor. The AL design procedure can be applied directly.

MIL-COTS PRM: parameters and modeling of MP028F036M12AL are identical to the commercial parts as with the only exception of R16 which changes to  $69.8k\Omega$ , as shown in the figure below.

The automated spreadsheet version of the procedure for MIL-COTS products is available at <a href="http://cdn.vicorpower.com/documents/calculators/mil\_al\_design\_procedure.xls">http://cdn.vicorpower.com/documents/calculators/mil\_al\_design\_procedure.xls</a>

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor components are not designed to be used in applications, such as life support systems, wherein a failure or malfunction could result in injury or death. All sales are subject to Vicor's Terms and Conditions of Sale, which are available upon request.

Specifications are subject to change without notice.