# HMC832LP6GE 寄存器编程的快速指导

#### 概述

HMC832LP6GE是Hittite Microwave公司继HMC830LP6GE之后推出的又一款 25MHz到 3GHz的频率合成芯片。该芯片拥有单电源供电、宽带、超低噪声、超低杂散的特性,自从发布以来受到了广大射频工程师的好评。但是很多用户也在不断抱怨"该器件的寄存器过多,《操作指南》过长,以至于编程无从下手"。本文旨在帮助广大用户采用最简单的方法对HMC832LP6GE进行控制,实现常规功能。如需进一步了解这个器件的其它特殊的功能,欢迎联系Hittite Microwave公司寻求技术支持: *china@hittite.com*

#### HMC832LP6GE 与 HMC830LP6GE 的主要区别

鉴于很多 HMC832LP6GE 的客户之前使用过 HMC830LP6GE,而且两个器件的封装和管脚完全相同,因此本文首先需要介绍一下两个器件的最主要的区别。

- 1. HMC832LP6GE 不再需要两组电源: +5.5V 和+3.3V。所有电源管脚仅需要单电源供电: +3.3V,电路设计简化。即便如此,VCO(VCC1 和 VCC2)和 Charge Pump(VCCCP)也应该在电路设计和 PCB 布局上做好充分地隔离,这是锁相环芯片应用的通用法则。

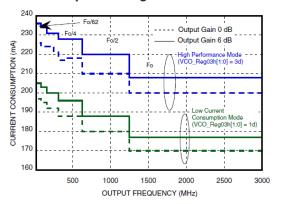

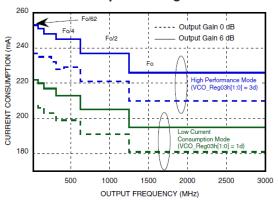

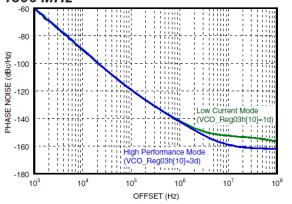

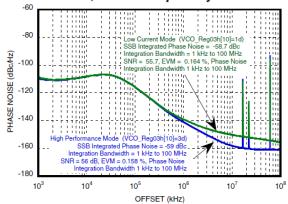

- 2. HMC832LP6GE 通过程序控制可以实现两种工作模式: 高性能模式、低电流模式。 如果关注降低功耗,推荐选用低电流模式。在图 1 中可以看到,在 1800MHz 单端输出,增益为 0dB 时,两种模式的总电流差异为 30mA; 如果是宽带设计,往往关注积分相噪(积分抖动),推荐选用高性能模式。在图 2 中比较了两种工作模式相位噪声的差异。在高性能模式下,VCO 远端(>1MHz)的相位噪声最大有接近 10dB 的改善,对应的闭环宽带积分相噪(1KHz 到 100MHz)也有一定的改善。

Figure 31. Current Consumption in Single-Ended Output Configuration [19]

Figure 32. Current Consumption in Differential Output Configuration [19]

图 1: 两种工作模式的电流比较

Figure 3. Open Loop VCO Phase Noise at 1800 MHz

Figure 8. Fractional Spurious Performance at 1804 MHz, Exact Frequency Mode ON [4]

图 2: 两种工作模式的相位噪声比较

- 3. HMC832LP6GE 的 RF 输出功率的调节范围提高到 12dB,并且步进减小为 1dB。有利于在工作温度或者其它外围应用条件改变时,精确控制作为本振信号的功率,或者作为时钟信号的幅度。

- 4. HMC832LP6GE 的 RF 输出端可通过软件配置为单端或者差分结构。在单端输出的

条件下,可以选择 RFP 或者 RFN 作为输出管脚。(HMC830LP6GE 只能支持单端 RFN 作为输出。)

5. HMC832LP6G 在 VCO 自动校准和频率锁定的过程中,VCO 的输出可以实现自动关闭(Automatic Mute)。这个功能的好处是,在频率切换的过程中没有 RF 信号输出,从而抑制不必要的干扰。

### 小数模式的控制方法介绍

| 应用条件: PFD = 61.44MHz, RF Out = 1055.2MHz |         |         |                        |  |  |  |

|------------------------------------------|---------|---------|------------------------|--|--|--|

| 编程顺序                                     | 寄存器编号   | 寄存器值    | 说明                     |  |  |  |

| 0                                        | REG 00h | 94075h  | 只读,用于检测SPI通信是否正常。      |  |  |  |

| 1                                        | REG 01h | 2h      | CEN由SPI程序控制,并且已经打开。    |  |  |  |

| 2                                        | REG 02h | 1h      | R分频器值为1。               |  |  |  |

| 3                                        | REG 05h | 110h    | VCO输出分频比为2。            |  |  |  |

| 4                                        | REG 05h | 4D98h   | VCO工作在高性能模式,单端,RFP输出。  |  |  |  |

| 5                                        | REG 05h | 7D8B    | RF输出增益设定为最大值。          |  |  |  |

| 6                                        | REG 05h | 0h      | 必须,打开自动校准。             |  |  |  |

| 7                                        | REG 06h | 200B4Ah | PFD工作在小数模式。            |  |  |  |

| 8                                        | REG 07h | 8CD     | 锁定窗口宽度。                |  |  |  |

| 9                                        | REG 08h | C1BEFFh | 如果参考输入频率小于200MHz,可以不写。 |  |  |  |

| 10                                       | REG 09h | 1F7EFD  | CP电流与CP Offset。        |  |  |  |

| 11                                       | REG 0Ah | 2006h   | 推荐值。                   |  |  |  |

| 12                                       | REG 0Fh | 81h     | 锁定指示输出。                |  |  |  |

| 13                                       | REG 03h | 22h     | N分频器的整数部分。             |  |  |  |

| 14                                       | REG 04h | 595555  | N分频器的小数部分,必须放在最后。      |  |  |  |

表 1: HMC832LP6GE 小数模式控制方法举例

REG 00h = 94075 h, 这是芯片的 ID, 只读,不需要写入。通常用于检测 SPI 的通信是否正常,一般只是用于产品的最初调试或者故障检测中。

REG 01h = 2h,用于指定 CEN(Chip enable)只由 SPI 程序控制,并且已经处于

"打开"状态。CEN 功能也可以直接通过 HMC832LP6GE 的第 17 管脚(CEN)的高低电平实现,这时寄存器应该设置为: REG 01h [0] = 1。这两种 CEN 实现方法,在实际应用只能选择一种。另外要注意,这里的 CEN 只能对 VCO 子系统之外的部分有效,关闭之后大约节省 60mA 左右的电流,但是 VCO 依然处于工作状态。如果关掉 VCO 的输出,则需要通过 REG 05h 实现,请参考后面章节的介绍。对于大多数的应用只需要对 VCO 进行打开和关断控制,因此 CEN 功能可以始终设置在"打开"的状态。

REG 02h = 1h,用于设定 R 分频器为 1。HMC832LP6GE 最大鉴相频率为 100MHz,但是参考源 REF 的最高允许输入频率可达 350MHz。因此需要合理设置 R 值,避免鉴相频率超过 100MHz。提高鉴相频率,有利于降低锁相环路中的 N 值,从而降低带内相位噪声。选取鉴相频率的上限不能忽略 N 最小值的要求。例如,在小数模式下 N 的最小值为 20,如果使用 100MHz 鉴相频率,是无法得到 1800MHz 的 RF 信号,因为这时候对应的 N 值仅为 9。但是用 100MHz 鉴相频率却可以得到 1400MHz 的 RF 信号,这又是因为在HMC832LP6GE 内部 VCO 的频段为 1.5GHz 到 3.0GHz。对应 1400MHz 的 RF 信号,VCO 此时的工作频率为 2800MHz,N 值计算为 28。只要将 VCO 输出端的分频器设为 2 就可以得到 1400MHz 的 RF 信号。

HMC832LP6GE 内部包含了两个子系统: PLL 子系统和 VCO 子系统。其中 PLL 子系统可以通过外部 SPI 直接读写,但是 VCO 子系统必须要通过 PLL 子系统中的 REG 05h 进行控制,而且 VCO 子系统中的寄存器只能读,不能写。两个子系统在芯片内部通过 16 位的 VSPI 进行通讯。因此对应的 REG 05h 有严格的格式要求: 最右边 3 位[2:0]为器件的标志位,对于 HMC832LP6GE 来说设置为 000; 中间 4 位[6:3]为 VCO 子系统的地址位; 最高 9 位 [15:7]为 VCO 子系统的数据位。对 REG 05h 进行多次写入就可以控制 VCO 的多种功能。

如果 RF 输出频率低于 1.5GHz,必须在 VCO\_Reg 02h 中设置 VCO 输出端的分频器。最大分频比为 62,并且只能为偶数。另外,如果 RF 输出频率较低,VCO 应该选用更高的工作频率,对应的输出端分频比也会更高,这样有利于改善 RF 输出信号的相位噪声。例如:如果 RF 的输出频率为 500MHz, VCO 的工作频率可以是 2GHz 或者 3GHz,但推荐的设置

是 3GHz,对应的输出端分频比为 6,分频器可以对 3GHz 的 VCO 相位噪声改善大约 15dB。注意,整个"闭环"系统并不包含输出端的分频器。因此,应该按照 VCO 的实际输出频率计算整数 N(REG 03h)和小数 N(REG 04h)。

REG 05h = 110h, 该指令的含义如下:

REG 05h = 110h = 100010000

$\Rightarrow$  [2:0] = 000, HMC832LP6GE

$\Rightarrow$  [6:3] = 0010, VCO\_Reg02 h

⇒[15:7]=[000000010], 分频器为2(VC0实际工作频率为输出RF频率2)

REG 05h = 4D98h, 该指令的含义如下:

#### REG 05h = 4D98h = 10011011 0011 000

$\Rightarrow$  [2:0] = 000, HMC832LP6GE

$\Rightarrow$  [6:3] = 0011, VCO\_Reg03 h

$\Rightarrow$  [15:7] = [010011011],

⇒ VCO\_REG 03h[1:0]=11, VC0工作在高性能模式。如写01则为低电流模式

⇒VCO\_REG 03h[2]=0, VCO单端输出,RFN端关闭。

⇒VCO\_REGO3h[3]=1, VCO单端输出, RFP端打开。

⇒ VCO REG03h[4]=1, 保留默认值。

⇒ VCO\_REG03h[5]=0, VCO输出端回波损耗大约为-5dB,输出功率最大。 如写1,回波损耗大约为-10dB。

⇒ VCO\_REG03h[6]=1,保留默认值。

⇒  $VCO_REGO3h[8:7]=1$ ,VCO在自动校准和频率锁定的过程中关闭输出。

REG 05h = 7DB8, 该指令的含义如下:

REG 05h = 7DB8h = 0111 1 1011 0111 000

$\Rightarrow$  [2:0] = 000, HMC832LP6GE

$\Rightarrow$  [6:3] = 0111, VCO Reg07h

$\Rightarrow$  [15:7] = [000000010],

⇒ VCO\_REG 07h[3:0]=1011, VCO输出增益最大。如写0000则增益最低,以此类推

REG 05h = 0,用于打开 VCO 子系统中所有 VCO 的可用频段,VCO 进行自动校准必须要有这条指令。而且只要 REG 05h 做任何改动,这一条指令必须增加在所有 REG 05h 命令行之后。

REG 06h = 200B4Ah,用于设定鉴相器工作在小数模式。当 REG 06h [7]= 0,REG06h[11]=1 时,为小数模式;当 REG 06h [7]=1,REG06h[11]=0 时,为整数模式。有个重要的概念一定要分清楚:小数模式条件下的整数频点与整数模式完全不同。在小数模式时,鉴相器的 Delta-Sigma 依然保持在打开状态,与对应的整数模式频点相比,带内相位噪声会恶化 3dB。

REG 08h = C1BEFFh, 这是器件上电以后的缺省值。如果输入的参考信号频率小于 200MHz, 可以不用写这个寄存器。如果参考输入信号大于等于 200MHz, 需要把 REG 08h [21] 改为 1, 对应完整的 REG 08h = E1BEFFh。

REG Ah = 2046h,用于设定 VCO 自动校准的相关参数。这条指令不能缺少。这里有一个设置需要注意一下: REG A [14:13],用于设定 VCO 子系统自动校准和控制的时钟速率,最大为 50MHz。表 1 中,参考输入信号 61.44MHz 大于 50MHz,因此 REG A [14:13] = 01,对应的 61.44MHz 除以 4。

REG Fh = 81h,设定在锁定状态下 LD\_LDO 管脚输出逻辑高电平。LD\_SDO 是功能复用管脚,除了用于锁定指示以外,还可以用作"回读",可以实现多种功能。其它 GPO 功

能的实现方法请参阅 HMC832LP6G 的 datasheet 中 REG 0Fh 的设置说明。当 SPI 程序发出 回读指令时,并且 REG Fh [6]=0,LD\_SDO 管脚按照读指令输出回读数据。一旦回读结束以 后,LD\_SDO 会自动切换到锁定指示状态。如果在产品设计中 SPI 控制没有用到回读功能,LD SDO 管脚只能用于锁定指示,这时候 REG Fh [6] =1。

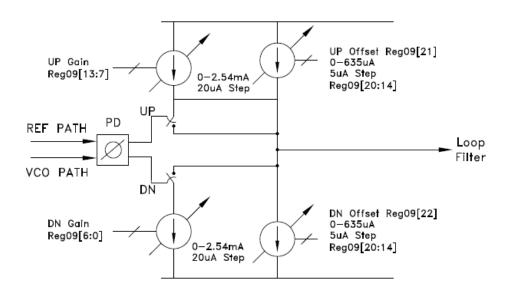

鉴相器有两个输入信号分别来自于参考 REF 和 VCO 的反馈端。在环路锁定的时候,两个输入信号的频率相等,相位相差一个固定值。鉴相器的功能是:将 VCO 的反馈信号和参考信号 REF 的相位进行比较,并且输 CP 电流。CP 电流的大小应该与鉴相器的两个输入信号的相位差成线性关系。图 3 介绍了 HMC832LP6GE 的 CP 和 CP Offset 控制方法,里面中包含了 4 个电流源。UP Gain 和 DN Gain 用于控制 CP 的增益, UP Offset 和 DN Offset 用于控制 CP Offset 的幅度。

图 3, HMC832LP6GE 鉴相器的 CP 和 CP Offset 控制说明

鉴相器在正常工作时,UP Gain 和 DN Gain 必须同时打开,并分别通过 REG 09h [13:7] 和 REG 09h [6:0]调整电流值。UP Gain 和 DN Gain 的电流值必须相等,推荐的范围是 2mA

到 2.5mA。如果的使用小于 1mA 的 CP 电流, 闭环相噪会恶化。

在整数模式下,鉴相器的两个输入信号同时到达输入端,不需要使用 CP Offset。关闭 UP Offset 和 DN Offset,并且将 CP Offset 的幅度设置为 0 的方法是:写入 REG 09h [22:21] = 00,REG 09h [20:14]=0。

在小数模式下,CP Offset 至关重要,直接关系到相位噪声和杂散的性能,甚至决定了能否可靠锁定。此时,鉴相器的两个输入信号不一定同步到达输入端,如果的两个输入信号的相位差很小,鉴相器的输入和输出之间的线性关系就不能满足。增加 UP Offset 可将VCO 反馈信号的相位提前,增加 DN Offset 则会将参考信号 REF 的相位提前。实际应用中两个方向的 CP Offset 只能选择一个,REG 09h [21] 用于的控制 UP Offset,REG 09h [22]用于控制 DN Offset。对于 HMC832LP6GE 在小数模式的应用,推荐使用 UP Offset,既写入REG 09h [22:21] = 01。CP Offset 的电流值由 REG 09h [20:14]控制,计算公式如下:

CP Offset = min

$$\left[ \left( 4.3 \times 10^{-9} \times F_{PD} \times I_{CP} \right), 0.25 \times I_{CP} \right]$$

F<sub>pn</sub>为鉴相频率,单位HZ,

la为CP电流值,分别由REG 09h[6:0]和REG 09h[13:7]控制。

(公式1)

举例说明 CP Offset 的计算方法以及完整的 REG 09h 指令:

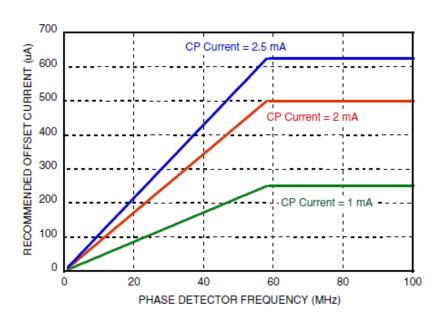

在图 4 中给出了常用 CP 电流和鉴相频率对应的 CP Offset 值,计算依据来自于公式 1。最后要注意的是 在实际应用中,CP Offset 不要超过的 CP 电流的 25%。

图 4, CP Offset 推荐值与鉴相频率和 CP 电流的关系

"锁定指示"对于锁相环芯片来说都是一个非常重要的功能。当 REG07h[3]=1 时,锁定指示功能打开。HMC832LP6GE 有两种锁定指示: 检测 LD\_SDO 管脚的高低电平、回读REG12h[1]的状态。这两种方法都使用逻辑"高"代表锁定。HMC832LP6GE 通过内部定时器产生连续的方波(又称为: 锁定窗)。在锁定窗打开期间,如果鉴相器的两个输入信号频率相等,相位相差为固定值,就被称为"一次锁定"。只要在连续数量的锁定窗内都能检测到锁定,这时锁相环路才是真正可靠的锁定。通过 REG 07h [2:0]可以定义连续锁定窗的数量,最小值为 5,最大值为 65535。在锁定检测过程中,只要出现在某一个锁定窗打开时鉴相器的两个输入信号不能满足"一次锁定"的条件,则锁定指示为"失锁",并且重新开始按照 REG 07h [2:0]定义的窗口数量检测锁定,直到整个环路真正锁定。锁定窗的宽度可用公式 2 来计算:

小数模式:

$$D \text{ Window (S)} = \frac{I_{CP \text{ Offset}}(A)}{F_{PD}(Hz) \times I_{CP}(A)} + 2.66 \times 10^{-9} \text{ (S)} + \frac{1}{F_{PD}(Hz)}$$

整数模式:

LD Window (S) =

$$\frac{1}{2 \times F_{PD}}$$

公式 2)

举例说明锁定窗宽度的计算方法:

$$\begin{split} F_{pD} &= 61.44 \, \text{MHz} = 61.44 \times 10^6 \, \text{Hz}, \\ I_{CP} &= 2.5 \, \text{mA} = 2.5 \times 10^{-3} \, \text{A}, \\ I_{CP \, Offset} &= 625 \, \text{uA} = 6.25 \times 10^{-6} \, \text{A}, \\ LD \, \text{Window} \, (S) &= \frac{\frac{I_{CP \, Offset}(A)}{F_{pD}(Hz) \times I_{CP}(A)} + 2.66 \times 10^{-9}(S) + \frac{1}{F_{pD}(Hz)}}{2} \\ &= \frac{6.25 \times 10^{-6}}{61.44 \times 10^6 \times 2.5 \times 10^{-3}} + 2.66 \times 10^{-9} + \frac{1}{61.44 \times 10^6} \\ &= 9.488 \, \text{nS} \end{split}$$

在表 2 中看到最接近的宽度是 9.2nS,因此 REG 07h [9:7] = 001,REG 07h [11:10]=10。 在表 1 中 REG 07h = 8CD h = 10 001 1 00 1 101,含义是:在连续 2048 个宽度为 9.2nS 的锁定窗打开时,如果能检测到锁定,则锁定指示输出为"锁定"。

Table 4. Typical Digital Lock Detect Window

| LD Timer Speed<br>Reg07[11:10]        | Digital Lock Detect Window Size<br>Nominal Value (ns) |      |      |     |     |     |     |     |  |

|---------------------------------------|-------------------------------------------------------|------|------|-----|-----|-----|-----|-----|--|

| Fastest 00                            | 6.5                                                   | 8    | 11   | 17  | 29  | 53  | 100 | 195 |  |

| 01                                    | 7                                                     | 8.9  | 12.8 | 21  | 36  | 68  | 130 | 255 |  |

| 10                                    | 7.1                                                   | 9.2  | 13.3 | 22  | 38  | 72  | 138 | 272 |  |

| Slowest 11                            | 7.6                                                   | 10.2 | 15.4 | 26  | 47  | 88  | 172 | 338 |  |

| LD Timer Divide Setting<br>Reg07[9:7] | 000                                                   | 001  | 010  | 011 | 100 | 101 | 110 | 111 |  |

表 2, 典型锁定窗宽度设置

REG 03h = 2Ah, 用于设定 N 分频器的整数部分。1055.2MHz 的 RF 信号对应的 VCO 频率是 2110.4MHz。因此 N 的计算方法为:

REG 04h = 用于设定 N 分频器的小数部分,一定要放在所有寄存器的最后,用触发 VCO 子系统的自动校准。计算方法是:

### 整数模式的控制方法介绍

| 应用条件: PFD=61.44MHz, RF Out=1044.48MHz |         |         |                        |  |  |  |

|---------------------------------------|---------|---------|------------------------|--|--|--|

| 编程顺序                                  | 寄存器编号   | 寄存器值    | 说明                     |  |  |  |

| 0                                     | REG 00h | 94075h  | 只读,用于检测SPI通信是否正常。      |  |  |  |

| 1                                     | REG 01h | 2h      | CEN由SPI程序控制,并且已经打开。    |  |  |  |

| 2                                     | REG 02h | 1h      | R分频器值为1。               |  |  |  |

| 3                                     | REG 05h | 110h    | VCO输出分频比为2。            |  |  |  |

| 4                                     | REG 05h | 4D98h   | VCO工作在高性能模式,单端,RFP输出。  |  |  |  |

| 5                                     | REG 05h | 7D8B    | RF输出增益设定为最大值。          |  |  |  |

| 6                                     | REG 05h | 0h      | 必须,打开自动校准。             |  |  |  |

| 7                                     | REG 06h | 2003CAh | PFD工作在整数模式。            |  |  |  |

| 8                                     | REG 07h | CDh     | 锁定窗口宽度。                |  |  |  |

| 9                                     | REG 08h | C1BEFFh | 如果参考输入频率小于200MHz,可以不写。 |  |  |  |

| 10                                    | REG 09h | 3FFFF   | CP电流。                  |  |  |  |

| 11                                    | REG 0Ah | 2006h   | 推荐值。                   |  |  |  |

| 12                                    | REG 0Fh | 81h     | 锁定指示输出。                |  |  |  |

| 13                                    | REG 03h | 22h     | N分频器的整数部分,必须放在最后。      |  |  |  |

表 3:HMC832LP6GE 整数模式控制方法举例

对比小数模式的控制方法,主要有以下几点重要改动:

- 1. 整数模式没有 N 分频器的小数部分,因此不需要控制 REG 04h。REG 03h 一定要放在所有寄存器的最后。

- 2. 整数模式没有 CP Offset,只需要设置 UP Gain 和 DN Gain。REG 09h = 3FFFF h 的含义是, CP 电流为 2.54mA,CP Offset 关闭。

- 3. 整数模式 Delta-Sigma 调制器关闭,REG 06h [7]=1,REG06h[11]=0。

- 4. 按照公式 2, 在鉴相频率为 61.44MHz 的条件下, 锁定窗的宽度计算为: 8.14nS。

#### 常用的初始化控制方法介绍

经常有用户希望在上电初始化的过程中关掉 HMC832LP6GE, 直到要求锁定输出在某一个特定频点时再唤醒。这里介绍两种"关断一唤醒"的控制方法:

1. 上电后不配置频率,直接关断整个器件,使整个器件进入到低功耗模式,直到唤醒指令到达,唤醒后按要求配置频率。

关断的过程:

REG 05h -- > 8h // 先关断 VCO

REG 01h -- > 0h //再关断 PFD + CLOCK

唤醒的过程:

REG 05h -- > F88h //再唤醒 VCO

注意关断和唤醒的顺序,这是因为 SPI 控制指令从外部先经过 PFD,然后才到达 VCO 子系统。如果先关断 PFD,则 VCO 不受控制。唤醒之后就可以按照前面介绍的方法对器件进其它控制。

2. 上电后先暂时配置某一个锁定频率,然后再关断输出。唤醒后直接恢复到关断前 的频率,或者继续设置新的锁定频率。

关断的过程:

REG 05h -- > 8h // 关断 VCO 输出

唤醒过程:

REG 05h -- > F88h //唤醒 VCO, 回复初始频率

设置新频率的过程:

REG 05h -- > 0h //必须,打开 VCO

REG 03h -- > 整数 N

REG 04h -- > 小数 N

注意这里的关断和唤醒只是针对 VCO 进行操作,因为绝大多数的应用只关心 VCO 的输出是否会干扰到整个通信链路的其他部分。关掉 VCO,大约降低功耗 125mA 左右。在这种应用场景中,由于一开始 HMC832LP6GE 已经锁定在某一个频点,因此唤醒之后只需要更改 REG 03h 和 REG 04h,其它寄存器只要不掉电,会一直保持"记忆"状态。

### Soft Reset 功能介绍

很多用户喜欢在 HMC832LP6GE 程序控制的最开始通过 REG Oh [5]进行 Reset。实际上没有必要增加这条指令,因为整个 HMC832LP6GE 在上电后大约 250uS,所有的寄存器自动就被 Reset 到缺省值。除非是上电速度非常缓慢,以至于超过 250uS,那么某些寄存器有可能会进入到未知的状态,这时候应该在所有 SPI 指令之前增加一个 REG Oh [5] = Oh。另外还要注意,VCO 子系统的寄存器不受 REG Oh 控制,重置只能通过重新上下电实现。

## 著作说明

作者: 高峻 Hittite Microwave Corp. Sr. FAE

联系方式: egao@hittite.com

本文初次发布日期: 2013年3月6日

第一次修订: 2013年3月7日

感谢选用 Hittite Microwave 公司器件!