# **HD Starlight Sensor**

#### FEATURES

- Best-in-class low-light performance

- True single exposure wide dynamic range operation (25000:1) to avoid motion artifacts

- Type 1/1.2-inch CMOS sensor

- Support both Rolling Shutter mode and Global Shutter mode

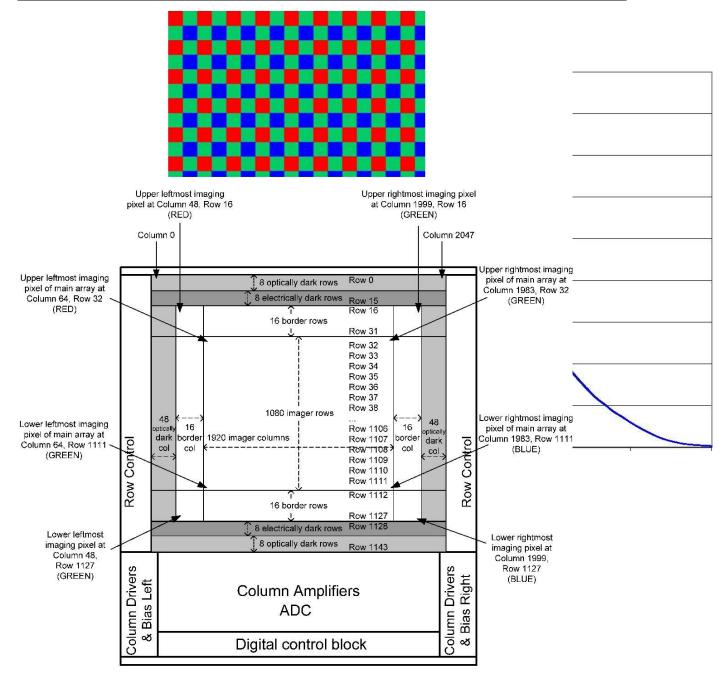

- High resolution imaging array: 1920(H) x 1080(V)

- Up to 100 fps @1080P in Rolling Shutter mode and 50 fps in Global Shutter mode

- Low noise: 1.2 e- RMS @ 30 fps in Rolling Shutter mode, 6.5 e- RMS @ 30 fps in Global Shutter mode

- 6.5µm by 6.5µm 5T active pixels

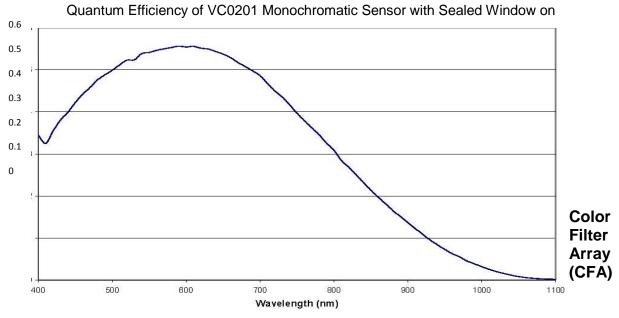

- Peak quantum efficiency > 50% at 600nm

- Protection against black-sun artifacts

- Low power consumption ( <0.4 W @ 30 fps)

#### APPLICATIONS

Video surveillance that demands low light performance as well as motion artifacts free high dynamic range imaging

#### DESCRIPTION

Vimicro's VC0201 is a high resolution, low-noise CMOS image sensor intended for video surveillance requiring high frame rate operation as well as high dynamic range capability at very low light levels. The device features an array of 5T pixels on a 6.5 µm pitch with an active imaging area of 1920(H) x 1080(V) pixels with support for both Rolling Shutter and Global Shutter readout modes. The sensor supports user-programmable row and column start/stop control in region of interest (ROI) readout mode. The sensor supports full frame readout up to 100 fps in Rolling Shutter mode and 50 fps in Global Shutter mode.

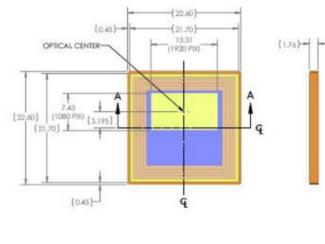

| Parameter                                         | Typical value                                                                                |

|---------------------------------------------------|----------------------------------------------------------------------------------------------|

| Active array size                                 | 2048 (H) x 1144 (V)                                                                          |

| Pixel size                                        | 6.5 µm x 6.5 µm                                                                              |

| Dimensions of active area                         | 13311.6 microns (H) x 7435.6 microns (V)                                                     |

| Dimensions of die                                 | 15675 microns (H) x 14829.8 microns (V)                                                      |

| Distance from die center to center of active area | 3187.68 microns                                                                              |

| Shutter type                                      | Rolling Shutter, Global Shutter (snapshot). ROI readout capabilities for both shutter types. |

| Maximum frame rate                                | 100 fps (Rolling Shutter) (@ 283MHz clock rate) 50 fps (Global Shutter)                      |

| Number of readout ports                           | 1                                                                                            |

| Maximum line rate                                 | 114kHz (8.7 μs/line)                                                                         |

| Maximum pixel rate                                | 234 MHz (3.5ns/pixel, and 2048 pixels/line, + ADC dead time)                                 |

| ADC resolution                                    | 2 x 11-bit                                                                                   |

| Column level amplifier gain                       | 1x or 2x (low gain output) 10x or 30x (high gain output)                                     |

| Power consumption                                 | 0.8W dual channel @100fps, 0.3W in Low-Gain only @50fps                                      |

| I/O interface                                     | 1.8V LVCMOS and 1.8V HSTL                                                                    |

#### General

### **Electrical-optical Specifications**

| Parameter                   | Specification                                                                                | Notes                                                                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Intra-frame dynamic range   | 30000:1.2 => 25000:1                                                                         |                                                                                                                                              |

| PRNU                        | < 3% RMS                                                                                     | at 75% of max output                                                                                                                         |

| Dark current                | < 35 e-/pixel/sec                                                                            | at 20°C                                                                                                                                      |

| Dark current non-uniformity | < 65 e-/pixel/sec RMS                                                                        | at 20°C                                                                                                                                      |

| Fixed pattern noise (FPN)   | < 2% RMS uncorrected                                                                         | of the max output                                                                                                                            |

| Conversion gain (DN/e-)     | High gain output - 1.7 at 30x -<br>0.55 at 10x Low gain output -<br>0.12 at 2x - 0.055 at 1x | w/1.4V ADC input range<br>(ADC input range is user<br>programmable from 0.8V to<br>2V) (30x: 1.3DN/e-<br>w/1.85V ADC default input<br>range) |

| Full well capacity (FWC)    | > 30,000 e-                                                                                  |                                                                                                                                              |

| Lag                         | < 0.1%                                                                                       | of maximum output                                                                                                                            |

| Non-linearity               | < 1%                                                                                         |                                                                                                                                              |

| Fill factor with microlens  | > 0.9                                                                                        |                                                                                                                                              |

| Microlens F-number          | 1.5                                                                                          |                                                                                                                                              |

| Peak QE                     | > 0.50                                                                                       | at 600nm                                                                                                                                     |

| MTF                         | > 0.4                                                                                        | at 600nm                                                                                                                                     |

| Temporal read noise         | < 1.2 e- RMS @ 50 fps Rolling<br>Shutter readout, @T=30°C                                    | Median value of read noise<br>distribution from high gain<br>output (30x gain)                                                               |

| Spectral sensitivity range  | 400 – 700nm                                                                                  | See QE plots for spectral<br>sensitivity in the Near IR<br>out to 1100 nm                                                                    |

### **Recommended Operating Condition**

| Parameter     | Definition                                                                           | Min   | Nom                             | Мах   | Units |

|---------------|--------------------------------------------------------------------------------------|-------|---------------------------------|-------|-------|

| AVDD          | Analog circuits power supply (avg<br>90 mA, Peak at 170mA on 5%<br>duty cycle)       | 3.135 | 3.3                             | 3.465 | V     |

| AVDD_PIX      | Pixel source follower power<br>supply (10 mA avg)                                    | 3.135 | 3.3                             | 3.465 | V     |

| AVDD_RST<br>1 | Pixel reset power supply1 (1mA)                                                      | 2.50  | 3.00<br>(RS) or<br>2.77<br>(GS) | 3.3   | V     |

| AVDD_RST<br>2 | Pixel reset power supply2 (1mA)                                                      | 2.50  | 3.0                             | 3.3   | V     |

| DVDD          | Digital circuits power supply (160mA)                                                | 1.71  | 1.8                             | 1.89  | V     |

| DVDD_IO       | I/O circuits power supply (65 mA) (with no terminations on outputs)                  | 1.71  | 1.8                             | 1.89  | V     |

| VTX1_POS      | TX1 Transfer gate positive power supply (80 mA/ 1µsec pulse in GS, <1mA in RS).      | 3.135 | 3.3                             | 3.465 | V     |

| VTX2_POS      | TX2 Transfer gate positive power<br>supply (80 mA/ 1µsec pulse in<br>GS, <1mA in RS) | 3.135 | 3.3                             | 3.465 | V     |

| VTX1_NEG      | TX1 Transfer gate negative power supply (80 mA/ 1µsec pulse in                       | -1.5  | -0.4                            | +0.3  | V     |

|            | GS, < 1mA in RS)                                                                      |      |                 |       |    |

|------------|---------------------------------------------------------------------------------------|------|-----------------|-------|----|

| VTX2_NEG   | TX2 Transfer gate negative power<br>supply (80 mA/ 1µsec pulse in<br>GS, < 1mA in RS) | -1.5 | -0.4 or<br>+0.8 | +0.85 | V  |

| Toperation | Sensor junction temperature                                                           | -40  | 30              | +55   | С° |

(.127)

0 (.127)

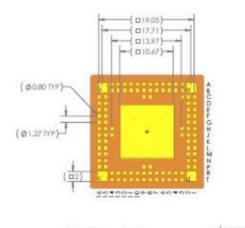

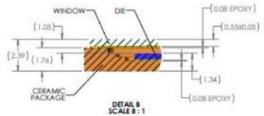

### Package

All the dimensions in the below drawing are in mm.

#### Package

B

1777

SECTION A-A SCALE 3:1

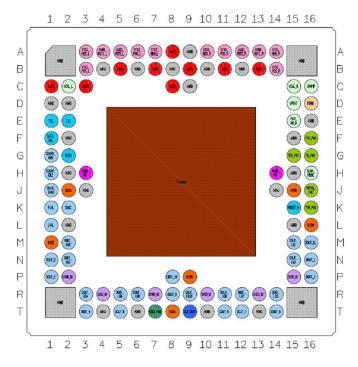

#### Pad Diagram

### Pad List

The VC0201 Standard package image sensor has 105 pads in a LGA (Land Grid Array) package. The list shown below provides a complete description of the pad names, their functions and electrical requirements. Note the suffix L is appended to pads on left side of the sensor, and the suffix R is appended to pads on right side of the sensor.

| Pad<br>number | Pad name    | Pad<br>type | Signa<br>I type | Power<br>voltage/current                                                                        | Pad description           |

|---------------|-------------|-------------|-----------------|-------------------------------------------------------------------------------------------------|---------------------------|

| A3            | VTX1_NEG_L  | Power       |                 | 0~-1.5v/80mA max,<br>Ripple < 100µV RMS                                                         | TX1 negative supply       |

| A4            | AVDD_RST1_L | Power       |                 | 2.7-3.0v/1 mA, Ripple<br>< 10 μV RMS                                                            | AVDD_RST1 reset<br>supply |

| A5            | AVDD_RST2_L | Power       |                 | 3.0v/1 mA, Ripple < 10<br>µV RMS                                                                | AVDD_RST2 reset<br>supply |

| A6            | VTX2_POS_L  | Power       |                 | 3.3v/80mA max, Ripple<br>< 1 mV RMS                                                             | TX2 positive supply       |

| A7            | VTX2_NEG_L  | Power       |                 | +0.8v to -1.5v/80mA<br>max, Ripple < 1 mV<br>RMS                                                | TX2 negative supply       |

| A8            | AVDD        | Power       |                 | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each line<br>time, Ripple < 1mV<br>RMS | AVDD analog supply        |

| A9            | AGND        | Ground      |                 |                                                                                                 | AGND common ground<br>0V  |

| A10           | VTX2_NEG_R  | Power       |                 | +0.8v to -1.5v/80mA<br>max, Ripple < 1 mV<br>RMS                                                | TX2 negative supply       |

| A11           | VTX2_POS_R  | Power       |                 | 3.3v/80mA max, Ripple<br>< 1 mV RMS                                                             | TX2 positive supply       |

| A12           | AVDD_RST2_R | Power       |                 | 3.0v/1 mA, Ripple < 10<br>µV RMS                                                                | AVDD_RST2 reset<br>supply |

| A13           | AVDD_RST1_R | Power       |                 | 2.7-3.0v/1 mA, Ripple<br>< 10 μV RMS                                                            | AVDD_RST1 reset<br>supply |

| A14           | VTX1_NEG_R  | Power       |                 | 0∼-1.5v/80mA max,<br>Ripple < 100µV RMS                                                         | TX1 negative supply       |

| B3            | VTX1_POS_L  | Power       |                 | 3.3v/80mA max, Ripple<br>< 1 mV RMS                                                             | TX1 positive supply       |

| B4            | AGND        | Ground      |                 |                                                                                                 | AGND common ground<br>0V  |

| B5            | AVDD        | Power       |                 | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each line<br>time, Ripple < 1mV<br>RMS | AVDD analog supply        |

| B6            | AGND        | Ground      |                 |                                                                                                 | AGND common ground<br>0V  |

| B7            | AVDD        | Power       |                 | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each line<br>time, Ripple < 1mV<br>RMS | AVDD analog supply        |

| B8            | AGND        | Ground      |                 |                                                                                                 | AGND common ground<br>0V  |

| Pad<br>number | Pad name   | Pad<br>type | Signal<br>type | Power<br>voltage/current                                                                        | Pad description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|------------|-------------|----------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В9            | AVDD       | Power       |                | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each<br>line time, Ripple <<br>1mV RMS | AVDD analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| B10           | AGND       | Ground      |                |                                                                                                 | AGND common<br>ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B11           | AVDD       | Power       |                | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each<br>line time, Ripple <<br>1mV RMS | AVDD analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| B12           | AGND       | Ground      |                |                                                                                                 | AGND common<br>ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B13           | AVDD       | Power       |                | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each<br>line time, Ripple <<br>1mV RMS | AVDD analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| B14           | VTX1_POS_R | Power       |                | 3.3v/80mA max,<br>Ripple < 1 mV RMS                                                             | TX1 positive supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C1            | AVDD       | Power       |                | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each<br>line time, Ripple <<br>1mV RMS | AVDD analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C2            | VCAL_L     | Input       | Analog         |                                                                                                 | Optional column<br>calibration reference<br>voltage. Normally not<br>used and so this pad is<br>left as no connection or<br>tied to ground. When it<br>is used, the user inputs<br>a fixed voltage<br>(2.5V-1.0V, 1mA),<br>when Register 2 bit 18<br>= 0 (not the default).<br>With this Register<br>setting, VCAL is<br>connected to the<br>column amplifier inputs<br>(instead of the pixel<br>floating diffusion<br>voltages being<br>connected to the<br>column amplifier<br>inputs). |

| C3            | AVDD       | Power       |                | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each<br>line time, Ripple <<br>1mV RMS | AVDD analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C8            | AVDD       | Power       |                | 3.3v/90mA average,<br>170mA peak on 5%<br>duty cycle for each                                   | AVDD analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## VC0201

|  | line time, Ripple < |  |

|--|---------------------|--|

|  | 1mV RMS             |  |

| Pad    | Pad name | Pad    | Signal | Power           | Pad description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|----------|--------|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| number |          | type   | type   | voltage/current | AGND common                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C9     | AGND     | Ground |        |                 | ground OV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C15    | VCAL_R   | Input  | Analog |                 | Optional column<br>calibration reference<br>voltage. Normally not<br>used and so this pad<br>is left as no<br>connection or tied to<br>ground. When it is<br>used, the user inputs<br>a fixed voltage<br>(2.5V-1.0V, 1mA),<br>when Register 2 bit 18<br>= 0 (not the default).<br>With this Register<br>setting, VCAL is<br>connected to the<br>column amplifier<br>inputs (instead of the<br>pixel floating diffusion<br>voltages being<br>connected to the<br>column amplifier<br>inputs). |

| C16    | VRAMP    | Input  | Analog |                 | Optional external<br>VRAMP voltage that<br>can be used in place<br>of the internally<br>provided VRAMP.<br>Normally this pad is<br>not used and can be<br>left as a no connection<br>or tied to ground. If it<br>is used, the user<br>inputs the ADC ramp<br>voltage (from 1.0V to<br>2.5V, 20mA) using<br>timing signals from<br>COUNT_EN[1:0].                                                                                                                                             |

| D1     | AGND     | Ground |        |                 | AGND common<br>ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D2     | AGND     | Ground |        |                 | AGND common<br>ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D15 | VPTAT | Output | Analog         | Temperature sensor<br>Output. This pad will<br>output a voltage of<br>slightly over 2 Volts at<br>room temperature that<br>will change linearly<br>with temperature with<br>a slope of 5 to 7 mV<br>per degree Celsius.<br>The exact calibration<br>of offset and slope for<br>VPTAT must be<br>performed by the user<br>with a reference<br>temperature sensor<br>(e.g. a thermocouple). |

|-----|-------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D16 | RTRIM | Output | Analog         | External current<br>reference resistor pad.<br>This pad must have a<br>$12.2 k\Omega$ resistor<br>attached to this pad at<br>one end and tied to<br>ground at the other<br>end. Providing this<br>pad with a path to<br>ground through a 12.2<br>$k\Omega$ resistor is<br>necessary for the<br>functioning of the<br>column amplifiers.                                                   |

| E1  | TX1   | Input  | 1.8v<br>Ivcmos | Global TX1 Charge<br>transfer control,<br>rise/fall time < 500ns,<br>Skew < 100ns, Ripple<br>< 100µV RMS                                                                                                                                                                                                                                                                                  |

| Pad<br>number | Pad name | Pad<br>type | Signal<br>type | Power<br>voltage/current | Pad description                                                                                                                                                                                |

|---------------|----------|-------------|----------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2            | TX2      | Input       | 1.8v<br>Ivcmos |                          | Global TX2 Charge<br>dump control, rise/fall<br>time < 500ns, Skew <<br>100ns, Ripple < 1mV<br>RMS                                                                                             |

| E15           | PWR_DN_B | Input       | 1.8v<br>Ivcmos |                          | Power Down Input<br>(active low). Setting<br>this pad to logic 0 has<br>the same effect as<br>setting Register 2 bit<br>25 to 1. It enables the<br>low power control<br>register, Register 12. |

| E16           | AGND     | Ground      |                |                          | AGND common<br>ground 0V                                                                                                                                                                       |

| F1DATA_SELInput1.8v<br>ivemosDATA_SEL = 0 selects<br>wavetable A for sensor<br>readout and wavetable<br>B for read/write<br>access. DATA_SEL<br>= 1 selects wavetable<br>A for<br>read/write access.<br>Typically, for Rolling<br>Shutter operation,<br>wavetable A is always<br>used for sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F1DATA_SELInput1.8v<br>lvcmosreadout and wavetable<br>B for read/write<br>access. DATA_SEL<br>= 1 selects wavetable<br>B for sensor readout<br>and wavetable A for<br>read/write access.<br>Typically, for Rolling<br>Shutter operation,<br>wavetable A is always<br>used for sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>B (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmos                                                                                                                                                                                                                                                                                                                      |

| F1DATA_SELInput1.8v<br>Ncmosaccess.DATA_SEL<br>= 1 selects wavetable<br>B for sensor readout<br>and wavetable A for<br>read/write access.<br>Typically, for Rolling<br>Shutter operation,<br>wavetable A is always<br>used fro sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>NcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                              |

| F1DATA_SELInput1.8v<br>lvcmos= 1 selects wavetable<br>B for sensor readout<br>and wavetable A for<br>read/write access.<br>Typically, for Rolling<br>Shutter operation,<br>wavetable A is always<br>used for sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL = 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL = 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less. |

| F1DATA_SELInput1.8v<br>lvcmosB for sensor readout<br>and wavetable A for<br>read/write access.<br>Typically, for Rolling<br>Shutter operation,<br>wavetable A is always<br>used fro sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                   |

| F1DATA_SELInput1.8v<br>lvcmosand wavetable A for<br>read/write access.<br>Typically, for Rolling<br>Shutter operation,<br>wavetable A is always<br>used fro sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                           |

| F1DATA_SELInput1.8v<br>lvcmosread/write access.<br>Typically, for Rolling<br>Shutter operation,<br>wavetable A is always<br>used fro sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                  |

| F1DATA_SELInput1.8v<br>lvcmosTypically, for Rolling<br>Shutter operation,<br>wavetable A is always<br>used fro sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                        |

| F1DATA_SELInput1.8v<br>lvcmosShutter operation,<br>wavetable A is always<br>used fro sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F1DATA_SELInput1.8v<br>lvcmoswavetable A is always<br>used fro sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| F1DATA_SELInputIvemosused fro sensor<br>readout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvemosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Feadout, so<br>DATA_SEL = 0 (fixed).<br>For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| For Global Shutter<br>operation, DATA_SEL<br>= 0 selects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| F16TCK_PADInput1.8v<br>lycmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.Spi clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| F16TCK_PADInput1.8v<br>lvcmos1.8v<br>lvcmosSelects wavetable<br>A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A (the GS Reset<br>frame) and DATA_SEL<br>= 1 selects wavetable<br>B (the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F2AGNDGroundAGND common<br>ground 0VF15AGNDGroundSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| F16TCK_PADInput1.8v<br>lvcmos1.8v<br>lvcmosSPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| F16TCK_PADGroundInput1.8v<br>lvcmosSel the GS Data frame)<br>so DATA_SEL is<br>constantly switching<br>between 0 and 1.F15AGNDGroundAGND common<br>ground 0VF16TCK_PADInput1.8v<br>SPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| F2 AGND Ground Ground AGND common ground 0V   F15 AGND Ground AGND common ground 0V   F16 TCK_PAD Input 1.8v lvcmos   Input 1.8v lvcmos SPI clock (clk) This clock must be 25 MHz or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| F2 AGND Ground Constantly switching<br>between 0 and 1.   F2 AGND Ground AGND common<br>ground 0V   F15 AGND Ground AGND common<br>ground 0V   F16 TCK_PAD Input 1.8v<br>lvcmos SPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| F2 AGND Ground AGND common ground 0V   F15 AGND Ground AGND common ground 0V   F16 TCK_PAD Input 1.8v lvcmos   F16 TCK_PAD Input 1.8v lvcmos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F2 AGND Ground AGND common ground 0V   F15 AGND Ground AGND common ground 0V   F16 TCK_PAD Input 1.8v lvcmos SPI clock (clk) This clock must be 25 MHz or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| F15 AGND Ground AGND common ground 0V   F16 TCK_PAD Input 1.8v lvcmos SPI clock (clk) This clock must be 25 MHz or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| F15 AGND Ground ground 0V   F16 TCK_PAD Input 1.8v<br>lvcmos SPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| F16 TCK_PAD Input 1.8v<br>Ivcmos SPI clock (clk) This<br>clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| F16 TCK_PAD Input 1.8v<br>Ivcmos clock must be 25 MHz<br>or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ' IVCMOS or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| external VRAMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| G1 COUNT_EN0 Output 1.8v hstl Output ignored unless the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| external VRAMP (pad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C16) is being used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (which it typically is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| not).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| External start/pause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| G2 READ Input 1.8v row counter and readout activities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| control Input from pad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPI serial data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| G15 TDO_PAD Output 1.8V fisti (so)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G16 TDI_PAD Input 1.8v SPI serial data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ivernos (si)<br>External count and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| external count and<br>external VRAMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Output, bit 1. Normally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| H1 COUNT_EN1 Output 1.8v hstl ignored unless the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| external VRAMP (pad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C16) is being used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (which it typically is not).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| H2 AGND Ground AGND common                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |