# **Datasheet**

# FS98025

8-bit MCU with 8k program EPROM, 256-byte RAM, 2 low noise OPAMP, 8-ch 14-bit ADC, 4 × 32 LCD driver and RTC

Fortune Semiconductor Corporation

富晶電子股份有限公司

28F., No.27, Sec. 2, Zhongzheng E. Rd., Danshui Town, Taipei County 251, Taiwan

Tel.: 886-2-28094742 Fax: 886-2-28094874 www.ic-fortune.com

This manual contains new product information. Fortune Semiconductor Corporation reserves the rights to modify the product specification without further notice. No liability is assumed by Fortune Semiconductor Corporation as a result of the use of this product. No rights under any patent accompany the sale of the product.

# **Contents**

| 1. | DEVI         | CE OVERVIEW                                                                         | 10 |

|----|--------------|-------------------------------------------------------------------------------------|----|

|    | 1.1          | High Performance RISC CPU                                                           | 10 |

|    | 1.2          | Peripheral Features                                                                 | 10 |

|    | 1.3          | Analog Features                                                                     | 10 |

|    | 1.4          | Special Microcontroller Features                                                    | 10 |

|    | 1.5          | CMOS Technology                                                                     | 10 |

|    | 1.6          | Applications                                                                        | 10 |

|    | 1.7          | Ordering Information                                                                | 11 |

|    | 1.8          | Pin Configuration                                                                   | 12 |

|    | 1.9          | Pin Description                                                                     |    |

|    | 1.10         | Functional Block Diagram                                                            |    |

|    | 1.11         | CPU Core                                                                            |    |

|    | 1.12         | Clocking Scheme/Instruction Cycle                                                   |    |

| 2. | ELEC         | TRICAL CHARACTERISTICS                                                              |    |

|    | 2.1          | Absolute Maximum Ratings                                                            | 19 |

|    | 2.2          | DC Characteristics (VDD=3V, T <sub>A</sub> =25℃, unless otherwise noted)            | 19 |

|    | 2.3          | ADC Characteristics (VDD=3V, T <sub>A</sub> =25°C, unless otherwise noted)          |    |

|    | 2.4          | OPAMP Characteristics (VDD=3V, T <sub>A</sub> =25℃, unless otherwise noted)         |    |

|    | 2.5 Te       | emperature Characteristics(VDD=3V)                                                  |    |

| 3. |              | DRY ORGANIZATION                                                                    |    |

|    | 3.1          | Program Memory Structure                                                            |    |

|    | 3.2          | Data Memory Structure                                                               |    |

|    | 3.3          | System Special Registers                                                            |    |

|    |              | 3.3.1 Special Register Contents after External Reset (Power On Reset) and WDT Reset |    |

|    |              | 3.3.2 IND and FSR Registers                                                         |    |

|    |              | 3.3.3 STATUS Register                                                               |    |

|    | 3.4          | Peripheral Special Registers                                                        |    |

| 4. | POWI         | ER SYSTEM                                                                           |    |

|    | 4.1          | Voltage Doubler                                                                     |    |

|    | 4.2          | Voltage Regulator                                                                   |    |

|    | 4.3          | Analog Bias Circuit                                                                 |    |

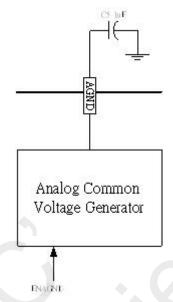

|    | 4.4          | Analog Common Voltage Generator                                                     |    |

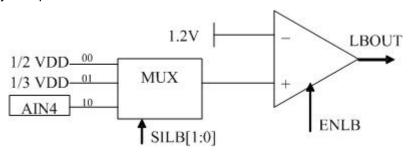

|    | 4.5          | Low Battery Comparator                                                              |    |

|    | <del>-</del> | · · · · · · · · · · · · · · · · · · ·                                               |    |

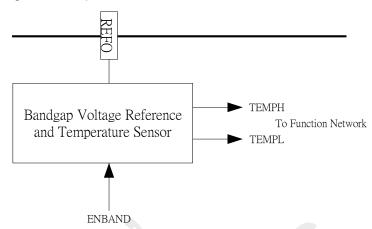

|     | 4.6   | Bandgap Voltage and Temperature Sensor                                        | 38  |

|-----|-------|-------------------------------------------------------------------------------|-----|

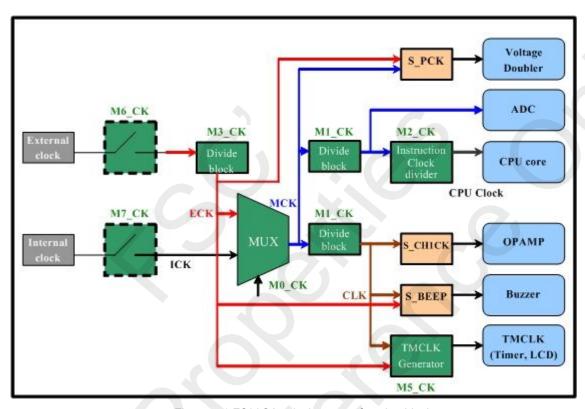

| 5.  | CLO   | CK SYSTEM                                                                     | 39  |

|     | 5.1   | Oscillator State                                                              | 40  |

|     | 5.2   | CPU Instruction Cycle                                                         | 41  |

|     | 5.3   | ADC Sample Frequency                                                          | 42  |

|     | 5.4   | Beeper Clock                                                                  | 42  |

|     | 5.5   | Voltage Doubler Operation Frequency                                           | 43  |

|     | 5.6   | Chopper Operation Amplifier Input Control Signal                              | 43  |

|     | 5.7   | TMCLK Timer and LCD Module Input Clock                                        | 44  |

| 6.  |       | R MODULE, WATCH DOG TIMER AND PROGRAMMABLE                                    | 45  |

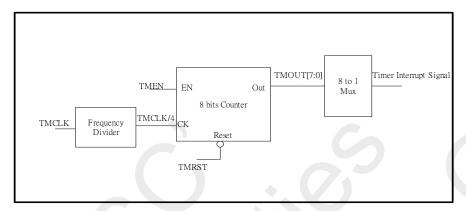

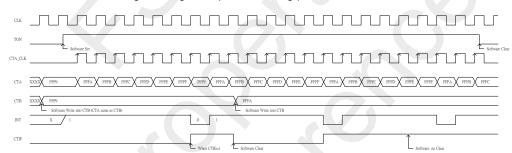

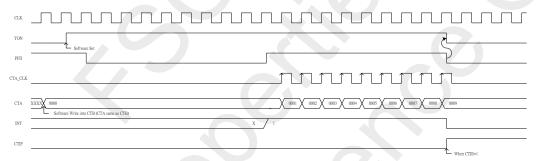

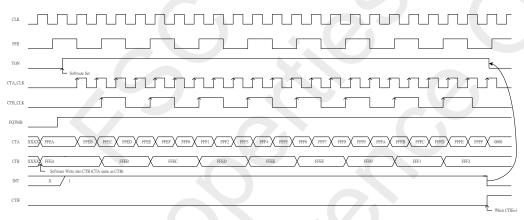

|     | 6.1   | Timer Module                                                                  | 50  |

|     |       | 6.1.1 Timer module interrupt                                                  |     |

|     |       | 6.1.2 Using Timer with External/Internal Clock                                |     |

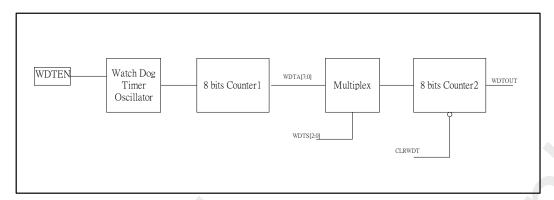

|     | 6.2   | Watch Dog Timer                                                               |     |

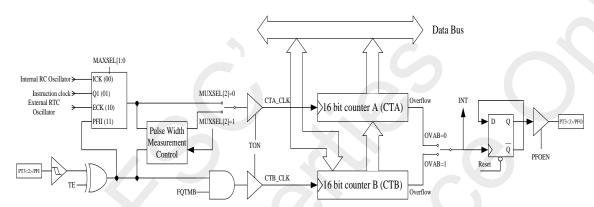

|     | 6.3   | Dual 16-bit Programmable Counter                                              |     |

| 7.  | I/O P | DRT                                                                           |     |

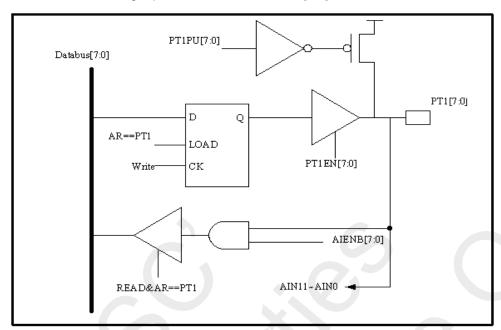

|     | 7.1   | Digital I/O Port with Analog Input Channel Shared: PT1[7:0]                   | 72  |

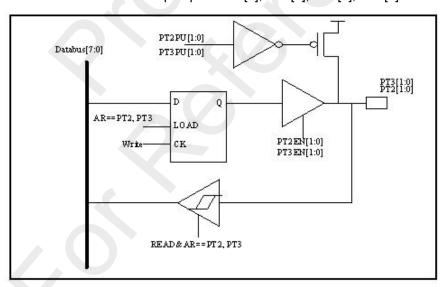

|     | 7.2   | Digital I/O Port and External Interrupt Input: PT2[0], PT2[1], PT3[0], PT3[1] |     |

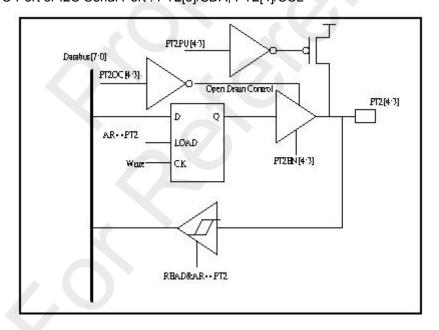

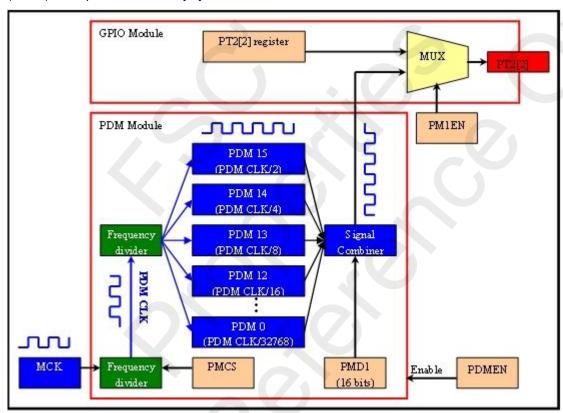

|     | 7.3   | Digital I/O Port or PDM Output : PT2[2] and PT2[5]                            | 76  |

|     | 7.4   | Digital I/O Port or I2C Serial Port : PT2[3]/SDA, PT2[4]/SCL                  |     |

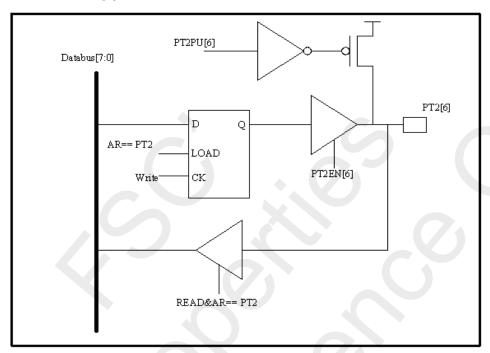

|     | 7.5   | Digital I/O Port : PT2[6]                                                     | 79  |

|     | 7.6   | Digital I/O Port or Buzzer Output : PT2[7]                                    | 81  |

| 8.  | PDM   | (PULSE DENSITY MODULATOR) MODULE                                              | 83  |

| 9.  | I2C M | ODULE (SLAVE MODE ONLY)                                                       | 90  |

| 10. | ANAL  | OG FUNCTION NETWORK                                                           | 96  |

|     | 10.1  | Analog to Digital Converter (ADC) :                                           | 105 |

|     | 10.2  | OPAMP : OP1 and OP2                                                           | 109 |

| 11. | ADC . | APPLICATION GUIDE                                                             | 112 |

|     | 11.1  | ADC Output Format                                                             | 112 |

|     | 11.2  | ADC Linear Range                                                              | 112 |

|     | 11.3  | ADC Output Rate and Settling Time                                             | 112 |

|     | 11.4  | ADC Input Offset                                                              | 112 |

|     | 11.5  | ADC Digital Output                                                            | 113 |

|     | 11.6  | ADC Resolution                                                                | 113 |

| 12. | LOW   | NOISE OPERATION AMPLIFIER GUIDE                                               | 114 |

|     | 12.1  | Single End Amplifier Application | 114 |

|-----|-------|----------------------------------|-----|

|     | 12.2  | Differential Amplifier           | 115 |

| 13. | LCD D | RIVER                            | 116 |

| 14. | HALT  | AND SLEEP MODES                  | 128 |

| 15. | INSTR | UCTION SET                       | 129 |

|     | 15.1  | Instruction Set Summary          | 129 |

|     | 15.2  | Instruction Description          | 131 |

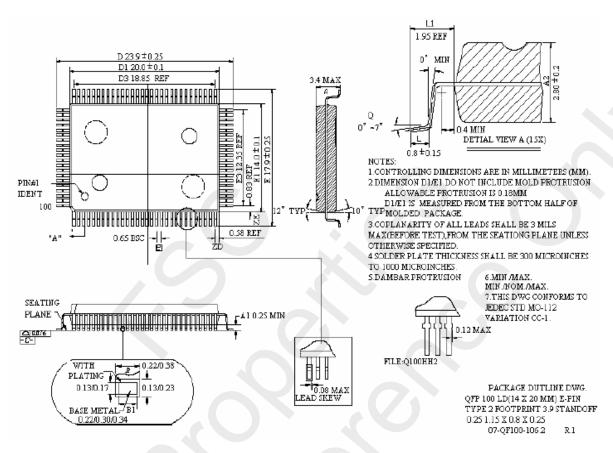

| 16. | PACK  | AGE INFORMATION                  | 142 |

|     | 16.1  | Package Outline                  | 142 |

| 17. | REVIS | ION HISTORY                      | 142 |

# Figure List

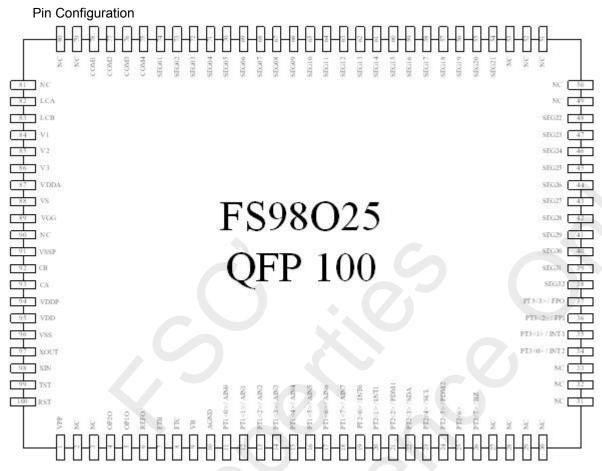

| Figure 1-1 FS98O25 pin configuration                             | 12     |

|------------------------------------------------------------------|--------|

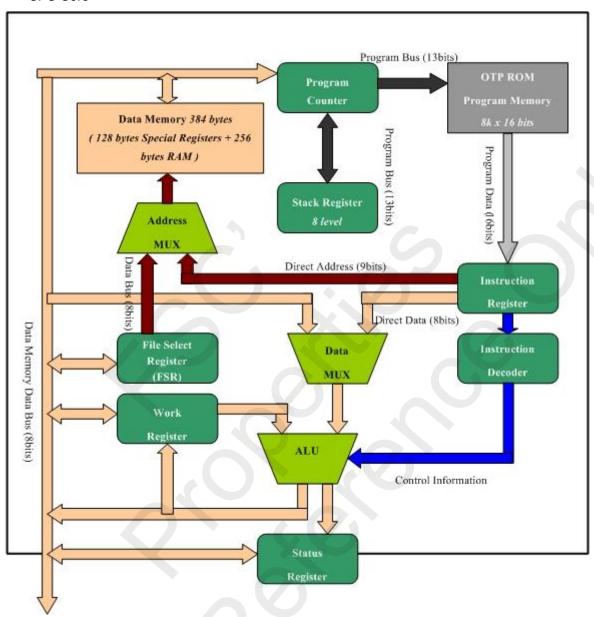

| Figure 1-2 FS98O25 function block                                | 14     |

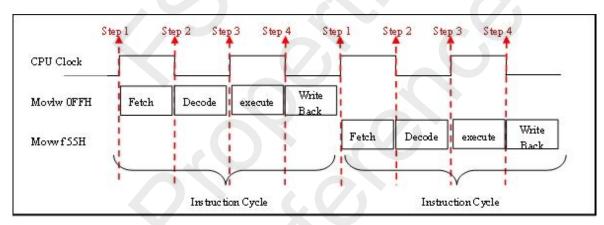

| Figure 1-3 FS98O25 CPU core function block                       |        |

| Figure 1-4 FS98O25 instruction cycle                             | 18     |

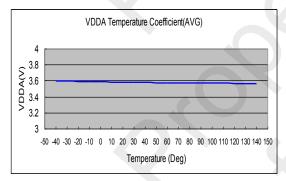

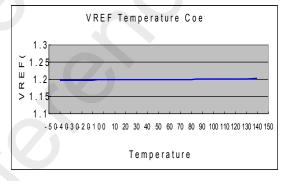

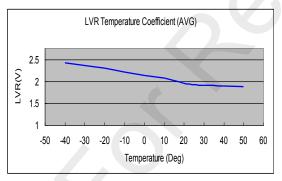

| Figure 2-1 VDDA vs Temp @ VDD=3V Figure 2-2 VREF vs Temp @ VDD   | =3V 20 |

| Figure2-3LVR vs Temp @ VDD=3V20                                  |        |

| Figure 3-1 FS98O25 program memory structure                      | 21     |

| Figure 3-2 IND & FSR function description                        | 23     |

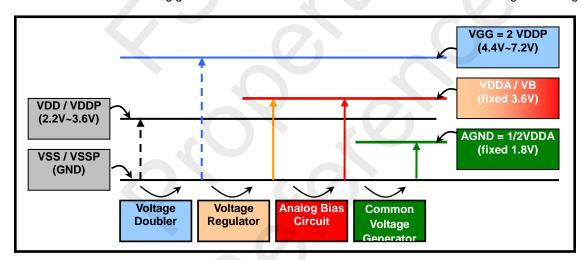

| Figure 4-1 FS98O25 power system block                            |        |

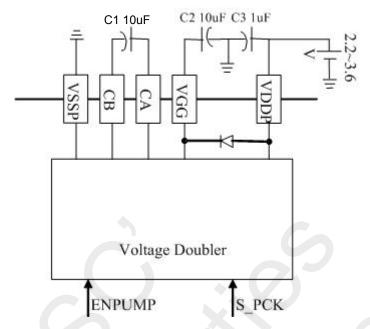

| Figure 4-2 Voltage Doubler                                       |        |

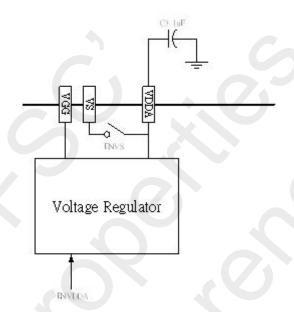

| Figure 4-3 Voltage regulator                                     |        |

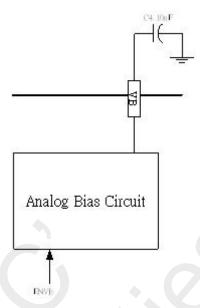

| Figure 4-4 analog bias circuit                                   |        |

| Figure 4-5 analog common voltage generator                       | 36     |

| Figure 4-6 low battery comparator function block                 | 37     |

| Figure 4-7 Bandgap voltage and temperature sensor function block | 38     |

| Figure 5-1 FS98O25 clock system function block                   |        |

| Figure 5-2 FS98O25 oscillator state block                        |        |

| Figure 6-1 FS98O25 timer module function block                   |        |

| Figure 6-2 watch dog timer function block                        | 54     |

| Figure 6-3 Programmable Counter Working block diagram            |        |

| Figure 6-4 Programmable Counter Counter mode                     | 56     |

| Figure 6-5 Programmable Counter Pulse Width Measurement mode     | 57     |

| Figure 6-6 Programmable Counter Frequency Measurement mode       |        |

| Figure 7-1 PT1[7:0] function block                               |        |

| Figure 7-2 PT2[0] PT2[1] PT3[0] PT3[1] function block            |        |

| Figure 7-3 PT2[2] function block                                 | 76     |

| Figure 7-4 PT2[3] PT2[4] function block                          |        |

| Figure 7-5 PT2[6] function block                                 |        |

| Figure 7-6 PT2[7] function block                                 | 81     |

| Figure 8-1 FS98O25 PDM module function block                     |        |

| Figure 8-2 PDM module signal generation                          |        |

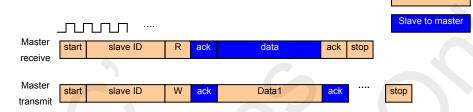

| Figure 9-1 FS98O25 I2C module communication                      |        |

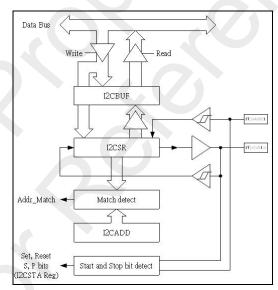

| Figure 9-2 I2C module function block                             | 90     |

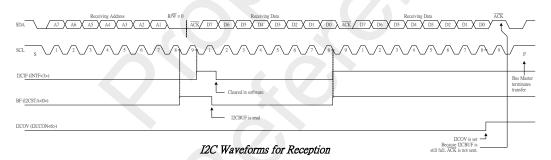

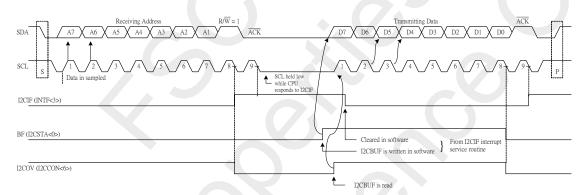

| Figure 9-3 I2C waveform for reception                            | 94     |

| Figure 9-4 I2C waveforms for transmission                        | 95     |

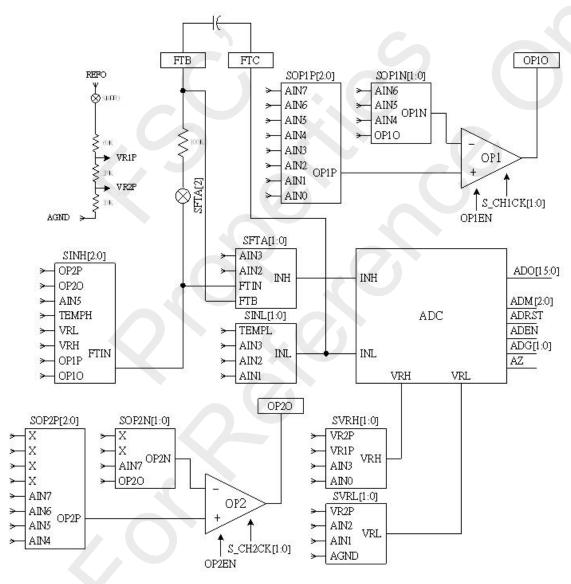

| Figure 10-1 FS98O25 analog function network                      |        |

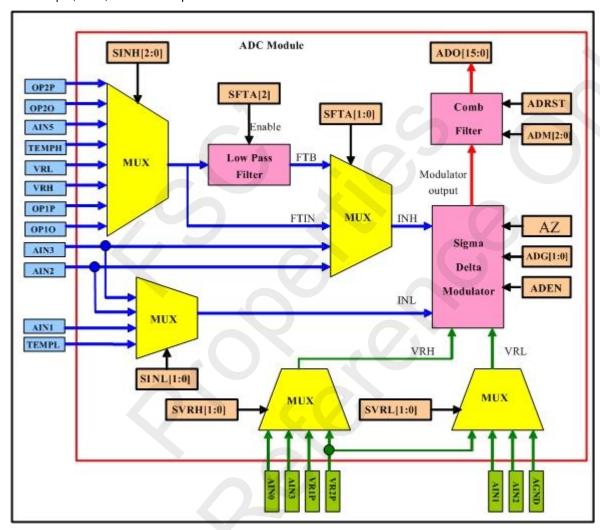

| Figure 10-2 FS98O25 ADC function block                           |        |

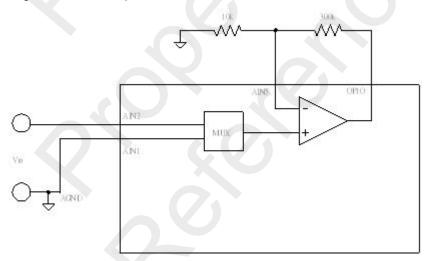

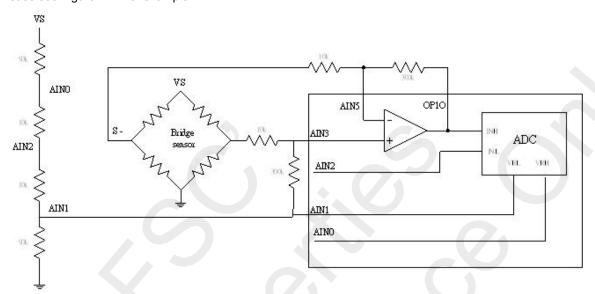

| Figure 12-1 single end amplifier application example             |        |

| Figure 12-2 differential amplifier example                       |        |

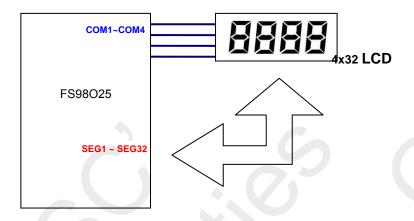

| Figure 13-1 LCD driver control block                             |        |

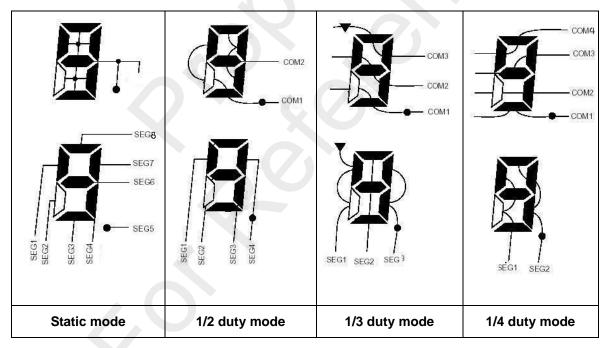

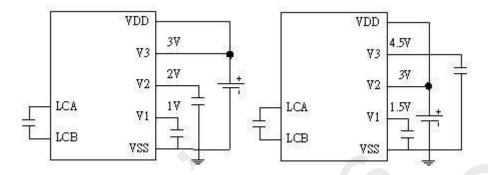

| Figure 13-2 LCD control mode                                     |        |

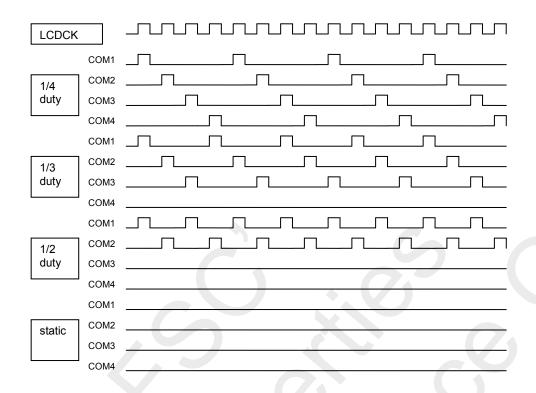

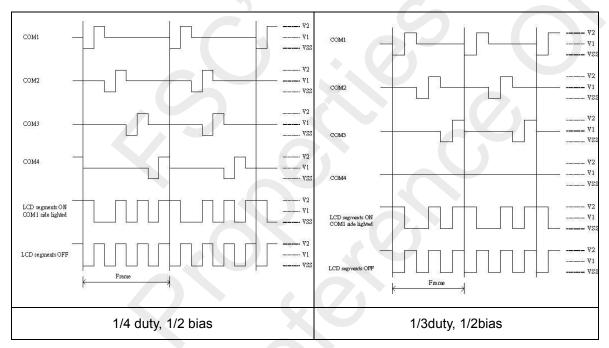

| Figure 13-3 LCD duty mode working cycle                          |        |

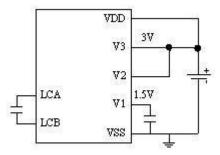

| Figure 13-4 1/3 bias LCD power system circuit connection example |        |

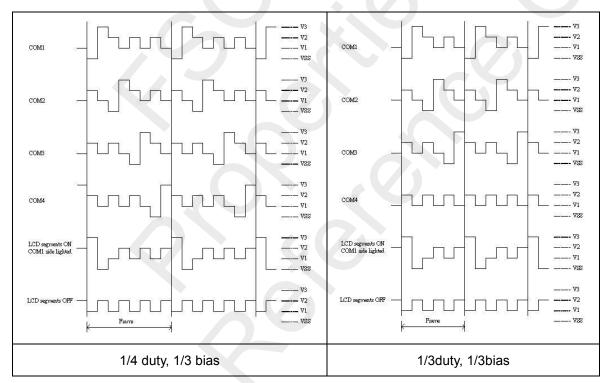

| Figure 13-5 1/3 bias LCD power system clock                      | 119    |

| Figure 13-6 1/2 bias LCD power system circuit connection example | 120    |

| Figure 13-7 1/2 bias LCD power system clock                      |        |

| Figure 16-1 FS98O25 package outline                              | 142    |

# **Table List**

| Table 1-1 Ordering Information                                  |            |

|-----------------------------------------------------------------|------------|

| Table 1-2 FS98O25 pin description                               |            |

| Table 1-3 FS98O25 main function description table               | 15         |

| Table 1-4 FS98O25 CPU core block diagram description table      | 17         |

| Table 2-1 FS98O25 absolute maximum rating table                 | 19         |

| Table 2-2 FS98O25 DC characteristics                            |            |

| Table 2-3 FS98O25 ADC characteristics                           | 20         |

| Table 2-4 FS98O25 OPAMP characteristics                         | 20         |

| Table 3-1 FS98O25 Data memory structure                         | 21         |

| Table 3-2 system register table                                 |            |

| Table 3-3 special register reset table                          |            |

| Table 3-4 peripheral special registers table                    | 27         |

| Table 4-1 FS98O25 power system register table                   |            |

| Table 4-2 Voltage Doubler register table                        |            |

| Table 4-3 Voltage Doubler operation frequency selection table   | 34         |

| Table 4-4 voltage regulator register table                      | 3/         |

| Table 4-5 analog bias circuit register table                    |            |

| Table 4-6 analog common voltage generator register table        |            |

| Table 4-7 low battery comparator register table                 | 27         |

| Table 4-7 low battery comparator register table                 | 3 <i>1</i> |

| Table 4-9 bandgap voltage and temperature sensor register table | 3 <i>1</i> |

| Table 5-1 FS98O25 clock system register table                   |            |

| Table 5-1 FS98O25 clock system register table                   |            |

| Table 5-3 MCK selection table                                   |            |

| Table 5-3 MCK selection table                                   |            |

| Table 5-5 oscillator state selection table                      |            |

| Table 5-6 FS98O25 CPU instruction cycle register table          |            |

| Table 5-6 P596025 CP0 Instruction cycle register table          |            |

| Table 5-8 instruction cycle selection table                     |            |

| Table 5-9 ADC sample frequency selection table                  |            |

| Table 5-10 beeper clock register table                          |            |

| Table 5-10 MCK selection table                                  |            |

| Table 5-11 MCK selection table                                  |            |

| Table 5-13 beeper clock selection table                         |            |

| Table 5-13 beeper clock selection table                         | 42         |

| Table 5-14 register and the beeper clock selection table        |            |

| Table 5-16 Voltage Doubler operation frequency selection table  |            |

| Table 5-17 CLK selection table                                  |            |

| Table 5-18 MCK selection table                                  |            |

| Table 5-19 chopper control signal selection table               | 44         |

| Table 5-19 Chopper Control signal selection table               |            |

| Table 6-1 Timer module and watch dog timer register table       |            |

| Table 6-1 Timer module and watch dog timer register table       |            |

| Table 6-3 timer selection table                                 |            |

| Table 6-4 external timer setup register table                   |            |

| Table 6-5 CLK selection table                                   |            |

| Table 6-6 MCK selection table                                   |            |

| Table 6-7 TMCLK selection table                                 |            |

| Table 6-8 registers and timer selection table                   |            |

| Table 6-9 watch dog timer register table                        |            |

| Table 6-10 Programmable Counter working mode selection table    |            |

| Table 6-11 Programmable Counter Clock signal selection table    |            |

| Table 7-1 FS98O25 I/O port register table                       |            |

| Table 7-1 F396023 WO port register table                        |            |

| Table 7-3 PT2 register table                                    |            |

| Table 7-4 PT2 register table                                    |            |

| Table 7-4 P12 register table                                    |            |

| Table 7-6 PT2 register table                                    |            |

| Table 7-7 PT2[7] register table                                 |            |

|                                                                 |            |

| Table 8-1 PDM module register table               |       |

|---------------------------------------------------|-------|

| Table 8-2 PMD register table                      |       |

| Table 8-3 PDM CLK selection table                 |       |

| Table 9-1 I2C module register table               | 91    |

| Table 9-2 I2C register table                      |       |

| Table 10-1 analog function network register table | 97    |

| Table 10-2 ADC function register table            | . 106 |

| Table 10-3 FTIN selection table                   | . 106 |

| Table 10-4 FTB selection table                    | . 106 |

| Table 10-5 INH selection table                    | . 107 |

| Table 10-6 INL selection table                    | . 107 |

| Table 10-7 ADG selection table                    | . 107 |

| Table 10-8 VRH selection table                    | . 107 |

| Table 10-9 SVRL selection table                   | . 108 |

| Table 10-10 ADC output rate selection table       | . 108 |

| Table 10-11 ADC sample frequency selection table  | . 108 |

| Table 10-12 FS98O25 OPAMP register table          | . 109 |

| Table 10-13 SOP1P selection table                 | . 109 |

| Table 10-14 SOP1N selection table                 | . 109 |

| Table 10-15 chopper mode selection table          |       |

| Table 10-16 FS98O25 OPAMP register table          | 110   |

| Table 10-17 SOP2P selection table                 | 110   |

| Table 10-18 SOP2N selection table                 | 111   |

| Table 10-19 chopper mode selection table          | 111   |

| Table 11-1 ADC rolling counts versus ADM          | 113   |

| Table 11-2 ADC rolling counts versus VR           | 113   |

| Table 13-1 LCD frame frequency selection table    | 117   |

| Table 13-2 LCD duty selection table               | 117   |

| Table 13-3 FS98O25 LCD driver register table      | . 121 |

| Table 13-4 LCD driver register table              | . 126 |

| Table 13-5 CLK selection table                    | . 126 |

| Table 13-6 MCK selection table                    | . 126 |

| Table 13-7 TMCLK selection table                  | . 127 |

| Table 13-8 LCD frame frequency selection table    | . 127 |

| Table 13-9 LCD duty control mode selection table  |       |

| Table 15-1 FS98O25 instruction set table          | 120   |

# **Register List**

| Register STATUS at address 04H  |     |

|---------------------------------|-----|

| Register INTE at address 07H    |     |

| Register INTF at address 06H    |     |

| Register PCK at address 15H     |     |

| Register NETE at address 1CH    |     |

| Register NETF at address 1DH    |     |

| Register SVD at address 1FH     |     |

| Register CTAH at address 08H    | 45  |

| Register CTAL at address 09H    | 45  |

| Register CTBH at address 0AH    | 46  |

| Register CTBL at address 0BH    |     |

| Register CTCON at address 0CH   |     |

| Register WDTCON at address 0DH  |     |

| Register TMOUT at address 0EH   |     |

| Register TMCON at address 0FH   |     |

| Register PT1 at address 20H     |     |

| Register PT1EN at address 21H   |     |

| Register PT1PU at address 22H   |     |

| Register AIENB1 at address 23H  |     |

| Register PT2 at address 24H     | 63  |

| Register PT2EN at address 25H   |     |

| Register PT2PU at address 26H   |     |

| Register PT2MR at address 27H   |     |

| Register PT3 at address 28H     |     |

| Register PT3EN at address 29H   |     |

| Register PT3PU at address 2AH   |     |

| Register PT3MR at address 2BH   |     |

| Register PT2OCB at address 37H  |     |

| Register PT2MR at address 27H   |     |

| Register PMD1H at address 30H   |     |

| Register PMD1L at address 31H   |     |

| Register PMD2H at address 32H   |     |

| Register PMD2L at address 33H   |     |

| Register PMCON at address 36H   |     |

| Register I2CCON at address 57H  |     |

| Register I2CSTA at address 58H  |     |

| Register I2CADD at address 59H  |     |

| Register I2CBUF at address 5AH  |     |

| Register ADOH at address 10H    |     |

| Register ADOL at address 11H    |     |

| Register ADOLL at address 12H   | 99  |

| Register ADCON at address 13H   | 99  |

| Register PCK at address 15H     |     |

| Register NETA at address 18H    |     |

| Register NETB at address 19H    |     |

| Register NETC at address 1AH    |     |

| Register NETD at address 1BH    |     |

| Register LCD1 at address 40H    |     |

| Register LCD2 at address 41H    |     |

| Register LCD3 at address 42H    |     |

| Register LCD4 at address 43H    |     |

| Register LCD5 at address 44H    |     |

| Register LCD6 at address 45H    |     |

| Register I CDENR at address 54H | 125 |

#### 1. Device Overview

The FS98O25 is a CMOS 8-bit single chip microcontroller(MCU) with embedded a 8kx16 bits one-time programmable (OTP) ROM, a 8-channel 14-bit fully differential input analog to digital converter, low noise amplifier, and 4 x 32 LCD driver.

The FS98O25 is best suited for applications such as electrical scale, meter, and sensor or transducer measurement application etc.

#### High Performance RISC CPU

- 8-bit single chip microcontroller(MCU).

- Embedded 8k x 16 bits program memory with one-time programmable (OTP) ROM.

- 256-byte data memory (RAM).

- Only 37 single word instructions to learn

- 8-level memory stacks.

## Peripheral Features

- 20-bit bi-directional I/O port.

- Two PDM (Pulse Density Modulator) output.

- Buzzer output.

- I2C serial I/O port (slave mode only).

- 4 x 32 LCD drivers.

- One 8-channel 14-bit fully differential input analog to digital converter(ADC)

- Two low noise amplifier

# **Analog Features**

- 8-channel Sigma-Delta ADC with programmable output rate and resolution.

- Low noise (1µV Vpp without chopper, 0.5µV Vpp with chopper, 0.1Hz~1Hz) OPAMP with chopper controller.

## Special Microcontroller Features

- External 32768Hz crystal oscillator (RTC).

- Embedded Low Voltage Reset (LVR) and Low Voltage Detector (LVD).

- Embedded charge pump (Voltage Doubler) and voltage regulator (3.6V regulated output).

- Embedded bandgap voltage reference (typical 1.16V±50mV, 150ppm/°C).

- 8 Interrupt sources (external: 5, internal: 3).

- Internal silicon temperature sensor.

- Watchdog timer (WDT).

- Embedded 1.0 MHz oscillator.

- Package: 82-pin dice form, 100-pin LQFP.

## **CMOS Technology**

- Voltage operation ranges from 2.2V to 3.6V.

- Operation current is less than 4 mA; sleep mode current is about 3μA.

## Applications

Sensor or transducer measurement applications.

- Electronic kitchen scale, personal scale.

- Digital meter.

# Ordering Information

Table 1-1 Ordering Information

| <b>Product Number</b> | Description                             | Package Type                  |

|-----------------------|-----------------------------------------|-------------------------------|

| FS98O25               | MCU with OTP ROM; The customer has to   | 82-pin Dice form, 100-pin QFP |

|                       | program the compiled hex code into OTP  |                               |

|                       | ROM.                                    |                               |

| FS98O25-nnnV          | MCU with program type; FSC programs the | 82-pin Dice form, 100-pin QFP |

|                       | customer's compiled hex code into EPROM |                               |

|                       | at factory before shipping.             |                               |

| FS98O251              | 6K ROM version of FS98O25               | 82-pin Dice form, 100-pin QFP |

| FS98O251-nnnV         | 6K ROM version of FS98O25 with program  | 82-pin Dice form, 100-pin QFP |

|                       | type                                    |                               |

Note1: Code number (nnnV) is assigned for customer.

Note2: Code number (nnn = 001~999); Version (V = A~Z).

Figure 1-1 FS98O25 pin configuration

# Pin Description

Table 1-2 FS98O25 pin description

| Name                                | In/Out | Pin No         | Description                                             |

|-------------------------------------|--------|----------------|---------------------------------------------------------|

| VPP                                 | 1      | 1              | Programming Power Supply                                |

| OP2O                                | I/O    | 4              | OPAMP 2 Output                                          |

| OP10                                | I/O    | 5              | OPAMP 1 Output                                          |

| REFO                                | 0      | 6              | Band gap Reference Output                               |

| FTB, FTC                            | I/O    | 7, 8           | ADC Pre-Filter Capacitor Connection                     |

| VB                                  | 1      | 9              | Analog Circuit Bias Current Input                       |

| AGND                                | I/O    | 10             | Analog Ground                                           |

| PT1<0~7>/AIN0~7                     | I/O    | 11~18          | Digital I/O Port or Analog input channel                |

| PT2<0~1>/INT0~1,<br>PT3<0~1>/INT2~3 | I/O    | 19~20<br>34~35 | Digital I/O Port and External Interrupt input           |

| PT2<2,5>/PDM1,2                     | I/O    | 21,24          | Digital I/O Port or PDM output                          |

| PT2<3>/SDA                          | I/O    | 22             | Digital I/O Port or I2C serial Bi-Directional data line |

| PT2<4>/SCL                          | I/O    | 23             | Digital I/O Port or I2C clock input                     |

| PT2<7>/BZ                           | I/O    | 26             | Digital I/O Port or Buzzer Output                       |

| PT3<2>/PFI                          | I/O    | 36             | Digital I/O Port or Programmable Frequency Input        |

| PT3<3>/PFO                          | I/O    | 37             | Digital I/O Port or Programmable Frequency Output       |

| PT2<6>                              | I/O    | 25             | Digital I/O Port                                        |

| SEG32~SEG1                          | 0      | 54~74<br>38~48 | LCD Segment Driver Output                               |

| COM4~COM1                           | 0      | 75~78          | LCD Common Driver Output                                |

| LCA                                 | I/O    | 82             | LCD Charge Pump Capacitor Positive Connection           |

| LCB                                 | I/O    | 83             | LCD Charge Pump Capacitor Negative Connection           |

| V3,V2,V1                            | I/O    | 84~86          | LCD Bias                                                |

| VDDA                                | 1/0    | 87             | Analog Power Output                                     |

| VS                                  | I/O    | 88             | Voltage Source from VDDA                                |

| VGG                                 | I/O    | 89             | Charge Pump Voltage                                     |

| NC                                  | -      | 90             | No Connection                                           |

| VSSP                                |        | 91             | Charge Pump Negative Power Supply                       |

| СВ                                  | I/O    | 92             | Charge Pump Capacitor Negative Connection               |

| CA                                  | I/O    | 93             | Charge Pump Capacitor Positive Connection               |

| VDDP                                | I      | 94             | Charge Pump Positive Power Supply                       |

| VDD                                 | I      | 95             | Positive Power Supply                                   |

| VSS                                 |        | 96             | Negative Power Supply (Ground)                          |

| XOUT                                | 0      | 97             | 32768Hz Oscillator Output                               |

| XIN                                 | 1      | 98             | 32768Hz Oscillator Input                                |

| TST                                 | 1      | 99             | Testing Mode                                            |

| RST                                 | 1      | 100            | CPU Reset                                               |

#### Functional Block Diagram V1,V2,V3 COM[1:4] OP10 PT1[0:7] LCA,LCB SEG[1:32] OP2O AIN[0:7] GPIO - PT 1[0:7] Timer LCD Amplifier Module Module 8 bits 4 \* 32 LCD $\Sigma \; \Delta \, \text{ADC}$ 14 bits XIN Internal 1MHZ External 32768HZ Power Programmable Module Ext. INT 12C PDM Buzzer Counter GPIO - PT 3[0:3] GPIO - PT 2[0:7] REFO AGND PT2[3:4] PT3[2:3] PT3[0:1] PT2[7] PT2[2,5] PT2[0:1] PFI,PFO /INT[2:3] / PDM1,2 /INT[0:1] SDA, SCL

Figure 1-2 FS98O25 function block

There are 5 kinds of functional blocks in the Function Block Diagram, described as table 1-3:

Table 1-3 FS98O25 main function description table

| Item                | Sub Item             | Description                                                                                                                |  |

|---------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| CPU Kernel          | FS98O25 CPU Core     | Please refer to Chapter 1.11 for detailed description                                                                      |  |

|                     | OTP Program Memory   | OTP: One Time Programmable                                                                                                 |  |

|                     |                      | 16k bytes is used for 8k line programming instructions                                                                     |  |

|                     | Data Memory          | FS98O25 has 384 bytes Data Memory embedded in it.                                                                          |  |

|                     |                      | (128 bytes registers, 256 bytes general data memory)                                                                       |  |

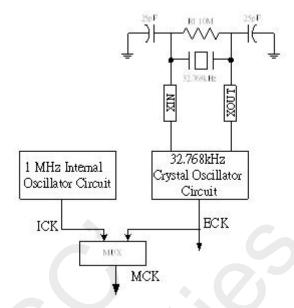

|                     | Clock sys            | There are two clock sources in FS98O25. One is the internal                                                                |  |

|                     |                      | clock which generates 1M HZ for CPU works, and the other                                                                   |  |

|                     |                      | is an external one which provide 32768 HZ clock signal to                                                                  |  |

|                     |                      | the chip.                                                                                                                  |  |

| Digital Function    | Timer Module         | Clock Counter for Time out interrupt and Watch dog Timer                                                                   |  |

|                     | LCD Module           | Embedded 4 X 32 LCD driver                                                                                                 |  |

|                     | I2C                  | Embedded Serial Port for Communication, It support I2C                                                                     |  |

|                     |                      | protocol which is designed by Philips                                                                                      |  |

|                     | PDM                  | Similar to PWM function                                                                                                    |  |

|                     | Buzzer               | User should connect a Buzzer to the embedded buzzer port                                                                   |  |

|                     |                      | to receive the warning or reminding signal.                                                                                |  |

|                     | Programmable Counter | FS98O25 embeds Dual 16-bit Programmable Counter which                                                                      |  |

|                     |                      | could be used to do three kinds of processes: Counter, Pulse                                                               |  |

|                     |                      | Width Measurement and Frequency Measurement.                                                                               |  |

|                     | Ext. INT             | FS98O25 support 2 External Interrupt port                                                                                  |  |

| Analog Function     | ADC                  | An embedded Sigma-Delta Analog to Digital Converter                                                                        |  |

|                     |                      | which converts the analog signal of the sensor to a digital                                                                |  |

|                     | 27 / 15              | number.                                                                                                                    |  |

|                     | OP Amplifier         | FS98O25 has an embedded low noise OP amplifier for                                                                         |  |

|                     |                      | pre-processing the signal, which is connected to the ADC to                                                                |  |

|                     |                      | get a better A/D resolution or amplify the signal to fit the ADC                                                           |  |

| Danna Franckian     | Davis Madela         | Input range.                                                                                                               |  |

| Power Function      | Power Module         | FS98O25 has a special power system. The power system                                                                       |  |

|                     |                      | can supply a fixed voltage for CPU and ADC. The input                                                                      |  |

| Conoral Durage      | PT1                  | voltage of the chip can be within a certain range and floating.  The PT1 port has 8 bits. User can define these 8 bits for |  |

| General Purpose I/O | FII                  |                                                                                                                            |  |

| 1/0                 | PT2                  | general purpose or special assignment as ADC input.  The PT2 port has 8 bits. User can define these 8 bits for             |  |

|                     | FIZ                  | general purpose or some special function as External                                                                       |  |

|                     |                      | Interrupt, I2C, PDM and the Buzzer.                                                                                        |  |

|                     |                      | ווונפוועטן, ובס, דטווו מווע נוופ מעצבפו.                                                                                   |  |

# **CPU Core**

Figure 1-3 FS98O25 CPU core function block

The "CPU Core Block Diagram" shown in Section 1.11 mainly includes 7 important registers and 2 memory units. Please see the Figure 1-3 and the Table 1-4 for detailed information.

Table 1-4 FS98O25 CPU core block diagram description table

| Items     | Sub Items            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Registers | Program Counter      | This Register plays an important role in all the CPU working cycle. It records the pointer of the instruction that the CPU processes every cycle in the <i>Program Memory</i> . In a general CPU cycle, <i>Program Counter</i> pushes the <i>Program Memory Address</i> (13bits), instruction pointer, into the <i>Program Memory</i> and then increments for the next cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|           | Stack Register       | Stack Register is used for recording the program return instruction pointer. When the program calls function, Program Counter will push the instruction pointer into the Stack Register. After finish this function, Stack Register pushes the instruction pointer back to the Program Counter to resume the original program process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|           | Instruction Register | After Program Counter pushes the instruction pointer (Program Memory Address) into the Program Memory, Program Memory pushes the Program Memory Data (16bits), instruction, into Instruction Register for reference.  FS98O25 instruction has 16 bits, and contains 3 kinds of information as Direct Address, Direct Data and Control Information.  CPU could push the Direct Data into Work Register or do some process for the register stored in the Data Memory pointed by the Direct Address by Control Information.  Direct Address (8bits)  It is the Data Memory Address. CPU can use this address to process the Data Memory.  Direct Data (8bits)  It is the value which CPU used for processing Work Register by the ALU (arithmetic and logic unit).  Control Information  It records the information for the ALU to process. |  |  |

|           | Instruction Decoder  | Instruction Register pushes the Control Information to the<br>Instruction Decoder to decode and then sends the decoded<br>information to related registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|           | File Select Register | In FS98O25 Instruction Sets, <i>FSR</i> ( <i>File Select Register</i> ) is used for indirect data process. User could fill the <i>FSR</i> with the <i>Data Memory Address</i> of some register, and then process this register by <i>IND Register</i> . CPU will fill the <i>IND Register</i> with the data address in the <i>Data Memory</i> as <i>FSR</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|           | Work Register        | Work Register is used for buffering the data which is stored in some memory address of Data Memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|           | Status Register      | While CPU processes some register data by <b>ALU</b> , the following status may change as follows: <b>PD</b> , <b>TO</b> , <b>DC</b> , <b>C</b> and <b>Z</b> . Please refer to <b>Section 3.3.2</b> for detailed introduction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Memory    | Program Memory       | FS98O25 has an embedded 16k bytes OTP (One Time Programmable) ROM as Program Memory. Because the OPCODE of the instruction is 16 bits, user could program 8k instructions in FS98O25 at most.  Program Memory Address Bus is 13 bits, and the Data Bus is 16bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|           | Data Memory          | FS98O25 has an embedded 384 bytes Data Memory. The Data Memory Address Bus is 9 bits, and Data Bus is 8 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

#### Clocking Scheme/Instruction Cycle

One Instruction cycle (CPU cycle) includes 4 steps and the CPU could process 2 steps per CPU Clock. Users can setup the MCK Register to decide the step timing. Please refer to Chapter 5 for related information. For Example, if the MCK Register is filled with 0x04H (MCK = ICK, Instruction Cycle = MCK / 2, ICK = 1MHZ), the step timing is 500k HZ, and one instruction cycle needs 4us (2 x 1/500k sec) to complete. The 4 steps are described as follows. Please refer to the CPU core (Section 1.11) to understand these 4 steps.

#### 1 Fetch

Program Counter pushes the Instruction Pointer into Program Memory, and the pointed Data in the Program Memory is stored in the Instruction Register.

#### 2. Decode

The Instruction Register pushes the Direct Address to Address MUX, or pushes the Direct Data to Data MUX, and pushes the Control Information into Instruction Decoder to decode the OPCODE.

#### 3. Execute

ALU executes the process based on the decoded Control Information.

#### 4. Write Back

Push the ALU result to Work Register or Assigned Data Memory Address.

Because one OPCODE can only have either Direct Address or Direct Data, sometimes user needs 2 instructions to complete one simple job. For example, if user want to fill Data Memory address 0x55h with data 0xFF, user needs to process [movlw 0xFFH] to filled Work Register with 0xFFH, and then process [movwf 0x55H] to fill Data Memory 0x55H with Work Register content. For the same reason, CPU needs 2 instruction cycles to complete some kinds of instructions such as call, goto...etc. Please see the Figure 1-4.

Figure 1-4 FS98O25 instruction cycle

# 2. Electrical Characteristics

Absolute Maximum Ratings

Table 2-1 FS98O25 absolute maximum rating table

| Parameter                                       | Rating          | Unit |

|-------------------------------------------------|-----------------|------|

| Supply Voltage to Ground Potential for any port | -0.3 to 5.5     | V    |

| Applied Input/Output Voltage                    | -0.3 to VDD+0.3 | V    |

| Ambient Operating Temperature                   | 0* to +70       | °C   |

| Storage Temperature                             | -55 to +150     | °C   |

| Soldering Temperature, Time                     | 260°C, 10 Sec   |      |

<sup>\*</sup> FS98O25 passed 0°C LTOL (Low Temperature Operating Life) test (VDD=3V)

DC Characteristics (VDD=3V, T<sub>A</sub>=25°C, unless otherwise noted)

Table 2-2 FS98O25 DC characteristics

| Symbol | Parameter                                          | Test Conditions                                             | Min. | Тур.       | Max. | Unit      |

|--------|----------------------------------------------------|-------------------------------------------------------------|------|------------|------|-----------|

| VDD    | Recommended Operation Power Voltage                |                                                             | 2.2  |            | 3.6  | V         |

| IDD1   | Supply Current 1                                   | MCK=1MHz,<br>CPUCLK=MCK/2, Charge<br>Pump, ADC,OPAMP ON     |      | 4          |      | mA        |

| IDD2   | Supply Current 2                                   | Internal Oscillator Off,<br>MCK=32768Hz<br>LCD ON.          |      | 8          | 15   | μА        |

| IPO    | Sleep Mode Supply Current                          | Sleep Instruction                                           |      | 3          |      | μΑ        |

| VIH    | Digital Input High Voltage                         | PT1, Reset                                                  | 0.7  |            |      | VDD       |

| VIL    | Digital Input Low Voltage                          | PT1, Reset                                                  |      |            | 0.3  | VDD       |

| VIHSH  | Input Hys. High Voltage                            | Schmitt-trigger port                                        |      | 0.45       |      | VDD       |

| VIHSL  | Input Hys. Low Voltage                             | Schmitt-trigger port                                        |      | 0.20       |      | VDD       |

| IPU    | Pull up Current                                    | Vin=0                                                       |      | 20         |      | μΑ        |

| IOH    | High Level Output Current                          | VOH=VDD-0.3 V                                               |      | 7          |      | mA        |

| IOL    | Low Level Output Current                           | VOL=0.3 V                                                   |      | 5          |      | mA        |

| VDDA   | Analog Power                                       |                                                             |      | 3.6        |      | V         |

| IREG   | VDDA Regulator Output Current                      | VDD=3V<br>Internal Voltage Double<br>VDDA=0.95*VDDA(unload) |      | 6          |      | mA        |

| VCVDDA | VDDA Voltage Coefficient                           |                                                             | -2   |            | 2    | %/V       |

| AGND   | Analog Ground Voltage                              |                                                             |      | VDDA/2     |      | V         |

| VREF   | Build in Reference Voltage                         | To AGND                                                     |      | 1.18       |      | V         |

| TCREF  | Build in Reference Voltage Temperature Coefficient | Ta=0~50°C                                                   |      | 100        |      | ppm/<br>℃ |

| VLBAT  | Low Battery Detection Voltage                      | S_LB [1:0]=00<br>S_LB [1:0]=01                              |      | 2.3<br>3.5 |      | V         |

| VSR    | VS Switch Resistor                                 |                                                             |      | 10         |      | Ω         |

| FRC    | Internal RC oscillator                             |                                                             | 0.7  | 1.0        | 1.3  | MHz       |

| FWDT   | Internal WDT Clock                                 |                                                             |      | 2.1        |      | kHz       |

Table 2-3 FS98O25 ADC characteristics

| Symbol | Parameter                                          | Test Conditions        | Min. | Тур.   | Max.                | Unit   |

|--------|----------------------------------------------------|------------------------|------|--------|---------------------|--------|

| VACIN  | ADC Common Mode Input Range                        | INH,INL,VRH,VRL to VSS | 0.6  | 0      | 2.3                 | V      |

| VADIN  | ADC Differential Mode Input Range                  | (INH,INL), (VRH,VRL)   |      |        | 0.6                 | V      |

|        | Resolution                                         |                        |      | ±15625 | ±31250 <sup>1</sup> | Counts |

|        | ADC Linearity Error                                | VRFIN=0.44V            | -0.1 | 0      | +0.1                | mV     |

|        | ADC Input Offset Voltage<br>With Zero Cancellation | VRFIN=0.44V<br>VAIN=0  |      | 0      |                     | V      |

OPAMP Characteristics (VDD=3V, T<sub>A</sub>=25°C, unless otherwise noted)

Table 2-4 FS98O25 OPAMP characteristics

| Symbol | Parameter                          | Test Conditions    | Min. | Тур. | Max. | Unit |

|--------|------------------------------------|--------------------|------|------|------|------|

|        | Input Offset                       |                    |      | 1.5  |      | mV   |

|        | Input Offset Voltage with Chopper  | Rs<100 .           |      | 20   |      | V    |

|        | Input Reference Noise              | Rs=100 , 0.1Hz~1Hz |      | 1.0  |      | Vpp  |

|        | Input Reference Noise with Chopper | Rs=100 , 0.1Hz~1Hz |      | 0.5  |      | Vpp  |

|        | Input Bias Current                 |                    |      | 10   | 30   | pА   |

|        | Input Bias Current with Chopper    |                    |      | 100  | 300  | pА   |

|        | Input Common Mode Range            | / • . \            | 0.5  |      | 2.4  | V    |

|        | Output Voltage Range               |                    | 0.5  |      | 2.4  | V    |

|        | Chopper Clock Frequency            | S_CHCK[1:0]=11     |      | 1k   |      | Hz   |

|        | Capacitor Load                     |                    |      | 50   | 100  | pF   |

# Temperature Characteristics(VDD=3V)

Figure 2-1 VDDA vs Temp @ VDD=3V

Figure 2-2 VREF vs Temp @ VDD=3V

Figure 2-3 LVR vs Temp @ VDD=3V

**Rev. 1.5** 20/142

<sup>&</sup>lt;sup>1</sup> Use ADOH, ADOL and ADOLL (Extra ADC output register) three register (24 bits ADC output)

# 3. Memory Organization

## **Program Memory Structure**

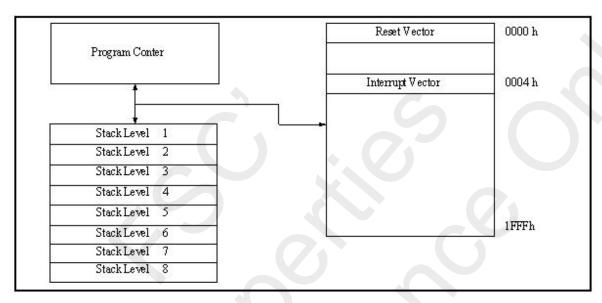

FS98O25 has an 13bits Program Counter which is capable of addressing a 8k x 16bits program memory space and a 8 level depth 13bits Stack Register. The Start up/Reset Vector is at 0x0000H. When FS98O25 is started or its program is reset, the Program Counter will point to Reset Vector. The Interrupt Vector is at 0x0004H. No matter what ISR is processed, the Program Counter will point to Interrupt Vector. Please see Figure 3-1.

Figure 3-1 FS98O25 program memory structure

# **Data Memory Structure**

FS98O25 has a 384-byte Data Memory. The data memory is partitioned into three parts. The area with address 00h~07h is reserved for system special registers, such as indirect address, indirect address pointer, status register, working register, interrupt flag, interrupt control register. The address 08h~7Fh areas are peripheral special registers, such as I/O ports, timer, ADC, signal conditional network control register, LCD driver. The address 80h~17Fh areas are general data memory. Please see Table 3-1.

| Start Address | End Address | Data Memory                    |

|---------------|-------------|--------------------------------|

| 0Х00Н         | 0Х07Н       | System Special Registers       |

| 0Х08Н         | 0X7FH       | Peripheral Special Registers   |

| 0Х80Н         | 0X17FH      | General Data Memory(256 bytes) |

Table 3-1 FS98O25 Data memory structure

# System Special Registers

The System Special Registers are designed to complete CPU Core functions, and consists of indirect address, indirect address pointer, status register, work register, interrupt flag, and interrupt control register. Please see Section 1.11 for related CPU work flow chart.

Table 3-2 system register table

| Address | Name   | Referenced<br>Section | Bit 7   | Bit 6                                      | Bit 5 | Bit 4  | Bit 3   | Bit 2   | Bit 1 | Bit 0 | Value on Power on Reset <sup>2</sup> |  |  |

|---------|--------|-----------------------|---------|--------------------------------------------|-------|--------|---------|---------|-------|-------|--------------------------------------|--|--|

| 00H     | IND0   | 027                   | Use co  | se contents of FSR0 to address data memory |       |        |         |         |       |       | uuuuuuu                              |  |  |

| 01H     | IND1   | 3.4.1                 | Use co  | e contents of FSR1 to address data memory  |       |        |         |         |       |       | uuuuuuu                              |  |  |

| 02H     | FSR0   | 1.11/3.4.1            | Indired | irect data memory address pointer 0        |       |        |         |         |       |       | uuuuuuu                              |  |  |

| 03H     | FSR1   | 1.11/3.4.1            | Indired | t data                                     | memo  | ry add | ress po | inter 1 |       |       | uuuuuuu                              |  |  |

| 04H     | STATUS | 1.11/3.4.2            | IRP1    | IRP0                                       |       | PD     | TO      | DC      | С     | Z     | 00u00uuu                             |  |  |

| 05H     | WORK   | 1.11                  |         |                                            |       | WOF    | RK regi | ster    |       |       | uuuuuuu                              |  |  |

| 06H     | INTF   | 3/6/7/9/10/11         |         |                                            |       | TMIF   | 12CIF   | ADIF    | E1IF  | E0IF  | 0000000                              |  |  |

| 07H     | INTE   | 3/6/7/9/10/11         | GIE     |                                            |       | TMIE   | 12CIE   | ADIE    | E1IE  | E0IE  | 00000000                             |  |  |

| 16H     | INTF2  | 6/7                   |         |                                            |       |        |         | CTIF    | E3IF  | E2IF  | 00000000                             |  |  |

| 17H     | INTE2  | 6/7                   |         |                                            |       |        |         | CTIE    | E3IE  | E2IE  | 0000000                              |  |  |

Rev. 1.5 22/142

<sup>&</sup>lt;sup>2</sup> u mean unknown or unchanged

# 3..1 Special Register Contents after External Reset (Power On Reset) and WDT Reset

| Register     | Register | Register       | Content   |

|--------------|----------|----------------|-----------|

| Address      | Name     | External Reset | WDT Reset |

| 04H          | STATUS   | 00u00uuu       | uuuu1uuu  |

| 0DH          | WDTCON   | 00000000       | uuuuuuu   |

| 20H          | PT1      | 00000000       | иииииии   |

| 21H          | PT1EN    | 00000000       | uuuuuuuu  |

| 22H          | PT1PU    | 00000000       | uuuuuuu   |

| 23H          | AIENB1   | 00000000       | uuuuuuuu  |

| 24H          | PT2      | 00000000       | uuuuuuu   |

| 25H          | PT2EN    | 00000000       | uuuuuuuu  |

| 26H          | PT2PU    | 00000000       | uuuuuuuu  |

| 27H          | PT2MR    | 00000000       | uuuuuuu   |

| 28H          | PT3      | 00000000       | uuuuuuu   |

| 29H          | PT3EN    | 00000000       | uuuuuuu   |

| 2AH          | PT3PU    | 00000000       | uuuuuuu   |

| 2BH          | PT3MR    | 00000000       | uuuuuuu   |

| 37H          | PT2OC    | uuu11uuu       | uuuuuuu   |

| 57H          | I2CCON   | 0001uuuu       | uuuuuuuu  |

| 58H          | STA      | uu0000u0       | uuuuuuu   |

| 59H          | I2CADD   | 00000000       | иииииии   |

| 5 <b>A</b> H | 12CBLIE  | 00000000       |           |

Table 3-3 special register reset table

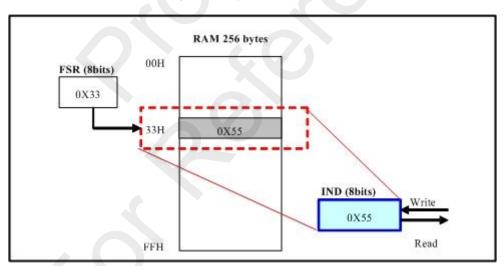

# 3..2 IND and FSR Registers

The IND (Indirect Addressing) register is not a physical register, but indirect addressing needs the IND register. Any instruction using the IND register actually accesses the register pointed by the FSR (File Select Register). While user reads data from the IND register, the CPU gets the data from the Data Memory at the address stored in FSR. While user writes the data into IND register, CPU actually saves the data into Data Memory at the address stored in FSR. Please see Figure 3-2.

Figure 3-2 IND & FSR function description

#### 3..3 STATUS Register

The STATUS register contains the arithmetic status of ALU and the RESET status. The STATUS register is similar to other registers, and can be the destination for any instruction. If the STATUS register is the destination for an instruction that affects the Z, DC or C bit, then the writing to these three bits is disabled. These bits are set or cleared according to the device logic. The TO and PD bits are not writable.

Register STATUS at address 04H

| property | R/W-0 | R/W-0 | U-X | R-0 | R-0 | R/W-X | R/W-X | R/W-X |

|----------|-------|-------|-----|-----|-----|-------|-------|-------|

| STATUS   | IRP1  | IRP0  |     | PD  | то  | DC    | С     | Z     |

|          | Bit7  |       |     |     |     |       |       | Bit0  |

Bit 7 IRP1: Indirect address 1 page select

1 = Indirect address 1 extend memory address is set (Memory 1XXH)

0 = Indirect address 1 extend memory address is Not set (Memory 0XXH)

Bit 6 IRP0: Indirect address 0 page select

1 = Indirect address 0 extend memory address is set (Memory 1XXH)

0 = Indirect address 0 extend memory address is Not set (Memory 0XXH)

Bit 4 **PD**: Power down Flag.

1 = By execution of SLEEP instruction

0 = After power-on reset

Bit 3 To: Watch Dog Time Out Flag. Cleared by writing 0 and Set by Watch Dog Time Out

1 = A Watch Dog Timer time-out occurred

0 = After power-on reset

Bit 2 DC: Digit Carry Flag/borrow Flag, for ADDWF(C) and SUBWF(C)

(for borrow the polarity is reversed)

1 = If there is a carry out from the 4th bit of the result

0 = No carry out from the 4th bit of the result

Bit 1 C: Carry Flag/borrow Flag (~Borrow)

(for borrow the polarity is reversed)

1 = If there is a carry out from the Most Significant bit of the result

0 = No carry out from the most significant bit of the result

Bit 0 **Z**: Zero Flag

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is NOT zero

**Rev. 1.5** 24/142

# 3..4 INTE and INTF registers

The INTE and INTF registers are readable and writable registers, and contain enable and flag bits for interrupt devices.

Register INTE at address 07H

| property | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|-------|-----|-----|-------|-------|-------|-------|-------|

| INTE     | GIE   |     |     | TMIE  | I2CIE | ADIE  | E1IE  | E0IE  |

|          | Rit7  | •   | •   |       |       | •     |       | Rit∩  |

Bit 7 GIE: Global Interrupt Enable flag

1 = Enable all unmasked interrupts

0 = Disable all interrupts

Bit 4 TMIE: 8-bit Timer Interrupt Enable flag

1 = Enable Timer interrupt

0 = Disable Timer interrupt

Bit 3 I2CIE: I2C Interface Interrupt Enable flag

1 = Enable I2C interface interrupt

0 = Disable I2C interface interrupt

Bit 2 ADIE: Analog to Digital converter Interrupt Enable flag

1 = Enable analog to digital converter interrupt

0 = Disable analog to digital converter interrupt

Bit 1 E1IE: PT2.1 External Interrupt Enable flag

1 = Enable PT2.1 external interrupt

0 = Disable PT2.1 external interrupt

Bit 0 E0IE: PT2.0 External Interrupt Enable flag

1 = Enable PT2.0 external interrupt

0 = Disable PT2.0 external interrupt

#### property

| R = Readable bit                 | W = Writable bit | U = unimplemented bit |                    |

|----------------------------------|------------------|-----------------------|--------------------|

| - n = Value at Power On<br>Reset | '1' = Bit is Set | '0' = Bit is Cleared  | X = Bit is unknown |

# Register INTF at address 06H

| property | U-0  | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|------|-----|-----|-------|-------|-------|-------|-------|

| INTF     |      |     |     | TMIF  | I2CIF | ADIF  | E1IF  | E0IF  |

|          | D:+7 |     |     |       |       |       |       | D:40  |

Bit7 Bit0

Bit 4 TMIF: 8-bit Timer Interrupt Flag

1 = Timer interrupt occurred (must be cleared in software)

0 = No Timer interrupt

Bit 3 I2CIF: I2C Interface Interrupt Flag

1 = I2C Interface interrupt occurred (must be cleared in software)

0 = No I2C Interface interrupt

Bit 2 ADIF: Analog to digital converter Interrupt Flag

1 = Analog to digital converter Interrupt occurred (must be cleared in software)

0 = No Analog to digital converter Interrupt

Bit 1 E1IF: PT2.1 External Interrupt Flag

1 = PT2.1 External Interrupt occurred (must be cleared in software)

0 = No PT2.1 External Interrupt

Bit 0 E0IF: PT2.0 External Interrupt Flag

1 = PT2.0 External Interrupt occurred (must be cleared in software)

0 = No PT2.0 External Interrupt

#### property

| R = Readable bit              | W = Writable bit | U = unimplemented bit |                    |

|-------------------------------|------------------|-----------------------|--------------------|

| - n = Value at Power On Reset | '1' = Bit is Set | '0' = Bit is Cleared  | X = Bit is unknown |

# Peripheral Special Registers

The Peripheral Special Registers are designed for Peripheral functions, such as I/O ports, timer, ADC, signal conditional network control register, LCD driver. Please see Table 3-4 and the following Chapters for detailed description of these peripheral functions.

Table 3-4 peripheral special registers table

| Address | Name         | Referenced<br>Section | Bit 7                   | Bit 6                         | Bit 5      | Bit 4        | Bit 3    | Bit 2    | Bit 1      | Bit 0          | Value on<br>Power on<br>Reset |

|---------|--------------|-----------------------|-------------------------|-------------------------------|------------|--------------|----------|----------|------------|----------------|-------------------------------|

| 08H     | CTAH         | 6.3                   |                         |                               |            | CTA[1        |          |          |            |                | uuuuuuu                       |

| 09H     | CTAL         | 6.3                   |                         |                               |            | CTA[7        |          |          |            |                | uuuuuuu                       |

| 0AH     | CTBH         | 6.3                   |                         |                               |            | CTB[1        |          |          |            |                | uuuuuuu                       |

| 0BH     | CTBL         | 6.3                   | <b>T</b> 011            |                               | D/0=1.50   | CTB[7        |          |          | 0.45       |                | uuuuuuu                       |

| 0CH     | CTCON        | 6.3                   | TON                     | MU                            | JXSEL[2:   | 0]           | TE       | FQTMB    |            |                | 0000000u                      |

| 0DH     | WDTCON       | 6.2                   | WTDTEN                  |                               |            |              |          | l V      | NTS [2:0   | )]             | 0uuuu000                      |

| 0EH     | TMOUT        | 6.1                   |                         | ı                             |            | TMOUT        |          | 1        |            |                | 00000000                      |

| 0FH     | TMCON        | 6.1                   | TRST                    |                               |            | 450.14       | TMEN     |          | INS [2:0   |                | 1uuu0000                      |

| 10H     | ADOH         | 10/11                 |                         | ADO [15:8]<br>ADO [7:0]       |            |              |          |          |            | 00000000       |                               |

| 11H     | ADOL         | 10/11                 |                         |                               | F. t       |              |          |          |            |                | 00000000                      |

| 12H     | ADOLL        | 10/11                 |                         |                               | Extra      | ADC out      |          |          | D14 10 1   | \7             | 00000000                      |

| 13H     | ADCON        | 10/11                 |                         | ADRST ADM [2:0]               |            |              | uuuu0000 |          |            |                |                               |

| 14H     | MCK          | 5                     | M7_CK                   | M6_CK                         | M5_CK      |              | М3_СК    | M2_CK    | M1_C<br>K  | M0_CK          | 00000000                      |

| 15H     | PCK          | 4/5/7.5/10            |                         | ENPUMP                        | S_CH2      | CK [1:0]     | S_CH1    | CK [1:0] | S_BE<br>EP | S_PCK          | 00000000                      |

| 18H     | NETA         | 10/11                 | SINL                    | SINL[1:0] SINH[2:0] SFTA[2:0] |            |              |          | 00000000 |            |                |                               |

| 19H     | NETB         | 10/11                 | SOP2                    | N[1:0]                        | SOP1       | N[1:0]       | SVR      | L[1:0]   | SVR        | H[1:0]         | 00000000                      |

| 1AH     | NETC         | 10/11                 | SREFO                   |                               |            |              | ADG      | G[1:0]   | ADEN       | AZ             | 00000000                      |

| 1BH     | NETD         | 10/11                 | OP2EN                   | S                             | OP2P[2:0   | )]           | OP1EN    | S        | OP1P[2:    | 0]             | 00000000                      |

| 1CH     | NETE         | 4/10/11               |                         |                               |            | ENVS         | SILE     | 3[1:0]   | ENLB       |                | 00000000                      |

| 1DH     | NETF         | 4/10/11               |                         | ENBAND                        | ENVDD<br>A |              |          |          | ENAG<br>ND | ENVB           | 00000000                      |

| 1FH     | SVD          | 4.5                   |                         |                               |            |              |          |          |            | LBOUT          | uuuuuuu                       |

| 20H     | PT1          | 7                     |                         |                               |            | PT1 [7       | 7:0]     |          |            |                | uuuuuuu                       |

| 21H     | PT1EN        | 7                     |                         |                               |            | PT1EN        | [7:0]    |          |            |                | 00000000                      |

| 22H     | PT1PU        | 7                     |                         |                               |            | PT1PU        | [7:0]    |          |            |                | 00000000                      |

| 23H     | AIENB1       | 7                     | AIEN                    | B[7:6]                        |            |              | AIENE    | 3[5:0]   |            |                | 00000000                      |

| 24H     | PT2          | 7                     |                         |                               | l .        | PT2 [7       | 7:0]     | • •      |            |                | uuuuuuu                       |

| 25H     | PT2EN        | 7                     |                         |                               |            | PT2EN        | [7:0]    |          |            |                | 00000000                      |

| 26H     | PT2PU        | 7                     |                         | ·                             |            | PT2PU        | [7:0]    |          |            |                | 00000000                      |

| 27H     | PT2MR        | 7.2/7.5/8             | BZEN                    | PM2EN                         |            | PM1EN        | E1M      | 1[1:0]   | EON        | <b>/</b> [1:0] | 00000000                      |

| 28H     | PT3          | 7                     |                         |                               |            |              | 7        | PT3      | [3:0]      |                | uuuuuuu                       |

| 29H     | PT3EN        | 7                     |                         |                               |            |              |          | PT3EN    | ۱ [3:0]    |                | 00000000                      |

| 2AH     | PT3PU        | 7                     |                         |                               |            |              |          | PT3PU    | J [3:0]    |                | 00000000                      |

| 2BH     | PT3MR        | 7                     |                         |                               |            | <b>PFOEN</b> | E3N      | 1[1:0]   | E2N        | <b>/</b> [1:0] | 00000000                      |

| 30H     | PMD1H        | 8                     |                         |                               |            | PMD1[        | 15:8]    |          |            |                | 00000000                      |

| 31H     | PMD1L        | 8                     |                         |                               |            | PMD1[        | 7:0]     |          |            |                | 00000000                      |

| 32H     | PMD2H        |                       |                         |                               |            | PDMD2        | [15:8]   |          |            |                | 00000000                      |

| 33H     | PMD2L        |                       |                         |                               |            | PDMD2        | [7:0]    |          |            |                | 00000000                      |

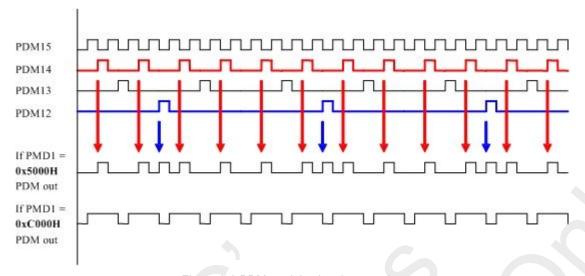

| 36H     | <b>PMCON</b> | 8                     |                         |                               |            | <b>PDMEN</b> |          | Р        | MCS[2:     | [0             | 00000000                      |