# Ultra-wide bandwidth, low-noise 3-axis digital accelerometer

#### **Features**

- 3-axis accelerometer with digital output

- User-selectable full-scale: ±2/±4/±8/±16 g

- Ultra-wide and flat frequency response range: from dc to 5 kHz (±3 dB point)

- Ultra-low noise density: down to 90  $\mu g/\sqrt{Hz}$  in 3-axis mode / 65  $\mu g/\sqrt{Hz}$  in single-axis mode

- High stability of the sensitivity over temperature and against mechanical shock

- Extended temperature range from -40 to +105 °C

- · Low power: 1.1 mA with all 3 axes delivering full performance

- SPI serial interface

- · Low-pass or high-pass filter with selectable cut-off frequency

- · Interrupts for wake-up / vibration no vibration / FIFO thresholds

- · Embedded FIFO: 3 kB

- · Embedded temperature sensor

- Embedded self-test

- Supply voltage: 2.1 V to 3.6 V

- Compact package: LGA 2.5 x 3 x 0.83 mm 14-lead

- ECOPACK<sup>®</sup>, RoHS and "Green" compliant

#### Product status link

**IIS3DWB**

| Product summary        |               |  |  |  |

|------------------------|---------------|--|--|--|

| Order code             | IIS3DWBTR     |  |  |  |

| Temperature range [°C] | -40 to +105   |  |  |  |

| Package                | LGA-14        |  |  |  |

| Packing                | Tape and reel |  |  |  |

#### Product label

### **Applications**

- Vibration monitoring

- Condition monitoring

- · Predictive maintenance

- Test and measurements

### **Description**

The IIS3DWB is a system-in-package featuring a 3-axis digital accelerometer with low noise over an ultra-wide and flat frequency range. The wide bandwidth, low noise, very stable and repeatable sensitivity, together with the capability of operating over an extended temperature range (up to +105 °C), make the device particularly suitable for vibration monitoring in industrial applications.

The high performance delivered at low power consumption, together with the digital output and the embedded digital features like the FIFO and the interrupts are enabling features for battery-operated industrial wireless sensor nodes.

The IIS3DWB has a selectable full-scale acceleration range of ±2/±4/±8/±16 g and is capable of measuring accelerations with a bandwidth up to 5 kHz with an output data rate of 26.7 kHz. A 3 kB first-in, first-out (FIFO) buffer is integrated in the device to avoid any data loss and to limit intervention of the host processor.

The MEMS sensor module family from ST leverages the robust and mature manufacturing processes already used for the production of micromachined accelerometers and gyroscopes to serve automotive, industrial and consumer markets. The sensing elements are manufactured using ST's proprietary

micromachining process, while the embedded IC interfaces are developed using CMOS technology.

The IIS3DWB has a self-test capability which allows checking the functioning of the sensor in the final application. The IIS3DWB is available in a 14-lead plastic land grid array (LGA) package and is guaranteed to operate over an extended temperature range from -40  $^{\circ}\text{C}$  to +105  $^{\circ}\text{C}$ .

DB3769 - Rev 1 page 2/13

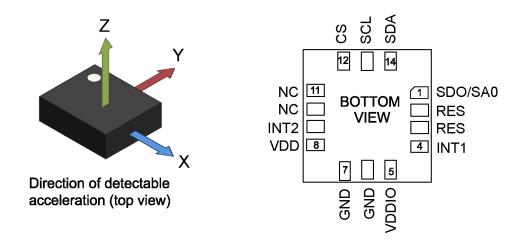

# 1 Pin description

Figure 1. Pin connections

Table 1. Pin desription

| Pin# | Name                  | Function                                                                          |

|------|-----------------------|-----------------------------------------------------------------------------------|

| 4    | SDO/SA0               | SPI 4-wire interface serial data output (SDO)                                     |

| 1    |                       | I <sup>2</sup> C <sup>(1)</sup> least significant bit of the device address (SA0) |

| 2    | RES                   | Connect to VDDIO or GND                                                           |

| 3    | RES                   | Connect to VDDIO or GND                                                           |

| 4    | INT1                  | Programmable interrupt 1                                                          |

| 5    | Vdd_IO <sup>(2)</sup> | Power supply for I/O pins                                                         |

| 6    | GND                   | Connect to GND                                                                    |

| 7    | GND                   | Connect to GND                                                                    |

| 8    | Vdd <sup>(3)</sup>    | Power supply                                                                      |

| 9    | INT2                  | Programmable interrupt 2                                                          |

| 10   | NC                    | Connect to Vdd_IO or leave unconnected <sup>(4)</sup>                             |

| 11   | NC                    | Connect to Vdd_IO or leave unconnected <sup>(4)</sup>                             |

|      |                       | I <sup>2</sup> C/SPI <sup>(1)</sup> mode selection                                |

| 12   | CS                    | (1: SPI idle mode / I²C <sup>(1)</sup> communication enabled;                     |

|      |                       | 0: SPI communication mode / I <sup>2</sup> C <sup>(1)</sup> disabled)             |

| 13   | SCL                   | I <sup>2</sup> C serial clock (SCL)                                               |

| 10   | OOL                   | SPI serial port clock (SPC)                                                       |

|      |                       | I <sup>2</sup> C serial data (SDA)                                                |

| 14   | SDA                   | SPI serial data input (SDI)                                                       |

|      |                       | 3-wire interface serial data output (SDO)                                         |

- 1. I<sup>2</sup>C can be used only in single-axis mode or for debugging.

- 2. Recommended 100 nF filter capacitor.

- 3. Recommended 100 nF plus 10  $\mu$ F capacitors.

- 4. Leave pin electrically unconnected and soldered to PCB.

DB3769 - Rev 1 page 3/13

# 2 Module specifications

### 2.1 Mechanical characteristics

@ Vdd = 3.0 V, T = 25 °C unless otherwise noted. The product is factory calibrated at 3.0 V. The operational power supply range is from 2.1 V to 3.6 V.

**Table 2. Mechanical characteristics**

| Symbol | Parameter                                      | Test conditions   | Min. (1) | Typ. <sup>(2)</sup> | Max. <sup>(1)</sup> | Unit   |

|--------|------------------------------------------------|-------------------|----------|---------------------|---------------------|--------|

| FS     | Linear acceleration measurement range          |                   |          | ±2                  |                     | g      |

|        |                                                |                   |          | ±4                  |                     |        |

|        |                                                |                   |          | ±8                  |                     |        |

|        |                                                |                   |          | ±16                 |                     |        |

| So     | Linear acceleration sensitivity <sup>(3)</sup> | FS = ±2 g         |          | 0.061               |                     | mg/LSB |

|        |                                                | FS = ±4 g         |          | 0.122               |                     |        |

|        |                                                | FS = ±8 g         |          | 0.244               |                     |        |

|        |                                                | FS = ±16 <i>g</i> |          | 0.488               |                     |        |

| BW     | Signal bandwidth                               | ±3 dB point       | 5        |                     |                     | kHz    |

| ODR    | Linear acceleration output data rate           |                   |          | 26.667              |                     | kHz    |

| F0     | Sensor resonant frequency                      |                   |          | 7.0                 |                     | kHz    |

| Тор    | Operating temperature range                    |                   | -40      |                     | +105                | °C     |

<sup>1.</sup> Min/Max values are based on characterization results at 3σ, not tested in production and not guaranteed

DB3769 - Rev 1 page 4/13

<sup>2.</sup> Typical specifications are not guaranteed.

<sup>3.</sup> Sensitivity values after factory calibration test and trimming.

### 2.2 Electrical characteristics

@ Vdd = 3.0 V, T = 25 °C unless otherwise noted.

Table 3. Electrical characteristics

| Symbol                         | Parameter                                           | Test conditions                       | Min. <sup>(1)</sup> | Typ. <sup>(2)</sup> | Max. <sup>(1)</sup> | Unit |

|--------------------------------|-----------------------------------------------------|---------------------------------------|---------------------|---------------------|---------------------|------|

| Vdd                            | Supply voltage                                      |                                       | 2.1                 |                     | 3.6                 | V    |

| Vdd_IO                         | Power supply for I/O                                |                                       | 1.62                |                     | Vdd + 0.1           | V    |

| ldd                            | Accelerometer current consumption                   | ODR = 26.7 kHz                        |                     | 1.1                 |                     | mA   |

| IddPD                          | Accelerometer current consumption during power-down |                                       |                     | 3                   |                     | μA   |

| Ton                            | Turn-on time <sup>(3)</sup>                         |                                       |                     | 10                  |                     | ms   |

| V <sub>IH</sub> <sup>(4)</sup> | Digital high-level input voltage                    |                                       | 0.7 *VDD_IO         |                     |                     | V    |

| V <sub>IL</sub> <sup>(4)</sup> | Digital low-level input voltage                     |                                       |                     |                     | 0.3 *VDD_IO         | V    |

| V <sub>OH</sub> <sup>(4)</sup> | High-level output voltage                           | I <sub>OH</sub> = 4 mA <sup>(5)</sup> | VDD_IO - 0.2        |                     |                     | V    |

| V <sub>OL</sub> <sup>(4)</sup> | Low-level output voltage                            | I <sub>OL</sub> = 4 mA <sup>(5)</sup> |                     |                     | 0.2                 | V    |

| Тор                            | Operating temperature range                         |                                       | -40                 |                     | +105                | °C   |

- 1. Min/Max values are based on characterization results at 3σ, not tested in production and not guaranteed.

- 2. Typical specifications are not guaranteed.

- 3. Time to obtain valid data switching from power-down to normal operation.

- 4. Guaranteed by design characterization and not tested in production.

- 4 mA is the maximum driving capability, i.e. the maximum DC current that can be sourced/sunk by the digital pad in order to guarantee the correct digital output voltage levels V<sub>OH</sub> and V<sub>OL</sub>.

DB3769 - Rev 1 page 5/13

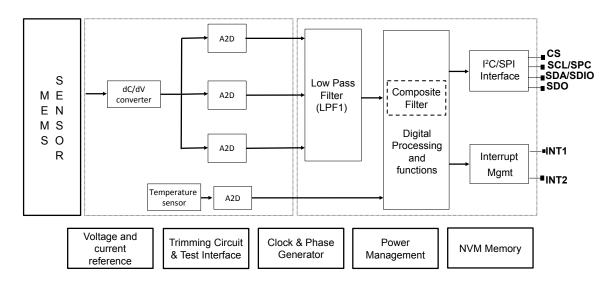

# 3 Block diagram

The IIS3DWB architecture is composed of the following functional blocks:

- · MEMS mechanical element

- ADC

- digital filter (LPF1)

- · composite filter

Figure 2. Accelerometer architecture

DB3769 - Rev 1 page 6/13

## 4 IIS3DWB electrical connections

SDA SCL CS **HOST** I2C/SPI (3/4-w) NC<sup>(1)</sup> 11 SDO/SA0 **IIS3DWB** NC<sup>(1)</sup> TOP **VIEW** INT2 GND or Vdd IO 4 8 Vdd VDD INT1 I<sup>2</sup>C configuration Vdd\_IO 7 GND GND SCL Vdd\_IO SDA 100nF Pull-up to be added  $R_{pu}$ =10kOhm

Figure 3. IIS3DWB electrical connections

The device core is supplied through the Vdd line while the I/O pads are supplied through the Vdd\_IO line. Power supply decoupling capacitors (C1, C2 = 100 nF ceramic) should be placed as near as possible to the the supply pin of the device (common design practice).

The functionality of the device and the measured acceleration data are selectable and accessible through the I<sup>2</sup>C or SPI interfaces. When using the I<sup>2</sup>C protocol, CS must be tied high. Every time the CS line is set to low level, the I<sup>2</sup>C bus is internally reset.

All the functions, the threshold and the timing of the two interrupt pins can be completely programmed by the user through the I²C/SPI interface.

Note: I<sup>2</sup>C can be used only in single-axis mode or for debugging.

DB3769 - Rev 1 page 7/13

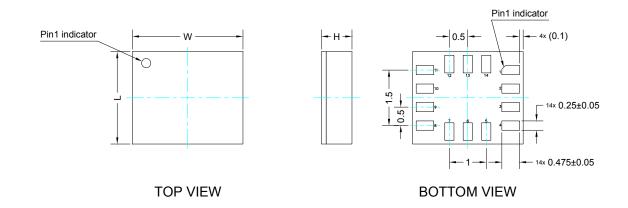

# 5 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

## 5.1 LGA-14L package information

Figure 4. LGA-14L 2.5 x 3.0 x 0.83 mm³ (typ) package outline and mechanical data

Dimensions are in millimeter unless otherwise specified General tolerance is +/-0.1mm unless otherwise specified

### **OUTER DIMENSIONS**

| ITEM       | DIMENSION [mm] | TOLERANCE [mm] |

|------------|----------------|----------------|

| Length [L] | 2.50           | ±0.1           |

| Width [W]  | 3.00           | ±0.1           |

| Height [H] | 0.86           | MAX            |

DM00249496\_1

DB3769 - Rev 1 page 8/13

ALL DIMENSIONS IN MILLIMETRES UNLESS OTHERWISE STATED.

#### LGA-14 packing information 5.2

P2 2.00±0.05(I) Po 4.00±0.10(II) E1 1.75<u>±</u>0.10 Ø1.50 0.00 0.30±0.05 D1 Ø1.50 MIN. R0.20 TYP. Ao SECTION Y-Y SECTION X-X Measured from centreline of sprocket ho to contreline of pocket. Cumulative tolerance of 10 sprocket holes is ± 0.20. Measured from contreline of sprocket hole to centreline of pocket. Other material available. (1) +/- 0.05 Ao Во +/- 0.05 (11) Ko 1.00 +/- 0.10 (111) +/- 0.05 +/- 0.10 +/- 0.30 5.50 8.00 (IV) Forming format : Press form - 17-B W Required length: 170 meter / 22B3 reel

Figure 5. Carrier tape information for LGA-14 package

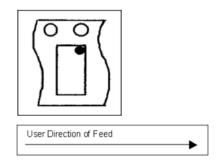

Figure 6. LGA-14 package orientation in carrier tape

DB3769 - Rev 1 page 9/13

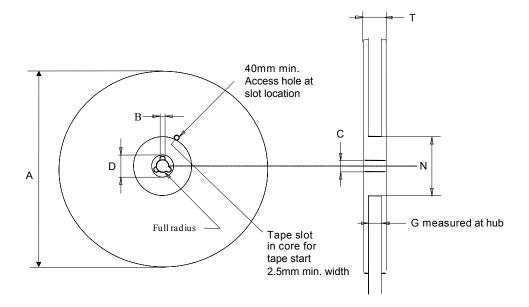

Figure 7. Reel information for carrier tape of LGA-14 package

Table 4. Reel dimensions for carrier tape of LGA-14 package

| Reel dimensions (mm) |            |  |  |

|----------------------|------------|--|--|

| A (max)              | 330        |  |  |

| B (min)              | 1.5        |  |  |

| С                    | 13 ±0.25   |  |  |

| D (min)              | 20.2       |  |  |

| N (min)              | 60         |  |  |

| G                    | 12.4 +2/-0 |  |  |

| T (max)              | 18.4       |  |  |

DB3769 - Rev 1 page 10/13

# **Revision history**

Table 5. Document revision history

| Date        | Version | Changes         |

|-------------|---------|-----------------|

| 15-Nov-2018 | 1       | Initial release |

DB3769 - Rev 1 page 11/13

# **Contents**

| 1   | Pin e | description                 | 3  |  |  |

|-----|-------|-----------------------------|----|--|--|

| 2   | -     |                             |    |  |  |

| _   |       |                             |    |  |  |

|     | 2.1   | Mechanical characteristics  | 4  |  |  |

|     | 2.2   | Electrical characteristics  | 5  |  |  |

| 3   | Bloc  | k diagram                   | 6  |  |  |

| 4   | IIS3I | OWB electrical connections  | 7  |  |  |

| 5   | Pacl  | kage information            | 8  |  |  |

|     | 5.1   | LGA-14L package information | 8  |  |  |

|     | 5.2   | LGA-14 packing information  | 8  |  |  |

| Rev | ision | history                     | 11 |  |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

DB3769 - Rev 1 page 13/13