**Application note**

#### **Document information**

| Information | Content                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | PT2001, combustion, engine, automotive, actuators, diagnostics, four, cylinder                                                        |

| Abstract    | This application note explains how to use PT2001 diagnostics in a typical four cylinder internal combustion engine (ICE) application. |

| Revision history | Revis | sion | histo | ry |

|------------------|-------|------|-------|----|

|------------------|-------|------|-------|----|

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 1.0 | 20190304 | Initial version |

# 1 Introduction

This application note explains how to use PT2001 diagnostics in a typical four cylinder internal combustion engine (ICE) application. The field of powertrain is just one example where diagnostics are required at very high speed. The PT2001 diagnostics manage this through four independent microcores.

This application note seeks to address different fault cases and describes how to program the microcode to detect them during idle and actuation mode.

# 2 Overview

The PT2001 is a 12-channel gate driver IC for automotive engine control applications. The IC consists of five external MOSFET high-side predrivers and seven external MOSFET low-side pre-drivers. The PT2001 provides a flexible solution for the MOSFET's gate drive with a versatile control and optimized latency time. Gate drive, diagnosis, and protection are managed through four independent microcores, two code RAM, and two data RAM banks.

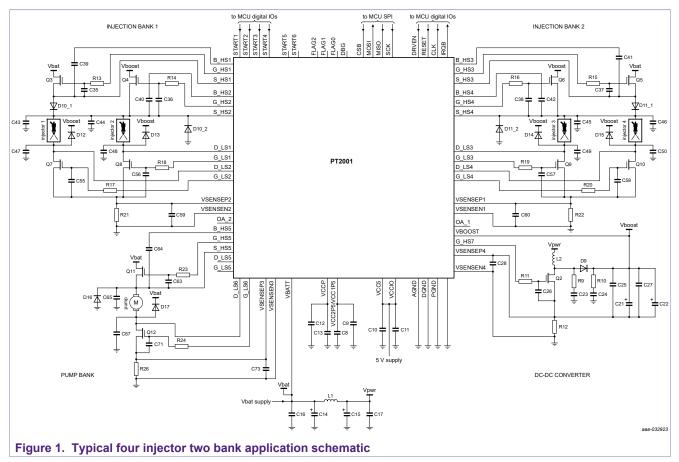

# **3** Application schematic

The PT2001 typical application controls two injection banks, one DC-DC and a pump bank.

# **4** Application instructions

This topology can be used on the evaluation board FRDMPT2001EVM. Register settings and microcode downloads can be achieved by using the FRDM-KL25Z embedded on the FRDMPT2001EVM.

Each bank is individually managed by one microcore of the digital channel 1 as described next:

- The bank #1 is managed by the digital microcore Uc0Ch1 with diagnostics.

- The bank # 2 is managed by the digital microcore Uc1Ch1 without diagnostics.

The two microcores of the second channel (channel 2) drive the DC-DC and the fuel pump as described next:

- The VFM (variable frequency modulation) is managed by the digital microcore Uc0Ch2.

- The fuel pump is managed by the digital microcore Uc1Ch2.

**Note:** This application note only focuses on BANK1 diagnostics managed by the digital microcore Uc0Ch1. See <u>AN4849</u> for register settings and microcode related to injection or DC-DC, unless specified in this document.

The following is the start-up sequence:

- Apply a battery voltage between 5.0 V and 72 V (with an external VCCP regulator).

- Download the registers channel configuration, main configuration, IO configuration, and diagnostic configuration.

- Download the dedicated microcode in the logic channel 1 and logic channel 2 Data RAM.

- Set '1' in the pre-flash enable bit and en dual seq bit in the Flash\_enable register of channel 1 (0x100) and channel 2 (0x120).

The register configurations and the microcodes are detailed in the following sections.

| Parameter name                                                                                       | Description                                                 | Value   |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------|

| IBOOST                                                                                               | Current threshold in boost phase                            | 16.09 A |

| Іреак                                                                                                | Current threshold in peak phase (depends on injectors type) | 14.89 A |

| I <sub>HOLD</sub>                                                                                    | Current threshold in hold phase                             | 8.89 A  |

| t <sub>PEAK_OFF</sub> Fixed time for high-side switch Off in peak phase                              |                                                             | 10 µs   |

| tPEAK_TOT                                                                                            | Fixed time for end of peak phase                            | 500 μs  |

| t <sub>BYPASS</sub> Fixed time for bypass phase                                                      |                                                             | 20 µs   |

| thold_off                                                                                            | Fixed time for high-side switch Off in hold phase           | 10 µs   |

| t <sub>HOLD_TOT</sub> Fixed time for end of hold phase (timeout)                                     |                                                             | 10 ms   |

| t <sub>INJMAXBOOST</sub> Maximum time allowed to reach I <sub>BOOST</sub> (depends on injector type) |                                                             | 500 µs  |

Table 1. Example of injection current profile key parameters

#### **Diagnostics interrupts description:**

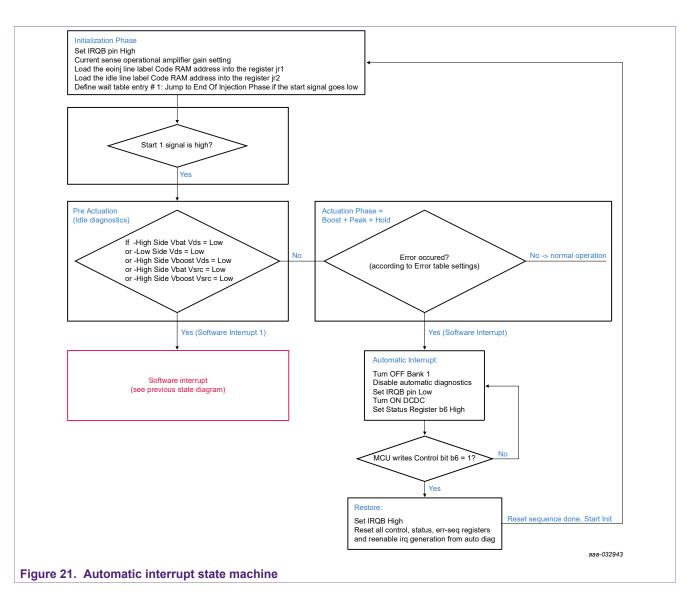

Diagnostics interrupts are handled in two different subroutines: automatic interrupt and software interrupt.

Status\_reg\_uc0 register (0x105) is used to inform MCU on error detected, and then control register is used to unlock the bank.

In all cases, the IRQB pin is set low to inform the MCU about the error detected in PT2001.

**Software interrupts** can be filtered by their req id (stored in Uc0\_irq\_status registers 0x10F):

Pre-diagnostics checks (req id = 1): interrupt occurs if the high-side V<sub>BOOST</sub>/ V<sub>BAT</sub>, V<sub>DS</sub> or V<sub>SRC</sub> are low or V<sub>DS</sub> low-side is low.

If an error occurs, the Status\_reg\_uc0 register (0x105) bit 7 sets high, Bank1 sets OFF, and MCU needs to write a 1 to the control register (0x101) bit 7 to unlock the Bank1.

Boost Error (Req id = 1): if  $I_{BOOST}$  is not reached before  $t_{INJMAXBOOST}$  = 500 µs, this number has to be set according to the injector characteristics.

If an error occurs, Status\_reg\_uc0 register (0x105) bit 5 sets high, Bank1 sets OFF, and MCU needs to write a 1 to the Ctrl\_reg\_uc0 register (0x101) bit 5 to unlock the Bank1.

Hold Error (Req id = 2): if Start signal is still high after  $t_{HOLD OFF}$ .

If an error occurs, the Status\_reg\_uc0 register (0x105) bit 4 sets high, Bank1 sets OFF, and MCU needs to write a 1 to the Ctrl\_reg\_uc0 register (0x101) bit 4 to unlock the Bank1.

**An automatic Interrupt** occurs during actuation, if comparators feedback is different than the error table (see <u>Section 6.3 "Diagnostics configuration registers"</u>).

If an error occurs, the Status\_reg\_uc0 register (0x105) bit 6 sets high, Bank1 sets OFF, and MCU needs to write a 1 to the Ctrl\_reg\_uc0 register (0x101) bit 6 to unlock the Bank1.

| T GIOTO A | . otati | uo_iog. | _400.10 | giotoro | (07100 | ,  | guiulio |         |                             |                |                   |                  |   |   |   |   |

|-----------|---------|---------|---------|---------|--------|----|---------|---------|-----------------------------|----------------|-------------------|------------------|---|---|---|---|

| Bit       | 15      | 14      | 13      | 12      | 11     | 10 | 9       | 8       | 7                           | 6              | 5                 | 4                | 3 | 2 | 1 | 0 |

| Name      |         |         |         |         |        |    |         | status_ | register                    |                |                   |                  |   |   |   | , |

| Value     | x       | x       | x       | x       | x      | x  | х       | x       | sw_<br>interrupt_<br>status | Auto<br>IrqBit | Boost<br>ErrorBit | Hold<br>ErrorBit | x | x | х | x |

#### Table 2. Status\_reg\_uc0 registers (0x105) configuration

Reading this register indicates the type of fault.

#### Table 3. Ctrl\_reg\_uc0 registers (0x101) configuration

| Bit   | 15 | 14 | 13 | 12           | 11          | 10 | 9 | 8 | 7                    | 6                        | 5                 | 4                | 3        | 2 | 1 | 0 |

|-------|----|----|----|--------------|-------------|----|---|---|----------------------|--------------------------|-------------------|------------------|----------|---|---|---|

| Name  |    |    | (  | control_regi | ster_shared | 1  |   |   |                      |                          |                   | control_         | register |   | - |   |

| Value | х  | х  | х  | х            | х           | х  | х | х | IdleDiag<br>ResetBit | Auto<br>Diag<br>ResetBit | Boost<br>ResetBit | Hold<br>ResetBit | х        | х | х | х |

Depending on the status register information, one of the bits must be set to 1 to unlock the BANK.

# 5 Diagnostic descriptions

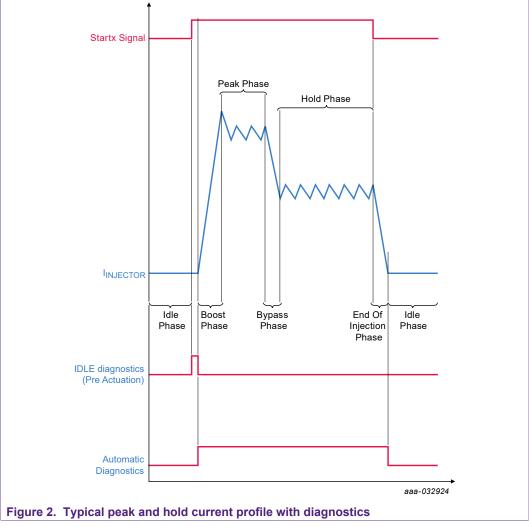

The PT2001 gives the possibility to check faults using two different methods:

• Automatic diagnostics (Actuation phase):

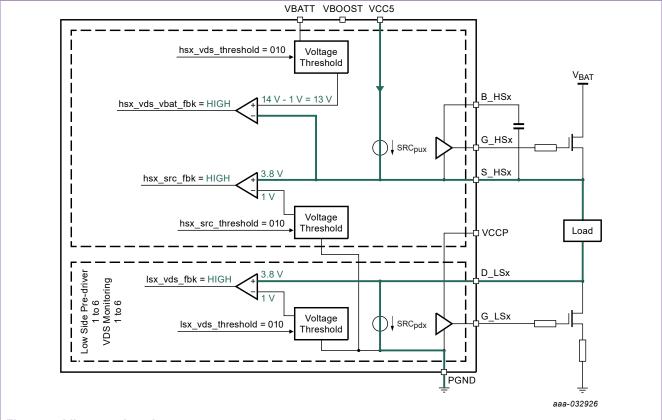

- Boost phase (HSBoost ON): automatic diagnostics are used during actuation phase; it performs a coherency check between an output and the related  $V_{DS}$  feedback (for all the outputs) and  $V_{SRC}$  feedback (for the high-side outputs only).

- Peak and Hold phase (HSBat ON): automatic diagnostics are used during actuation phase; it performs a coherency check between an output and the related V<sub>DS</sub> feedback (for all the outputs) and V<sub>SRC</sub> feedback (for the high-side outputs only).

- Idle diagnostics (Pre-actuation): internal voltage biasing V<sub>BIAS</sub> should be applied to the load to enable diagnostics in this phase.

Several fault cases could occur in the application, the following sections describe most of them, and explain how the PT2001 is able to detect them.

# 5.1 Idle diagnostics (pre-actuation)

As described in Figure 2, idle diagnostics start after a rising edge on the start 1 or start 2 (Bank 1). A voltage biasing  $V_{BIAS}$  should be applied to the load, to enable electrical diagnosis while the external load is not actuating the power stage.

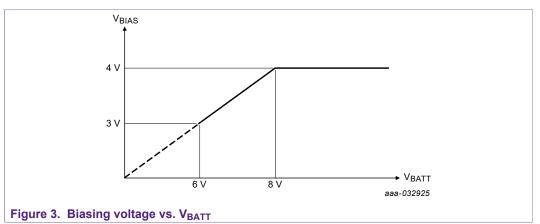

This V<sub>BIAS</sub> voltage is generated by:

- the activation of the SRC<sub>PUX</sub> pull-up voltage source connected to each of the S\_HSx pins. Each pull-up voltage source is supplied from VCC5.

- the activation of each SRC<sub>PDX</sub> pull-down current source connected to each of the D\_LSx pins. Each pull-down voltage source is referenced to ground.

When the battery voltage V<sub>BATT</sub> is in the nominal range or greater, the external load is biased at a minimum voltage of typically 3.8 V. In a low battery voltage condition (V<sub>BATT</sub> < 8.0 V), the load is biased at half the V<sub>BATT</sub> voltage, to guarantee symmetrical voltage margins to high-side and low-side VDS comparators.

The bias generators can be kept ON even during actuation, to control the voltage on the source, even if the MOSFET is OFF. This does not impact the application, because of their low strength. If at least one MOSFET is turned ON, it fixes the voltage on the load and does not affect the bias.

These pre-actuation diagnostics are used to ensure the injectors can be turned ON safely. If an error occurs in any of the following cases, the PT2001 keeps Bank 1 OFF until the MCU writes a 1 through the SPI to the Ctrl\_reg\_uc0 register (0x101) bit 7.

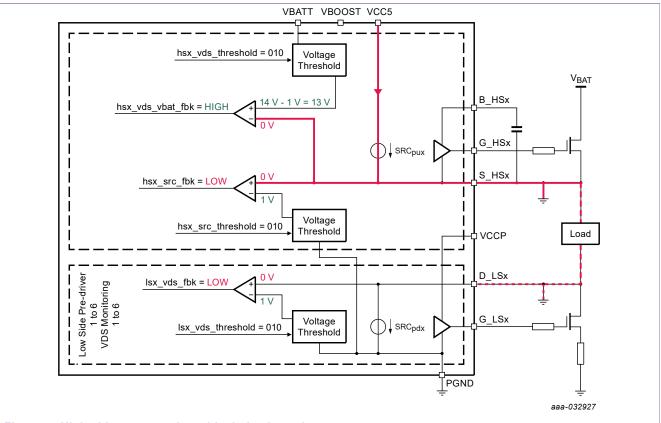

# 5.1.1 Normal behavior

#### Figure 4. Idle normal mode

During normal operation, a current limited pull-up voltage source (SRC<sub>PUX</sub>) generates a voltage on S\_HSx (minimum 3.8 V). The current goes to the load and to a pull-down current source on D\_LSx, generating a 3.8 V minimum voltage. Drain source voltage on the high-side is not monitored directly, and since there is no pin for the drain, monitoring is directly done from  $V_{BAT}$  or  $V_{BOOST}$ , and only HS2 and HS4 can use  $V_{BOOST}$  as a reference. Voltage thresholds are selected to be lower than the voltage generated.

#### Table 4. Normal mode truth table

| Error case  | LSx_vds_fbk | HSx_src_fbk | Hsx_vds_Vbat_fbk | S_HSx voltage V <sub>BAT</sub> | D_LS_x voltage |

|-------------|-------------|-------------|------------------|--------------------------------|----------------|

| Normal mode | 1           | 1           | 1                | 3.8                            | 3.8            |

# 5.1.2 High-side source or low-side drain shorted to GND

#### Figure 5. High-side source or low-side drain shorted

In cases where the high source (S\_HSx) shorts to GND or the low-side drain (D\_LSx) shorts to GND, the current limited voltage source pulls to ground, and the voltage on S\_HSx and D\_LSx is 0 V. A diagnostic error is detected, and since the high-side  $V_{SRC}$  and low-side  $V_{DS}$  feedback are low, the bank does not turn ON.

| Table 5. S HSx or D LSx shorted to GND truth table | Table 5. S | S HSx | or D LS | x shorted t | o GND t | ruth table |

|----------------------------------------------------|------------|-------|---------|-------------|---------|------------|

|----------------------------------------------------|------------|-------|---------|-------------|---------|------------|

| Error case     | LSx_vds_fbk | HSx_src_fbk | Hsx_vds_Vbat_fbk | S_HSx voltage V <sub>BAT</sub> | D_LS_x voltage |

|----------------|-------------|-------------|------------------|--------------------------------|----------------|

| Normal mode    | 1           | 1           | 1                | 3.8                            | 3.8            |

| D_LS GND short | 0           | 0           | 1                | 0                              | 0              |

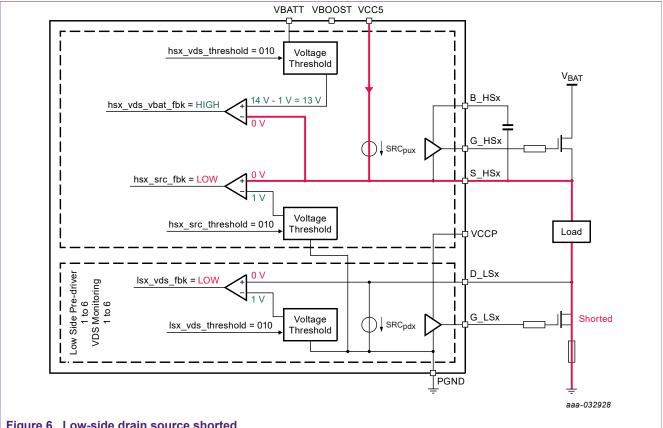

## 5.1.3 Drain source low-side shorted to GND

#### Figure 6. Low-side drain source shorted

In cases where the low-side drain source shorts, D\_LSx pulls to 0 V, the current limited voltage source pulls to ground, and the voltage on S\_HSx and D\_LSx is 0 V. A diagnostic error is detected, since the high-side V<sub>SRC</sub> and low-side V<sub>DS</sub> feedback are low.

#### Table 6. Drain source low-side shorted truth table

| Error case                  | LSx_vds_fbk | HSx_src_fbk | Hsx_vds_Vbat_fbk | S_HSx voltage V <sub>BAT</sub> | D_LS_x voltage |

|-----------------------------|-------------|-------------|------------------|--------------------------------|----------------|

| Normal mode                 | 1           | 1           | 1                | 3.8                            | 3.8            |

| Low-side drain source short | 0           | 0           | 1                | 0                              | 0              |

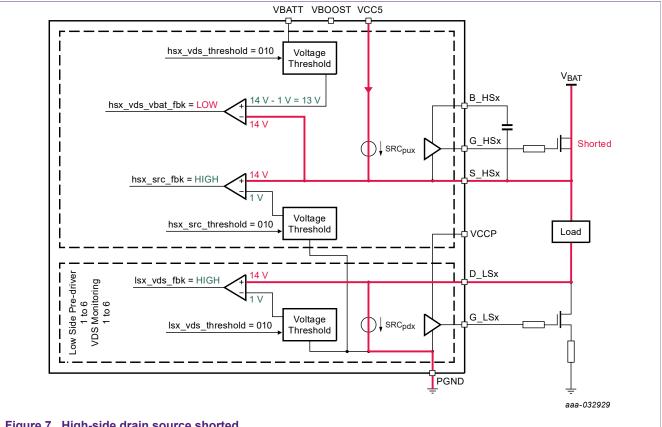

# 5.1.4 Drain source high-side shorted to VBAT

#### Figure 7. High-side drain source shorted

The diagnostic fails in cases where the high-side drain source shorts. As a consequence, S\_HSx and D\_LSx pulls up to V<sub>BAT</sub>, the difference between drain and source on the highside goes negative, resulting in low feedback on the high-side V<sub>DS</sub>.

| Table 7.  | Drain source | e high-side shorted truth table |

|-----------|--------------|---------------------------------|

| 100010111 | Diami ocaiot |                                 |

| Error case                   | LSx_vds_fbk | HSx_src_fbk | Hsx_vds_Vbat_fbk | S_HSx voltage V <sub>BAT</sub> | D_LS_x voltage |

|------------------------------|-------------|-------------|------------------|--------------------------------|----------------|

| Normal mode                  | 1           | 1           | 1                | 3.8                            | 3.8            |

| High-side drain source short | 1           | 1           | 0                | 14                             | 14             |

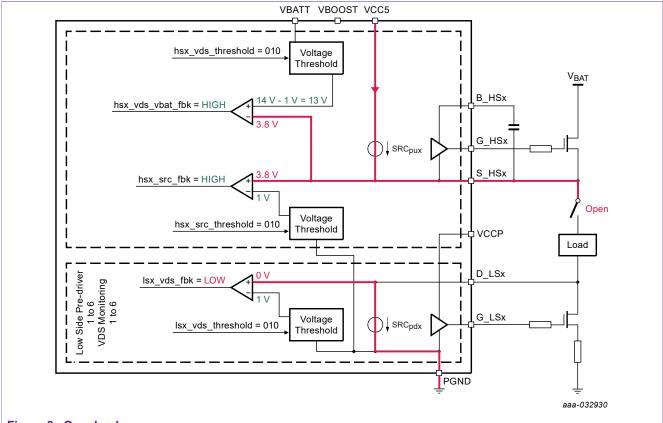

# 5.1.5 Openload

#### Figure 8. Openload

If one of the sides of the load is not connected properly, there is no current path between S\_HSx and D\_LSx. The voltage on D\_LSx is forced to ground, because of the SRC<sub>PDX</sub> current pull-down. The diagnostic fails, because the low-side  $V_{DS}$  feedback is low.

#### Table 8. Openload truth table

| Error case            | LSx_vds_fbk | HSx_src_fbk | Hsx_vds_Vbat_fbk | S_HSx voltage V <sub>BAT</sub> | D_LS_x voltage |

|-----------------------|-------------|-------------|------------------|--------------------------------|----------------|

| Normal mode           | 1           | 1           | 1                | 3.8                            | 3.8            |

| Openload on low-side  | 0           | 1           | 1                | 3.8                            | 0              |

| Openload on high-side | 0           | 1           | 1                | 3.8                            | 0              |

#### 5.1.6 Faults not detected in idle phase

There are different cases that cannot be detected in the idle phase:

- High-side  $V_{\text{BAT}}$  or  $V_{\text{BOOST}}$  open: not possible to be detected since both are OFF in idle phase

- · LS open: not possible to be detected since it is OFF in idle phase

- Short between load pins: not possible to detect, because it allows the bias current to

pass through

All these faults are detected in the actuation mode only.

# 5.2 Actuation phase

The bias voltage used for idle diagnostics is kept ON, to predict the voltage on each pin even if the MOSFETs are OFF. In this case, when the MOSFETs are OFF, there is a 3.8 V voltage on the high-side source. In each case, if an error occurs, the PT2001 turns bank 1 OFF, keeps it OFF, and sets the Status\_reg\_uc0 register (0x105) bit 6 high until the MCU writes a 1 to the control register bit 6.

# 5.2.1 Actuation diagnostics peak and hold phase (HS Boost OFF, HS Bat ON, LS ON)

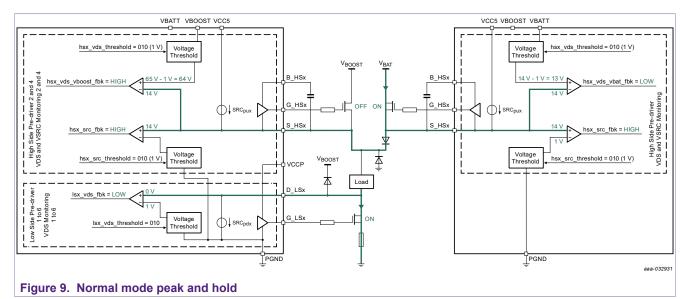

#### 5.2.1.1 Normal mode

During peak and hold phase, the low-side is fully ON and  $V_{BAT}$  high-side is controlled in PWM to regulate the current inside the injector.

To have a device as flexible as possible, detection error during automatic diagnostics is configurable for each low-side and high-side. To configure which case will lead the device to an error, it is necessary to set the registers *Error\_table* for each low-side  $V_{DS}$ , high-side  $V_{DS}$ , and high-side  $S_{RC}$  where diagnostics are needed (see Section 6.3 "Diagnostics configuration registers"). In Normal mode, the PT2001 comparator outputs should be in the following state:

#### Table 9. Actuation in Normal mode truth table

| Error case  | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|-------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode | 0           | 1                | 0                | 1                  | 1                   |

#### 5.2.1.2 High-side (Bat or Boost) source shorted to GND

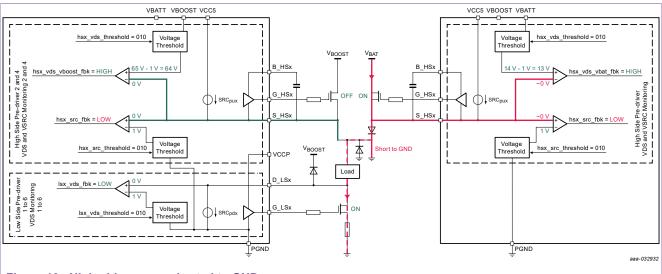

Figure 10. High-side source shorted to GND

When S\_HSx shorts to GND, the PT2001 detects an overcurrent, due to the V<sub>DS</sub> monitoring on the V<sub>BAT</sub> high-side. The high-side shuts down as soon as the current is substantial enough to generate a higher drop across the MOSFET than the threshold. In this case, it is important to set a threshold (1.0 V, in this case) and a filter time to the lowest value allowed by the application, to quickly detect it (see Section 6.3.1.1 "Filter time"). The automatic diagnostic fails, because high-side V<sub>DS</sub> feedback is high.

#### Table 10. High-side source shorted to GND truth table

| Error case                                      | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|-------------------------------------------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode                                     | 0           | 1                | 0                | 1                  | 1                   |

| S_HSx V <sub>BAT</sub> or $V_{BOOST}$ GND short | 0           | 0                | 1                | 1                  | 0                   |

This case is also applicable when there is a short between the two load pins, substantial current flows inside  $V_{BAT}$  HS and LS until the difference between drain and source is higher than the threshold.

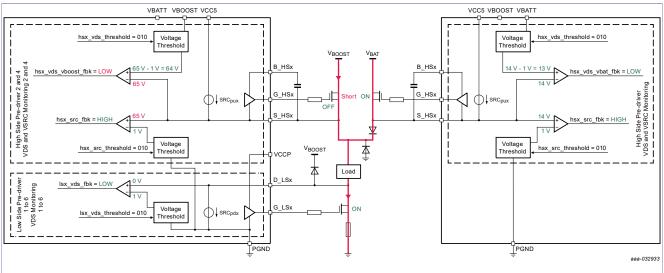

#### 5.2.1.3 High-side V<sub>BOOST</sub> short drain source

#### Figure 11. High-side V<sub>BOOST</sub> shorted

During a peak and hold phase,  $V_{BOOST}$  high-side should be OFF, but if there is a shortcircuit between the drain and source, the voltage on the  $V_{BOOST}$  high-side source rises to  $V_{BOOST}$ . The automatic diagnostic fails, because  $V_{DS}$  on the  $V_{BOOST}$  high-side is low.

#### Table 11. High-side V<sub>BOOST</sub> drain source shorted truth table

| Error case                 | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |  |  |  |

|----------------------------|-------------|------------------|------------------|--------------------|---------------------|--|--|--|

| Normal mode                | 0           | 1                | 0                | 1                  | 1                   |  |  |  |

| HSvboot drain source short | 0           | 1                | 0                | 0                  | 1                   |  |  |  |

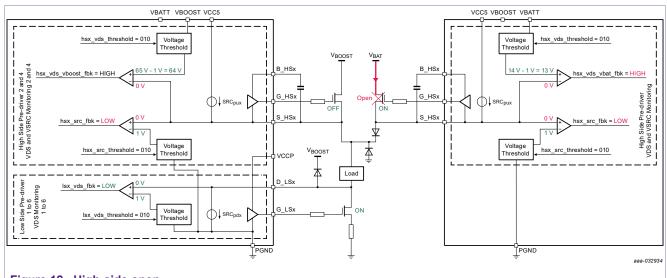

## 5.2.1.4 High-side V<sub>BAT</sub> open

#### Figure 12. High-side open

During peak and hold phase, high-side  $V_{BAT}$  is ON. If open or not controlled properly, S\_HSx voltage will be lower than expected. The automatic diagnostic fails because on  $V_{BAT}$  high-side, the  $V_{DS}$  feedback is high and  $V_{SRC}$  feedback is low.

#### Table 12. High-side V<sub>BAT</sub> open truth table

| Error case   | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|--------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode  | 0           | 1                | 0                | 1                  | 1                   |

| HS vbat open | 0           | 0                | 1                | 1                  | 0                   |

This case is only detectable in actuation mode.

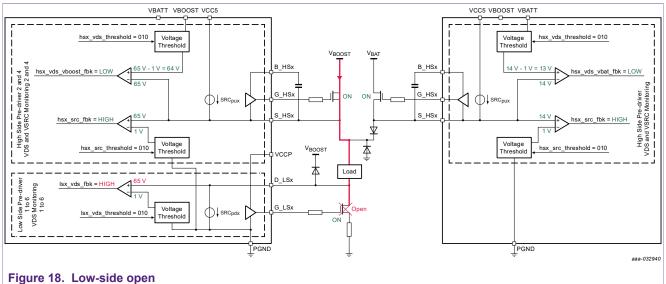

#### 5.2.1.5 Low-side open

With the low-side open, current on the D\_LSx pin flows through the load to the internal pull-down (SCR<sub>PDX</sub>) and the voltage rises to  $V_{BAT}$ . Automatic diagnostics fail, because the low-side  $V_{DS}$  feedback is high.

#### Table 13. Low-side open truth table

| Error case  | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|-------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode | 0           | 1                | 0                | 1                  | 1                   |

| LS open     | 1           | 1                | 0                | 1                  | 1                   |

This is one case only detectable in actuation mode.

## 5.2.1.6 Drain low-side shorted to $V_{\text{BAT}}$ or $V_{\text{BOOST}}$

#### Figure 14. Drain low-side shorted

When the low-side drain is shorted to  $V_{BAT}$  or  $V_{BOOST}$  (low probability case), the voltage on D\_LSx rises to  $V_{BAT}/V_{BOOST}$ . Voltage thresholds and filter times must be set to the lowest value allowed by the application, to detect the error as fast as possible. The automatic diagnostic fails, because the low-side  $V_{DS}$  feedback is high.

#### Table 14. D\_LS battery short truth table

| Error Case                                                  | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|-------------------------------------------------------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode                                                 | 0           | 1                | 0                | 1                  | 1                   |

| D_LS battery short<br>depending on external<br>MOS behavior | 1           | 1                | 0                | 1                  | 1                   |

#### 5.2.1.7 Cases undetectable during peak and hold phase

There are different cases that cannot be detected during peak and hold phase:

- Drain low-side shorted to GND: not detectable since the low-side is ON, in this case (detectable in idle phase)

- High-side V<sub>BAT</sub> drain source shorted: not detectable since the high-side is ON, in this case (detectable in idle phase)

- High-side  $V_{BOOST}$  open: not detectable since the high-side  $V_{BOOST}$  is OFF in this mode (detectable during  $V_{BOOST}$  phase)

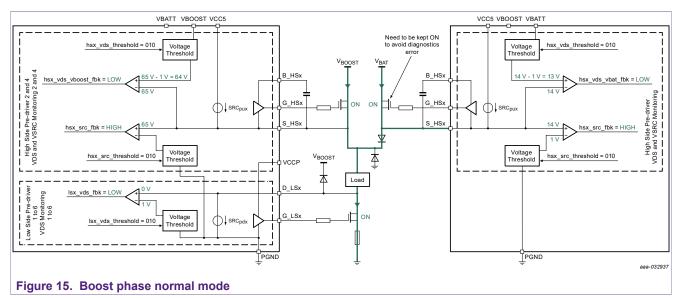

#### 5.2.2 Actuation diagnostics boost phase (HS Boost ON, HS Bat ON, LS ON)

During boost phase, boost voltage is used to turn the injector ON as fast as possible, high-side  $V_{BOOST}$  and low-side are ON. The high-side  $V_{BAT}$  source needs to be turned ON, to avoid errors during diagnostics, which has no impact on the application. Another option would be to disable automatic diagnostics on the high-side  $V_{BAT}$  source during boost phase.

In this example, the PT2001 automatic diagnostics are configured using instruction endiags (see Section 7 "Application source code"). During actuation phase, automatic diagnostics monitor HS  $V_{BAT} V_{DS}$ , HS  $V_{BAT} V_{SRC}$ , HS  $V_{BOOST} V_{DS}$ , and LS  $V_{DS}$  continuously. To simplify the diagnostics code, HS  $V_{BAT}$  is kept ON during boost phase to avoid unwanted errors on the  $V_{BAT}$  source.

### 5.2.2.1 Normal mode

During boost phase, the high-side boost is fully ON to reach boost current as fast as possible, high-side  $V_{BAT}$  is ON (for diagnostic purposes), and the low-side is fully ON. As with the peak and hold phase, the high-side  $V_{BOOST}$  error table must be set-up accordingly (see Section 6.3 "Diagnostics configuration registers").

#### Table 15. Boost phase normal mode truth table

| Error case  | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |  |  |

|-------------|-------------|------------------|------------------|--------------------|---------------------|--|--|

| Normal mode | 0           | 1                | 0                | 0                  | 1                   |  |  |

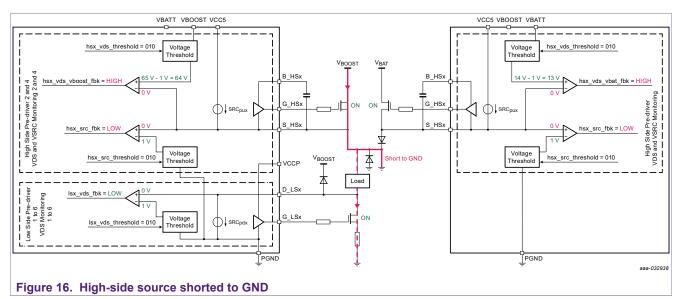

#### 5.2.2.2 High-side boost source shorted to GND

The same behavior as in the peak and hold phase except this time the short is from  $V_{BOOST}$  to GND. The comparator threshold must be set as low as possible to detect the

overcurrent faster and avoid any damage to the MOS. The automatic diagnostic on high-side  $V_{\text{BOOST}}$  fails because  $V_{\text{DS}}$  monitoring is high.

#### Table 16. High-side boost source shorted to GND truth table

| Error case                | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|---------------------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode               | 0           | 1                | 0                | 0                  | 1                   |

| HSvbat drain source short | 0           | 0                | 1                | 1                  | 0                   |

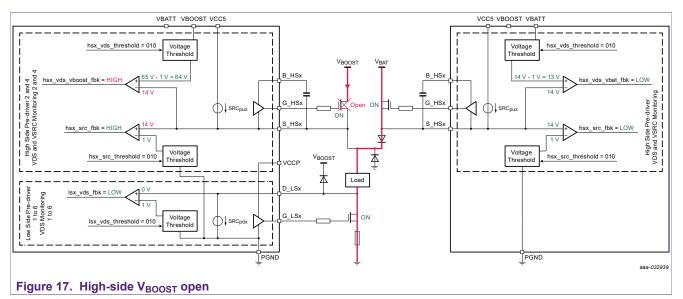

## 5.2.2.3 High-side V<sub>BOOST</sub> open

When V<sub>BOOST</sub> high-side is open, the voltage on S\_HSx floats and forced to 0 V, due to the parasitic leakage on the S\_HSx pin. The automatic diagnostic on high-side V<sub>BOOST</sub> fails because V<sub>DS</sub> feedback is high.

#### Table 17. High-side boost open truth table

| Error case    | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|---------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode   | 0           | 1                | 0                | 0                  | 1                   |

| HS vboot open | 0           | 1                | 0                | 1                  | 1                   |

This case is undetectable in idle phase.

#### 5.2.2.4 Low-side open

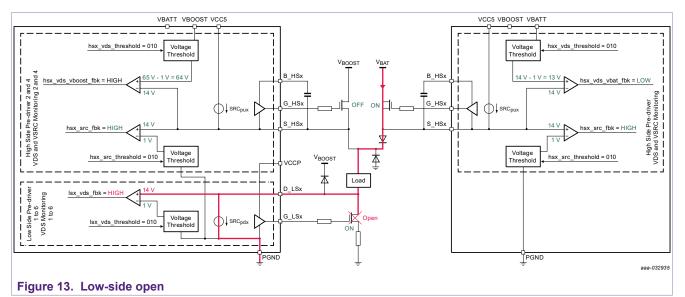

igure 10. Low-side open

When the low-side is not connected properly, the voltage on D\_LSx is around a  $V_{\text{BOOST}}$  of 65 V. The automatic diagnostic fails due to  $V_{\text{DS}}$  feedback on the low-side.

#### Table 18. Low-side open truth table

| Error case  | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|-------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode | 0           | 1                | 0                | 0                  | 1                   |

| LS open     | 1           | 1                | 0                | 0                  | 1                   |

This case is undetectable in idle phase.

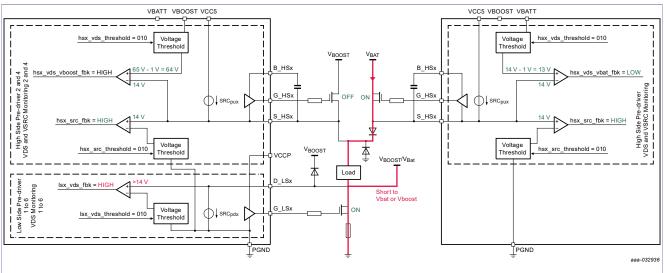

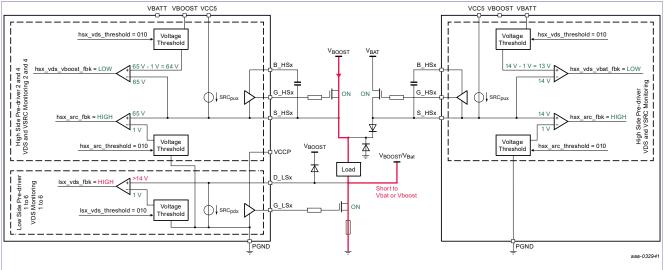

# 5.2.2.5 Drain low-side shorted to $V_{\text{BAT}}$ or $V_{\text{BOOST}}$

#### Figure 19. Drain low-side shorted to $V_{\text{BAT}}$ or $V_{\text{BOOST}}$

This is the same behavior as in the peak and hold phase, when the drain low-side is shorted to V<sub>BAT</sub> or V<sub>BOOST</sub> (low probability), with a short to GND on V<sub>BOOST</sub> or V<sub>BAT</sub>. The automatic diagnostic fails, because the voltage on D\_LSx is higher than the V<sub>DS</sub> threshold.

#### Table 19. Drain low-side shorted to $V_{\text{BAT}}$ or $V_{\text{BOOST}}$ truth table

| Error case           | LSx_vds_fbk | HSx_src_vbat_fbk | Hsx_vds_Vbat_fbk | HSx_vds_Vboost_fbk | HSx_vsrc_Vboost_fbk |

|----------------------|-------------|------------------|------------------|--------------------|---------------------|

| Normal mode          | 0           | 1                | 0                | 0                  | 1                   |

| D_LS boost/bat short | 1           | 1                | 0                | 0                  | 1                   |

#### 5.2.2.6 Cases undetectable during boost mode

There are different cases undetectable in the boost phase:

- Drain low-side shorted to GND: not detectable, since the low-side is ON in this case (detectable in the idle phase)

- High-side V<sub>BAT</sub> or V<sub>BOOST</sub> drain source shorted: not detectable, since in this case, highside is ON (detectable in the idle phase)

- High-side  $V_{BOOST}$  open: not detectable, since the high-side  $V_{BOOST}$  is OFF in this mode (detectable during the  $V_{BOOST}$  phase)

- A short on the high-side V<sub>BAT</sub> source S\_HSx (before diode): the high-side V<sub>BAT</sub> is OFF in this mode, but detectable during the idle phase

# 6 Software

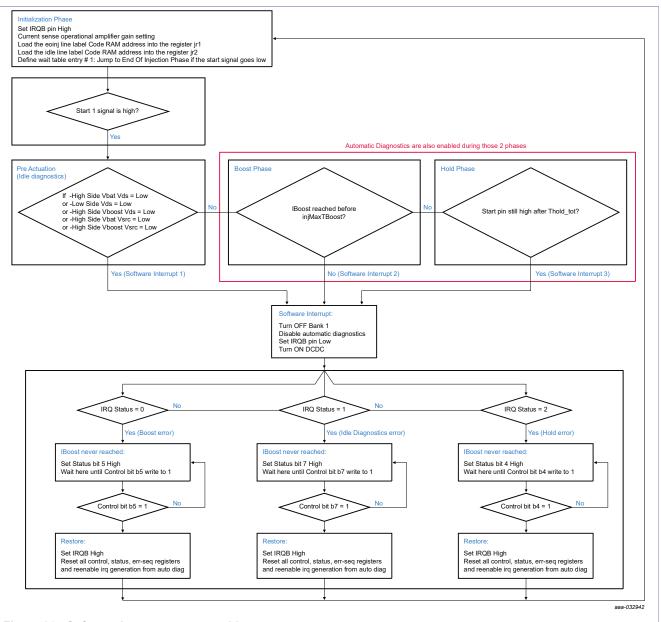

#### 6.1 Interrupt state machine

The following state diagrams describe how the MCU knows which interrupt occurred and which fault has been detected during both automatic and software interrupts.

For injectors actuation and DCDC state diagram, see AN4849.

# **NXP Semiconductors**

AN12336 PT2001 diagnostics

#### Figure 20. Software interrupt state machine

# **NXP Semiconductors**

AN12336 PT2001 diagnostics

# 6.2 General registers setup

Unless specified, use the register settings described in <u>AN4849</u>. Registers related to diagnostics and interrupts are described in the following sections.

## 6.2.1 Main configuration registers

| l able 2 | 20. Dri              | ver_coi         | ntig reg    | gister (l         | IX1C5)                    |                          |                       |                       |                 |                 |         |                        |                        |                        |                        |                |

|----------|----------------------|-----------------|-------------|-------------------|---------------------------|--------------------------|-----------------------|-----------------------|-----------------|-----------------|---------|------------------------|------------------------|------------------------|------------------------|----------------|

| Bit      | 15                   | 14              | 13          | 12                | 11                        | 10                       | 9                     | 8                     | 7               | 6               | 5       | 4                      | 3                      | 2                      | 1                      | 0              |

| Name     | hs5_<br>ls36_<br>ovr | vccp_<br>ext_en | ls7_<br>ovr | vboost_<br>mon_en | vboost_<br>disable_<br>en | over_<br>temp_<br>irq_en | drv_<br>en_irq_<br>en | vboost_<br>irq_<br>en | vcc5_<br>irq_en | vccp_<br>irq_en | iret_en | irq_<br>uc1_<br>ch2_en | irq_<br>uc0_<br>ch2_en | irq_<br>uc1_<br>ch1_en | irq_<br>uc0_<br>ch1_en | irq_<br>mcu_en |

| Value    | х                    | х               | х           | Х                 | х                         | х                        | х                     | х                     | 1               | х               | х       | х                      | х                      | х                      | х                      | 1              |

Table 20. Driver\_config register (0x1C5)

This register need not be set for the diagnostic on the external MOSFET, since it is handled in the microcode directly. If an error is detected, it forces IRQB low using the microcode. The return address (iret) is also determined in the microcode.

AN12336 Application note © NXP B.V. 2019. All rights reserved.

As an example, set vcc5\_irq\_en to '1', to force IRQB low in case of undervoltage on Vcc5. When the undervoltage is missing, the IRQB pin is kept low until the user writes a '1' in the uv\_vcc5 bit (Driver\_status register (0x1D2)).

#### 6.2.2 IO configuration registers

This register (one for each microcore) selects the feedback by which each microcore is enabled. Setting the bit to '1' generates an interrupt towards UcXChY, in case an error is detected on the HSx or LSx feedback.

Table 21. Fbk\_sens\_uc0ch1 register (0x180)

| Bit   | 15                   | 14                   | 13                   | 12                   | 11                   | 10                   | 9                     | 8                    | 7                     | 6                    | 5                     | 4                    | 3                     | 2                    | 1                     | 0                    |

|-------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|

| Name  | ls6_<br>vds_<br>sens | ls5_<br>vds_<br>sens | ls4_<br>vds_<br>sens | ls3_<br>vds_<br>sens | ls2_<br>vds_<br>sens | ls1_<br>vds_<br>sens | hs5_<br>vsrc_<br>sens | hs5_<br>vds_<br>sens | hs4_<br>vsrc_<br>sens | hs4_<br>vds_<br>sens | hs3_<br>vsrc_<br>sens | hs3_<br>vds_<br>sens | hs2_<br>vsrc_<br>sens | hs2_<br>vds_<br>sens | hs1_<br>vsrc_<br>sens | hs1_<br>vds_<br>sens |

| Value | 0                    | 1                    | 0                    | 0                    | 1                    | 1                    | 0                     | 0                    | 0                     | 0                    | 0                     | 0                    | 1                     | 1                    | 1                     | 1                    |

In this particular application (see the schematics in <u>FRDMPT2001EVM</u>), microcore 0 channel 1 controls HS1 as high-side V<sub>BAT</sub> and HS2 as high-side V<sub>BOOST</sub>, LS1 and LS2. An interrupt is generated if an error occurs on LS2 V<sub>DS</sub>, LS1 V<sub>DS</sub>, HS2 V<sub>DS</sub>, HS1 V<sub>DS</sub>, HS2 V<sub>SRC</sub>, and HS1 V<sub>SCR</sub> (see <u>Table 21</u>).

#### 6.2.2.1 PT2001 threshold settings

Each comparator threshold is set on four bits. The V<sub>DS</sub> thresholds for high-side predrivers are defined by registers 0x1AE and 0x1AF. The V<sub>SRC</sub> thresholds are defined by registers 0x1B0 and 0x1B1. The V<sub>DS</sub> thresholds for low-side predrivers are defined by registers 0x1B2 and 0x1B3.

As described in fault description, these thresholds must be set according to the external MOSFET and maximum current level used in the application. As with FRDMPT2001EVM, the R<sub>DS(on)</sub> MOSFET is approximately equal to 24 m $\Omega$  (worst case condition). The maximum current used in this application is 16.09 A, and overcurrent detection (using V<sub>DS</sub> monitoring) must be set at around 30 % higher than maximum current allowed (32 A).

#### Table 22. V<sub>DS</sub> and V<sub>SRC</sub> monitoring typical threshold selection

| hsx_vds/src_threshold(3:0) | Threshold voltage HS VDS / HS VSRC (V) |

|----------------------------|----------------------------------------|

| 0000                       | 0.00                                   |

| 1001                       | 0.10                                   |

| 1010                       | 0.20                                   |

| 1011                       | 0.30                                   |

| 1100                       | 0.40                                   |

| 0001                       | 0.50                                   |

| 0010                       | 1.0                                    |

| 0011                       | 1.5                                    |

| 0100                       | 2.0                                    |

| 0101                       | 2.5                                    |

| 0110                       | 3.0                                    |

| 0111                       | 3.5                                    |

AN12336 Application note

#### 6.2.2.1.1 High-side V<sub>DS</sub> threshold calculation

$V_{DS}$  threshold (HS) = Overcurrent x  $R_{DS(on)}$  = 32 A x 0.025  $\Omega$  = 0.8 V  $\rightarrow$  **1.0 V** threshold selected. In this case, overcurrent = 1.0 V/0.025  $\Omega$  = 40 A.

#### Table 23. Vds\_threshold\_hs Part1 (1AEh)

|       |    |          |     | · · · |    |        |        |   |   |        |        |   |   |        |        |   |

|-------|----|----------|-----|-------|----|--------|--------|---|---|--------|--------|---|---|--------|--------|---|

| Bit   | 15 | 14       | 13  | 12    | 11 | 10     | 9      | 8 | 7 | 6      | 5      | 4 | 3 | 2      | 1      | 0 |

| Name  |    | Vds_thr_ | Hs4 |       |    | Vds_th | nr_Hs3 |   |   | Vds_th | nr_Hs2 |   |   | Vds_th | nr_Hs1 |   |

| R/W   |    | R/W      |     |       |    | R/     | w      |   |   | R/     | W      |   |   | R/     | W      |   |

| Lock  |    | no       |     |       |    | n      | 0      |   |   | n      | 0      |   |   | n      | 0      |   |

| Value |    | 0000     |     |       |    | 00     | 00     |   |   | 00     | 00     |   |   | 00     | 00     |   |

#### Table 24. Vds\_threshold\_hs Part2 (1AFh)

| Bit   | 15 | 14 | 13 | 12 | 11 | 10        | 9      | 8      | 7 | 6 | 5 | 4 | 3 | 2  | 1  | 0 |

|-------|----|----|----|----|----|-----------|--------|--------|---|---|---|---|---|----|----|---|

| Name  |    |    |    |    |    |           | Vds_th | nr_Hs5 |   |   |   |   |   |    |    |   |

| R/W   |    |    |    |    |    |           |        | R/     | W |   |   |   |   |    |    |   |

| Lock  |    |    |    |    |    | _         |        |        |   |   |   |   |   | n  | 0  |   |

| Value |    |    |    |    | (  | 0000 0000 | 0000   |        |   |   |   |   |   | 00 | 00 |   |

#### 6.2.2.1.2 Low-side V<sub>DS</sub> threshold calculation

Low-side the  $V_{\text{DS}}$  monitoring is done between D\_LSx and GND, sense resistance must be included in the calculation.

$V_{DS}$  threshold (LS) = Overcurrent x ( $R_{DS(on)} + R_{SENSE}$ ) = 32 A x (0.025  $\Omega$  + 0.015  $\Omega$ ) = 1.28 V  $\rightarrow$  **1.0 V** threshold selected, in this case overcurrent = 1.0 V / 0.04  $\Omega$  = 25 A.

#### Table 25. Vds\_threshold\_ls Part1 (1B2h)

|       |    |          |     |    | ,  |        |        |   |   |        |        |   |   |       |        |   |

|-------|----|----------|-----|----|----|--------|--------|---|---|--------|--------|---|---|-------|--------|---|

| Bit   | 15 | 14       | 13  | 12 | 11 | 10     | 9      | 8 | 7 | 6      | 5      | 4 | 3 | 2     | 1      | 0 |

| Name  |    | Vds_thr_ | Ls4 |    |    | Vds_th | nr_Ls3 | - |   | Vds_th | nr_Ls2 |   |   | Vds_t | nr_Ls1 |   |

| R/W   |    | R/W      |     |    |    | R/     | W      |   |   | R/     | W      |   |   | R/    | W      |   |

| Lock  |    | no       |     |    |    | n      | 0      |   |   | n      | 0      |   |   | n     | 0      |   |

| Value |    | 0000     |     |    |    | 00     | 00     |   |   | 00     | 00     |   |   | 00    | 00     |   |

#### Table 26. Vds\_threshold\_ls Part2 (1B3h)

| Bit   | 15 | 14 | 13 | 12      | 11 | 10 | 9 | 8 | 7 | 6     | 5      | 4 | 3 | 2      | 1      | 0 |

|-------|----|----|----|---------|----|----|---|---|---|-------|--------|---|---|--------|--------|---|

| Name  |    |    |    | reserve | ed |    |   |   |   | Vds_t | nr_Ls6 |   |   | Vds_tl | hr_Ls5 |   |

| R/W   |    |    |    | _       |    |    |   |   |   | R     | w      |   |   | R      | /W     |   |

| Lock  |    |    |    | _       |    |    |   |   |   | r     | 0      |   |   | n      | 10     |   |

| Value |    |    |    | 0000 00 | 00 |    |   |   |   | 00    | 00     |   |   | 00     | 000    |   |

#### 6.2.2.1.3 High-side SRC threshold

$V_{SRC}$  is used mostly during idle phase to understand the type of fault present. It is better to keep the detection threshold far from the polarization condition. During actuation in this application, recirculation is done through a diode, keeping the voltage of the HS source below ground. In this case, any  $V_{SRC}$  voltage can be used, to prevent false diagnostics. In order to avoid detecting noise and to be far from the 3.8 V threshold, the PT2001  $V_{SRC}$  threshold is set to 1.0 V.

#### Table 27. Vsrc\_threshold\_hs Part1 (1B0h)

| Bit   | 15 | 14        | 13  | 12 | 11 | 10      | 9      | 8 | 7 | 6      | 5      | 4 | 3 | 2      | 1      | 0 |

|-------|----|-----------|-----|----|----|---------|--------|---|---|--------|--------|---|---|--------|--------|---|

| Name  |    | Vsrc_thr_ | Hs4 |    |    | Vsrc_tl | nr_Hs3 |   |   | Vsrc_t | hr_Hs2 |   |   | Vsrc_t | nr_Hs1 |   |

| R/W   |    | R/W       |     |    |    | R/      | W      |   |   | R/     | w      |   |   | R/     | W      |   |

| Lock  |    | no        |     |    |    | n       | 0      |   |   | n      | 0      |   |   | n      | 0      |   |

| Value |    | 0000      |     |    |    | 00      | 00     |   |   | 00     | 00     |   |   | 00     | 00     |   |

#### Table 28. Vsrc\_threshold\_hs Part2 (1B1h)

| Bit   | 15 | 14 | 13 | 12 | 11 | 10        | 9    | 8  | 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0 |

|-------|----|----|----|----|----|-----------|------|----|---|---|---|---|---|--------|--------|---|

| Name  |    |    |    |    |    | reserve   | d    |    |   |   |   |   |   | Vsrc_t | nr_Hs5 |   |

| R/W   |    |    |    |    |    |           |      | R/ | W |   |   |   |   |        |        |   |

| Lock  |    |    |    |    |    | _         |      |    |   |   |   |   |   | n      | 0      |   |

| Value |    |    |    |    | (  | 0000 0000 | 0000 |    |   |   |   |   |   | 00     | 00     |   |

#### 6.2.3 Channel 1 configuration registers

Unless specified, use the same settings specified in the AN4849.

#### Table 29. Ctrl\_reg\_uc0 control registers for the microcore 0 (0x101, 0x121)

| Bit   | 15 | 14 | 13 | 12          | 11         | 10 | 9 | 8 | 7 | 6 | 5 | 4        | 3        | 2 | 1 | 0 |

|-------|----|----|----|-------------|------------|----|---|---|---|---|---|----------|----------|---|---|---|

| Name  |    |    | c  | ontrol_regi | ster_share | d  |   |   |   |   |   | control_ | register |   |   |   |

| Value |    |    |    | XXXX        | xxxx       |    |   |   |   |   |   | 0000     | 0000     |   |   |   |

control\_register: control bits 4, 5, 6, and 7 are used to control the turn ON of the bank after a fault occurs

- B4: if START pin is still high after t<sub>HOLD\_TOT</sub> is reached (see <u>Section 7 "Application</u> source code")

- B5: if I<sub>BOOST</sub> is not reached before the specified time

- B6: if errors are detected during actuation (automatic diagnostics)

- B7: if errors are detected during pre-actuation phase (idle diagnostics)

Entry point for each microcode as specified, corresponds to the location in the CRAM where each microcontroller starts.

#### Table 30. Uc0\_entry\_point registers (0x10A, 0x12A)

| В  | it | 15 | 14 | 13   | 12   | 11 | 10 | 9 | 8 | 7 | 6 | 5          | 4         | 3 | 2 | 1 | 0 |

|----|----|----|----|------|------|----|----|---|---|---|---|------------|-----------|---|---|---|---|

| Na | me |    |    | rese | rved |    |    |   |   |   |   | entry_poin | t_address |   |   |   |   |

| Va | ue |    |    | 000  | 000  |    |    |   |   |   |   | 10011      | 0000      |   |   |   |   |

With the code provided, uc0 channel 1 starts line152 label *init0*, interrupt code should not be taken in account in the entry code.

AN12336 Application note

#### Table 31. Uc1\_entry\_point registers (0x10B, 0x12B)

| Bit   | 15 | 14 | 13   | 12   | 11 | 10 | 9 | 8 | 7 | 6 | 5          | 4         | 3 | 2 | 1 | 0 |

|-------|----|----|------|------|----|----|---|---|---|---|------------|-----------|---|---|---|---|

| Name  |    |    | rese | rved |    |    |   |   |   |   | entry_poin | t_address |   |   |   |   |

| Value |    |    | 000  | 000  |    |    |   |   |   |   | 00000      | 01000     |   |   |   |   |

With code provided, uc1 channel starts line 091 label init1.

It is required to specify the location in the CRAM, because the automatic interrupt is handled here.

#### Table 32. Diag\_routine\_addr registers (0x10C, 0x12C)

| Bit   | 15 | 14   | 13   | 12 | 11     | 10    | 9            | 8          | 7    | 6 | 5 | 4     | 3           | 2          | 1    | 0 |

|-------|----|------|------|----|--------|-------|--------------|------------|------|---|---|-------|-------------|------------|------|---|

| Name  |    | rese | rved |    |        | diagr | nosis_routir | ne_address | _uc1 |   |   | diagr | osis_routir | ne_address | _uc0 |   |

| Value |    | 00   | 00   |    | XXXXXX |       |              |            |      |   |   |       | 000         | 000        |      |   |

- diagnosis\_routine\_address\_uc0: automatic diagnostics are located at line 0 (label irq\_auto)

- diagnosis\_routine\_address\_uc1: not used in this example

The same settings on software interrupt are needed to specify the location in the CRAM where SW interrupts are handled.

#### Table 33. Sw\_interrupt\_routine\_addr registers (0x10E, 0x12E)

| Bit   | 15                                            | 14                                           | 13                                           | 12                                           | 11 | 10        | 9            | 8          | 7         | 6 | 5 | 4         | 3            | 2          | 1         | 0 |

|-------|-----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----|-----------|--------------|------------|-----------|---|---|-----------|--------------|------------|-----------|---|

| Name  | sw_irq_<br>falling_<br>edge_<br>start_<br>uc1 | sw_irq_<br>rising_<br>edge_<br>start_<br>uc1 | sw_irq_<br>falling_<br>edge<br>start_<br>uc0 | sw_irq_<br>rising_<br>edge_<br>start_<br>uc0 |    | software_ | _interrupt_r | outine_add | lress_uc1 |   |   | software_ | _interrupt_r | outine_add | lress_uc0 |   |

| Value | x                                             | x                                            | x                                            | х                                            |    |           | XXX          | XXX        |           |   |   |           | 000          | 111        |           |   |

- software\_interrupt\_routine\_address\_uc0: line 7 in the CRAM

- software interrupt routine address uc1: not used in this example

- sw irq rising edge start uc0: not used in this example

- sw\_irq\_falling\_edge start\_uc0: not used in this example

## 6.3 Diagnostics configuration registers

#### 6.3.1 LS1 and LS2 output register

#### 6.3.1.1 Filter time

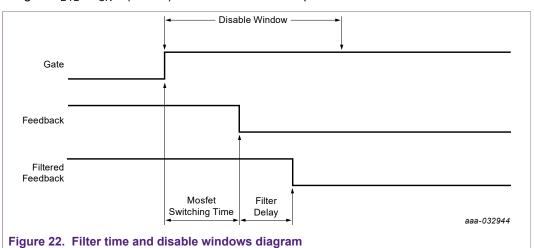

These registers define the automatic diagnostics filtering. Values depend on noise in the application and MOSFET switching time to get stable for reliable feedback when diagnostics start.

| Table S | 94. LSX | _ulay_ | comig           | regisi |        | 140, 07       | 145, 07 | (140, 0) | x 143, U | x 140, U | X 14F) |     |             |   |   |   |

|---------|---------|--------|-----------------|--------|--------|---------------|---------|----------|----------|----------|--------|-----|-------------|---|---|---|

| Bit     | 15      | 14     | 13              | 12     | 11     | 10            | 9       | 8        | 7        | 6        | 5      | 4   | 3           | 2 | 1 | 0 |

| Name    | rese    | rved   | filter_<br>type |        |        | filter_length |         |          |          |          |        | dis | sable_windo | w |   |   |

| Value   | 0       | C      | 0               |        | 111011 |               |         |          |          |          |        |     | 1011010     |   |   |   |

Table 34. Lsx\_diag\_config1 registers (0x140, 0x143, 0x146, 0x149, 0x14C, 0x14F)

• filter\_type: set to 0, in this case, means any different sample resets the filter counter

• filter\_length: the filtering time is:  $t_{FTN} = t_{CK} x (5 + 1) = 1/6$  MHz x 6 = 1 µs

AN12336 Application note © NXP B.V. 2019. All rights reserved.

disable\_window: this 7-bit parameter configures a time period during which any check on the LSx\_Vds\_feed signal is disabled after any change on the output\_command signal. t<sub>DTI</sub> = t<sub>CK</sub> x (14 + 4) = 1/6 MHz x 18 = 3.0 µs

#### 6.3.1.2 Error table

Using <u>Section 5 "Diagnostic descriptions"</u>, error tables can be easily generated.

#### Table 35. Lsx diag config2 registers (0x141, 0x144, 0x147, 0x14A, 0x14D, 0x150)

| Bit   | 15 | 14         | 13 | 12 | 11 | 10   | 9    | 8 | 7 | 6 | 5 | 4 | 3  | 2      | 1     | 0 |

|-------|----|------------|----|----|----|------|------|---|---|---|---|---|----|--------|-------|---|

| Name  |    |            |    | -  |    | rese | rved |   |   |   |   |   |    | error_ | table |   |

| Value |    | 0000000000 |    |    |    |      |      |   |   |   |   |   | 10 | 01     |       |   |

error\_table: this 4-bit parameter defines the logical value of an error signal, issued from the output and the related V<sub>DS</sub> feedback signal. This table defines the output of the coherency check between the driven output and the acquired feedback; a logic one value means there is no coherency in the check, and then an error signal towards the microcore should be generated.

#### Table 36. Error table for both low-sides

|                                                   | output_command = 0 (predriver switched OFF) | output_command = 1 (predriver switched ON) |

|---------------------------------------------------|---------------------------------------------|--------------------------------------------|

| lsx_vds_fbk = 0 (V <sub>DS</sub> below threshold) | error_table (0) = 1                         | error_table (2) = 0 (OK)                   |

| lsx_vds_fbk = 1 (V <sub>DS</sub> above threshold) | error_table (1) = 0 (OK)                    | error_table (3) = 1                        |

Normal mode in this application:

- Low-side is ON and the  $V_{\text{DS}}$  comparator should be low

- Low-side is OFF and the  $V_{\text{DS}}$  comparator should be high

#### 6.3.2 HS1/HS2 output register

#### 6.3.2.1 Filter time

Use the same filtering as the low-side, since the same MOSFET and slew rates are used for both.

| Bit   | 15    | 14  | 13              | 12 | 11 | 10       | 9     | 8 | 7 | 6 | 5 | 4   | 3         | 2 | 1 | 0 |

|-------|-------|-----|-----------------|----|----|----------|-------|---|---|---|---|-----|-----------|---|---|---|

| Name  | reser | ved | filter_<br>type |    |    | filter_l | ength |   |   |   |   | dis | able_wind | w |   |   |

| Value | 00    | )   | 0               |    |    | 111      | 011   |   |   |   |   |     | 1011010   |   |   |   |

#### Table 37. Hsx\_diag\_config\_1 registers (0x153, 0x156, 0x159, 0x15C, 0x15F)

- filter\_type: set to 0, in this case, means any different sample resets the filter counter

- filter\_length: the filtering time is:  $t_{FTN} = t_{CK} x (5 + 1) = 1/6$  MHz x 6 = 1 µs

- disable\_window: this 7-bit parameter configures a time period during which any check on the LSx\_Vds\_feed signal is disabled after any change on the output\_command signal. t<sub>DTL</sub> = t<sub>CK</sub> x (14 + 4) = 1/6 MHz x 18 =  $3.0 \mu$ s

#### 6.3.2.2 Error table

#### 6.3.2.2.1 HS1 (VBAT) error table

#### Table 38. Hsx\_diag\_config\_2 registers (0x154, 0x157, 0x115A, 0x15D, 0x160)

| Bit   | 15      | 14 | 13 | 12   | 11   | 10 | 9  | 8 | 7 | 6        | 5        | 4 | 3 | 2        | 1       | 0 |

|-------|---------|----|----|------|------|----|----|---|---|----------|----------|---|---|----------|---------|---|

| Name  |         |    |    | rese | rved |    |    |   |   | error_ta | able_src |   |   | error_ta | ble_vds |   |

| Value | 0000000 |    |    |      |      | 01 | 10 |   |   | 10       | 01       |   |   |          |         |   |

#### Table 39. Error table for high-side V<sub>DS</sub>

|                                                   | output_command = 0 (predriver switched OFF) | output_command = 1 (predriver switched ON) |

|---------------------------------------------------|---------------------------------------------|--------------------------------------------|

| hsx_vds_fbk = 0 (V <sub>DS</sub> below threshold) | error_table_vds (0) = 1                     | error_table_vds (2) = 0                    |

| hsx_vds_fbk= 1 (V <sub>DS</sub> above threshold)  | error_table_vds (1) = 0                     | error_table_vds (3) = 1                    |

Normal mode in this application:

- High-side is ON and the  $V_{DS}$  comparator should be low

- High-side is OFF and the  $V_{DS}$  comparator should be high

#### Table 40. Error table for high-side V<sub>SRC</sub>

|                                                    | output_command = 0 (predriver switched OFF) | output_command = 1 (predriver switched ON) |

|----------------------------------------------------|---------------------------------------------|--------------------------------------------|

| hsx_src_fbk = 0 (V <sub>SRC</sub> below threshold) | error_table_src (0) = 0                     | error_table_src (2) = 1                    |

| hsx_src_fbk = 1 (V <sub>SRC</sub> above threshold) | error_table_src (1) = 1                     | error_table_src (3) = 0                    |

Normal mode in this application:

- High-side is ON and the  $V_{\mbox{\scriptsize SRC}}$  comparator should be high

- High-side is OFF and the  $V_{\mbox{\scriptsize SRC}}$  comparator should be low

#### 6.3.2.2.2 HS2 (VBOOST) error table

#### Table 41. Hsx\_diag\_config\_2 registers (0x154, 0x157, 0x115A, 0x15D, 0x160)

| Bit   | 15 | 14      | 13 | 12   | 11   | 10 | 9  | 8  | 7 | 6        | 5        | 4  | 3 | 2        | 1       | 0 |

|-------|----|---------|----|------|------|----|----|----|---|----------|----------|----|---|----------|---------|---|

| Name  |    |         |    | rese | rved |    |    |    |   | error_ta | able_src |    |   | error_ta | ble_vds |   |

| Value |    | 0000000 |    |      |      |    | 01 | 00 |   |          | 10       | 01 |   |          |         |   |

|                                                   | output_command = 0 (predriver switched OFF) | output_command = 1 (predriver switched ON) |

|---------------------------------------------------|---------------------------------------------|--------------------------------------------|

| hsx_vds_fbk = 0 (V <sub>DS</sub> below threshold) | error_table_vds (0) = 1                     | error_table_vds (2) = 0                    |

| hsx_vds_fbk= 1 (V <sub>DS</sub> above threshold)  | error_table_vds (1) = 0                     | error_table_vds (3) = 1                    |

AN12336 Application note © NXP B.V. 2019. All rights reserved.

|                                                    | output_command = 0 (predriver switched OFF) | output_command = 1 (predriver switched ON) |

|----------------------------------------------------|---------------------------------------------|--------------------------------------------|

| hsx_src_fbk = 0 (V <sub>SRC</sub> below threshold) | error_table_src (0) = 0                     | error_table_src (2) = 1                    |

| hsx_src_fbk = 1 (V <sub>SRC</sub> above threshold) | error_table_src (1) = 0                     | error_table_src (3) = 0                    |

$V_{BOOST}$  high-side source detection is different in this application from  $V_{BAT}$  since S\_HSVbat and S\_HS\_VBoost are shorted together through a diode. If  $V_{BAT}$  high-side is ON, voltage on the  $V_{BOOST}$  source high-side is equal to  $V_{PWR}$  - diode. Consequently, the PT2001 should not detect an error on high-side  $V_{BOOST}$  if command = 0 and source feedback = 1.

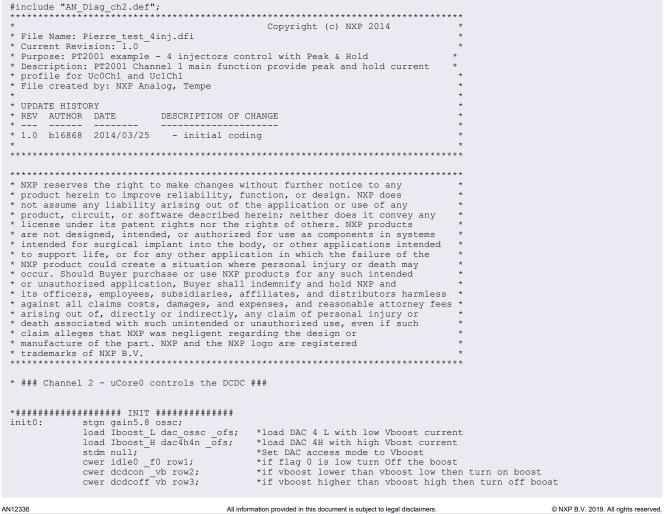

# 7 Application source code

The following microcode can be directly downloaded from the NXP web site (see <u>FRDMPT2001EVM</u>). Using the IDE and SPIGEN, the microcode can be downloaded to the PT2001.

#### 7.1 Injection banks management source code

```

#include "AN_Diag_ch1.def";

*****

Copyright (c) NXP 2016 *

* File Name: Pierre_test_4inj.dfi

Current Revision: 1.0

Purpose: PT2001 example - 1 Bank diagnostic

Description: PT2001 Channel 1 main function provide peak and hold current

profile for Uc0Chl and use idle and automatic diagnostics

Uc1CH1 provide peak and hold without diagnostics

* REV AUTHOR DATE

DESCRIPTION OF CHANGE

* 1.0 b16868 2014/03/25 - initial coding

* NXP reserves the right to make changes without further notice to any

product herein to improve reliability, function, or design. NXP does

not assume any liability arising out of the application or use of any

product, circuit, or software described herein; neither does it convey any

license under its patent rights nor the rights of others. NXP products

*

are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended

to support life, or for any other application in which the failure of the NXP product could create a situation where personal injury or death may

NAP product could create a situation where personal injury or death may

occur. Should Buyer purchase or use NXP products for any such intended

or unauthorized application, Buyer shall indemnify and hold NXP and

its officers, employees, subsidiaries, affiliates, and distributors harmless

against all claims costs, damages, and expenses, and reasonable attorney fees

* arising out of, directly or indirectly, any claim of personal injury or

* death associated with such unintended or unauthorized use, even if such

* claim alleges that NXP was negligent regarding the design or

* manufacture of the part. NXP and the NXP logo are registered

trademarks of NXP B.V.

* * * * * * * * * * * * * * * * * * *

* ### Channel 1 - uCore0 controls the injectors 1 ###

* Constant definition

#define HSBoost_B1 hs2;

#define HSBAT_B1 hs1;

#define LS1_B1 ls1;

#define LS2 B1 ls2;

* This bit must be set to 1 if the Iboost current is never reached during the boost phase #define BoostErrorBit b5;

* This bit must be set to 1 the sequencer is currently executing the Automatic interrupt routine

#define AutoIrqBit b6;

This bit must be set to 1 the sequencer is currently executing the Idle Diag interrupt routine

#define IdleIrqBit b7;

This bit must be set to 1 if start pin stays high longer than 10ms

#define HoldErrorBit b4;

AN12336

```

#### **NXP Semiconductors**

PT2001 diagnostics

AN12336

\* This flag is sent to the DCDC sequencer. It must be active for the whole period the boost voltage is used \* When the boost voltage is used, the DCDC must be deactivated flag = 0 => boost voltage is used, DCDC must be deactivated flag = 1 => boost voltage not used, DCDC can be active #define BstFlag b0; \* During the interrupt routine, the sequencer wait for this bit to be set to '1' before resuming execution of application code #define AutoDiagResetBit b6; During the interrupt routine, the sequencer wait for this bit to be set to '1' before resuming execution of application code #define IdleDiagResetBit b7; \* During the interrupt routine, the sequencer wait for this bit to be set to '1' before resuming execution of application code #define BoostResetBit b5; \* During the interrupt routine, the sequencer wait for this bit to be set to '1' before resuming execution of application code #define HoldResetBit b4; #define IRQ\_stat\_Reg r0; \*\*\*\*\* \* AUTOMATIC INTERUPT \* stos off off off; \* Disable drivers irg auto: \* Disable automatic diagnostic \* Set the low IRQB pin endiaga diagoff; stirq low; stf high BstFlag; \* Set flag0 high DCDC active stsrb high AutoIrqBit; \* Set status register bit 5 when automatic diagnosis interrupt trig auto\_waitEnable:jcrr auto\_waitEnable AutoDiagResetBit low; \* the sequencer is stuck here until the bit of the control register is set to '1' b6 \* Load restore to jr1 to do a jump far ldir1 restore; \* Jump to restore impf ir1; \* SOFTWARE INTERUPT irq1\_sw: stos off off off; \* Disable drivers endiaga diagoff; \* Disable automatic diagnostic \* Set low the IRQB pin \* Set flag0 high to release the DC-DC converter idle stirq low; stf high BstFlag; mode \* Check which Sw interrupt occured BoostErr 0 or Idle Diag Fail 1 \* copy the irq status registers to a temp ALU reg \* This register contains also the sw irq ID \* load MSB in ir reg: 0x0C00 in immediate register, to use as mask cp irq IRQ stat Reg; ldirh OCh rst; for irq status

and IRQ\_stat\_Reg; \* extract the sw id from irq status register (bits 11-10) \* if the sw id is 0 => Iboost never reached => go to Boost\_waitEN \* Else => error detected in idle diag=> go to next line => seq stuck until micro jarr Boost\_waitEN all0; write 1 in control register b8 ldirh 08h rst: \* load MSB in ir reg: 0x0800 in immediate register, to use as mask for irq status and IRQ\_stat\_Reg; jarr sw\_waitEnable all0; diagnostics fails \* Else => Hold error => go to next line => idle diag fail Hold\_waitEN: stsrb high HoldErrorBit;  $\star$  Start pin stays higher longer than 10ms jcrr Hold\_waitEN HoldResetBit low; \* Wait here until control bit register is write to 1 jmpr restore; \* IDle diag fail we set status b8 high to let user know sw waitEnable: stsrb high IdleIrgBit; which error occured jcrr sw\_waitEnable IdleDiagResetBit low; \* Wait here until control bit register is write to 1 jmpr restore; Boost waitEN: stsrb high BoostErrorBit; \* Iboost never reached, let user know by setting status register bit b5 jcrr Boost waitEN BoostResetBit low; \* Wait here until control bit register is write to 1 restore: stirq high; \* Set high IROB pin \* Reset a) control registers \* b) status regsiter rstreg all; \* c) err\_seq register (status of automatic diagnosis

AN12336

© NXP B.V. 2019. All rights reserved.

AN12336

#### PT2001 diagnostics

\* d) re-enables irg generation from automatic diagnosis iret restart rst; \* Clear interrupt queue and restart from init phase \*\*\*\*\* INIT PHASE stirq high; \* Set high IRQB pin \* Set gain amplifier for current feedback 1 init0: stgn gain8.68 sssc; \* Load end of injector in jrl to use jump far ldjr1 eoinj0; ldjr2 idle0; \* Load idle0 in jr1 to use jump far \* If any start goes low go to eoi cwef jr1 start row1; \* IDLE PHASE idle0: joslr inje1 start1; joslr inje2 start2; \* Start injector 1 if start1 goes high \* Start injector 2 if start2 goes high jmpf jr1; \* Jump to end of injection \* SHORTCUT DEFINITION dfsct HSBAT\_B1 LS1\_B1 HSBoost\_B1; \* Shortcut1 = HSVBAT, Shortcut2= LS2\_B1, Shortcut3= inje1: HSBOOST \* use current feedback1

\* Jump to idle\_diag0 dfcsct dac1; jmpr idle\_diag0; dfsct HSBAT B1 LS2 B1 HSBoost B1; \* Shortcut1 = HSVBAT, Shortcut2= LS2 B1, Shortcut3= inje2: HSBOOST dfcsct dac1; \* use current feedback1 jmpr idle\_diag0; \* Jump to idle\_diag0 (useless here) \*\*\*\*\* \* PRE-ACTUATION DIAG PHASE \*\*\*\*\* idle diag0: bias all on; \* Enable all biasing structures, kept ON even during actuation jocr idle\_diag\_fail0 \_sclv; jocr idle\_diag\_fail0 \_sc2v; jocr idle\_diag\_fail0 \_sc3v; jocr idle\_diag\_fail0 \_sc1s; jocr idle\_diag\_fail0 \_sc3s; \* Error detected if Vds of shortcut1 (HS) is low \* Error detected if Vds of shortcut2 (LS) is low \* Error detected if Vds of shortcut3 (Boost) is low \* Error detected if Vsrc of shortcutl (HS) is low \* Error detected if Vsrc of shortcutl (HS) is low \* Jump to actuation phase if no failure detected in idle jmpr boost0; phase idle\_diag\_fail0:reqi 1;

phase HSBat error \* Go to software subroutine is fault detected in idle \* BOOST PHASE \* boost0: ldcd rst \_ofs keep keep injMaxTBoost c3; \* Start Boost Counter in case Iboost never reached load Iboost dac\_sssc \_ofs; \* Load Boost current threshold load Iboost dac\_sssc\_ofs; cwer peak0 curl row2; cwer boost\_err0 tc3 row5; \* Define Wait Table Iboost is reached and jump to peak phase

\* Define Wait Table if actuation longer than injMaxGuard go eoini (added from AN4849) stf low BstFlag; \* Turn OFF the boost during this phase \* Vbat high-side On, Vboost HS On et LS1/2 ON, need to turn stos on on on; HS1 also to avoid diag failure \* Enable auto diag endiags on on on on; wait row125; \* Wait start goes low or Iboost reached or InjMaxTBoost reached boost\_err0: reqi 0; \* Go to software subroutine is fault detected in Boost phase, did not reach Iboost on time (added from AN4849) PEAK PHASE \*\*\*\*\*\* ldcd rst \_ofs keep keep Tpeak\_tot c1; \* Start Tpeak tot counter stf high BstFlag; \* Turn Boost back on peak0: stf high BstFlag; load Ipeak dac\_sssc \_ofs; cwer bypass0 tc1 row2; \* Load the peak current threshold in the current DAC \* Define Wait: Jump to bypass phase when tcl reaches end of count \* Define Wait: Jump to peak\_on when tc2 reaches end of count \* Define Wait: Jump to peak\_off when current is over cwer peak\_on0 tc2 row3; cwer peak off0 ocur row4; threshold peak on0: stos on on off; \* Vbat On LS On, if needed Boost HS can stay ON during this phase wait row124; peak\_off0: ldcd rst ofs keep keep Tpeak\_off c2; \* Load in the counter 2 the length of the peak\_off phase AN12336 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2019. All rights reserved.

AN12336 PT2001 diagnostics

| stos off o                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                        |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wait row12                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | * turn OFF HSvbat keep LS ON                                                                                                                                                                           |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ****                                                                                                                                                                                                   |