PT2001 programming guide and instruction set Rev. 3.0 — 29 April 2019

**User guide**

# 1 Introduction

This programming guide relates to the PT2001 Programmable Solenoid Controller. Refer to the individual device data sheet for feature information. The PT2001 programming guide describes the microcore programming model, instruction set, data types used, and basic memory organization. Also included in the guide is an example of microcode used in the FRDMPT2001EVM using most of the instructions described herein. The programming of the microcores has to be done using the PT2001 IDE, which is available at <a href="https://www.nxp.com">https://www.nxp.com</a>.

# 2 Microcore programming description

## 2.1 CRAM addressing mode

All the jump instructions have two possible outcomes: if a specific condition (if any) is true, then the code flow continues at a destination specified by a parameter, otherwise it continues to the next code line. In the same way, when a wait entry is configured, a parameter specifies the destination.

The instruction set of PT2001 allows only two addressing modes to express the destination parameter for the CRAM:

- **Relative address** (relative): The relative address parameter is represented by 5 bits. The physical address of the destination is obtained by adding the relative address to the physical address of the instruction that uses the parameter (that is the value of the uprogram counter when the instruction is executed). The relative address must be considered as two's complement represented and must be extended on 10 bit before the addition. By using relative addresses it is possible to range from "current\_address 16" to "current\_address + 15".

- Indirect address (far): It is possible to jump to the CRAM address contained into one of two jump\_registers (jr1 or jr2). These registers can be loaded with a dedicated instruction and simply referred to in the wait or jump instructions. Refer to <u>ldjr1</u> and <u>ldjr2</u> in <u>Section 3.2 "Instruction set"</u>.

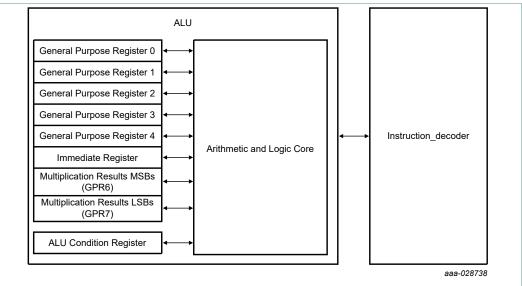

## 2.2 Arithmetic logic unit

The microcore contains a simple Arithmetic Logic Unit (ALU). The ALU has an 8-word internal register file connected to the internal bus. The ALU can perform the following operations:

- Addition and subtraction. These operations are completed in a single ck clock cycle.

- **Multiplication.** This operation is completed in up to 32 ck clock cycles. The result is available as a 32-bit number, and is always in the registers GPR6 (MSBs) and GPR7 (LSBs).

### PT2001 programming guide and instruction set

- **Shift operations.** The operand is shifted one position (left or right) each ck clock cycle, so it requires from 1 to 16 ck clock cycles to execute. The shift operations always consume the operand. It is also possible to shift an operand by eight positions (left or right) or to swap the eight MSBs with the eight LSBs in one ck clock cycle.

- Logic operation. It is possible to operate a bitwise logical operation (and, not, or, xor) between an operand and a mask. It is also possible to bitwise invert an operand. All these operations are completed in a single ck clock cycle. These operations always consume the operand.

**C2 conversions.** It is possible to convert data from an unsigned representation to two's complement and vice versa. These operations are completed in a single ck clock cycle.

### Figure 1. ALU block diagram

These operations consume the operand. While the ALU is busy performing an operation, request of other operations is impossible. In such cases, the request is ignored by the ALU.

The ALU instructions are:

- Addition (add), addition with immediate (addi)

- Subtraction (sub), subtraction with immediate (subi)

- Multiplication (mul), multiplication with immediate (muli)

- Logical operation (and, not, or, xor)

- Conversion from positive to two's complement (toc2) and from two's complement to positive (toint)

- Shift operation (sh32r, sh32l, shl, shr, shls, shrs), shift operation with immediate (sh32ri, sh32li, shli, shri, shlsi, shrsi), and byte manipulation shift (shl8, shr8, swap)

- ALU configuration (stal)

Some ALU instructions are multicycle (mul, muli and possibly sh32r, sh32l, shl, shr, shls, shrs, sh32ri, sh32li, shli, shri, shlsi, shrsi, depending on how many shift positions are required). While a multicycle operation is in progress, all ALU instructions are ignored, except for the stal instruction.

During this time any operations which try to modify the ALU registers (GPR0-7, arith\_reg) are ignored (ldirl, ldirh and possibly cp, load if their destination address is one of the ALU registers). Instructions which try to read the ALU registers are successful (possibly cp

### PT2001 programming guide and instruction set

and store). It is possible to transfer constant values to the ALU immediate register using the ldirl and ldirh instructions.

When a multicycle instruction is required, it is recommended to wait until the operation is finished (ex: cwer Dest opd row1) before going to the next instruction. The operation completion can be checked by reading back the bit OP\_DONE of the Arithmetic Condition Register (arith\_reg).

## 2.2.1 Arithmetic condition register

The 16-bit register contain the status of the ALU concerning the last requested operation.

| Bit     | Name           | Description                            |

|---------|----------------|----------------------------------------|

| 15      | SHIFT_OUT      | Shifted out bit                        |

| 14      | CONV_SIGN      | Last conversion sign                   |

| 13      | CARRY          | Carryover bit                          |

| 12 to 1 | ARITH_LOGIC    | Arithmetic logic                       |

| 10      | MASK_MIN       | Mask result 0000h                      |

| 9       | MASK_MAX       | Mask result FFFFh                      |

| 8       | MUL_SHIFT_OVR  | Multiplication shift overflow          |

| 7       | MUL_SHIFT_LOSS | Multiplication shift precision loss    |

| 6       | RES_ZERO       | Addition or subtraction result is zero |

| 5       | RES_SIGN       | Addition or subtraction sign result    |

| 4       | UNSIGNED_UND   | Unsigned underflow                     |

| 3       | UNSIGNED_OVR   | Unsigned overflow                      |

| 2       | SIGNED_UND     | Signed underflow                       |

| 1       | SIGNED_OVR     | Signed overflow                        |

| 0       | OP_DONE        | Operation complete                     |

Table 1. Arithmetic condition register

• SHIFT\_OUT is the last bit shifted out (either left or right) from a shift operation.

• CONV\_SIGN is the product of all signs removed by toint instruction. This bit can be reset by performing a toint conversion with an rst parameter.

• CARRY is the carry produced by the last addition or subtraction operation performed.

- ARITH\_LOGIC is a parameter used for addition and subtraction operations. It has four possible values:

- "00" or "10": no limitation is imposed on addition or subtraction. In case of an overflow, the result should be represented by 17 bits, but only the 16 LSBs of this result are put in the target register. In case of an underflow, the result put in the target register is "65536 the correct result", which can always be represented on 16 bits.

- "01": the result of addition or subtraction are saturated between the maximum possible value (if overflow) or the minimum possible value (if underflow). The numbers are considered to be two's complement representation, so they are saturated between 8000h (-32768) and 7FFFh (+32767).

- "11": the result of addition or subtraction are saturated between the maximum possible value (if overflow) or the minimum possible value (if underflow). The numbers are

## PT2001 programming guide and instruction set

considered to be unsigned, so they are saturated between FFFFh (65535) and 0000h (0).

- MASK\_MAX bit is set if the result of the last mask operation is FFFFh.

- MASK\_MIN bit is set if the result of the last mask operation is 0000h.

- MUL\_SHIFT\_OVR is set to 0 if the 16 MSBs of the last multiplication or 32-bit shift result are all 0, otherwise it is 1.

- MUL\_SHIFT\_LOSS is set to 0 if the 16 LSBs of the last multiplication or 32-bit shift result are all 0, otherwise it is 1.

- RES\_ZERO is set if the result of the last addition or subtraction is zero.

- RES\_SIGN is set if the result of the last addition or subtraction is negative.

- UNSIGNED\_UND is set if the last addition or subtraction produced underflow, considering the operands as unsigned numbers.

- SIGNED\_UND is set if the last addition or subtraction produced underflow, considering the operands as two's complement numbers.

- UNSIGNED\_OVR is set if the last addition or subtraction produced overflow, considering the operands as unsigned numbers.

- SIGNED\_OVR is set if the last addition or subtraction produced overflow, considering the operands as two's complement numbers.

The OP\_DONE can be set by the ALU, and the Instruction\_decoder can only read it. This bit is set to 0 when a multicycle operation is in progress, otherwise is set to 1. If an ALU operation is issued when another operation is in progress (that is when the OP\_DONE is set to 0), the request is ignored.

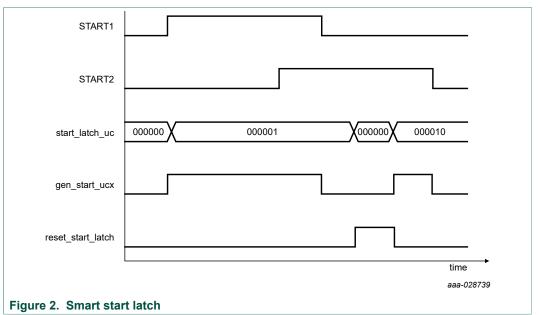

## 2.3 Start management

The start management block is designed to provide an anti-glitch functionality in order to reject glitches on the input start signal and also to provide the gen\_start\_uc0, gen\_start\_uc1, start\_latch\_uc0 and start\_latch\_uc1 signals. The main purpose of this block is to generate the internal gen\_start signals feeding the microcores starting from the startx pins. Each microcore can be sensitive to the 6 startx pins according to the sensitivity map defined in the register start\_config\_reg (104h, 124h).

This block also provides the start\_latch\_ucx signals; these 8-bit signals (1 for each microcore) are used by the corresponding microcore to check which startx pin was active when the currently ongoing actuation began. In this way each microcore can be configured to be sensitive for up to all the 6 startx pins. While the actuation is ongoing, it also has the ability to check the level of the startx pins in two different modes that can be selected. The gen\_start\_ucx and start\_latch\_ucx can be generated according to two different strategies. The strategies for the two signals can be separately selected in the start\_config\_reg (104h, 124h).

Transparent mode: The gen\_start\_ucx is high if at least one of the starx signals is high for which the corresponding microcore is sensitive (refer to register start\_config\_reg (104h, 124h)). The start\_latch\_ucx signal is a living copy of the 6 startx pins for which the channel can be sensitive.

Smart Latch mode: When a startx pin (to which the microcore is sensitive) goes high and the start\_latch\_ucx is "00000000", the gen\_start\_ucx is set and the current startx pin status is latched in the start\_latch\_ucx register. If a rising edge is detected on any other startx pin, it is ignored. The gen\_start\_ucx signal goes to 0 only when the startx pin initially latched goes low. The start\_latch\_ucx register is reset only by the microcode (and this is done usually when the actuation currently ongoing is stopped by the gen\_start\_ucx

### PT2001 programming guide and instruction set

falling edge). The gen\_start\_ucx signal does not go high, until the start\_latch\_ucx register has been reset.

The gen\_start\_ucx signals generated by this anti-glitch circuit are then also provided as an input to the corresponding microcores. If Smart Latch mode is enabled, no start edge is latched before the channel is locked by the flash enable bit.

## 2.4 Microprogram counter block

This block contains two registers: the microprogram counter (uPC) and the auxiliary register.

## 2.4.1 MicroPC

This is a 10-bit counter used to address the Code RAM containing the microprogram.

After the Code RAM is locked, this counter is loaded with an entry point selected through a SPI register (refer to the Uc0\_entry\_point (10Ah and 12Ah) and the Uc1\_entry\_point (10Bh and 12Bh) sections), which is the address of the first active instruction.

If an interrupt is requested, the uPC counter is moved to the appropriate interrupt routine register, as programmed in the parameter registers (refer to Diag\_routine\_addr (10Ch and 12Ch) and the Driver\_disabled\_routine\_addr (10Dh, and 12Dh) and the Sw\_interrupt\_routine\_addr (10Eh and 12Eh) sections). Only one level of interrupt is supported.

Before entering an interrupt routine, the interrupt status register is latched (refer to the Uc0\_irq\_status (10Fh, and 12Fh)). When an iret (interrupt return) instruction is executed, the interrupt status register is cleared and the uPC counter can be restored to the original address.

The instruction\_decoder block directly controls the uPC in order to allow an efficient management of:

- Direct jumps

- Conditional jumps

© NXP B.V. 2019. All rights reserved.

### PT2001 programming guide and instruction set

- · Subroutine execution

- · Wait states

### 2.4.2 Auxiliary register

This 10-bit register is used to manage the one-level subroutine return or as an auxiliary memory element.

Any time the system executes a "jump to subroutine" instruction, the uPC is automatically stored in the auxiliary register before jumping to the subroutine start address. When the subroutine execution ends, the incremented auxiliary register content is transferred back to the uPC.

## 2.5 Wait instructions

The PT2001 is an event/response machine. An event occurs and then code executes, the wait instructions are the key to this behavior. The core waits at a 'wait' instruction for an event to occur.

These pending events are configured as rows in a six-row wait table. Before the wait instruction is issued, the wait table has to be configured with the <u>cwef</u> and <u>cwer</u> instructions to obtain the desired behavior. One instruction is required for each wait entry to be configured.

Although there are many possible event sources which can be configured inside the six row wait table:

- terminal\_counts: any of the four terminal count (tc1, tc2, tc3, and tc4) signals can be checked to detect if any of the four counters has reached its end-of-count position.

- Flags: checks the value (both polarities) of one of the 16 flag signals available.

- Shortcut feedback: the voltage feedback (both polarities) related to the three shortcut outputs.

- gen\_start: checks the value (both polarities) of the filtered chx\_start input signal to define when to start and finish an actuation.

- current\_feedback: the value (both polarities) of the six current feedbacks.

- own\_current\_feedback: the value (both polarities) of the own current feedbacks. This

feedback can be different for each microcore and can be changed with the microcode

instruction dfcsct. <u>Table 2 "Current feedback assignment"</u> shows the configuration after

reset.

| Microcore     | Own current feedback (reset value) |  |

|---------------|------------------------------------|--|

| Uc0,channel 1 | current feedback 1                 |  |

| Uc1,channel 1 | current feedback 2                 |  |

| Uc0,channel 2 | current feedback 3                 |  |

| Uc1,channel 2 | current feedback 4                 |  |

#### Table 2. Current feedback assignment

• vboost: the output (both polarities) of the comparator that measures the boost voltage.

op\_done: check if a previously issued ALU operation is still in progress or it is completed. This is mandatory for multiple cycle instructions (like mul, muli and possibly sh32r, sh32l, shl, shr, shls, shrs, sh32ri, sh32li, shli, shri, shlsi, shrsi, depending on how many shift positions are required)

### PT2001 programming guide and instruction set

### Table 3. Wait instructions

| <u>cwef</u> | Create wait table entry far      |

|-------------|----------------------------------|

| <u>cwer</u> | Create wait table entry relative |

| <u>wait</u> | Wait until condition satisfied   |

## 2.6 Subroutine instructions

This section covers the instructions that support calling and returning from subroutines. As explained in the CRAM addressing mode, the jump to subroutine can be relative if the destination address is in a range from "current\_address - 16" to "current\_address +15". If not, instruction jump far to subroutine needs to be used. When a subroutine instruction is set, the program counter (pc) is saved in the auxiliary register 'aux'. The rfs instruction "return from subroutine" causes the program counter to jump back to the main program.

### Table 4. Subroutine instructions

| j <u>srf</u> | Jump far to subroutine      |

|--------------|-----------------------------|

| <u>jtsr</u>  | Jump relative to subroutine |

| <u>rfs</u>   | Return from subroutine      |

## 2.7 Program flow (jump, Ldjr) instructions

Conditions to be checked by the jump instructions are the same as the wait instruction with the addition of the following inputs:

- ctrl\_reg: checks the value (both polarities) of one of the 16 control bits available in the ctrl\_reg register (see register 101h, 102h, 121h,122h).

- status\_bits: checks the value (both polarities) of one of the 16 control bits available in the Status\_bits register (see register 105h, 106h, 125h, 126h).

- voltage feedback: the voltage feedback (both polarities) related to all the outputs.

- start\_latch: checks the value of the six bit start\_latch.

- arithmetic\_register: checks the value (high polarity only) of one of the bits of the ALU arithmetic register. See <u>Section 2.2 "Arithmetic logic unit"</u>.

- microcore\_id: check if the microcore currently executing is uc0 or uc1

Same as the wait table, it is possible to jump far or jump relative. The following instructions need to be used to define the destination address when a jump far is required.

#### Table 5. Load jump registers instructions

| ldjr1        | Load jump register 1 |

|--------------|----------------------|

| <u>ldjr2</u> | Load jump register 2 |

Table 6 defines the list of different jump instructions which are triggered.

#### Table 6. Jump instructions

| <u>jarf</u> | Jump far on arithmetic condition            |  |

|-------------|---------------------------------------------|--|

| <u>jarr</u> | Jump relative on arithmetic condition       |  |

| <u>jcrf</u> | Jump far on control register condition      |  |

| <u>jcrr</u> | Jump relative on control register condition |  |

## PT2001 programming guide and instruction set

| <u>jfbkf</u> | Jump far on feedback condition                 |

|--------------|------------------------------------------------|

| <u>jfbkr</u> | Jump relative on feedback condition            |

| jmpf         | Unconditional jump far                         |

| jmpr         | Unconditional jump relative                    |

| <u>jocf</u>  | Jump far on condition                          |

| <u>jocr</u>  | Jump relative on condition                     |

| <u>joidf</u> | Jump far on microcore condition                |

| <u>joidr</u> | Jump relative on microcore condition           |

| <u>joslf</u> | Jump far on start condition                    |

| <u>joslr</u> | Jump relative on start condition               |

| <u>jsrf</u>  | Jump far on status register bit condition      |

| <u>jsrr</u>  | Jump relative on status register bit condition |

| <u>jtsf</u>  | Jump far to subroutine                         |

| <u>jtsr</u>  | Jump relative to subroutine                    |

## 2.8 DataRAM access instructions

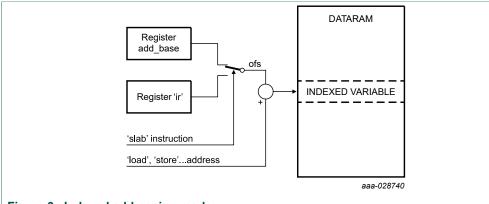

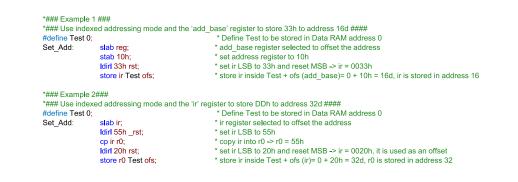

The Data RAM access instructions are used to load and store data memory. These instructions also set the access mode which can be set to either 'Immediate' (\_ofs parameter to be used) mode or 'Indexed' mode using the <u>slab</u> instruction. 'Indexed' mode is when an offset from the Base Address register is applied to the access's address (ofs parameter to be used). It is possible to modify the value of add\_base with the <u>stab</u> instruction.

### Figure 3. Indexed addressing mode

The three basic operations are:

- **Copy**. This instruction copies the value of one of the internal registers to another. The value of addr\_base is neglected.

- Load. This instruction copies the value of a Data RAM element into one of the internal registers. A boolean parameter specifies if addr\_base must be considered while addressing the Data RAM only.

- **Store**. This instruction copies the value of one of the internal registers to a Data RAM element. A boolean parameter specifies if addr\_base must be considered while addressing the Data RAM only.

## PT2001 programming guide and instruction set

| Table 7. DRAM access instructions | Table 7. | DRAM | access | instructions |

|-----------------------------------|----------|------|--------|--------------|

|-----------------------------------|----------|------|--------|--------------|

| <u>cp</u>    | Copy source register data to destination register |

|--------------|---------------------------------------------------|

| <u>ldca</u>  | Load counter from ALU register and set outputs    |

| Idcd         | Load counter from Data RAM and set outputs        |

| <u>ldirh</u> | Load 8-MSB ir register                            |

| Idirl        | Load 8-LSB ir register                            |

| load         | Load data from Data RAM to register               |

| <u>slab</u>  | Select Data RAM address base                      |

| <u>stab</u>  | Set Data RAM address base                         |

| <u>stdm</u>  | Set Data RAM read mode                            |

| store        | Store register data in Data RAM                   |

|              |                                                   |

## 2.9 Arithmetic instructions

The Arithmetic Logic Unit (ALU) does math calculations and bitwise operations. The immediate register (ir) is used for most instructions. This register can be loaded using the <u>Idrh</u> and <u>Idirl</u> instructions.

| Table 8. | Math | instructions |  |

|----------|------|--------------|--|

|----------|------|--------------|--|

|              | Instructions                                                                                              |

|--------------|-----------------------------------------------------------------------------------------------------------|

| add          | Add two ALU registers and place the result in one of the ALU registers                                    |

| addi         | Add an ALU register to the value in the immediate register and place the result in an ALU register        |

| <u>mul</u>   | Multiply two ALU registers and place the result in reg32                                                  |

| muli         | Multiply an ALU register with the value in the immediate register and place the result in reg32           |

| <u>stal</u>  | Set arithmetic logic mode                                                                                 |

| <u>sub</u>   | Subtract two ALU registers and place the result in one of the ALU registers                               |

| <u>subi</u>  | Subtract the value in the immediate register from an ALU register and place the result in an ALU register |

| <u>swap</u>  | Swap bytes inside ALU register                                                                            |

| <u>toc2</u>  | Convert an integer in an ALU register to 2's compliment format                                            |

| <u>toint</u> | Convert the two's complement value contained in an ALU register to integer format                         |

|              |                                                                                                           |

### Table 9. Bitwise instructions

| and       | AND an ALU register with the value in the immediate register and place the result in the ALU register |

|-----------|-------------------------------------------------------------------------------------------------------|

| not       | Invert ALU register bits                                                                              |

| <u>or</u> | OR an ALU register with the value in the immediate register and place the result in the ALU register  |

| xor       | XOR an ALU register with the value in the immediate register and place the result in the ALU register |

### PT2001 programming guide and instruction set

## 2.10 Shift instructions

This section covers the shift instructions. Shifts include 'shift left' and 'shift right', 'shift by register' and 'shift immediate', 'normal shift' and 'signed shift' in which the most significant bit does not change, and 32-bit shifts in which the 'mh' and 'ml' registers are treated as a single 32-bit register in which the 'mh' register's lsb connects with the 'ml's registers msb.

Shifts take one instruction cycle per shifted bit and the 'arith\_reg' register's 'OD' bit can be tested to determine when the shift is completed. So an 11-bit shift would normally take 11 clock cycles to execute. However, there is a special 8-bit shift which takes just a single clock cycle so shifts by constants greater than 8 bit positions can be accelerated by combining the 8-bit shift with the immediate shift.

| <u>sh32l</u>  | Shift left multiplication result register                     |

|---------------|---------------------------------------------------------------|

| <u>sh32li</u> | Shift left multiplication result register by immediate value  |

| <u>sh32r</u>  | Shift right multiplication result register                    |

| <u>sh32ri</u> | Shift right multiplication result register by immediate value |

| <u>shl</u>    | Shift left ALU register                                       |

| <u>shl8</u>   | Shift left ALU register by 8 bits                             |

| <u>shli</u>   | Shift left the ALU register by immediate value                |

| <u>shls</u>   | Shift left signed ALU register                                |

| <u>shlsi</u>  | Shift left signed ALU register by immediate value             |

| <u>shr</u>    | Shift right ALU register                                      |

| <u>shr8</u>   | Shift right ALU register by 8 bits                            |

| <u>shri</u>   | Shift right the ALU register immediate value                  |

| <u>shrs</u>   | Shift right signed ALU register                               |

| <u>shrsi</u>  | Shift right signed ALU register immediate value               |

#### Table 10. Shift instructions

## 2.11 Control, status, and flags instructions

This section covers the instructions that handle the control register, the status register and the flags register. Note that each of the four cores has its own control and status register but the four cores share the flag register.

The flags register has many purposes. The devices' input pins can be read through the (single) flags register (refer to register 1C1h and 1C3h). On the other hand, if flags are configured as output pins (refer to register 1C1h and 1C3h) they can be controlled through the flags register. The flags register can also be used by the 'wait' instruction to execute a section of code depending on its value high or low.

### Table 11. Control, status and flags instructions

| rstreg       | Reset registers (control, status, automatic diagnostics) |

|--------------|----------------------------------------------------------|

| <u>stcrb</u> | Set control register bit                                 |

| <u>stf</u>   | Set flag                                                 |

| <u>stsrb</u> | Set status register bit                                  |

PT2001SWUG

© NXP B.V. 2019. All rights reserved.

### PT2001 programming guide and instruction set

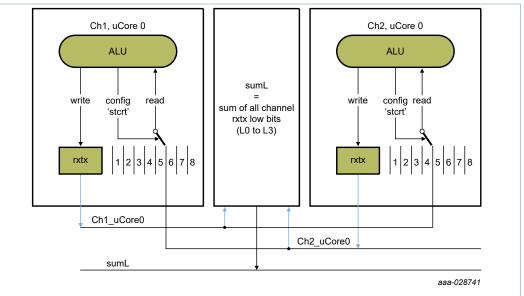

## 2.12 Intercore communication instructions

The intercore communication register 'rxtx' provides a mechanism to share data between cores. It is possible to exchange 16-bit data between different microcores, even belonging to different channels, using the ch\_rxtx address in the internal memory map. Table 12 "ch\_rxtx internal register in write mode" shows the register in write mode. The transmitting microcores can write data at this address; the receiving microcores can read the data using the same address, selecting the source with the <u>stcrt</u> instruction. Each core has its own 'rxtx' register that only it can write.

It is possible to select between two different ways of receiving the data. <u>Table 13 "ch\_rxtx</u> internal register in read mode for source sssc to ospc" shows the register in read mode when the data from one single microcore is selected. This allows transmitting 16-bit data between one microcore and another.

<u>Table 14 "ch\_rxtx internal register in read mode for source sumh, suml"</u> shows the register in read mode when the source "sumh" or "suml" is selected. In this mode, the bits H0 to H3 or L0 to L3 in all four microcores ch\_rxtx registers are counted and the result can be read from the communication register. The result for each bit Hx and Lx can be between 0 ("0000") and 6 ("0110").

| Table 12. ch_rxtx internal register in write mode |    |                     |    |    |    |    |    |    |   |   |   |   |   |   |   |   |

|---------------------------------------------------|----|---------------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|

| Bit                                               | 15 | 14                  | 13 | 12 | 11 | 10 | 9  | 8  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name                                              |    | Transmit_data       |    |    |    |    |    |    |   |   |   |   |   |   |   |   |

| Bits in sumh or suml mode                         | H3 | H2                  | H1 | H0 | L3 | L2 | L1 | L0 |   |   |   | _ | _ |   |   | _ |

| Reset                                             |    | 0000 0000 0000 0000 |    |    |    |    | _  |    |   |   |   |   |   |   |   |   |

## PT2001 programming guide and instruction set

| Bit   | 15 | 14 | 13                                    | 12 | 11 | 10 | 9  | 8       | 7       | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|----|---------------------------------------|----|----|----|----|---------|---------|-----|---|---|---|---|---|---|

| Name  |    |    | Received_data_from_selected_microcore |    |    |    |    |         |         |     |   |   |   |   |   |   |

| R/W   |    |    | R/W                                   |    |    |    |    |         |         |     |   |   |   |   |   |   |

| Lock  |    |    |                                       |    |    |    |    | y       | es      |     |   |   |   |   |   |   |

| Reset |    |    |                                       |    |    |    | 00 | 00 0000 | 0000 00 | 000 |   |   |   |   |   |   |

#### Table 14. ch\_rxtx internal register in read mode for source sumh, suml

| Bit   | 15 | 14             | 13      | 12 | 11                       | 10 | 9 | 8 | 7 | 6       | 5        | 4  | 3  | 2       | 1        | 0   |

|-------|----|----------------|---------|----|--------------------------|----|---|---|---|---------|----------|----|----|---------|----------|-----|

| Name  | su | ım(H3)o        | r sum(L | 3) | sum(H2)or sum(L2) sum(H1 |    |   |   |   | m(H1) c | or sum(L | 1) | su | m(H0) c | or sum(L | .0) |

| Reset |    | 0000 0000 0000 |         |    |                          |    |   |   |   |         |          |    |    |         |          |     |

| Table 15. | Inter- | communication | instruction | set |

|-----------|--------|---------------|-------------|-----|

|           |        |               |             |     |

| <u>stcrt</u> | Set channel communication register |

|--------------|------------------------------------|

|--------------|------------------------------------|

## 2.13 Shortcuts

Shortcuts are used to connect a core to the hardware. There are two types of shortcuts; 'output driver' shortcuts (<u>dfcsct</u>) and 'current sense block' shortcuts (<u>dfsct</u>). Output driver shortcuts allow a core to modify the states of up to three outputs at once. By modifying all three outputs in a single instruction, fully synchronized driver changes can occur in a single instruction.

Each core has one current sense block shortcut. The current sense block shortcut connects the core to one of the six current sense blocks. This shortcut is used primarily for testing the 'own current' current threshold (see the 'ocur' field value of the 'jocf' and 'jocr' instructions) or waiting for the 'own current' threshold to be reached (see the 'wait' instruction's 'ocur' field value.)

Another benefit of shortcuts is the ability to write core-independent code. This allows the exact same code to operate on different sets of output drivers and current sense blocks without having to make driver specific conditional jumps.

### Table 16. Shortcuts definition instructions

| <u>dfcsct</u> | Define current shortcut           |

|---------------|-----------------------------------|

| <u>dfsct</u>  | Define predriver output shortcuts |

## 2.14 Current sense blocks

As described in the data sheet, current sense blocks can be used as a current sense with offset compensation, or as an ADC or in a DCDC mode. The following instructions in this section are used to configure each mode.

It is possible to set the DCDC mode (stdcctl) from the microcode of any core, as long as the core has access to the LS7 output. The low-side used to control the DCDC low-side (LS7) has to be defined as shortcut 2 (dfsct) in order to use the DCDC mode.

The DAC registers are used to setup the current measurement block DACs. These DACs are affected as shown in <u>Table 17 "Current measurement DACs affectation to</u>

### PT2001 programming guide and instruction set

<u>microcores</u>". These DACs can be set by using the stdm instruction to setup the access mode. The DAC registers can be loaded with the cp and load instructions. Loading DAC register values to other registers or DRAM is also possible by means of the cp and store instructions.

### Table 17. Current measurement DACs affectation to microcores

| Microcore      | dacsssc | dacossc | oc_dac_sel_uc)<br>(next channel) | <i>ζ</i> = '0' | oc_dac_sel_ucX = '1'<br>(previous channel) |          |  |

|----------------|---------|---------|----------------------------------|----------------|--------------------------------------------|----------|--|

|                |         |         | dacssoc                          | dacosoc        | dacssoc                                    | dac osoc |  |

| Uc0, channel 1 | dac1    | dac2    | dac3                             | dac4           | dac5                                       | dac6     |  |

| Uc1, channel 1 | dac2    | dac1    | dac4                             | dac3           | dac6                                       | dac5     |  |

| Uc0, channel 2 | dac3    | dac4    | dac5                             | dac6           | dac1                                       | dac2     |  |

| Uc1, channel 2 | dac4    | dac3    | dac6                             | dac5           | dac2                                       | dac1     |  |

### Table 18. Current sense instructions

| <u>stadc</u> | Set ADC mode                                   |

|--------------|------------------------------------------------|

| stdcctl      | Set DC-DC control mode                         |

| <u>stdm</u>  | Set DAC register mode access                   |

| <u>stdm</u>  | Set current measure operational amplifier gain |

| stoc         | Set offset compensation                        |

## 2.15 Output drivers

The instructions described in this section are used to control the output drivers. Each high-side and low-side can be turned ON/OFF by all microcores if the output access registers are configured properly (refer to register 184h to 187h). Low-side and high-side bias needs to be enabled before using the diagnostics, and can be kept ON during the application.

It is possible to enable or disable the end-of-actuation mode. In the final phase of an actuation, while the current in the actuator is decreasing, it is possible to detect when the current has reached the zero value. In most applications, it is required that the Vsource threshold for the corresponding HS output is set to zero. This condition can be automatically enabled and disabled together with the end-of-actuation mode.

| Table 19. Outp | ut drivers instructions                                           |

|----------------|-------------------------------------------------------------------|

| <u>bias</u>    | Enable high-side and low-side bias                                |

| <u>steoa</u>   | Set end-of-actuation mode                                         |

| <u>stfw</u>    | Set freewheeling mode                                             |

| <u>sto</u>     | Set single predriver output                                       |

| <u>stos</u>    | Set predriver output shortcuts                                    |

| <u>stslew</u>  | Set predriver output slew rate mode                               |

| Section 3.2.2  | Set measurement function multiplexers (only available on PT2001M) |

Table 19. Output drivers instructions

### PT2001 programming guide and instruction set

## 2.16 Interrupts

An interrupt routine is executed when an interrupt request is received by the microcore. The microcore must not have already been executing another interrupt routine. The interrupt routine cannot be interrupted by any other interrupt, but only be terminated via an iret instruction or (if configured in this way by the iconf instruction) by reading the related diagnosis register through SPI (not through the SPI back door):

- Err\_ucXchY registers (162h to 169h) for the automatic diagnosis interrupt

- Driver\_status register (1D2h) for the disabled drivers interrupt.

The interrupts received are queued while another interrupt execution is ongoing. When exiting the ongoing interrupt routine with the iret instruction, the queue can be cleared and queued interrupts are ignored. Otherwise, the queued interrupts are executed according to their priorities:

- Automatic diagnosis interrupt (higher priority)

- Driver disabled interrupt

- Software interrupt (lower priority)

The interrupt return address is always calculated when the interrupt occurs, and is stored in the Ucx\_irq\_status registers (10Fh, 110h, 12Fh, 130h). The return address is the address where the code execution was interrupted. If a wait or a conditional jump instruction is interrupted, the return address is defined, restoring the status of the feedback at the moment the interrupt request occurred.

## 2.16.1 Automatic interrupt

Automatic diagnosis interrupt routine address: this address (defined in the Diag\_routine\_addr (10Ch and 12Ch) section) is selected as the new uPC value if an automatic diagnosis interrupt request is received by the microcore. This condition has an higher priority than any instruction and any other interrupt.

The following instructions are used to enable or disable the automatic diagnostics and select different configuration.

Before turning ON the diagnostics, the error table needs to be configured properly by the SPI (refer to registers HSx\_output\_config (153h to 161h) and LSx\_output\_config (140h to 152h)). The threshold can be configured either by the SPI (refer to registers  $V_{DS}$  and  $V_{SRC}$  threshold section in the data sheet) or by using the <u>chth</u> instruction.

| <u>chth</u>   | Change $V_{DS}$ and $V_{SRC}$ threshold |

|---------------|-----------------------------------------|

| <u>endiag</u> | Enable automatic diagnosis              |

| endiaga       | Enable all automatic diagnosis          |

| endiags       | Enable automatic diagnosis shortcuts    |

| <u>slfbk</u>  | Select HS2/4/6 feedback reference       |

## 2.16.2 Driver disable interrupt

Driver disabled interrupt routine address: this address (defined in the Driver\_disabled\_routine\_addr (10Dh and 12Dh) section) is selected as the new uPC value if an interrupt request, due to disabled drivers, is received by the microcore. This condition has an higher priority than any instruction and the software interrupt.

### PT2001 programming guide and instruction set

### 2.16.3 Software interrupt

Software interrupt routine address: this address (defined in the Sw\_interrupt\_routine\_addr (10Eh and 12Eh) section) is selected as the new uPC value if a software interrupt request is received by the microcore. This condition has a higher priority than any instruction.

### Table 21. Software interrupt Instructions

| reqi        | Software interrupt request        |

|-------------|-----------------------------------|

| <u>swi</u>  | Enable/disable software interrupt |

| <u>iret</u> | Return from interrupt             |

## 2.17 Counter/timers

This block contains 4 pairs of 16-bit up counter and 16-bit end-of-count registers. Each of the four counters is compared with an eoc\_reg (end-of-count register); if the counter is greater or equal than its corresponding end-of-count, then a terminal count signal is asserted. These signals are fed to uinstruction\_rom.

At reset each counter and eoc\_reg is set to zero. When a counter reaches its end-ofcount value, its value does not increase. If the eoc\_reg is changed without resetting the counter value, the counter value starts to increase again (if the new end-of-count value is greater than the counter value) until the new end-of-count value is reached.

These counters can be loaded with data coming from the DRAM or from the internal bus (e.g. ALU registers). Also, the counters can write data into the DRAM or into any of the registers connected to the internal bus (this function can be used to perform period measurements on the input signals).

It is possible to update any terminal count register without stopping the associated counter. This feature allows on-the-fly data correction in the actuated timings. All load instructions executed can simultaneously load the eoc\_reg with the value specified in the microinstruction and reset the counter.

The counter starts counting up until it meets the eoc\_reg value: at this point an eoc (endof-count) signal is set to inform the microprogram that this event has occurred. There are also load instructions that do not reset the counter after loading the eoc\_reg register. See <u>Section 3.2 "Instruction set"</u> for details of all the instructions.

Counter 1 and 2 always operate with the ck execution clock: so the maximum time that is possible to measure with a single counter is  $2^{16}$  \* ck clock period (10,923 ms at 6.0 MHz). Counter 3 and 4 can operate with a slower clock, obtained dividing the execution clock frequency (by an integer factor from 1 to 12, 14, 16, 32, or 64), to measure longer times with lower resolution (refer to register Counter\_34\_prescaler (111h and 131h).

#### Table 22. Load counter and set output instructions

| ldca | Load counter from ALU register and set outputs |

|------|------------------------------------------------|

| ldcd | Load counter from Data RAM and set outputs     |

## 2.18 SPI back door

All the SPI accessible registers can be accessed also by the microcores through an "SPI back door". Note that both Data and Code RAMs are unavailable through the back

### PT2001 programming guide and instruction set

door. The spi\_access\_controller receives all the register read/write requests, from the SPI interface and from all the enabled microcores. Top priority is given to the requests coming from the SPI interface.

To read a SPI register, first the eight LSBs of the address must be provided in the eight LSBs of the 'SPI address' at an internal memory map address to the <u>load</u> instruction. A read operation must be requested with the <u>rdspi</u> instruction. The result is available at the 'SPI data' address of the internal memory map. Note that it is necessary to wait one clk cycle to make sure the spi\_data register is updated.

To write to a SPI register, first the eight LSBs of the address must be provided in the eight LSBs of the 'SPI address' address, and the data to write must be provided at the 'SPI data' address to the <u>load</u> instruction. A write operation must be requested with the <u>wrspi</u> instruction. Both the SPI read and write operations are two cycle operations. The registers must not be changed while the operation is in progress.

If the SPI back door is not used, the 8-bit register at the address 'SPI address' and the 16-bit register at the address 'SPI data' can be used as spare register.

### Table 23. SPI back door instructions

| <u>rdspi</u> | SPI read request   |

|--------------|--------------------|

| <u>slsa</u>  | Select SPI address |

| <u>wrspi</u> | SPI write request  |

## 3 Instruction set and subsets

### 3.1 Internal registers operand subsets

This section details the predefined microcore register subsets used as instruction operands in Direct Addressing mode (DM).

| Operand label | Operand subset description                                                                                                                                                                                                                                                                                               |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AluReg        | Register designator for registers r0, r1, r2, r3, r5, r5, ir, mh, and ml                                                                                                                                                                                                                                                 |

| AluGprIrReg   | Register designator for registers r0, r1, r2, r3, r5, r5, and ir                                                                                                                                                                                                                                                         |

| UcReg         | Register designator for registers r0, r1, r2, r3, r5, r5, ir, mh, ml, ar (arith_reg),<br>aux, jr1, jr2, cnt1, cnt2, cnt3, cnt4, eoc1, eoc1, eoc3, eoc4, flag, cr (ctrl_reg),<br>sr (status_bits), spi_data, dac_sssc, dac_ossc, dac_ssoc, dac_osoc/batt,<br>dac4h4n/boost, spi_add, irq (irq_status), and rxtx (ch_rxtx) |

| JpReg         | Register designator for registers jr0 and jr1                                                                                                                                                                                                                                                                            |

#### Table 24. Operand subset overview

### 3.1.1 AluReg subset

### Table 25. AluReg subset description

| Register label | Operand binary value |

|----------------|----------------------|

| r0             | 000                  |

| r1             | 001                  |

| r2             | 010                  |

| r3             | 011                  |

## PT2001 programming guide and instruction set

| Register label | Operand binary value |

|----------------|----------------------|

| r4             | 100                  |

| ir             | 101                  |

| mh             | 110                  |

| ml             | 111                  |

## 3.1.2 AluGprIrReg subset

### Table 26. AluGpsIrReg subset description

| Register label | Operand binary value |

|----------------|----------------------|

| rO             | 000                  |

| r1             | 001                  |

| r2             | 010                  |

| r3             | 011                  |

| r4             | 100                  |

| ir             | 101                  |

## 3.1.3 UcReg subset

## Table 27. UcReg subset description

| Register label    | Operand binary value |

|-------------------|----------------------|

| r0                | 00000                |

| r1                | 00001                |

| r2                | 00010                |

| r3                | 00011                |

| r4                | 00100                |

| ir                | 00101                |

| mh                | 00110                |

| ml                | 00111                |

| ar <sup>[1]</sup> | 01000                |

| aux               | 01001                |

| jr1               | 01010                |

| jr2               | 01011                |

| cnt1              | 01100                |

| cnt2              | 01101                |

| cnt3              | 01110                |

| cnt4              | 01111                |

| eoc1              | 10000                |

| eoc2              | 10001                |

| eoc3              | 10010                |

PT2001SWUG

© NXP B.V. 2019. All rights reserved.

### PT2001 programming guide and instruction set

| Register label      | Operand binary value |

|---------------------|----------------------|

| eoc4                | 10011                |

| flag                | 10100                |

| cr <sup>[2]</sup>   | 10101                |

| sr <sup>[3]</sup>   | 10110                |

| spi_data            | 10111                |

| dac_sssc            | 11000                |

| dac_ossc            | 11001                |

| dac_ssoc            | 11010                |

| dac_osoc            | 11011                |

| dac4h4n             | 11100                |

| spi_add             | 11101                |

| irq <sup>[4]</sup>  | 11110                |

| rxtx <sup>[5]</sup> | 11111                |

[1] ar is the ALU arithmetic register arith\_reg

[2] [3]

[4] [5]

ar is the ALU anithmetic register anith\_reg cr is the control register ctrl\_reg sr is the status bits register status\_bits irq is the interrupt status register irq\_status rxtx is the other channel communication register ch\_rxtx

## 3.1.4 JpReg subset

### Table 28. JrReg subset description

| Register label | Operand binary value |

|----------------|----------------------|

| jr1            | 0                    |

| jr2            | 1                    |

## 3.2 Instruction set

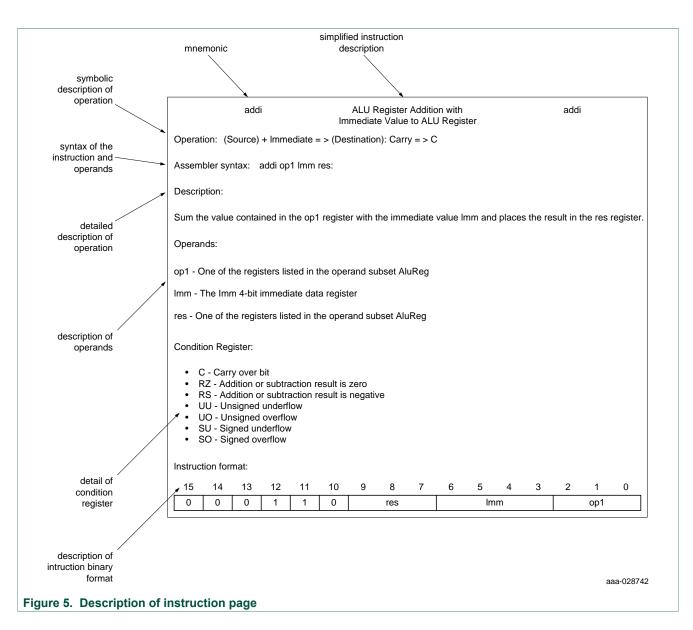

The instructions contain an entry for each assembler mnemonic, in alphabetic order. Figure 5 is a representation of an instruction page.

## **NXP Semiconductors**

# PT2001SWUG

## PT2001 programming guide and instruction set

## 3.2.1 Mnemonic index

This subsection contains an entry for each assembler mnemonic, in alphabetic order.

| Instruction name | Instruction description                                                                            |

|------------------|----------------------------------------------------------------------------------------------------|

| add              | Add two ALU registers and place the result in one of the ALU registers                             |

| <u>addi</u>      | Add an ALU register to the value in the immediate register and place the result in an ALU register |

| and              | AND-mask on ALU register with the immediate register to ALU register                               |

| <u>bias</u>      | Enable high-side and low-side bias                                                                 |

| <u>chth</u>      | Change $V_{DS}$ and $V_{SRC}$ threshold                                                            |

| <u>cp</u>        | Copy source register data in destination register                                                  |

PT2001SWUG

© NXP B.V. 2019. All rights reserved.

# PT2001 programming guide and instruction set

| Instruction name | Instruction description                                                                         |

|------------------|-------------------------------------------------------------------------------------------------|

| cwef             | Create wait table entry far                                                                     |

| <u>cwer</u>      | Create wait table entry relative                                                                |

| dfcsct           | Define current shortcut                                                                         |

| dfsct            | Define predriver output shortcuts                                                               |

| endiag           | Enable automatic diagnosis                                                                      |

| endiaga          | Enable all automatic diagnosis                                                                  |

| endiags          | Enable automatic diagnosis shortcuts                                                            |

| iconf            | Interrupt configuration                                                                         |

| <u>iret</u>      | Return from interrupt                                                                           |

| <u>jarf</u>      | Jump far on arithmetic condition                                                                |

| jarr             | Jump relative on arithmetic condition                                                           |

| <u>jcrf</u>      | Jump far on control register condition                                                          |

| <u>jcrr</u>      | Jump relative on control register condition                                                     |

| <u>jfbkf</u>     | Jump far on feedback condition                                                                  |

| <u>jfbkr</u>     | Jump relative on feedback condition                                                             |

| j <u>mpf</u>     | Unconditional jump far                                                                          |

| <u>jmpr</u>      | Unconditional jump relative                                                                     |

| <u>jocf</u>      | Jump far on condition                                                                           |

| jocr             | Jump relative on condition                                                                      |

| <u>joidf</u>     | Jump far on microcore condition                                                                 |

| <u>joidr</u>     | Jump relative on microcore condition                                                            |

| <u>joslf</u>     | Jump far on start condition                                                                     |

| <u>joslr</u>     | Jump relative on start condition                                                                |

| <u>jsrf</u>      | Jump far on status register bit condition                                                       |

| <u>jsrr</u>      | Jump relative on status register bit condition                                                  |

| <u>jtsf</u>      | Jump far to subroutine                                                                          |

| <u>jtsr</u>      | Jump relative to subroutine                                                                     |

| <u>ldca</u>      | Load counter from ALU register and set outputs                                                  |

| ldcd             | Load counter from Data RAM and set outputs                                                      |

| <u>ldirh</u>     | Load 8-MSB ir register                                                                          |

| <u>ldirl</u>     | Load 8-LSB ir register                                                                          |

| ldjr1            | Load jump register 1                                                                            |

| <u>ldjr2</u>     | Load jump register 2                                                                            |

| load             | Load data from Data RAM to register                                                             |

| mul              | Multiply two ALU registers and place the result in reg32                                        |

| muli             | Multiply an ALU register with the value in the immediate register and place the result in reg32 |

PT2001SWUG

# PT2001 programming guide and instruction set

| Instruction name | Instruction description                                          |

|------------------|------------------------------------------------------------------|

| not              | Invert ALU register bits                                         |

| or               | OR mask on ALU register with immediate register to ALU register  |

| <u>rdspi</u>     | SPI read request                                                 |

| <u>reqi</u>      | Software interrupt request                                       |

| <u>rfs</u>       | Return from subroutine                                           |

| rstreg           | Reset registers (control, status, automatic diagnostics)         |

| <u>rstsl</u>     | Start-latch registers reset                                      |

| <u>sh32l</u>     | Shift left multiplication result register                        |

| <u>sh32li</u>    | Shift left multiplication result register of immediate value     |

| <u>sh32r</u>     | Shift right multiplication result register                       |

| <u>sh32ri</u>    | Shift right multiplication result register of immediate value    |

| <u>shl</u>       | Shift left ALU register                                          |

| <u>shl8</u>      | Shift left ALU register of 8 bits                                |

| <u>shli</u>      | Shift left the ALU register of immediate value                   |

| <u>shls</u>      | Shift left signed ALU register                                   |

| <u>shlsi</u>     | Shift left signed ALU register of immediate value                |

| <u>shr</u>       | Shift right ALU register                                         |

| <u>shr8</u>      | Shift right ALU register of 8 bits                               |

| <u>shri</u>      | Shift right the ALU register of immediate value                  |

| <u>shrs</u>      | Shift right signed ALU register                                  |

| <u>shrsi</u>     | Shift right signed ALU register of immediate value               |

| <u>slab</u>      | Select Data RAM address base                                     |

| <u>slfbk</u>     | Select HS2/4/6 feedback reference                                |

| <u>slfbks</u>    | Select feedback for $V_{\text{DS}}$ HS1 to HS5 based on shortcut |

| <u>slsa</u>      | Select SPI address                                               |

| <u>stab</u>      | Set Data RAM address base                                        |

| <u>stadc</u>     | Set ADC mode                                                     |

| <u>stal</u>      | Set arithmetic logic mode                                        |

| <u>stcrb</u>     | Set control register bit                                         |

| stcrt            | Set channel communication register                               |

| stdcctl          | Set DC-DC control mode                                           |

| <u>stdm</u>      | Set DAC register mode access                                     |

| <u>stdrm</u>     | Set Data RAM read mode                                           |

| <u>steoa</u>     | Set end-of-actuation mode                                        |

| stf              | Set flag                                                         |

| <u>stfw</u>      | Set freewheeling mode                                            |

| <u>stgn</u>      | Set current measure operational amplifier gain                   |

PT2001SWUG User guide

# PT2001 programming guide and instruction set

| Instruction name | Instruction description                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------|

| stirq            | Set IRQB pin                                                                                              |

| sto              | Set single predriver output                                                                               |

| stoc             | Set offset compensation                                                                                   |

| store            | Store register data in Data RAM                                                                           |

| <u>stos</u>      | Set predriver output shortcuts                                                                            |

| stslew           | Set predriver output slew rate mode                                                                       |

| <u>stmfm</u>     | Set measurement function MUX                                                                              |

| <u>stsrb</u>     | Set status register bit                                                                                   |

| sub              | Subtract two ALU registers and place the result in one of the ALU registers                               |

| <u>subi</u>      | Subtract the value in the immediate register from an ALU register and place the result in an ALU register |

| <u>swap</u>      | Swap bytes inside ALU register                                                                            |

| <u>swi</u>       | Enable / disable software interrupt                                                                       |

| <u>toc2</u>      | Convert an integer in an ALU register to 2's compliment format                                            |

| toint            | Convert the two's complement value contained in an ALU register to integer format                         |

| wait             | Wait until condition satisfied                                                                            |

| <u>wrspi</u>     | SPI write request                                                                                         |

| xor              | Mask XOR with immediate register                                                                          |

PT2001SWUG User guide

### PT2001 programming guide and instruction set

### add

### Description:

Sums the value contained in the op1 register with the value contained in op2 register and places the result in the res register.

**Operation:** (Source1) + (Source2)  $\rightarrow$  (Destination); Carry  $\rightarrow$  C

Assembler syntax: add op1 op2 res;

### **Operands:**

- op1 One of the registers listed in the operand Section 3.1.1 "AluReg subset"

- op2 One of the registers listed in the operand Section 3.1.1 "AluReg subset"

- res One of the registers listed in the operand Section 3.1.1 "AluReg subset"

### Condition register:

- C Carry over bit

- RZ Addition or subtraction result is zero

- RS Addition or subtraction result is negative

- UU Unsigned underflow

- UO Unsigned overflow

- SU Signed underflow

- SO Signed overflow

### Table 30. add instruction format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7 | 6 | 5 | 4   | 3 | 2   | 1 | 0 |

|----|----|----|----|----|----|---|-----|---|---|---|-----|---|-----|---|---|

| 0  | 0  | 1  | 0  | 1  | 0  |   | res |   | 0 |   | op2 |   | op1 |   |   |

## PT2001 programming guide and instruction set

### addi

### Description:

Sums the value contained in the op1 register with the immediate value Imm and places the result in the res register.

**Operation:** (Source) + Immediate value  $\rightarrow$  (Destination); Carry  $\rightarrow$  C

Assembler syntax: addi op1 Imm res;

### **Operands:**

- op1 One of the registers listed in the operand Section 3.1.1 "AluReg subset"

- op2 One of the registers listed in the operand Section 3.1.1 "AluReg subset"

- res One of the registers listed in the operand Section 3.1.1 "AluReg subset"

#### Table 31. addi instruction format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7 | 6 | 5  | 4  | 3 | 2   | 1 | 0 |

|----|----|----|----|----|----|---|-----|---|---|----|----|---|-----|---|---|

| 0  | 0  | 0  | 1  | 1  | 0  |   | res |   |   | Im | ım |   | op1 |   |   |

### PT2001 programming guide and instruction set

### and

### **Description:**

Applies the AND-mask contained in the Ir register to the value contained in the op1 register. The result is placed in the op1 register. The initial data stored in the op1 register is lost.

**Operation:** (Source) + Immediate register  $\rightarrow$  (Source)

Assembler syntax: and op1;

### **Operands:**

- op1 One of the registers listed in the operand Section 3.1.1 "AluReg subset"

- Ir The ALU immediate register

### **Condition register:**

- MN Mask result is 0000h

- MM Mask result is FFFFh

### Table 32. and instruction format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|---|---|

| 0  | 0  | 1  | 0  | 1  | 1  | 1 | 0 | 1 | 1 | 0 | 0 | 1 | op1 |   |   |

### Source code example:

\*### Do 0x0C00 & IRQ status register ####

irq\_and: cp irq r0; Idirh 0Ch rst; and r0; \* Save irq register into r0 (for this example irq = 0x400 due to a sw interrupt 1)

\* Load immediate register ir MSB with 0x0C and reset the LSB -> IR = 0x0C00

\* Operation does ir & r0 = 0x0C00 & 0x0400 = 0x0400 and save this results in r0

### PT2001 programming guide and instruction set

### bias

### **Description:**

Enables/disables individually the high-side and low-side PT2001 load bias structures. This operation is successful only if the microcore has the right to drive the output related to the selected bias structure. The drive right is granted by setting the related bits in the Out\_acc\_ucX\_chY (184h, 185h, 186h, 187h) configuration registers.

Assembler syntax: bias BiasTarget Ctrl;

### **Operands:**

BiasTarget- Operand defines the bias structure(s) to be selected

| Operand label | Operand description                                                                          |

|---------------|----------------------------------------------------------------------------------------------|

| hs1           | Select HS1 bias structure                                                                    |

| hs2           | Select HS2 bias structure                                                                    |

| hs3           | Select HS3 bias structure                                                                    |

| hs4           | Select HS4 bias structure                                                                    |

| hs5           | Select HS5 bias structure                                                                    |

| ls1           | Select LS1 bias structure                                                                    |

| ls2           | Select LS2 bias structure                                                                    |

| ls3           | Select LS3 bias structure                                                                    |

| ls4           | Select LS4 bias structure                                                                    |

| ls5           | Select LS5 bias structure                                                                    |

| ls6           | Select LS6 bias structure                                                                    |

| hs2s          | Select HS2 strong bias structure                                                             |

| hs4s          | Select HS4 strong bias structure                                                             |

| all           | Select all high-side and low-side predriver bias structures including strong bias structures |

| hs            | Select all high-side predriver bias structures including strong bias structures              |

| ls            | Select all low-side predriver bias structures                                                |

### **Operands:**

• Ctrl - Operand defines the bias structure(s) state to be applied

| Operand label | Operand description    |

|---------------|------------------------|

| off           | Bias structure disable |

| on            | Bias structure enable  |

### Table 33. bias instruction format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4    | 3          | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|------|------------|---|---|---|

| 0  | 0  | 1  | 1  | 0  | 1  | 1 | 0 | 0 | 0 | 1 | Ctrl | BiasTarget |   |   |   |

### PT2001 programming guide and instruction set

### chth

### **Description:**

Changes the thresholds for the selected  $V_{DS}$  and  $V_{SRC}$  feedback comparator.

These are the same values as in registers Vds\_threshold\_hs\_partx (16Bh, 16Ch), Vsrc\_threshold\_hs\_partx (16Dh, 16Eh) and Vds\_threshold\_ls\_partx (16Fh, 170h).

This operation is successful only if the microcore has the right to drive the output related to selected threshold. The configuration of the high-side predriver  $V_{SRC}$  threshold is also impacted by the bootstrap initialization mode.

Assembler syntax: chth SelFbk ThLevel;

### **Operands:**

- SelFbk Operand defines the threshold comparator to be selected

- ThLevel This operand specifies one of the 16 threshold level values

| Operand label   | Operand description           |

|-----------------|-------------------------------|

| SelFbk operand  | ·                             |

| hs1v            | HS1 V <sub>DS</sub> feedback  |

| hs1s            | HS1 V <sub>SRC</sub> feedback |

| hs2v            | HS2 V <sub>DS</sub> feedback  |

| hs2s            | HS2 V <sub>SRC</sub> feedback |

| hs3v            | HS3 V <sub>DS</sub> feedback  |

| hs3s            | HS3 V <sub>SRC</sub> feedback |

| hs4v            | HS4 V <sub>DS</sub> feedback  |

| hs4s            | HS4 V <sub>SRC</sub> feedback |

| hs5v            | HS5 V <sub>DS</sub> feedback  |

| hs5s            | HS5 V <sub>SRC</sub> feedback |

| ls1v            | LS1 V <sub>DS</sub> feedback  |

| ls2v            | LS2 V <sub>DS</sub> feedback  |

| ls3v            | LS3 V <sub>DS</sub> feedback  |

| ls4v            | LS4 V <sub>DS</sub> feedback  |

| ls5v            | LS5 V <sub>DS</sub> feedback  |

| ls6v            | LS6 V <sub>DS</sub> feedback  |

| ThLevel operand |                               |

| lv1             | First level: 0.00 V           |

| lv2             | Second level: 0.50 V          |

| lv3             | Third level: 1.0 V            |

| lv4             | Fourth level: 1.5 V           |

| lv5             | Fifth level: 2.0 V            |

| lv6             | Sixth level: 2.5 V            |

| lv7             | Seventh level 3.0 V           |

# **NXP Semiconductors**

# PT2001SWUG

# PT2001 programming guide and instruction set

| Operand label | Operand description      |

|---------------|--------------------------|

| lv8           | Eighth level: 3.5 V      |

| lv9           | Ninth level: 0.10 V      |

| lv10          | Tenth level: 0.20 V      |

| lv11          | Eleventh level: 0.30 V   |

| lv12          | Twelfth level: 0.40 V    |

| lv13          | Thirteenth level: 0.60 V |

| lv14          | Fourteenth level: 0.70 V |

| lv15          | Fifteenth level: 0.80 V  |

| lv16          | Sixteenth level: 0.90 V  |

### Table 34. chth instruction format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6      | 5 | 4 | 3 | 2 | 1       | 0 |

|----|----|----|----|----|----|---|---|---|--------|---|---|---|---|---------|---|

| 0  | 0  | 1  | 0  | 1  | 1  | 1 | 1 | 1 | SelFbk |   |   |   |   | ThLevel |   |

PT2001SWUG User guide

PT2001 programming guide and instruction set

### ср

### Description:

Copies the value from the source register op1 into the destination register op2.

Assembler syntax: cp op1 op2;

### Operands:

- op1 One of the registers listed in the operand Section 3.1.3 "UcReg subset"

- op2 One of the registers listed in the operand <u>Section 3.1.3 "UcReg subset"</u>

### Table 35. cp instruction format

| 15 | 14 | 13 | 12 | 11 | 10  | 9 | 8 | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|-----|---|---|-----|---|---|---|---|---|---|---|

| 1  | 0  | 1  |    |    | op1 |   |   | op2 |   |   |   | 0 | 0 | 0 |   |

### PT2001 programming guide and instruction set

### cwef

### **Description:**

Initializes or changes a row in the wait table used by the wait instruction The wait table is a five-row/two-column table:

- The first column contains the wait conditions.

- The second column contains the jump register name op1 contains the absolute destination addresses. Up to five conditions may be checked at the same time.

When the condition Cond is satisfied and the entry is enabled, the execution continues either to the address 'jr1' or 'jr2' as specified by the op1 parameter.

Assembler syntax: cwef op1 Cond Entry;

### **Operands:**

- op1 One of the registers listed in the operand Section 3.1.4 "JpReg subset"

- Cond Operand defines the condition to be satisfied to enable the jump far

| Operand label | Operand description |

|---------------|---------------------|

| Cond operand  |                     |

| _f0           | Flag 0 low          |

| _f1           | Flag 1 low          |

| _f2           | Flag 2 low          |

| _f3           | Flag 3 low          |

| _f4           | Flag 4 low          |

| _f5           | Flag 5 low          |

| _f6           | Flag 6 low          |

| _f7           | Flag 7 low          |

| _f8           | Flag 8 low          |

| _f9           | Flag 9 low          |

| _f10          | Flag 10 low         |

| _f11          | Flag 11 low         |

| _f12          | Flag 12 low         |

| _f13          | Flag 13 low         |

| _f14          | Flag 14 low         |

| _f15          | Flag 15 low         |

| fO            | Flag 0 high         |

| f1            | Flag 1 high         |

| f2            | Flag 2 high         |

| f3            | Flag 3 high         |

| f4            | Flag 4 high         |

| f5            | Flag 5 high         |

| f6            | Flag 6 high         |

# **NXP Semiconductors**

# PT2001SWUG

# PT2001 programming guide and instruction set

| Operand label | Operand description                     |  |  |  |

|---------------|-----------------------------------------|--|--|--|

| f7            | Flag 7 high                             |  |  |  |

| f8            | Flag 8 high                             |  |  |  |

| f9            | Flag 9 high                             |  |  |  |

| f10           | Flag 10 high                            |  |  |  |

| f11           | Flag 11 high                            |  |  |  |

| f12 / cur4    | Flag 12 high / current feedback high    |  |  |  |

| f13           | Flag 13 high                            |  |  |  |

| f14           | Flag 14 high                            |  |  |  |

| f15           | Flag 15 high                            |  |  |  |

| tc1           | Terminal count 1                        |  |  |  |

| tc2           | Terminal count 2                        |  |  |  |

| tc3           | Terminal count 3                        |  |  |  |

| tc4           | Terminal count 4                        |  |  |  |

| _start        | Start low                               |  |  |  |

| start         | Start high                              |  |  |  |