**Application note**

#### **Document information**

| Information | Content                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | PMIC, PF7100, i.MX 8, S32                                                                                                    |

| Abstract    | This application note provides a comprehensive list of design guidelines used for the hardware development of PF7100 device. |

#### Revision history

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 1.0 | 20200615 | Initial version |

## 1 Overview

The PF7100 family of devices feature a power management integrated circuit (PMIC) designed for high performance i.MX 8 processors. It features high-efficiency buck converters and linear regulators for powering the processor, memory and miscellaneous peripherals.

The PF7100 PMIC family comprises three devices, to address different market needs:

- PF7100 automotive ASIL B device provides a full feature PMIC with five switching regulators and two LDOs, integrates functional safety mechanism to comply with the ISO 26262 standard, and provides a powerful and flexible solution for ASIL B(D) automotive modules.

- PF7100 automotive QM device provides the same switching and LDO regulator resources as ASIL B device, but without the functional safety overhead to provide an economic platform for systems not required to meet the ASIL B qualification.

- PF7100 industrial version device provides all the same switching and LDO regulator resources as automotive ASIL B device. It addresses industrial market applications.

Built-in one-time programmable (OTP) memory stores key startup configurations, drastically reducing external components typically used to set output voltage and sequence of external regulators. Regulator parameters are adjustable through high-speed I2C after power-up offering flexibility for different system states.

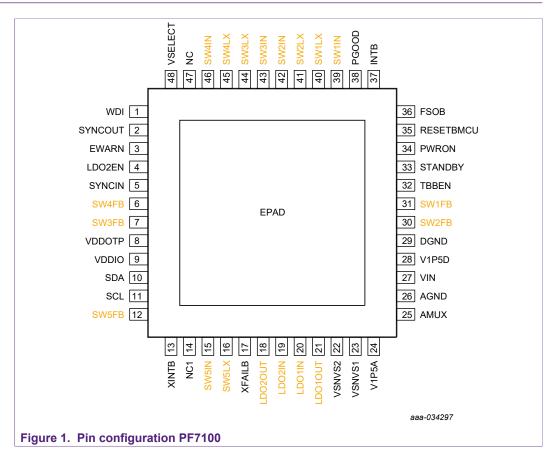

The PF7100 devices are available in HVQFN48 package with dimple wettable flank. Refer to PF7100 data sheet for more information.

AN12870 PF7100 design guidelines

## 2 Package pinout

## 3 PMIC control schematic design

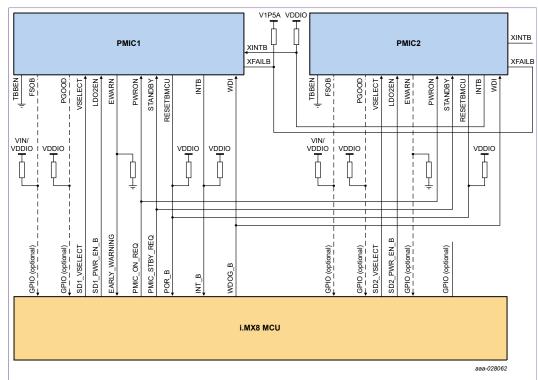

## 3.1 I/O interfacing diagram

#### Figure 2. I/O interfacing diagram

| Pin #        | Symbol     | Pin description                                 | Туре | i.MX8 application connection                                                                                                                               |

|--------------|------------|-------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCU interfac | ce I/Os    | <u>.</u>                                        |      |                                                                                                                                                            |

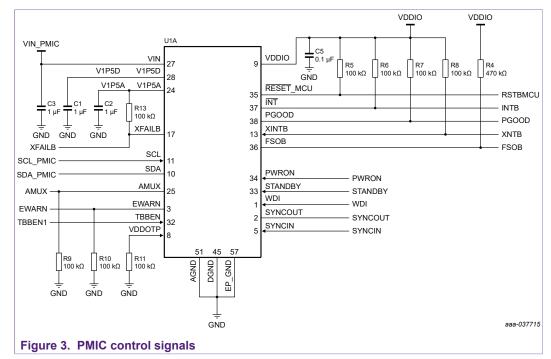

| 34           | PWRON      | PWRON input                                     | I    | Autostart mode: 100 kΩ pull up to VIN or VSNVS<br>SCU control mode: connected to MCU PMIC_ON_REQ                                                           |

| 33           | STANDBY    | STANDBY input                                   | I    | Connected to MCU PMIC_STBY_REQ                                                                                                                             |

| 1            | WDI        | Watchdog Input from MCU                         | I    | Connected to MCU WDOG_B                                                                                                                                    |

| 35           | RESETBMCU  | RESETBMCU open drain output                     | 0    | Connected to MCU I/O (POR_B) with 100 k $\Omega$ pull up to VDDIO                                                                                          |

| 37           | INTB       | INTB open drain output                          | 0    | Connected to MCU INT_B with a 100 k $\Omega$ pull up to VDDIO                                                                                              |

| 3            | EWARN      | Early warning to MCU                            | 0    | Connected to MCU EARLY_WARNING with a 100 k $\Omega$ pull down to ground                                                                                   |

| General func | ction I/Os |                                                 |      | }                                                                                                                                                          |

| 4            | LDO2EN     | LDO2 Enable pin                                 | I    | Connect to MCU I/O                                                                                                                                         |

| 48           | VSELECT    | LDO2 voltage select input                       | I    | Connected to MCU SDx_VSELECT                                                                                                                               |

| 38           | PGOOD      | PGOOD open drain output                         | 0    | Connect to MCU I/O with 100 k $\Omega$ pull up to VDDIO                                                                                                    |

| 5            | SYNCIN     | External clock input pin for synchronization    | I    | Connect to external clock signal                                                                                                                           |

| 2            | SYNCOUT    | Clock out pin for external part synchronization | 0    | Pin for master clock generation                                                                                                                            |

| 25           | AMUX       | Analog multiplexer output                       | 0    | Connect to MCU analog to digital converter                                                                                                                 |

| 36           | FSOB       | Safety output pin                               | 0    | Connected to safety output monitoring I/O on MCU with a 100 k $\Omega$ pull up to VDDIO Optional system interface pin with a 470 k $\Omega$ pull up to VIN |

| 11           | SCL        | I <sup>2</sup> C synchronous clock              | I    | 2.2 kΩ pull up to VDDIO                                                                                                                                    |

AN12870

# AN12870

#### PF7100 design guidelines

| Pin #        | Symbol  | Pin description                                      | Туре | i.MX8 application connection                                                                                      |

|--------------|---------|------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------|

| 10           | SDA     | I <sup>2</sup> C data line                           | I/O  | 2.2 kΩ pull up to VDDIO                                                                                           |

| PMIC interfa | ce I/Os |                                                      |      |                                                                                                                   |

| 13           | XINTB   | External interrupt input                             | I    | Connected to companion PMIC INTB pin with a 100 $k\Omega$ pull up to VDDIO                                        |

| 17           | XFAILB  | External fail detection and PMIC synchronization pin | I/O  | Connect to companion PMIC XFAILB with a 100 $k\Omega$ pull up to its own V1P5A                                    |

| 32           | TBBEN   | Try before buy enable pin                            | 1    | GND                                                                                                               |

| PMIC core s  | upplies |                                                      |      | )                                                                                                                 |

| 9            | VDDIO   | System I/O supply                                    | I/O  | Bypass with a 0.1 µF capacitor                                                                                    |

| 23           | VSNVS1  | VSNVS1 regulator output                              | I    | Connected to SNVS domain in MCU with a 2.2 $\mu\text{F}$ capacitor                                                |

| 22           | VSNVS2  | VSNVS2 regulator output                              | 0    | Second connection to SNVS domain in MCU with a 2.2 µF capacitor<br>Used as general purpose always in power supply |

| 24           | V1P5A   | Internal 1.5 V analog supply decoupling pin          | 0    | Bypass with 1.0 μF capacitor                                                                                      |

| 28           | V1P5D   | Internal 1.5 V digital supply decoupling pin         | 0    | Bypass with 1.0 μF capacitor                                                                                      |

#### 3.2 PMIC control signals

The PF7100 automotive devices are targeted for a range of automotive applications, including Infotainment, telematics. For this reason, the devices have been defined to comply with the AEQ-100 automotive standard. In order to fulfill the automotive standards at system level, it is encouraged to use automotive grade components.

## 3.3 Special use case configurations

One of the main features of the PF7100 PMIC device is the flexibility to configure the default configuration of the system as well as provide full control of the PMIC during the system-on state via the  $I^2C$  communication bus.

The default configuration (OTP) can be defined and programmed in several ways:

- For high volume opportunities, NXP offers full device customization, including default OTP programing and custom part marking.

- For lower volume opportunities, NXP works with distributors to enable them to provide in-house programming of the PF7100 PMIC device for their customers.

- On-board device programming is available for customers that require in-house programming out of their production line.

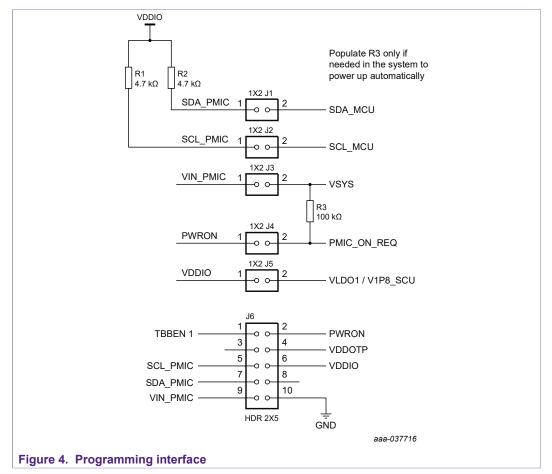

For customers opting for on-board OTP configuration, a special configuration is required to allow proper access to the PMIC configuration signals without interfering or damaging any components from the main system. Figure 4 shows the recommended configuration compatible with NXP programming tools.

**Note:** Programming interface connector pinout shown in <u>Figure 4</u> is compatible with the KITPF7100FRDMPGM programming tool.

**Note:** Configuration signal may require isolation from the main system in order to allow proper communication with the PMIC during OTP programming procedure. Such isolation may be achieved via two row pin headers,  $0 \Omega$  resistor arrays or a dip switch array.

**Note:** PMIC\_ON\_REQ pull up may be moved to the SNVS\_SCU\_V1P8 domain on i.MX8 processor or not connected when the PMIC\_ON\_REQ is a push pull driver.

### 3.4 Unused pin termination

When a specific feature is not required on the system, certain rules should be followed to properly terminate the unused pins on the system. Likewise, some software/OTP configuration may be required to ensure proper operation of the PMIC. <u>Table 1</u> provides all considerations for unused pin termination.

Termination if not used Software/OTP considerations Pin # Symbol NC 1. NC 47 2. GND TBBEN GND 32 VSELECT 48 GND OTP VSELECTEN = 0 WDI GND OTP WDI INV = 0 1 3 EWARN 100 k $\Omega$  pulled down to GND RESETBMCU 35 100 k $\Omega$  pulled up to VDDIO PWRON N/A 34 STANDBY GND OTP STBY INV = 0 33 INTB 100 k $\Omega$  pulled up to VDDIO All interrupt mask = 1 37 FSOB 100 k $\Omega$  pulled up to VDDIO/VIN OTP ASS FSOB = 0 36 OTP FSOB configuration bits = 0 13 XINTB 1. NC 2. 100 k $\Omega$  pulled up to VDDIO 38 PGOOD 1. NC 1. All OTP SWx PG EN bits = 0 and OTP LDOx PG EN bits = 0 2. 100 k $\Omega$  pulled up to VDDIO 4 LDO2EN GND OTP LDO2EN = 0 17 XFAILB OTP\_XFAIL\_EN = 0 1. 100 k $\Omega$  pulled up to V1P5A 2. GND 23 VSNVS1 2.2 µF OTP VSNVS1 = 00 VSNVS2 2.2 µF OTP VSNVS2 = 00 22 5 SYNCIN GND OTP SYNCIN EN = 0 2 SYNCOUT 1. NC OTP SYNCOUT EN = 0 2. 100 k $\Omega$  pulled down to GND 25 AMUX 1. NC AMUX\_EN = 0 2. 100 k $\Omega$  pulled down to GND

Table 1. Unused functional pin termination

## 4 **Power supplies schematic design**

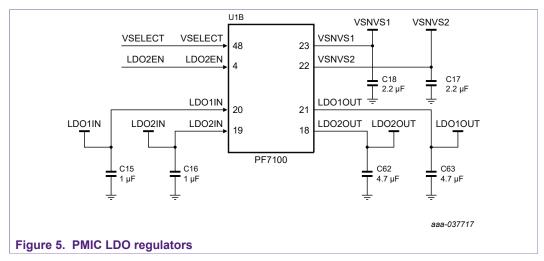

LDO regulators schematic require only the input capacitance and output capacitance as shown in Figure 5.

AN12870

#### PF7100 design guidelines

Input/output capacitors must be rated at least twice the value of the input in the pin. For input capacitors, it is recommended to use at least a 10 V or 16 V rating and for output capacitors at least 6.3 V to 10 V rating to minimize capacitance variation overvoltage.

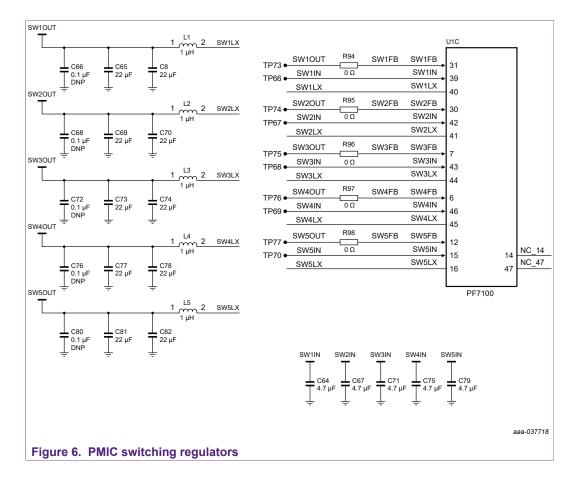

Switching regulators require the following components:

- 4.7 µF input capacitor rated at least 10 V or 16 V.

- 1.0 µH inductor with saturation current higher than the current limit selected for the application. DCR < 40 mΩ is recommended to improve efficiency performance of the regulator.

- 2 x 22 µF output capacitor rated at least 6.3 V. Multiple capacitors are required to improve total ESR of the output capacitor.

- Both input and output may add a small 0.1 µF capacitor for decoupling high frequency noise on the pins, however the noise reduction impact with these capacitors is minimal and they may be excluded if desired.

# AN12870

#### PF7100 design guidelines

#### 4.1 Terminating unused regulator pins

For unused LDO regulators, the OTP\_LDOx\_SEQ must be set as 0x00 in OTP and the LDOs cannot be enabled by software when PMIC is On. The pins can be terminated as indicated below:

- LDOXIN = GND

- LDOxOUT = GND

For unused switching regulators, the OTP\_SWx\_SEQ must be set as 0x00 in OTP and the regulators cannot be enabled by software when PMIC is On. The pins can be terminated as shown in <u>Table 2</u>.

| No connects allowed (preferred) | Physical termination required |  |

|---------------------------------|-------------------------------|--|

| SWxIN = VIN                     | SWxIN = GND                   |  |

| SWxLX = not connected           | SWxLX = GND                   |  |

| SWxFB = GND                     | SWxFB = GND                   |  |

## **5 PCB** layout recommendations

### 5.1 General layout recommendations

- 1. The PF7100 PMIC device pinout is defined in such a way that it can be laid-out in as little as four layers, however, at least six layers are recommended to provide proper shielding and grounding to minimize ground loops and ensure proper operation.

- High current signals

- GND

- Signal

- Signal

- GND

- High current signal

- 2. Allocate TOP layer for main component placement and output power routing of the switching regulators and LDOs; place a dynamic copper plane to ground on the unused area.

- 3. Allocate bottom layer for input power routing; place a dynamic copper plane to ground on the unused area.

- 4. Use internal layers sandwiched between two GND planes for the SIGNAL routing.

- 5. It is desirable to keep all components related to the power stage as close to the PMIC as possible, specially decoupling input and output capacitors.

## 5.2 General routing requirements

- 1. Some recommended rules to keep in mind for manufacturability:

- Via in pads require a 4.5 mil minimum annular ring. Pad must be 9.0 mils larger than the hole

- Maximum copper thickness for lines less than 5.0 mils wide is 0.6 oz copper

- Minimum allowed spacing between line and hole pad is 3.5 mils

- Minimum allowed spacing between line and line is 3.0 mils

- 2. Care must be taken with SWxFB pins traces. These signals are susceptible to noise and must be routed far away from power, clock, or high-power signals, like the ones on the SWxIN, SWx, SWxLX pins.

- 3. Run feedback traces of the regulators in the inner layers to keep them shielded from the power and noise nodes.

- 4. Avoid coupling V1P5D, V1P5A traces with any high current, high-speed switching nodes (i.e. SWxLX nodes).

- 5. Make sure all components related to a specific block are referenced to the corresponding ground. Use through vias to connect signals to the closest ground plane to minimize the ground loop.

### 5.3 Switching regulators layout recommendations

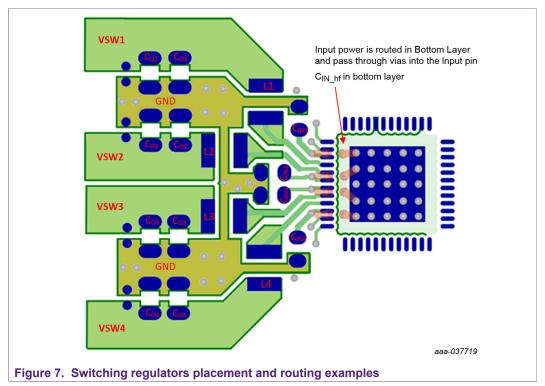

1. Per design, the switching regulators in PF7100 PMIC device, are designed to operate with only one input bulk capacitor. Depending on the strategy and the specific PCB layout design rules, the input capacitor can be placed on the top layer as close as possible to the input pin, or placed on the bottom layer underneath the PMIC, using enough vias to connect to the Input pin and to the expose path.

- 2. A high frequency filter input capacitor (CIN\_hf), can be added to help filter out high frequency noise at the regulator input. This capacitor should be in the range of 100 nF and should be placed right next to or under the IC, closest to the IC pins.

- 3. Make the LX nodes as wide and short as possible to minimize the trace inductance and improve the output efficiency.

- 4. Make high-current traces as symmetrical as possible for dual or quad phase regulators.

AN12870 Application note

# AN12870 PF7100 design guidelines

# 6 Legal information

## 6.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

## 6.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors

accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors or of the application or use by customer(s). NXP does not accept any liability in this respect.

Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

### 6.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

$I^2$ C-bus — logo is a trademark of NXP B.V. NXP — is a trademark of NXP B.V.

## **NXP Semiconductors**

## **Tables**

| Tab. 1.            | Unused functional pin termination8                    | Tab. 2.            | Switching regulator termination1                     | 0 |

|--------------------|-------------------------------------------------------|--------------------|------------------------------------------------------|---|

| Figur              | es                                                    |                    |                                                      |   |

| Fig. 1.<br>Fig. 2. | Pin configuration PF71004<br>I/O interfacing diagram5 | Fig. 5.<br>Fig. 6. | PMIC LDO regulators<br>PMIC switching regulators     |   |

| Fig. 3.<br>Fig. 4. | PMIC control signals6<br>Programming interface7       | Fig. 7.            | Switching regulators placement and routing examples1 | 2 |

### **NXP Semiconductors**

# AN12870 PF7100 design guidelines

## Contents

| 1   | Overview                          | 3  |

|-----|-----------------------------------|----|

| 2   | Package pinout                    | 4  |

| 3   | PMIC control schematic design     | 5  |

| 3.1 | I/O interfacing diagram           | 5  |

| 3.2 | PMIC control signals              |    |

| 3.3 | Special use case configurations   |    |

| 3.4 | Unused pin termination            | 8  |

| 4   | Power supplies schematic design   |    |

| 4.1 | Terminating unused regulator pins |    |

| 5   | PCB layout recommendations        |    |

| 5.1 | General layout recommendations    | 11 |

| 5.2 | General routing requirements      | 11 |

| 5.3 | Switching regulators layout       |    |

|     | recommendations                   | 11 |

| 6   | Legal information                 | 13 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2020.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 15 June 2020 Document identifier: AN12870