#### 1 Features

- 3-State Outputs Drive Bus Lines Directly

- PNP Inputs Reduce DC Loading on Bus Lines

- Hysteresis at Bus Inputs Improves Noise Margins

- Typical Propagation Delay Times Port to Port, 8 ns

### 2 Applications

- Building Automation

- Electronic Point of Sale

- Factory Automation and Control

- Test and Measurement

### 3 Description

These octal bus transceivers are designed for asynchronous two-way communication between data buses. The control-function implementation minimizes external timing requirements.

The 74HC245 devices allow data transmission from the A bus to the B bus or from the B bus to the A bus, depending on the logic level at the directioncontrol (DIR) input. The output-enable ( $\overline{OE}$ ) input can disable the device so that the buses are effectively isolated.

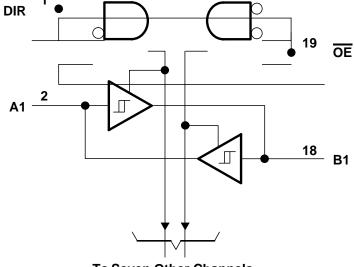

4 Logic Diagram (Positive Logic)

**To Seven Other Channels**

## 5 Device Comparison Table

| ТҮРЕ    | I <sub>OL</sub><br>(SINK CURRENT) | I <sub>ОН</sub><br>(SOURCE CURRENT) |

|---------|-----------------------------------|-------------------------------------|

| 74HC245 | 24 mA                             | –15 mA                              |

## 6 Pin Configuration and Functions

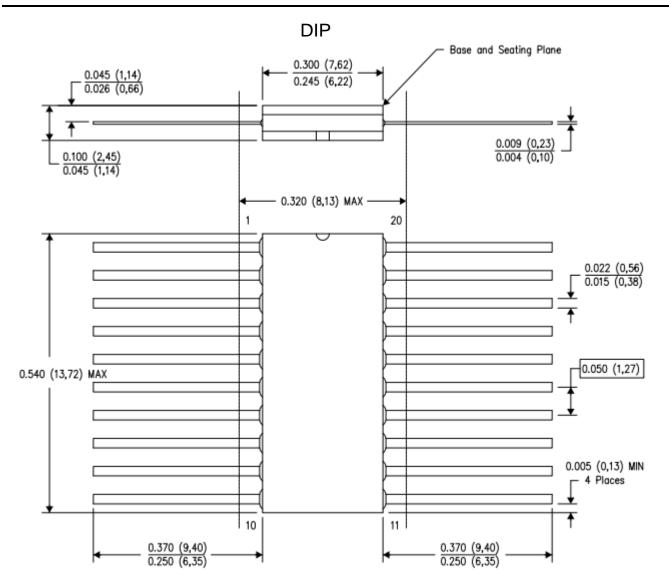

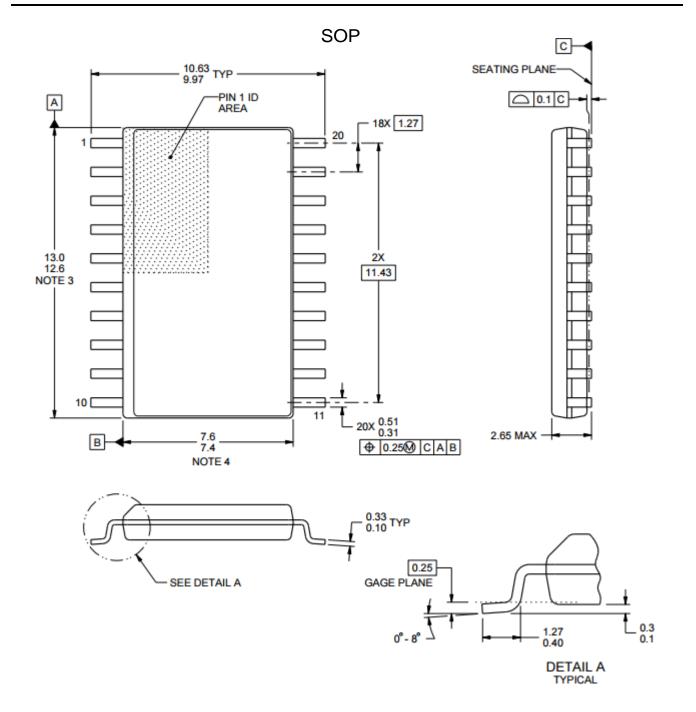

| SOP/DIP |    |                   |    |      |  |  |

|---------|----|-------------------|----|------|--|--|

|         | -  | $\mathbf{\nabla}$ |    | L    |  |  |

| DIR     | Ц1 | -                 | 20 | Vcc  |  |  |

| A1      | 2  |                   | 19 | ] OE |  |  |

| A2      | 3  |                   | 18 | ] B1 |  |  |

| A3      | 4  |                   | 17 | ] B2 |  |  |

| A4      | 5  |                   | 16 | ] B3 |  |  |

| A5      | 6  |                   | 15 | ] B4 |  |  |

| A6      | 7  |                   | 14 | ] B5 |  |  |

| A7      | 8  |                   | 13 | ] B6 |  |  |

| A8      | 9  |                   | 12 | ] B7 |  |  |

| GND     | 10 |                   | 11 | ] B8 |  |  |

#### **Pin Functions**

| PIN |                 | - I/O | DESCRIPTION                                                                                        |  |  |

|-----|-----------------|-------|----------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME            | 1/0   | DESCRIPTION                                                                                        |  |  |

| 1   | DIR             | I     | Controls signal direction; Low = Bx to Ax, High = Ax to Bx                                         |  |  |

| 2   | A1              | I/O   | Channel 1, A side                                                                                  |  |  |

| 3   | A2              | I/O   | Channel 2, A side                                                                                  |  |  |

| 4   | A3              | I/O   | Channel 3, A side                                                                                  |  |  |

| 5   | A4              | I/O   | Channel 4, A side                                                                                  |  |  |

| 6   | A5              | I/O   | Channel 5, A side                                                                                  |  |  |

| 7   | A6              | I/O   | Channel 6, A side                                                                                  |  |  |

| 8   | A7              | I/O   | Channel 7, A side                                                                                  |  |  |

| 9   | A8              | I/O   | Channel 8, A side                                                                                  |  |  |

| 10  | GND             | _     | Ground                                                                                             |  |  |

| 11  | B8              | O/I   | Channel 8, B side                                                                                  |  |  |

| 12  | B7              | O/I   | Channel 7, B side                                                                                  |  |  |

| 13  | B6              | O/I   | Channel 6, B side                                                                                  |  |  |

| 14  | B5              | O/I   | Channel 5, B side                                                                                  |  |  |

| 15  | B4              | O/I   | Channel 4, B side                                                                                  |  |  |

| 16  | B3              | O/I   | Channel 3, B side                                                                                  |  |  |

| 17  | B2              | O/I   | Channel 2, B side                                                                                  |  |  |

| 18  | B1              | O/I   | Channel 1, B side                                                                                  |  |  |

| 19  | ŌĒ              | I     | Active low output enable; Low = all channels active, High = all channels disabled (high impedance) |  |  |

| 20  | V <sub>CC</sub> |       | Power supply                                                                                       |  |  |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

|                  |                                        | MIN | MAX | UNIT |

|------------------|----------------------------------------|-----|-----|------|

| V <sub>CC</sub>  | Supply voltage                         |     | 7   | V    |

| VI               | Input voltage <sup>(1)</sup>           |     | 7   | V    |

| TJ               | Operating virtual junction temperature |     | 150 | °C   |

| T <sub>stg</sub> | Storage temperature                    | -65 | 150 | °C   |

(1) All voltage values are with respect to GND.

#### 7.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±1500 | V    |

#### 7.5 Electrical Characteristics

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER        |                                                     | TEST CONDITIONS <sup>(1)</sup>                             |                                            | MIN                      | TYP <sup>(1)</sup> | MAX | UNIT |      |    |

|------------------|-----------------------------------------------------|------------------------------------------------------------|--------------------------------------------|--------------------------|--------------------|-----|------|------|----|

| $V_{\text{IH}}$  | High-level input voltage                            |                                                            |                                            |                          |                    | 2   |      |      | V  |

| V <sub>IL</sub>  | Low-level input voltage                             |                                                            |                                            | 74HC245                  |                    |     |      | 0.8  | V  |

| V <sub>IK</sub>  | Input clamp voltage                                 |                                                            | V <sub>CC</sub> = MIN,                     | I <sub>I</sub> = -18 mA  |                    |     |      | -1.5 | V  |

|                  | Hysteresis<br>(V <sub>T+</sub> – V <sub>T</sub> _)  | A or B                                                     | $V_{CC} = MIN$                             |                          |                    | 0.2 | 0.4  |      | V  |

|                  |                                                     |                                                            | $V_{CC} = MIN,$                            | $I_{OH} = -3 \text{ mA}$ |                    | 2.4 | 3.4  |      |    |

| V <sub>OH</sub>  | High-level output voltage                           | 9                                                          | $V_{IL} = V_{IL(max)}$<br>$V_{IH} = 2 V$ , | $I_{OH} = MAX$           |                    | 2   |      |      | V  |

|                  |                                                     |                                                            | V <sub>CC</sub> = MIN,                     | I <sub>OL</sub> = 12 mA  |                    |     |      | 0.4  |    |

| V <sub>OL</sub>  | Low-level output voltage                            |                                                            | $V_{IH} = 2 V,$<br>$V_{IL} = V_{IL(max)}$  | I <sub>OL</sub> = 24 mA  | 74HC245            |     |      | 0.5  | V  |

| I <sub>OZH</sub> | Off-state output current, high-level voltage applie | d                                                          | <u>V<sub>CC</sub></u> = MAX,<br>OE at 2 V  | V <sub>O</sub> = 2.7 V   |                    |     |      | 20   | μΑ |

| I <sub>OZL</sub> | Off-state output current, low-level voltage applied | l                                                          | <u>V<sub>CC</sub></u> = MAX,<br>OE at 2 V  | V <sub>O</sub> = 0.4 V   |                    |     |      | -200 | μΑ |

|                  | Input current at                                    | A or B                                                     |                                            | V <sub>I</sub> = 5.5 V   |                    |     |      | 0.1  |    |

| I <sub>I</sub>   | maximum<br>input voltage                            | DIR or OE                                                  | V <sub>CC</sub> = MAX                      | $V_I = 7 V$              |                    |     |      | 0.1  | mA |

| I <sub>IH</sub>  | High-level input current                            |                                                            | V <sub>CC</sub> = MAX,                     | V <sub>IH</sub> = 2.7 V  |                    |     |      | 20   | μA |

| I <sub>IL</sub>  | Low-level input current                             |                                                            | $V_{CC} = MAX,$                            | $V_{IL} = 0.4 V$         |                    |     |      | -0.2 | mA |

| I <sub>OS</sub>  | Short-circuit output current <sup>(2)</sup>         |                                                            | $V_{CC} = MAX$                             |                          |                    | -40 |      | -225 | mA |

|                  |                                                     | ly current Total,<br>outputs high<br>Total,<br>outputs low |                                            |                          |                    |     | 48   | 70   |    |

| I <sub>CC</sub>  | Supply current                                      |                                                            | V <sub>CC</sub> = MAX                      | Outputs open             |                    |     | 62   | 90   | mA |

|                  |                                                     | Outputs at high Z                                          |                                            |                          |                    |     | 64   | 95   |    |

(1) All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ . (2) Not more than one output should be shorted at a time, and duration of the short circuit should not exceed one second.

## 7.6 Switching Characteristics

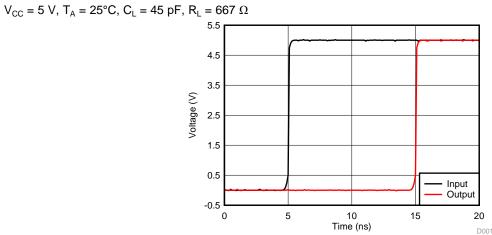

$V_{CC} = 5 \text{ V}, \text{ } \text{T}_{A} = 25^{\circ}\text{C} \text{ (see Figure 2)}$

|                  | PARAMETER                                         | TEST CONDITIONS                             | MIN | TYP | MAX | UNIT |

|------------------|---------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

| t <sub>PLH</sub> | Propagation delay time, low- to high-level output |                                             |     | 8   | 12  | ~~   |

| t <sub>PHL</sub> | Propagation delay time, high- to low-level output | $C_{L}$ = 45 pF, R <sub>L</sub> = 667 Ω     |     | 8   | 12  | ns   |

| t <sub>PZL</sub> | Output enable time to low level                   |                                             |     | 27  | 40  | ~~   |

| t <sub>PZH</sub> | Output enable time to high level                  | $C_{L} = 45 \text{ pF}, R_{L} = 667 \Omega$ |     | 25  | 40  | ns   |

| t <sub>PLZ</sub> | Output disable time from low level                |                                             |     | 15  | 25  |      |

| t <sub>PHZ</sub> | Output disable time from high level               | $C_{L} = 5 \text{ pF}, R_{L} = 667 \Omega$  |     | 15  | 28  | ns   |

## 7.7 Typical Characteristics

Figure 1. Simulated Propagation Delay From Input to Output

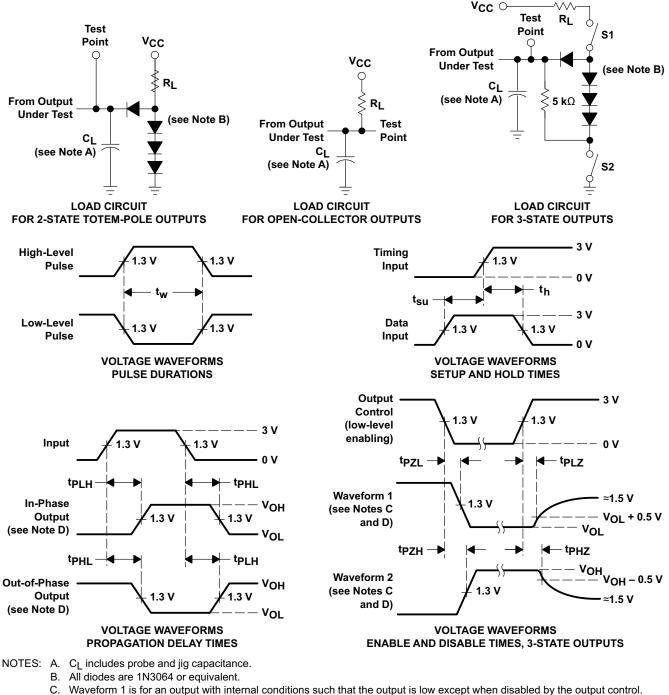

### 8 Parameter Measurement Information

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. S1 and S2 are closed for tpLH, tpHZ, and tpLZ; S1 is open and S2 is closed for tpZH; S1 is closed and S2 is open for tpZL.

- E. Phase relationships between inputs and outputs have been chosen arbitrarily for these examples.

- F. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz, Z<sub>O</sub>  $\approx$  50  $\Omega$ , t<sub>r</sub>  $\leq$  1.5 ns, t<sub>f</sub>  $\leq$  2.6 ns.

- G. The outputs are measured one at a time with one input transition per measurement.

Figure 2. Load Circuits and Voltage Waveforms

### 9 Detailed Description

#### 9.1 Overview

The 74HC245 uses Schottky transistor logic to perform the standard '245 transceiver function. This standard logic function has a common pinout, direction select pin, and active-low output enable. When the outputs are disabled, the A and B sides of the device are effectively isolated.

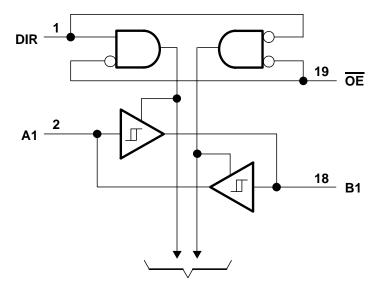

#### 9.2 Functional Block Diagram

To Seven Other Channels

Figure 3. Logic Diagram (Positive Logic)

#### 9.3 Feature Description

#### 9.3.1 3-State outputs

The 3-state outputs can drive bus lines directly. All outputs can be put into high impedance mode through the  $\overline{OE}$  pin.

#### 9.3.2 PNP Inputs

This device has PNP inputs which reduce dc loading on bus lines.

#### 9.3.3 Hysteresis on Bus Inputs

The bus inputs have built-in hysteresis that improves noise margins.

#### 9.4 Device Functional Modes

The 74HC245 performs the standard '245 logic function. Data can be transmitted from A to B or from <u>B</u> to A depending on the DIR pin value, or the A and B sides can be isolated from one another by setting the  $\overline{OE}$  pin HIGH.

#### Table 1. Function Table

| INP | UTS | OPERATION       |  |  |

|-----|-----|-----------------|--|--|

| OE  | DIR | OPERATION       |  |  |

| L   | L   | B data to A bus |  |  |

| L   | Н   | A data to B bus |  |  |

| Н   | Х   | Isolation       |  |  |

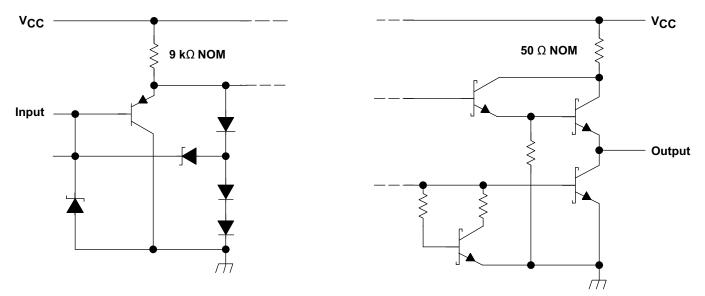

#### EQUIVALENT OF EACH INPUT

**TYPICAL OF ALL OUTPUTS**

Figure 4. Schematics of Inputs and Outputs

以上信息仅供参考. 如需帮助联系客服人员。谢谢 XINLUDA

以上信息仅供参考. 如需帮助联系客服人员。谢谢 XINLUDA