Order

Now

SNLS638A - DECEMBER 2018 - REVISED AUGUST 2019

# DP83825I Low Power 10/100 Mbps Ethernet Physical Layer Transceiver

# Features

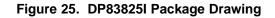

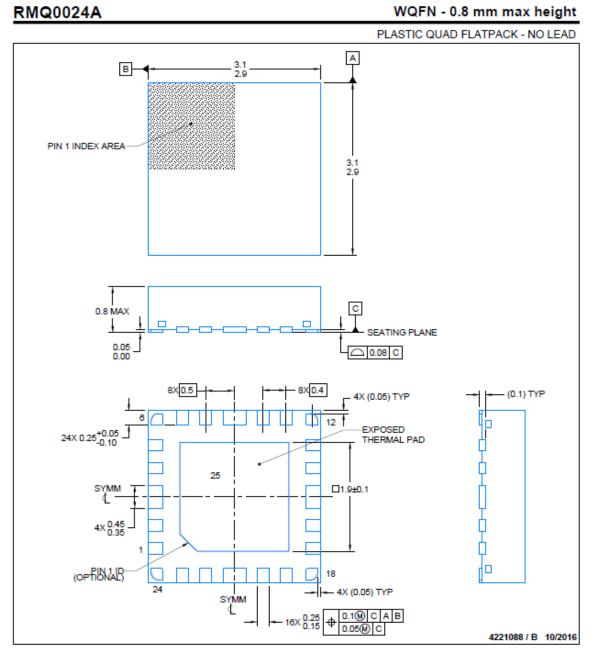

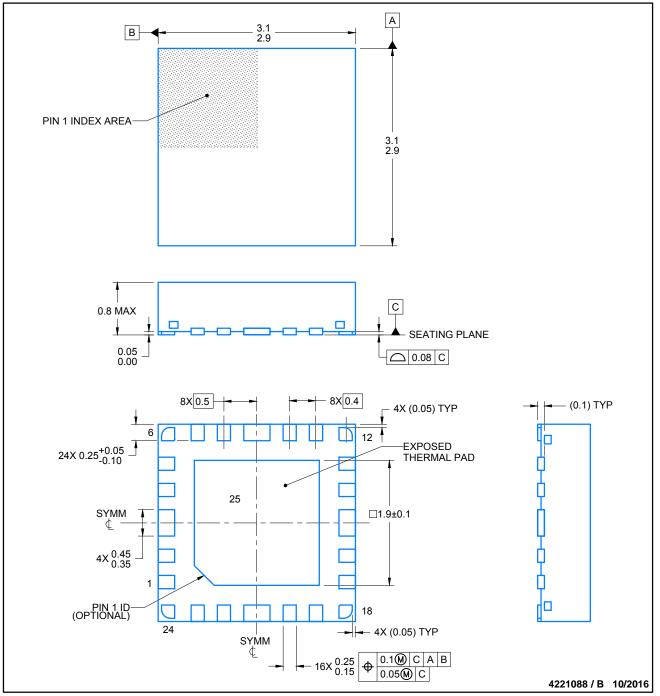

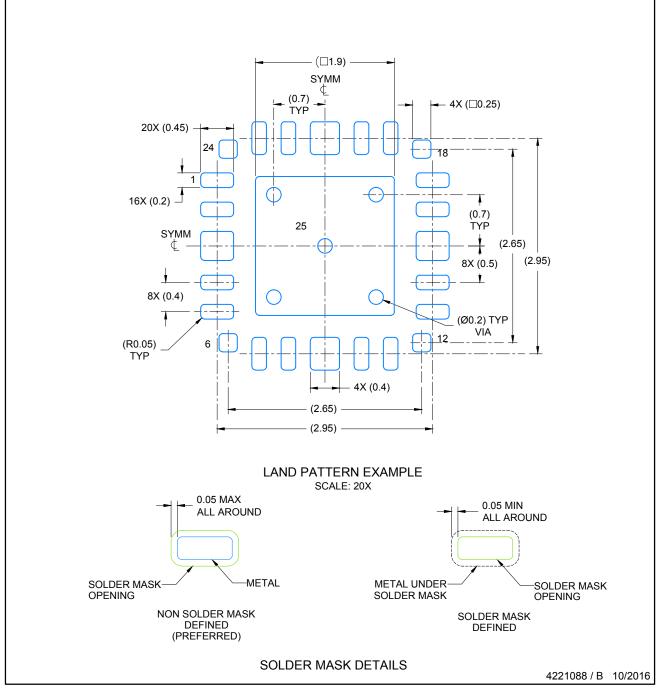

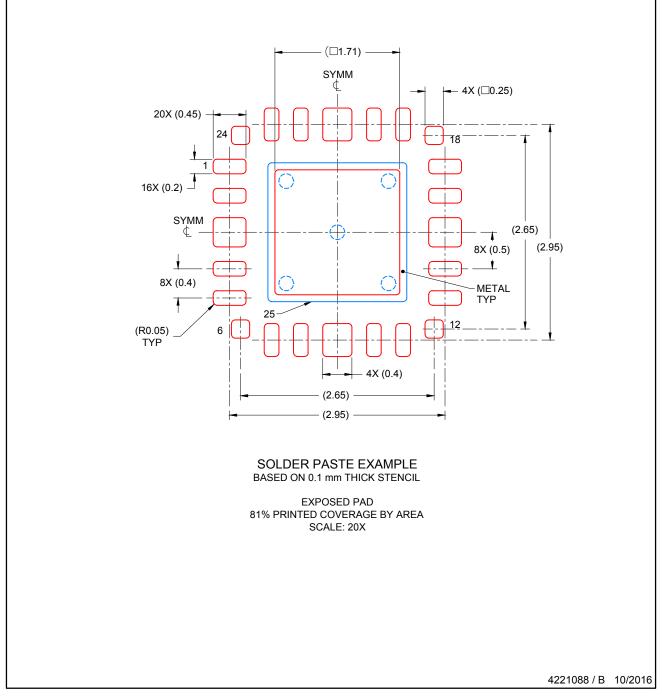

- Ultra Small Form Factor 10/100 Mbps PHY : QFN 3 mm × 3 mm, 24 pin

- Cable reach > 150 meters

- Very low power consumption < 127 mW

- Small system solution : integrated MDI and MAC termination resistors

- Programmable energy saving modes

- Active sleep

- Deep power-down

- Energy Efficient Ethernet (EEE) IEEE 802.3az

- EEE support for legacy MAC

- Wake-on-LAN (WoL)

- Voltage mode line driver

- MAC interface : RMII (master and slave mode)

- Single 3.3 V power supply

- I/O voltages: 1.8 V and 3.3 V

- Repeater : RMII back-to-back mode in unmanaged mode

- MDC/MDIO Interface for configuration and status

- Fast link drop modes

- **Diagnostics** features

- TDR-based cable diagnostics for open, short

- Built-in packet generator

- Multiple loopbacks

- Programmable Hardware interrupt pin

- Operating temperature range: -40°C to 85°C

- Compliant to IEEE 802.3 100BASE-TX and **10BASE-Te specification**

# 2 Applications

- Building automation: IP camera, HMI

- Consumer electronics: STB, OTT, IPTV, game . consoles

- **Printers**

- Electronic point of sale

- Factory automation

#### Description 3

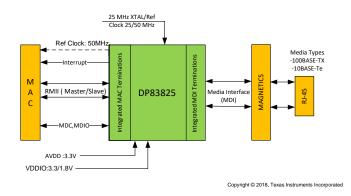

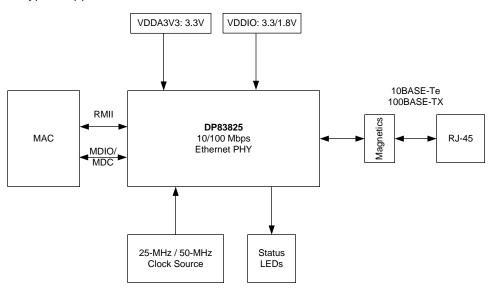

The DP83825I is an ultra small form factor, very low power Ethernet Physical Layer transceiver with integrated PMD sublayers to support 10BASE-Te, 100BASE-TX Ethernet protocols. It supports up to 150 meters reach over CAT5e cable. The DP83825I interfaces directly to twisted pair media via an external transformer. It interfaces to the MAC layer through Reduced MII (RMII) both in Master and Slave mode. It provide 50-MHz output clock in RMII Master Mode. This clock is synchronized to MDI derived clock to reduce the jitter in the system.

The DP83825I also supports Energy Efficient Ethernet, Wake-on-LAN and MAC isolation to further lower the system power consumption. Energy Efficient Mode can be enabled through register configuration for legacy MACs not supporting EEE signaling over MAC. DP838251 can operate in unmanaged repeater mode. In this mode, DP83825I works as a repeater without register configuration. The DP83825I offers integrated cable diagnostic tools, built-in self-test and loopback capabilities for ease of development and debug.

### Device Information<sup>(1)</sup>

| PART NUMBER |          |                    |

|-------------|----------|--------------------|

| DP838251    | QFN (24) | 3.00 mm × 3.00 mm, |

| DF030231    | QFN (24) | 0.4-mm pitch       |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

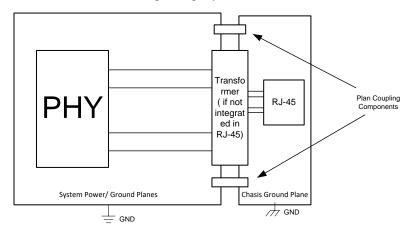

# DP83825I Application Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 | Feat | tures 1                           |

|---|------|-----------------------------------|

| 2 | Арр  | lications 1                       |

| 3 | Des  | cription 1                        |

| 4 | Rev  | ision History 2                   |

| 5 | Pin  | Configuration and Functions       |

| 6 | Spe  | cifications5                      |

|   | 6.1  | Absolute Maximum Ratings 5        |

|   | 6.2  | ESD Ratings5                      |

|   | 6.3  | Recommended Operating Conditions5 |

|   | 6.4  | Thermal Information 5             |

|   | 6.5  | Electrical Characteristics 6      |

|   | 6.6  | Timing Requirements 9             |

|   | 6.7  | Timing Diagrams 11                |

|   | 6.8  | Typical Characteristics 14        |

| 7 | Deta | ailed Description                 |

|   | 7.1  | Overview                          |

|   | 7.2  | Functional Block Diagram 19       |

|   | 7.3  | Feature Description 19            |

|   |      |                                   |

|    | 7.4  | Device Functional Modes                         | 36              |

|----|------|-------------------------------------------------|-----------------|

|    | 7.5  | Programming                                     | 38              |

|    | 7.6  | Register Maps                                   | 41              |

| 8  | Арр  | lication and Implementation                     | 90              |

|    | 8.1  | Application Information                         | 90              |

|    | 8.2  | Typical Applications                            | 90              |

| 9  | Pow  | er Supply Recommendations                       | 94              |

| 10 | Lay  | out                                             | 94              |

|    | 10.1 | Layout Guidelines                               | 94              |

|    | 10.2 | Layout Example                                  | <mark>98</mark> |

| 11 | Dev  | ice and Documentation Support                   | 99              |

|    | 11.1 | Receiving Notification of Documentation Updates | 99              |

|    | 11.2 | Community Resources                             | 99              |

|    | 11.3 | Trademarks                                      | 99              |

|    | 11.4 | Electrostatic Discharge Caution                 | 99              |

|    | 11.5 | Glossary                                        | 99              |

| 12 |      | hanical, Packaging, and Orderable               |                 |

|    | Info | rmation                                         | 99              |

|    |      |                                                 |                 |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | nanges from Original (December 2018) to Revision A                   | <b>Page</b> |

|----|----------------------------------------------------------------------|-------------|

| •  | Changed device status from: Advanced Information to: Production Data | 1           |

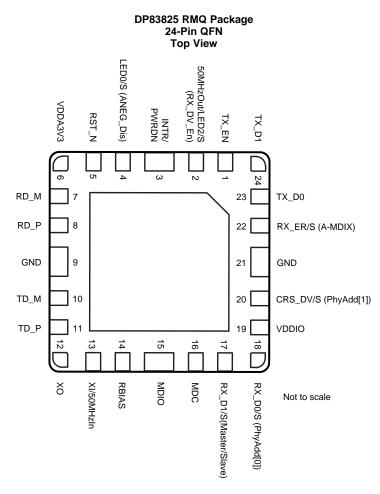

# 5 Pin Configuration and Functions

### **DP83825I Pin Functions**

| PIN           |   | <b>TYPF</b> <sup>(1)</sup>                                                                                                                                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.      |   | TTPE'                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|               |   | RMII Transmit Enable: TX_EN is active high signal and is presented on the rising edge of the TX_CLK. TX_EN indicates the presence of valid data inputs on TX_D [1:0]. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 50MHzOut/LED2 | 2 | Reset: I, PD, S<br>Active: O                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| INTR/PWRDN    | 3 | Reset: I, PU<br>Active: I, PU                                                                                                                                         | Interrupt / Power Down(default): The default function of this pin is power down.<br>Register access is required to configure this pin as an interrupt. In power-down<br>function, an active low signal on this pin places the device in power down mode. When<br>this pin is configured as an interrupt pin, this pin is asserted low when an interrupt<br>condition occurs. The pin has an open-drain output with a weak internal pullup ( $9.5K\Omega$ ).<br>Some applications may require an external pullup resistor. |  |  |

(1) The pin functions are defined below: Type I: Input Type O: Output Type I/O: Input/Output Type PD or PU: Internal Pulldown or Pullup Type S: Strap Configuration Pin

Copyright © 2018–2019, Texas Instruments Incorporated

DP83825I SNLS638A – DECEMBER 2018 – REVISED AUGUST 2019

www.ti.com

NSTRUMENTS

**Texas**

# DP83825I Pin Functions (continued)

| PIN        |     | TYPE <sup>(1)</sup>                            | DECODUCTION                                                                                                                                                                                                                                                                                                                                                  |  |  |

|------------|-----|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME       | NO. | ITPE''                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  |  |  |

| LED0       | 4   | Reset: I, PD, S<br>Active: O                   | LED0 : Activity Indication LED indicates transmit and receive activity in addition to the status of the Link. The LED is ON when Link is good. The LED blinks when the transmitter or receiver is active. This pin can also act as GPIO through register configuration.<br>This pin is at 3.3 V always and not linked to voltage supplied to VDDIO pin. This |  |  |

|            |     |                                                | is to avoid external components when operating PHY at VDDIO 1.8 V.                                                                                                                                                                                                                                                                                           |  |  |

| RST_N      | 5   | Reset: I, PU<br>Active: I, PU                  | RST_N: This pin is an active low reset input. Asserting this pin low for at least 1 $\mu$ s will force a reset process to occur. Initiation of reset causes strap pins to be re-scanned and resets all the internal registers of the PHY to default value.                                                                                                   |  |  |

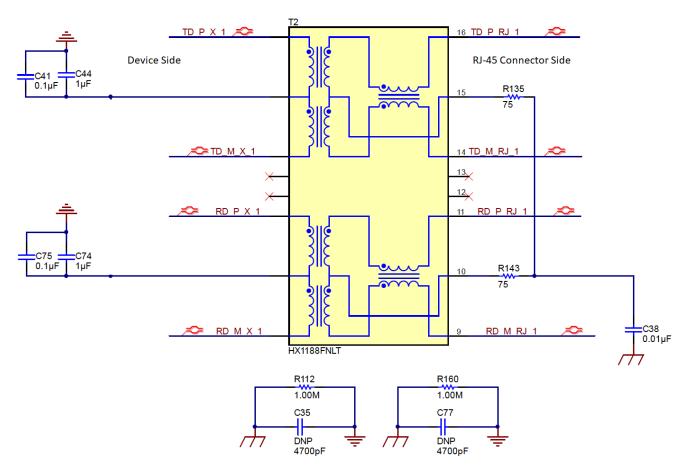

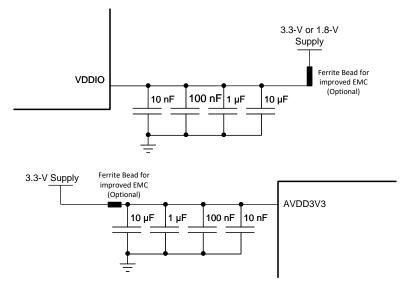

| VDDA3V3    | 6   | Power                                          | Input Analog Supply: 3.3 V. For decoupling capacitor requirements, refer to the <i>Application and Implementation</i> section.Figure 20                                                                                                                                                                                                                      |  |  |

| RD_M       | 7   | A                                              | Differential Receive Input (PMD): These differential inputs are automatically configured                                                                                                                                                                                                                                                                     |  |  |

| RD_P       | 8   | A                                              | to accept either 10BASE-Te, 100BASE-TX specific signaling mode                                                                                                                                                                                                                                                                                               |  |  |

| GND        | 9   | GND                                            | Ground: Connect to Ground                                                                                                                                                                                                                                                                                                                                    |  |  |

| TD_M       | 10  | A                                              | Differential Transmit Output (PMD): These differential outputs are configured to either                                                                                                                                                                                                                                                                      |  |  |

| TD_P       | 11  | A                                              | 10BASE-Te, 100BASE-TX signaling mode based on configuration chosen for PHY.                                                                                                                                                                                                                                                                                  |  |  |

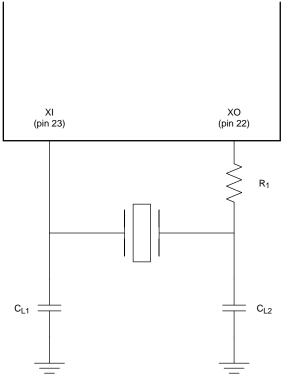

| ХО         | 12  | A                                              | Crystal Output: Reference Clock output. XO pin is used for crystal only. This pin shou be left floating when a CMOS-level oscillator is connected to XI.                                                                                                                                                                                                     |  |  |

|            |     |                                                | Crystal / Oscillator Input Clock                                                                                                                                                                                                                                                                                                                             |  |  |

| XI/50MHzIn | 13  | A                                              | RMII Master mode: 25-MHz ±50 ppm-tolerance crystal or oscillator clock                                                                                                                                                                                                                                                                                       |  |  |

|            |     |                                                | RMII Slave mode: 50-MHz ±50 ppm-tolerance CMOS-level oscillator clock                                                                                                                                                                                                                                                                                        |  |  |

| RBIAS      | 14  | A                                              | RBIAS value 6.49 K $\Omega$ 1% connected to ground                                                                                                                                                                                                                                                                                                           |  |  |

| MDIO       | 15  | Reset: I, PU-<br>10K<br>Active: IO, PU-<br>10K | Management Data I/O: Bidirectional management data signal that may be source by the management station or the PHY. This pin has internal pullup of 10 K $\Omega$ . External pullup of up to 2.2 K $\Omega$ can be added if needed                                                                                                                            |  |  |

| MDC        | 16  | Reset: I, PD<br>Active: I, PD                  | Management Data Clock: Synchronous clock to the MDIO serial management input/output data. This clock may be asynchronous to the MAC transmit and receive clocks. The maximum clock rate is 25 MHz. There is no minimum clock rate.                                                                                                                           |  |  |

| RX_D1      | 17  | Reset: I, PD, S<br>Active: O                   | RMII Receive Data: Symbols received on the cable are decoded and presented on these pins synchronous to reference clock. They contain valid data when RX_DV is asserted.                                                                                                                                                                                     |  |  |

| RX_D0      | 18  | Reset: I, PD, S<br>Active: O                   | RMII Receive Data: Symbols received on the cable are decoded and presented on these pins synchronous to reference clock. They contain valid data when RX_DV is asserted.                                                                                                                                                                                     |  |  |

| VDDIO      | 19  | Power                                          | I/O Supply : 3.3 V/1.8 V. For decoupling capacitor requirements, refer to the <i>Application</i> and <i>Implementation</i> section.                                                                                                                                                                                                                          |  |  |

| CRS_DV     | 20  | Reset: I, PD, S<br>Active: O                   | Carrier Sense / Receive Data Valid: This pin combines the RMII Carrier and Receive Data Valid indications.                                                                                                                                                                                                                                                   |  |  |

| GND        | 21  | GND                                            | Ground pin                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RX_ER      | 22  | Reset: I, PD, S<br>Active: O                   | RMII Receive Error: This pin indicates an error symbol has been detected within a received packet in RMII mode. RX_ER is asserted high synchronously to the rising edge of the reference clock. This pin is not required to be used by the MAC in RMII because the PHY will automatically corrupting data on a receive error.                                |  |  |

| TX_D0      | 23  | Reset: I, PD<br>Active: I, PD                  | RMII Transmit Data: TX_D[1:0] received from the MAC and shall be synchronous to the                                                                                                                                                                                                                                                                          |  |  |

| TX_D1      | 24  | Reset: I, PD<br>Active: I, PD                  | rising edge of the reference clock.                                                                                                                                                                                                                                                                                                                          |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>(

|                                                                  | PARAMETER          | MIN  | MAX | UNIT |

|------------------------------------------------------------------|--------------------|------|-----|------|

| Analog supply voltage                                            | AVDD3V3            | -0.3 | 4   | V    |

| Analog supply voltage       //////////////////////////////////// | VDDIO3V3           | -0.3 | 4   | V    |

|                                                                  | VDDIO1V8           | -0.3 | 2.1 | V    |

| Junction Temperature                                             | Tj                 |      | 105 | °C   |

| Storage Temperature                                              | Tstg               | -65  | 150 | °C   |

| MDI pins                                                         | TD-, TD+, RD-, RD+ | -0.3 | 4   | V    |

| MAC interface pins                                               |                    | -0.3 | 4   | V    |

| SMI interface pins                                               |                    | -0.3 | 4   | V    |

| XI                                                               |                    | -0.3 | 4   | V    |

| Reset                                                            |                    | -0.3 | 4   | V    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

| PARAMETER                                                     | DEFINITION                            | MIN MAX | UNIT |

|---------------------------------------------------------------|---------------------------------------|---------|------|

| Human-body                                                    | All Pins ( except MDI)                | ±1.5    | kV   |

| model (HBM), per<br>ANSI/ESDA/JEDE<br>C JS-001 <sup>(1)</sup> | MDI ( Media Dependent Interface) pins | ±5      | kV   |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing withless than 500-V HBM is possible with the necessary precautions.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                              | PARAMETER                                                                   | MIN             | TYP     | MAX             | UNIT |

|----------------------------------------------|-----------------------------------------------------------------------------|-----------------|---------|-----------------|------|

| Analog supply voltage                        | AVDD3V3                                                                     | 3               | 3.3     | 3.6             | V    |

|                                              | VDDIO3V3                                                                    | 3               | 3.3     | 3.6             | V    |

| IO supply voltage                            | VDDIO1V8                                                                    | 1.62            | 1.8     | 1.98            | V    |

| Operating Free Air<br>Temperature (DP83825I) | Та                                                                          | -40             | 25      | 85              | С    |

| Pins                                         | TX_EN, TX_D0, TX_D1, RX_D0, RX_D1, RX_DV, RX_ER, MDIO, MDC, INT/PWDN, RESET | VDDIO-10%       | VDDIO   | VDDIO+10<br>%   | V    |

| Pins                                         | XI Osciliator Input                                                         | VDDIO-10%       | VDDIO   | VDDIO+10<br>%   | V    |

| Pins                                         | LED0                                                                        | AVDD3V3-<br>10% | AVDD3V3 | AVDD3V3+<br>10% | V    |

# 6.4 Thermal Information

|                       | THERMAL METRIC(1)                                                  |      | UNIT |

|-----------------------|--------------------------------------------------------------------|------|------|

| $R_{	ext{	heta}JA}$   | R <sub>0JA</sub> Junction-to-ambient thermal resistance 5          |      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                          | 49.6 | °C/W |

| R <sub>0JC(bot)</sub> | R <sub>0JC(bot)</sub> Junction-to-case (bottom) thermal resistance |      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                               | 2.3  | °C/W |

| Y <sub>JT</sub>       | Junction-to-top characterization parameter                         | 28.5 | °C/W |

| Y <sub>JB</sub>       | Junction-to-board characterization parameter                       | 14.9 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Copyright © 2018–2019, Texas Instruments Incorporated

SNLS638A - DECEMBER 2018 - REVISED AUGUST 2019

www.ti.com

**ISTRUMENTS**

**Texas**

# 6.5 Electrical Characteristics

over operating free-air temperature range with VDDA = 3.3V (unless otherwise noted) <sup>(1)</sup>

|                  | PARAMETER                           | TEST CONDITIONS               | MIN TYP | MAX | UNIT |

|------------------|-------------------------------------|-------------------------------|---------|-----|------|

| IEEE Tx C        | CONFORMANCE (100BaseTx)             |                               |         |     |      |

|                  | Differential Output Voltage         | 100 Base Tx idle transmission | 1.0     |     | V    |

| IEEE Tx C        | CONFORMANCE (10BaseTe)              |                               |         |     |      |

|                  | Differential Voltage                | 10BaseTe data transmission    | 1.75    |     | V    |

|                  | CONSUMPTION ( Power Optimised Mode  | e)                            |         |     |      |

| I(AVDD3<br>V3)   | RMII Master (100BaseTx)             | Traffic = 50%                 | 37.5    |     | mA   |

| I(AVDD3<br>V3)   | RMII Slave (100BaseTx)              | Traffic = 50%                 | 37.5    |     | mA   |

| I(VDDIO<br>=3V3) | RMII Master (100BaseTx)             | Traffic = 50%                 | 7.5     |     | mA   |

| I(VDDIO<br>=3V3) | RMII Slave (100BaseTx)              | Traffic = 50%                 | 3.5     |     | mA   |

| I(VDDIO<br>=1V8) | RMII Master (100BaseTx)             | Traffic = 50%                 | 4.5     |     | mA   |

| I(VDDIO<br>=1V8) | RMII Slave (100BaseTx)              | Traffic = 50%                 | 1.6     |     | mA   |

| POWER C          | CONSUMPTION ( Cable Reach Optimised | i Mode)                       |         | +   |      |

| I(AVDD3<br>V3)   | RMII Master (100BaseTx)             | Traffic = 50%                 | 41      |     | mA   |

| I(AVDD3<br>V3)   | RMII Master (100BaseTx)             | Traffic = 100%                | 41      | 50  | mA   |

| I(AVDD3<br>V3)   | RMII Master (10BaseTe)              | Traffic = 50%                 | 28      |     | mA   |

| I(AVDD3<br>V3)   | RMII Master (10BaseTe)              | Traffic = 100%                | 32      | 40  | mA   |

| I(AVDD3<br>V3)   | RMII Slave (100BaseTx)              | Traffic = 50%                 | 41      | 50  | mA   |

| I(AVDD3<br>V3)   | RMII Slave (100BaseTx)              | Traffic = 100%                | 41      | 50  | mA   |

| I(AVDD3<br>V3)   | RMII Slave (10BaseTe)               | Traffic = 50%                 | 28      |     | mA   |

| I(AVDD3<br>V3)   | RMII Slave (10BaseTe)               | Traffic = 100%                | 32      | 40  | mA   |

| I(VDDIO<br>=3V3) | RMII Master (100BaseTx)             | Traffic = 50%                 | 7.5     |     | mA   |

| I(VDDIO<br>=3V3) | RMII Master (100BaseTx)             | Traffic = 100%                | 10      | 14  | mA   |

| I(VDDIO<br>=3V3) | RMII Master (10BaseTe)              | Traffic = 50%                 | 6.5     |     | mA   |

| I(VDDIO<br>=3V3) | RMII Master (10BaseTe)              | Traffic = 100%                | 7.5     | 12  | mA   |

| I(VDDIO<br>=3V3) | RMII Slave (100BaseTx)              | Traffic = 50%                 | 3.5     |     | mA   |

| I(VDDIO<br>=3V3) | RMII Slave (100BaseTx)              | Traffic = 100%                | 5       | 8   | mA   |

| I(VDDIO<br>=3V3) | RMII Slave (10BaseTe)               | Traffic = 50%                 | 2.5     | 6   | mA   |

| I(VDDIO<br>=3V3) | RMII Slave (10BaseTe)               | Traffic = 100%                | 2.5     | 6   | mA   |

| I(VDDIO<br>=1V8) | RMII Master (100BaseTx)             | Traffic = 50%                 | 4       | 14  | mA   |

(1) Ensured by production test, characterization or design

# **Electrical Characteristics (continued)**

over operating free-air temperature range with VDDA = 3.3V (unless otherwise noted) <sup>(1)</sup>

|                     | PARAMETER                                 | TEST CONDITIONS                          | MIN | TYP  | MAX | UNIT |

|---------------------|-------------------------------------------|------------------------------------------|-----|------|-----|------|

| I(VDDIO<br>=1V8)    | RMII Master (100BaseTx)                   | Traffic = 100%                           |     | 5.5  | 14  | mA   |

| I(VDDIO<br>=1V8)    | RMII Master (10BaseTe)                    | Traffic = 50%                            |     | 4    |     | mA   |

| I(VDDIO<br>=1V8)    | RMII Master (10BaseTe)                    | Traffic = 100%                           |     | 4    | 14  | mA   |

| I(VDDIO<br>=1V8)    | RMII Slave (100BaseTx)                    | Traffic = 50%                            |     | 1.5  |     | mA   |

| I(VDDIO<br>=1V8)    | RMII Slave (100BaseTx)                    | Traffic = 100%                           |     | 2.5  | 6   | mA   |

| I(VDDIO<br>=1V8)    | RMII Slave (10BaseTe)                     | Traffic = 50%                            |     | 1    |     | mA   |

| I(VDDIO<br>=1V8)    | RMII Slave (10BaseTe)                     | Traffic = 100%                           |     | 1    | 6   | mA   |

| POWER               | CONSUMPTION (Low Power Modes)             |                                          |     |      |     |      |

|                     | 100 BaseTx EEE mode                       | 100 BaseTx link in EEE mode with LPIs ON |     | 15.5 |     | mA   |

|                     | Deep Power Down                           |                                          |     | 3.5  |     | mA   |

| I(AVDD=             | IEEE Power Down                           |                                          |     | 4    |     | mA   |

| 3V3)                | Active Sleep                              |                                          |     | 11   |     | mA   |

|                     | Active but not Link                       |                                          |     | 37   |     | mA   |

|                     | RESET                                     |                                          |     | 5.5  |     | mA   |

|                     | 100 BaseTx EEE mode                       |                                          |     | 2    |     | mA   |

|                     | Deep Power Down                           |                                          |     | 2.5  |     | mA   |

| I(VDDIO             | IEEE Power Down                           |                                          |     | 2    |     | mA   |

| =3V3)               | Active Sleep                              |                                          |     | 5    |     | mA   |

|                     | Active but not Link                       |                                          |     | 5    |     | mA   |

|                     | RESET                                     |                                          |     | 2.5  |     | mA   |

|                     | 100 BaseTx EEE mode                       |                                          |     | 2    |     | mA   |

|                     | Deep Power Down                           |                                          |     | 1.5  |     | mA   |

| I(VDDIO             | IEEE Power Down                           |                                          |     | 1.5  |     | mA   |

| =1V8)               | Active Sleep                              |                                          |     | 3    |     | mA   |

|                     | Active but not Link                       |                                          |     | 3    |     | mA   |

|                     | RESET                                     |                                          |     | 1.5  |     | mA   |

| BOOTST              | RAP DC CHARACTERISTICS (2 Level)          |                                          |     |      | T   |      |

| V <sub>IH_3v3</sub> | High Level Bootstrap Threshold : 3V3      |                                          | 1.3 |      |     | V    |

| V <sub>IL_3v3</sub> | Low Level Bootstrap Threshold : 3V3       |                                          |     |      | 0.6 | V    |

| V <sub>IH_1v8</sub> | High Level Bootstrap Threshold:1V8        |                                          | 1.3 |      |     | V    |

| V <sub>IL_1v8</sub> | Low Level Bootstrap Threshold :1V8        |                                          |     |      | 0.6 | V    |

| Crystal o           |                                           |                                          |     |      |     |      |

|                     | Load Capacitance                          |                                          |     | 15   | 30  | pF   |

| ю                   | ·                                         | · · · · · · · · · · · · · · · · · · ·    |     |      |     |      |

|                     | V <sub>IH</sub> High Level Input Voltage  | VDDIO= 3V3+/- 10%                        | 1.7 |      |     | V    |

| 21/2                | V <sub>IL</sub> Low Level Input Voltage   | VDDIO= 3V3+/- 10%                        |     |      | 0.8 | V    |

| 3V3                 | V <sub>OH</sub> High Level Output Voltage | I <sub>oH</sub> = -2mA, VDDIO=3V3 +/-10% | 2.4 |      |     | V    |

|                     | V <sub>OL</sub> Low Level Output Voltage  | I <sub>oL</sub> = 2mA, VDDIO=3V3 +/- 10% |     | -    | 0.4 | V    |

STRUMENTS

EXAS

# **Electrical Characteristics (continued)**

over operating free-air temperature range with VDDA = 3.3V (unless otherwise noted) <sup>(1)</sup>

| PARAMETER |                                           | TEST CONDITIONS                          | MIN            | TYP     | MAX            | UNIT  |

|-----------|-------------------------------------------|------------------------------------------|----------------|---------|----------------|-------|

|           | V <sub>IH</sub> High Level Input Voltage  | VDDIO= 1V8+/- 10%                        | 0.65*VD<br>DIO |         |                | V     |

| 1V8       | V <sub>IL</sub> Low Level Input Voltage   | VDDIO= 1V8+/- 10%                        |                |         | 0.35*VD<br>DIO | V     |

|           | V <sub>OH</sub> High Level Output Voltage | I <sub>oH</sub> = -2mA, VDDIO=1V8 +/-10% | VDDIO-<br>0.45 |         |                | V     |

|           | V <sub>OL</sub> Low Level Output Voltage  | I <sub>oL</sub> = 2mA, VDDIO=1V8 +/- 10% |                |         | 0.45           | V     |

|           | lih (VIN=VCC)                             | T <sub>A</sub> =-40 TO 85C, VIN=VDDIO    |                |         | 15             | uA    |

|           | lil (VIN=GND)                             | T <sub>A</sub> =-40 TO 85C, VIN=GND      |                |         | 15             | uA    |

|           | lozh                                      | Tri State Output High Current            | -15            |         | 15             | uA    |

|           | lozl                                      | Tri State Output Low Current             | -15            |         | 15             | uA    |

|           | Cin (Input Capacitance)                   |                                          |                | 5       |                | pF    |

|           | R Pull Down                               |                                          | 8              | 10      | 13             | Kohms |

|           | R Pull UP                                 |                                          | 8              | 10      | 13             | Kohms |

|           | XI input osc clock pk-pk                  |                                          |                | VDDIO   |                | V     |

|           | XI input osc clock common mode            |                                          | V              | /DDIO/2 |                | V     |

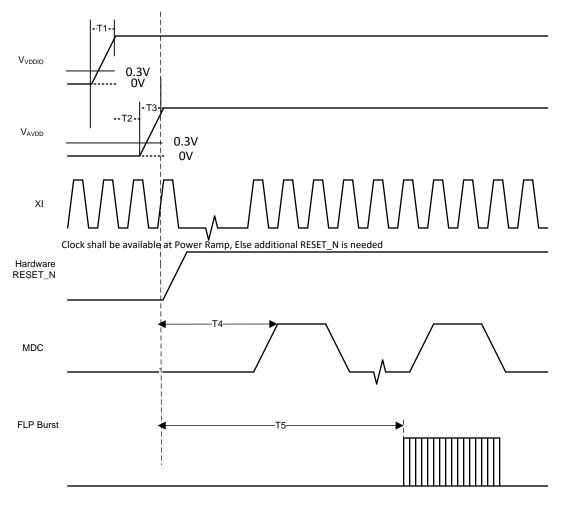

# 6.6 Timing Requirements

|          | PARAMETER                                                                                                           | MIN | NOM  | MAX  | UNIT    |

|----------|---------------------------------------------------------------------------------------------------------------------|-----|------|------|---------|

| POWER    | -UP TIMING                                                                                                          |     |      |      |         |

| T1       | Voltage Ramp Duration (0 to 100% VDDIO) <sup>(1)</sup>                                                              | 0.5 |      | 40   | ms      |

| T2       | Supply Sequencing AVDD followed by VDDIO                                                                            |     |      | 200  | ms      |

| Т3       | Voltage Ramp Duration ( 0 to 100% of AVDD)                                                                          | 0.5 |      | 40   | ms      |

| T4       | POR release time / Powerup to SMI ready: Post power-up stabilization time prior to MDC preamble for register access |     |      | 50   | ms      |

| T5       | Powerup to FLP                                                                                                      |     | 1500 |      | ms      |

| -        | Pedestal Voltage on AVDD, VDDIO before Power Ramp                                                                   |     |      | 0.3  | V       |

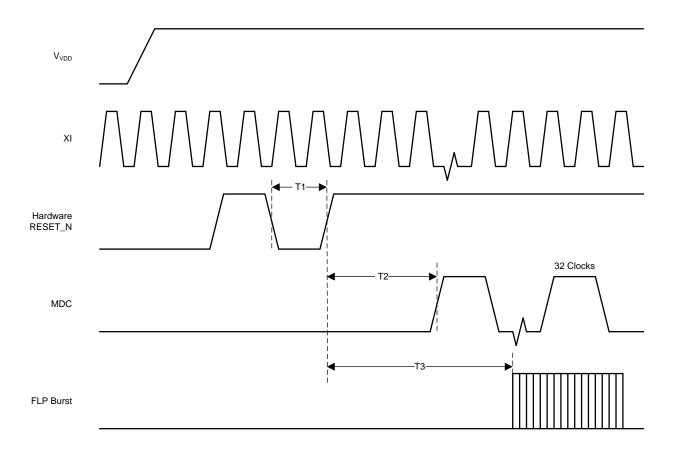

| RESET    |                                                                                                                     |     |      |      |         |

| T1       | RESET PULSE Width: Miminum Reset pulse width to be able to reset (w/o debouncing caps)                              | 25  |      |      | us      |

| T2       | Reset to SMI ready: Post reset stabilization time prior to MDC preamble for register access                         |     |      | 2    | ms      |

| ТЗ       | Reset to FLP                                                                                                        |     | 1500 |      | ms      |

|          | Reset to 100M signaling (strapped mode)                                                                             |     | 0.5  |      | ms      |

|          | Reset to RMII Master clock                                                                                          |     | 0.2  |      | ms      |

| 100M E   | EE timings                                                                                                          |     |      |      |         |

|          | Sleep time (Ts)                                                                                                     |     | 210  |      | us      |

|          | Quiet time (Tq)                                                                                                     |     | 20   |      | ms      |

|          | Refresh time (Tr)                                                                                                   |     | 200  |      | us      |

|          | Wake time (Tw_sys_tx)                                                                                               |     | 36   |      | us      |

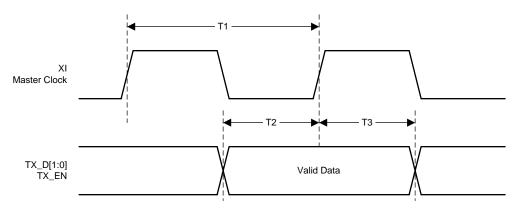

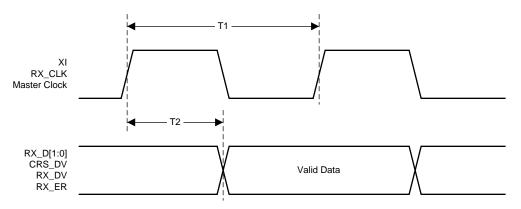

| RMII Ma  | Ister TIMING (100M)                                                                                                 |     |      |      |         |

|          | RMII Master Clock Period                                                                                            |     | 20   |      | ns      |

|          | RMII Master Clock Duty Cycle                                                                                        | 35  |      | 65   | %       |

| T2       | TX_D[1:0], TX_ER, TX_EN Setup to RMII Master Clock                                                                  | 4   |      |      | ns      |

| T3       | TX_D[1:0], TX_ER, TX_EN Hold from RMII Master Clock                                                                 | 2   |      |      | ns      |

| T4       | RX_D[1:0], RX_ER, CRS_DV Delay from RMII Master Clock rising edge                                                   | 4   | 10   | 14   | ns      |

| RMII SIa | ave TIMING (100M)                                                                                                   |     |      |      |         |

| T1       | Input Reference Clock Period                                                                                        |     | 20   |      | ns      |

|          | Reference Clock Duty Cycle                                                                                          | 35  | -    | 65   | %       |

| T2       | TX_D[1:0], TX_ER, TX_EN Setup to XI Clock rising <sup>(2)</sup>                                                     | 4   |      |      | ns      |

| T3       | TX_D[1:0], TX_ER, TX_EN Hold from XI Clock rising                                                                   | 2   |      |      | ns      |

| T4       | RX_D[1:0], RX_ER, CRS_DV Delay from XI Clock rising                                                                 | 4   |      | 14   | ns      |

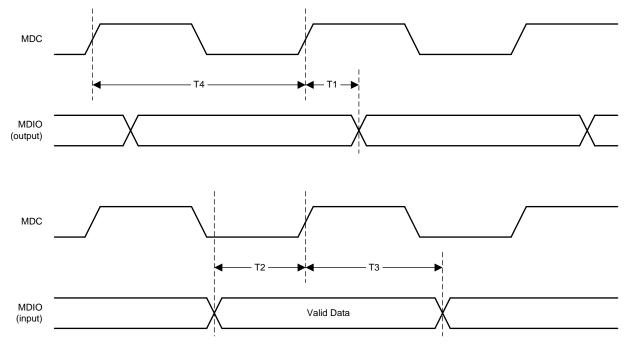

| SMI TIM  |                                                                                                                     | •   |      |      |         |

| T1       | MDC to MDIO (Output) Delay Time                                                                                     | 0   |      | 10   | ns      |

| T2       | MDIO (Input) to MDC Setup Time                                                                                      | 10  |      |      | ns      |

| T3       | MDIO (Input) to MDC Hold Time                                                                                       | 10  |      |      | ns      |

| T4       | MDC Frequency                                                                                                       | 10  | 2.5  | 20   | MHz     |

|          | T CLOCK TIMING (50M RMII Master Clock)                                                                              |     | 2.0  | 20   | 1411 12 |

|          | Frequency (PPM)                                                                                                     | -50 |      | 50   | ppm     |

|          | Duty Cycle                                                                                                          | 35  |      | 65   | ېر<br>% |

|          | Rise time                                                                                                           | 00  |      | 4000 | ps      |

|          | Fall Time                                                                                                           |     |      | 4000 |         |

|          |                                                                                                                     |     |      | 4000 | ps      |

|          | Jitter (Long Term)                                                                                                  |     |      |      | ps      |

|          | RefCLK to clock out delay with multiple resets                                                                      |     |      | 40   | ns      |

| INPUT    | CLOCK tolerance                                                                                                     |     |      |      |         |

Clock shall be available at power ramp. If Clock is provided after power ramp, external Reset of PHY is needed once clock is available

RMII Slave Output Timing default supports setup time upto 7.5 ns. For 7.5ns to 10.5ns, program register 0x0017.8 = 1, 0x0042=0x0014

# **Timing Requirements (continued)**

|            | PARAMETER                                                                                    | MIN | NOM  | MAX  | UNIT   |

|------------|----------------------------------------------------------------------------------------------|-----|------|------|--------|

|            | Rise / Fall Time                                                                             |     |      | 5    | ns     |

|            | Jitter Tolerance (Accumulated over 100,000 cycles)                                           |     |      | 1.75 | ns     |

|            | Duty Cycle                                                                                   | 40  |      | 60   | %      |

|            | input phase noise at 1KHz                                                                    |     |      | -98  | dBc/Hz |

|            | input phase noise at 10KHz                                                                   |     |      | -113 | dBc/Hz |

|            | input phase noise at 100KHz                                                                  |     |      | -113 | dBc/Hz |

|            | input phase noise at 1MHz                                                                    |     |      | -113 | dBc/Hz |

|            | input phase noise at 10MHz                                                                   |     |      | -113 | dBc/Hz |

| 50MHz      | Frequency Tolerance                                                                          | -50 |      | 50   | ppm    |

|            | Rise / Fall Time                                                                             |     |      | 5    | ns     |

|            | Jitter Tolerance (Accumulated over 100,000 cycles)                                           |     |      | 1.75 | ns     |

|            | Duty Cycle                                                                                   | 40  |      | 60   | %      |

|            | input phase noise at 1KHz                                                                    |     |      | -87  | dBc/Hz |

|            | input phase noise at 10KHz                                                                   |     |      | -107 | dBc/Hz |

|            | input phase noise at 100KHz                                                                  |     |      | -107 | dBc/Hz |

|            | input phase noise at 1MHz                                                                    |     |      | -107 | dBc/Hz |

|            | input phase noise at 10MHz                                                                   |     |      | -107 | dBc/Hz |

| LATENCY    | TIMING                                                                                       |     |      | ,    |        |

|            | Slave RMII Rising edge XI clock with assertion TX_EN to SSD symbol on MDI (100M)             |     | 105  |      | ns     |

| <b>T</b> . | Master RMII Rising edge clock with assertion TX_EN to SSD symbol on MDI (100M)               |     | 105  |      | ns     |

| Тх         | Slave RMII Rising edge XI clock with assertion TX_EN to SSD symbol on MDI (10M)              |     | 1350 |      | ns     |

|            | Master RMII Rising edge clock with assertion TX_EN to SSD symbol on MDI (10M)                |     | 1300 |      | ns     |

|            | SSD symbol on MDI to Slave RMII Rising edge of XI clock with assertion of CRS_DV (100M)      |     | 350  |      | ns     |

| Du         | SSD symbol on MDI to Master RMII Rising edge of Master clock with assertion of CRS_DV (100M) |     | 325  |      | ns     |

| Rx         | SSD symbol on MDI to Slave RMII Rising edge of XI clock with assertion of CRS_DV (10M)       |     | 2150 |      | ns     |

|            | SSD symbol on MDI to Master RMII Rising edge of Master clock with assertion of CRS_DV (10M)  |     | 2150 |      | ns     |

# 6.7 Timing Diagrams

Figure 1. Power-Up Timing

# **Timing Diagrams (continued)**

Figure 2. Reset Timing

# **Timing Diagrams (continued)**

# Figure 3. Serial Management Timing

# Figure 4. RMII Transmit Timing

# Figure 5. RMII Receive Timing

SNLS638A-DECEMBER 2018-REVISED AUGUST 2019

www.ti.com

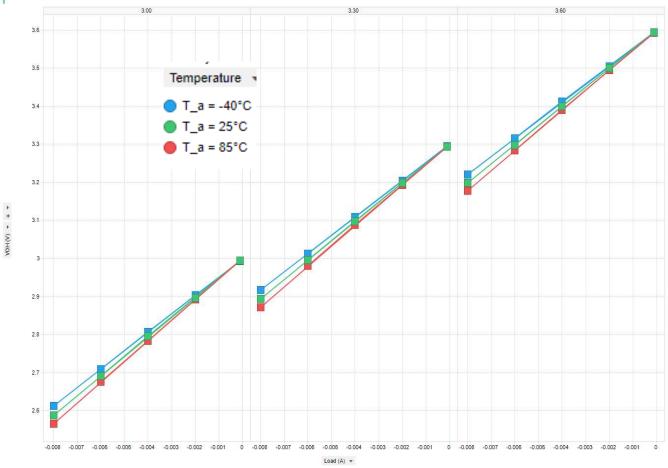

# 6.8 Typical Characteristics

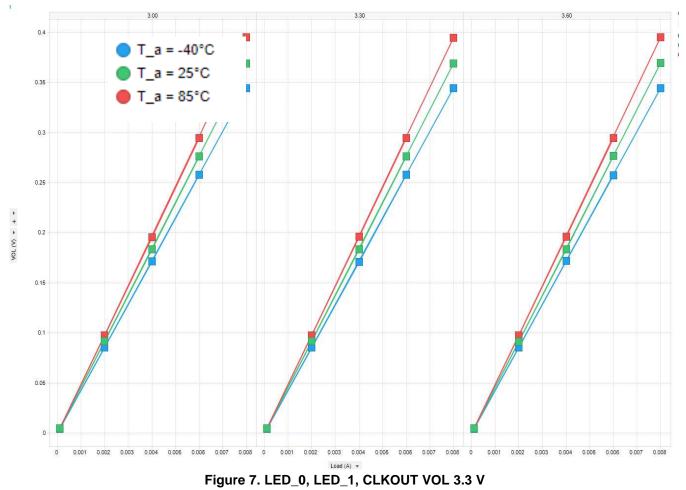

Figure 6. LED\_0, LED\_1, CLKOUT VOH 3.3 V

# **Typical Characteristics (continued)**

SNLS638A-DECEMBER 2018-REVISED AUGUST 2019

www.ti.com

ISTRUMENTS

EXAS

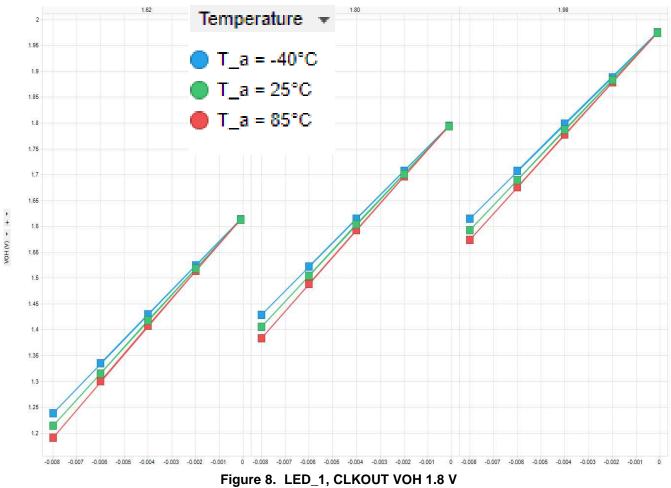

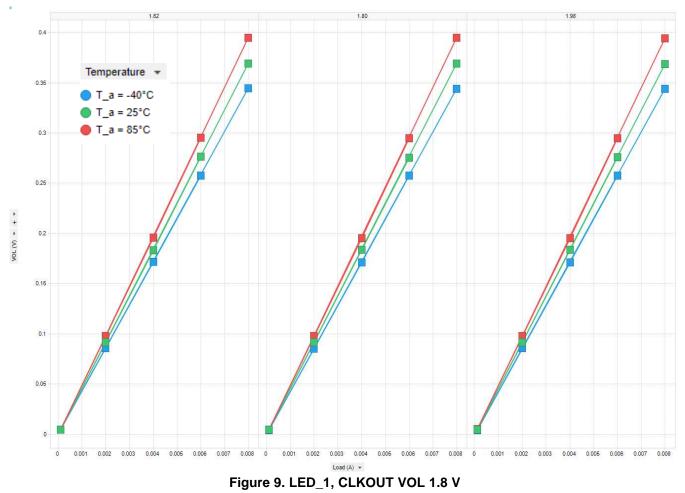

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# 7 Detailed Description

# 7.1 Overview

The DP83825I is a fully-featured single-port Physical Layer transceiver compliant to IEEE802.3 10BASE-Te and 100BASE-TX standards. The device supports the standard Reduced Media Independent Interface (RMII) for direct connection to Media Access Controller (MAC).

The device is designed for a single 3.3-V power supply with an integrated LDO to provide voltage rails needed for internal blocks. The device allows I/O voltage interfaces for 3.3 V or 1.8 V. Automatic supply configuration within the DP83825I allows for any combination of VDDIO supply and AVDD supply without the need for additional configuration settings.

The DP83825I uses mixed-signal processing to perform equalization, data recovery, and error correction to achieve robust operation over a CAT5e twisted-pair cable greater than 150 meters. DP83825I supports various Low Power features like Active Sleep, IEEE Power Down and Deep Power Down. It also supports Energy Efficient Ethernet and Wake-on-LAN.

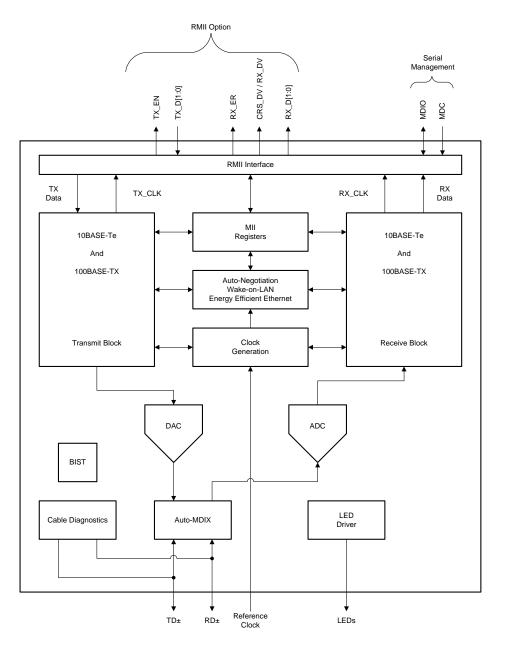

# 7.2 Functional Block Diagram

# 7.3 Feature Description

# 7.3.1 Auto-Negotiation (Speed / Duplex Selection)

Auto-Negotiation provides a mechanism for exchanging configuration information between the two ends of a link segment. This mechanism is implemented by exchanging Fast Link Pulses (FLP). FLPs are burst pulses that provide the information used to communicate the abilities between two devices at each end of a link segment. The DP83825I supports 100BASE-TX and 10BASE-Te modes of operation for Auto-Negotiation. Auto-Negotiation ensures that the highest common speed is selected based on the advertised abilities of the Link Partner and the local device. Auto-Negotiation can be enabled or disabled in hardware, using the bootstrap, or by register configuration, using bit[12] in the Basic Mode Control Register (BMCR, address 0x0000). For further details regarding Auto-Negotiation, refer to Clause 28 of the IEEE 802.3 specification.

Copyright © 2018–2019, Texas Instruments Incorporated

# **Feature Description (continued)**

## 7.3.2 Auto-MDIX Resolution

The DP83825I can determine if a "straight" or "crossover" cable is used to connect to the link partner. It can automatically re-assign channel A and B to establish link with the link partner. Auto-MDIX resolution precedes the actual Auto-Negotiation process that involves exchange of FLPs to advertise capabilities. Automatic MDI/MDIX is described in IEEE 802.3 Clause 40, section 40.8.2. It is not a required implementation for 10BASE-Te and 100BASE-TX. Auto-MDIX can also be used when operating the PHY in Forced modes.

Auto-MDIX can be enabled or disabled in hardware, using the hardware bootstrap, or by register configuration, using bit[15] of the PHY Control Register (PHYCR, address 0x0019). When Auto-MDIX is disabled, the PMA is forced to either MDI ("straight") or MDIX ("crossover"). Manual configuration of MDI or MDIX can also be accomplished using register configuration, using bit[14] of the PHYCR.

### 7.3.3 Energy Efficient Ethernet

### 7.3.3.1 EEE Overview

Energy Efficient Ethernet (EEE), defined by IEEE 802.3az, is a capability integrated into Layer 1 (Physical Layer) and Layer 2 (Data Link Layer) to operate in Low Power Idle (LPI) mode. In LPI mode, power is saved during periods of low packet utilization. EEE defines the protocol to enter and exit LPI mode without dropping the link or corrupting packets.

The DP83825I EEE supports 100-Mbps and 10-Mbps speeds. In 10BASE-Te operation, EEE operates with a reduced transmit amplitude that is fully interoperable with a 10BASE-T PHY.

# 7.3.3.2 EEE Negotiation

EEE is advertised during Auto-Negotiation. Auto-Negotiation is performed at power up, on management command, after link failure, or due to user intervention. EEE is supported if and only if both link partners advertise EEE capabilities. If EEE is not supported, all EEE functions are disabled and the MAC should not assert LPI. To advertise EEE capabilities, the PHY needs to exchange an additional formatted next page and unformatted next page in sequence.

EEE Negotiation can be activated using Register Access. IEEE 802.3az defines MMD3 and MMD7 as the locations for EEE control and status registers. The MMD3 registers 0x1014, 0x1001, 0x1016, and MMD7 registers 0x203C and 0x203D contain all the required controls and status indications for operating EEE. The Energy Efficient Ethernet Configuration Register #3 (EEECFG3, address 0x04D1) contains controls for EEE configuration bypass. By default, EEE capabilities are bypassed. To advertise EEE based on MMD3 and MMD7 registers, EEE capabilities bypass needs to be disabled (0x04D1.0 = 0, 0x04D1.3 = 0) and EEE Advertisement shall be enabled (MMD7 0x203C.1 = 1).

## 7.3.4 EEE for Legacy MACs Not Supporting 802.3az

The device can be configured to initiate LPI signaling (Idle and Refresh) through register programming as well. This feature enables the system to perform EEE even when the MAC used is not supporting EEE. In this mode, responsibility of enabling and disabling LPI signaling lies on the Host Controller Application. While the DP838251 is in LPI signaling mode, this application will move the DP838251 into active mode before sending any data over the MAC interface. The DP838251 does not have buffering capability to store the data while in LPI signaling mode. To enable EEE through register configuration, the following registers must be configured:

- 1. Enable EEE capabilities by writing 0x04D1.0 = 0, 0x04D1.3 = 0

- 2. Advertise EEE capabilities during auto-negotiation by writing (MMD7 0x203C.1 = 1)

- 3. Renegotiate the link by writing 0x0000.9 = 1

- 4. Forced Tx LPI idles by writing 0x04D1.12 = 1

- 5. Write 0x04D1.12=0 to stop transmitting LPI Idles

# Feature Description (continued)

## 7.3.5 Wake-on-LAN Packet Detection

Wake-on-LAN (WoL) provides a mechanism to detect specific frames and notify the connected controller through either register status change, GPIO indication, or an interrupt flag. The WoL feature within the DP838251 allows for connected devices residing above the Physical Layer to remain in a low power state until frames with the qualifying credentials are detected. Supported WoL frame types include: Magic Packet and Magic Packet with Secure-ON Match. When a qualifying WoL frame is received, the DP838251 WoL logic circuit is able to generate a user-defined event (either pulses or level change) through any of the GPIO pins or a status interrupt flag to inform a connected controller that a wake event has occurred. Additionally, the DP838251 includes a CRC Gate to prevent invalid packets from triggering a wake-up event. The Wake-on-LAN feature includes:

- Identification of WoL frames in all supported speeds (100BASE-TX and 10BASE-Te).

- Wake-up interrupt generation upon reception of a WoL frame.

- CRC error checking of WoL frames to prevent interrupt generation from invalid frames.

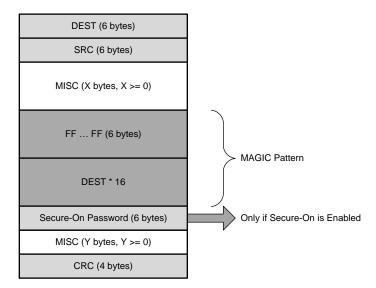

# 7.3.5.1 Magic Packet Structure

When configured for Magic Packet detection, the DP83825I scans all incoming frames addressed to the node for a specific data sequence. This sequence identifies the frame as a Magic Packet frame.

A Magic Packet frame must also meet the basic requirements for the LAN technology chosen, such as SOURCE ADDRESS, DESTINATION ADDRESS (which may be the receiving station's IEEE address or a BROADCAST ADDRESS), and CRC.

The specific Magic Packet sequence consists of 16 duplications of the MAC address of this node, with no breaks or interruptions, followed by Secure-ON password if security is enabled. This sequence can be located anywhere within the packet, but must be preceded by a synchronization stream. The synchronization stream is defined as 6 bytes of 0xFF.

Figure 10. Magic Packet Structure

## 7.3.5.2 Magic Packet Example

The following is an example Magic Packet for a Destination Address of 11h 22h 33h 44h 55h 66h and a secureon password 2Ah 2Bh 2Ch 2Dh 2Eh 2Fh:

DESTINATION

SOURCE

MISC

FF

FF

FF

FF

FF

11

22

33

44

55

66

11

22

33

44

55

66

12

23

44

55

66

11

22

33

44

55

66

12

23

44

55

66

11

22

33

44

55

66

12

23

44

55

66

11

22

33

44

55

66

12

23

44

55

66

11

22

33

44

55

66

12

23

44

55

66

11

22

33

44

55

66

12

23

44

55

66

11

22

33

44

55

66

12

23

44

55

66

11

22

33

44

55

66

11

22

33

44

55

# Feature Description (continued)

### 7.3.5.3 Wake-on-LAN Configuration and Status

Wake-on-LAN functionality is configured through the Receive Configuration Register (RXFCFG, address 0x04A0). Wake-on-LAN status is reported in the Receiver Status Register (RXFS, address 0x04A1). The Wake-on-LAN interrupt flag configuration and status is located in the MII Interrupt Status Register #2 (MISR2, address 0x0013).

### 7.3.6 Low Power Modes

The DP83825I supports three Low Power Modes. This section discusses the principles behind these low power modes and configuration to enable them.

### 7.3.6.1 Active Sleep

When the DP83825I enters into Active Sleep mode, all internal circuitry shuts down in the PHY except for the SMI and energy detection circuitry on the TD± and RD± pins. In this mode, the DP83825 sends out NLPs every 1.4 seconds to wake up the link partner. Automatic power up occurs when a link partner is detected.

Active Sleep is enabled by setting bits[14:12] = 0b110 in the PHY Specific Control Register (PHYSCR, address 0x0011).

## 7.3.7 IEEE Power Down

IEEE Power Down shuts down all PHY circuitry except the SMI and internal clock circuitry.

IEEE Power Down can be activated by either register access or through the INTR/PWRDN pin when the pin is configured for power-down function.

To enable IEEE Power Down through the INTR/PWRDN pin, the pin must be driven LOW to ground.

To enable IEEE Power Down through the SMI, set bit[11] = 1 in the Basic Mode Control Register (BMCR, address 0x0000).

## 7.3.8 Deep Power Down

Deep Power Down shuts down all PHY circuitry except the SMI. In this mode, the PHY PLL is shut-down to further reduce power consumption.

Deep Power Down is activated by first enabling IEEE Power Down (from either the SMI or INT/PWDN\_N pin) and then setting bit[2] = 1 in the Deep Power Down Control Register (DPDWN, address 0x0428).

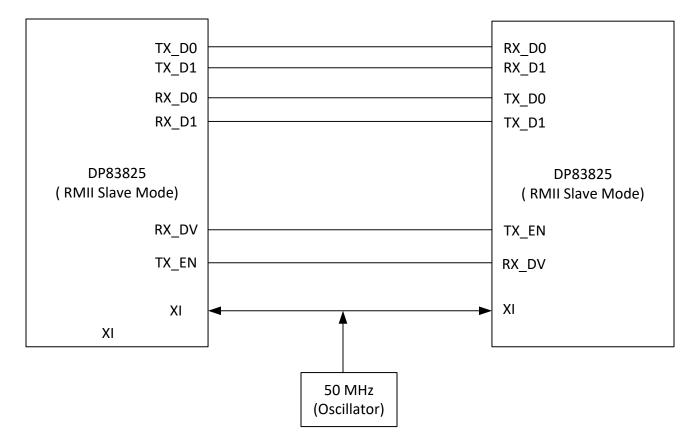

### 7.3.9 RMII Repeater Mode

The DP83825I provides an option to enable repeater mode functionality to extend the cable reach in unmanaged mode (without the need of additional register configuration). Two DP83825I can be connected in backto-back mode without any external configuration. It provides a Hardware Strap to configure the CRS\_DV pin of RMII interface to RX\_DV pin for back-to-back operation. Figure 11 shows the RMII pin connection that can enable DP83825I Repeater mode. If using managed mode, external Reset to both PHYs will be triggered at the same time.

# Feature Description (continued)

Figure 11. RMII Repeater Mode

# Feature Description (continued)

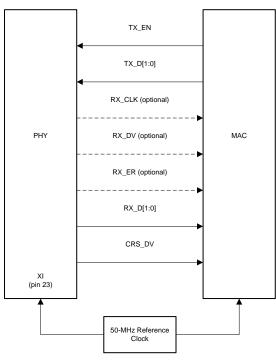

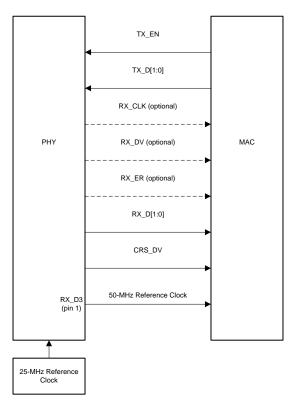

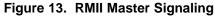

## 7.3.10 Reduced Media Independent Interface (RMII)

The DP83825I incorporates the Reduced Media Independent Interface (RMII) as specified in the RMII specification v1.2. The purpose of this interface is to provide a reduced pin count alternative to the IEEE 802.3 MII as specified in Clause 22. Architecturally, the RMII specification provides an additional reconciliation layer on either side of the MII, but can be implemented in the absence of an MII. The DP83825I offers two types of RMII operations: RMII Slave and RMII Master. In RMII Master operation, the DP83825I operates off either a 25-MHz CMOS-level oscillator connected to XI pin or a 25-MHz crystal connected across XI and XO pins. A 50-MHz output clock referenced from DP83825I can be connected to the MAC. In RMII Slave operation, the DP83825I operates off of a 50-MHz CMOS-level oscillator connected to the XI pin and shares the same clock as the MAC. Alternatively, in RMII Slave mode, the PHY can run from 50MHz clock provided by the Host MAC.

The RMII specification has the following characteristics:

- Supports 100BASE-TX and 10BASE-Te.

- Single clock reference sourced from the MAC to PHY (or from an external source)

- Provides independent 2-bit wide transmit and receive data paths

- Uses CMOS signal levels, the same levels as the MII interface

In this mode, data transfers are two bits for every clock cycle using the internal 50-MHz reference clock for both transmit and receive paths.

The RMII signals are summarized in Table 1:

### Table 1. RMII Signals

| FUNCTION                | PINS      |

|-------------------------|-----------|

| Receive Data Lines      | TX_D[1:0] |

| Transmit Data Lines     | RX_D[1:0] |

| Receive Control Signal  | TX_EN     |

| Transmit Control Signal | CRS_DV    |

Data on TX\_D[1:0] are latched at the PHY with reference to the clock edges on the XI pin. Data on RX\_D[1:0] are latched at the MAC with reference to the same clock edges on the XI pin.

In addition, CRX\_DV can be configured as RX\_DV signal. It allows a simpler method of recovering received data without the need to separate RX\_DV from the CRS\_DV indication.

### 7.3.11 Serial Management Interface

The Serial Management Interface provides access to the DP83825I internal register space for status information and configuration. The SMI is compatible with IEEE 802.3 clause 22 and clause 45. The implemented register set consists of the registers required by the IEEE 802.3 plus several others to provide additional visibility and controllability of the DP83825I.

The SMI includes the management clock (MDC) and the management input/output data pin (MDIO). MDC is sourced by the external management entity, also called Station (STA), and can run at a maximum clock rate of 25 MHz. MDC is not expected to be continuous, and can be turned off by the external management entity when the bus is idle.

MDIO is sourced by the external management entity and by the PHY. The data on the MDIO pin is latched on the rising edge of the MDC. MDIO pin requires a pullup resistor (2.2 K $\Omega$  or 1.5K $\Omega$ ), which pulls MDIO high during IDLE and turnaround.

Up to 4 PHYs can share a common SMI bus. To distinguish between the PHYs, during power up or hardware reset, the DP83825I latches the Phy\_Address[1:0] configuration pins to determine its address.

The management entity must not start an SMI transaction in the first cycle after power up or hardware reset. To maintain valid operation, the SMI bus must remain inactive at least one MDC cycle after reset is deasserted. In normal MDIO transactions, the register address is taken directly from the management-frame reg\_addr field, thus allowing direct access to 32 16-bit registers (including those defined in IEEE 802.3 and vendor-specific). The data field is used for both reading and writing. The Start code is indicated by a <01> pattern. This pattern makes sure that the MDIO line transitions from the default idle line state. Turnaround is defined as an idle bit time inserted between the Register Address field and the Data field. To avoid contention during a read transaction, no device may actively drive the MDIO signal during the first bit of turnaround. The addressed DP83825I drives the MDIO with a zero for the second bit of turnaround and follows this with the required data.

For write transactions, the station-management entity writes data to the addressed DP83825I, thus eliminating the requirement for MDIO Turnaround. The turnaround time is filled by the management entity by inserting <10>.

| SMI PROTOCOL    | <idle><start><op code=""><phy address=""><reg addr=""><turnaround><data><idle></idle></data></turnaround></reg></phy></op></start></idle> |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Read Operation  | <idle>&lt;01&gt;&lt;10&gt;<aaaaa><rrrr><z0><xxxx xxxx=""><idle></idle></xxxx></z0></rrrr></aaaaa></idle>                                  |

| Write Operation | <idle>&lt;01&gt;&lt;01&gt;<aaaaa><rrrr>&lt;10&gt;<xxxx xxxx=""><idle></idle></xxxx></rrrr></aaaaa></idle>                                 |

### Table 2. SMI Protocol

## 7.3.11.1 Extended Register Space Access

The DP83825I SMI function supports read and write access to the extended register set using the Register Control Register (REGCR, address 0x000D), the Data Register (ADDAR, address 0x000E), and the MDIO Manageable Device (MMD) indirect method defined in IEEE 802.3ah draft for Clause 22 for accessing the Clause 45 extended register set.

The standard register set, MDIO registers 0 to 31, is accessed using the normal direct-MDIO access or the indirect method, except for register REGCR and register ADDAR, which are accessed only using the normal MDIO transaction. The SMI function will ignore indirect access to these registers.

REGCR is the MMD access control. In general, register REGCR[4:0] is the device address DEVAD that directs any accesses of the ADDAR register to the appropriate MMD.

The DP83825I supports three MMD device addresses:

- 1. The Vendor-Specific device address DEVAD[4:0] = 11111 is used for general MMD register accesses.

- 2. DEVAD[4:0] = 00011 is used for Energy Efficient Ethernet MMD register accesses. Register names for registers accessible at this device address are preceded by MMD3.

- 3. DEVAD[4:0] = 00111 is used for Energy Efficient Ethernet MMD registers accesses. Register names for registers accessible at this device address are preceded by MMD7.

All accesses through register REGCR and ADDAR must use the correct DEVAD. Transactions with other DEVAD are ignored. REGCR[15:14] holds the access function: address (00), data with no post increment (01), data with post increment on read and writes (10) and data with post increment on writes only (11).

- ADDAR is the address/data MMD register. ADDAR is used in conjunction with REGCR to provide the access

to the extended register set. If register REGCR[15:14] is (00), then ADDAR holds the address of the extended

address space register. Otherwise, ADDAR holds the data as indicated by the contents of its address

register. When REGCR[15:14] is set to (00), accesses to register ADDAR modify the extended register set

address register. This address register must always be initialized in order to access any of the registers within

the extended register set.

- When REGCR[15:14] is set to (01), accesses to register ADDAR access the register within the extended register set selected by the value in the address register.

- When REGCR[15:14] is set to (10), access to register ADDAR access the register within the extended register set selected by the value in the address register. After that access is complete, for both reads and writes, the value in the address register is incremented.

- When REGCR[15:14] is set to (11), access to register ADDAR access the register within the extended register set selected by the value in the address register. After that access is complete, for write access only, the value in the address register is incremented. For read accesses, the value of the address register remains unchanged.

The following sections describe how to perform operations on the extended register set using register REGCR and ADDAR. The descriptions use the device address for general MMD register accesses (DEVAD[4:0] = 11111). For register accesses to the MMD3 or MMD7 registers the corresponding device address would be used.

SNLS638A - DECEMBER 2018 - REVISED AUGUST 2019

www.ti.com

## 7.3.11.2 Write Address Operation

To set the address register:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Write the register address to register ADDAR.

Subsequent writes to register ADDAR (step 2) continue to write the address register.

# 7.3.11.3 Read Address Operation

To read the address register:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Read the register address from register ADDAR.

Subsequent reads to register ADDAR (step 2) continue to read the address register.

# 7.3.11.4 Write (No Post Increment) Operation

To write a register in the extended register set:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Write the desired register address to register ADDAR.

- 3. Write the value 0x401F (data, no post increment function field = 01, DEVAD = 31) to register REGCR.

- 4. Write the content of the desired extended register set to register ADDAR.

Subsequent writes to register ADDAR (step 4) continue to rewrite the register selected by the value in the address register.

# NOTE

Steps (1) and (2) can be skipped if the address register was previously configured.

## 7.3.11.5 Read (No Post Increment) Operation

To read a register in the extended register set:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Write the desired register address to register ADDAR.

- 3. Write the value 0x401F (data, no post increment function field = 01, DEVAD = 31) to register REGCR.

- 4. Read the content of the desired extended register set in register ADDAR.

Subsequent reads to register ADDAR (step 4) continue to reading the register selected by the value in the address register.

# NOTE

Steps (1) and (2) can be skipped if the address register was previously configured.

# 7.3.11.6 Write (Post Increment) Operation

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Write the desired register address to register ADDAR.

- 3. Write the value 0x801F (data, post increment function field = 10, DEVAD = 31) or the value 0xC01F (data, post increment on writes function field = 11, DEVAD = 31) to register REGCR.

- 4. Write the content of the desired extended register set to register ADDAR.

Subsequent writes to register ADDAR (step 4) write the next higher addressed data register selected by the value of the address register; the address register is incremented after each access.

# 7.3.11.7 Read (Post Increment) Operation

To read a register in the extended register set and automatically increment the address register to the next higher value following the write operation:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Write the desired register address to register ADDAR.

- 3. Write the value 0x801F (data, post increment function field = 10, DEVAD = 31) to register REGCR.

- 4. Read the content of the desired extended register set in register ADDAR.

Subsequent reads to register ADDAR (step 4) read the next higher addressed data register selected by the value of the address register; the address register is incremented after each access.

# 7.3.11.8 Example Write Operation (No Post Increment)

The following example will demonstrate a write operation with no post increment. In this example, the MAC impedance will be adjusted to 99.25  $\Omega$  using the IO MUX GPIO Control Register (IOCTRL, address 0x0461).

- 1. Write the value 0x001F to register 0x000D.

- 2. Write the value 0x0461 to register 0x000E. (Sets desired register to the IOCTRL)

- 3. Write the value 0x401F to register 0x000D.

- 4. Write the value 0x0400 to register 0x000E. (Sets MAC impedance to 99.25  $\Omega$ )

# 7.3.11.9 Example Read Operation (No Post Increment)

The following example will demonstrate a read operation with no post increment. In this example, the MMD7 Energy Efficient Ethernet Link Partner Ability Register (MMD7\_EEE\_LP\_ABILITY, address 0x703D) will be read.

- 1. Write the value 0x0007 to register 0x000D.

- 2. Write the value 0x003D to register 0x000E. (Sets desired register to the MMD7\_EEE\_LP\_ABILITY)

- 3. Write the value 0x4007 to register 0x000D.

- 4. Read the value of register 0x000E. (Data read is the value contained within the MMD7\_EEE\_LP\_ABILITY)

# 7.3.12 100BASE-TX

## 7.3.12.1 100BASE-TX Transmitter

The 100BASE-TX transmitter consists of several functional blocks which convert synchronous 4-bit nibble data, as provided by the MII, to a scrambled MLT-3 125 Mbps serial data stream on the MDI. 4B5B encoding and decoding is detailed in Table 3 below.

The transmitter section consists of the following functional blocks:

- 1. Code-Group Encoder and Injection Block

- 2. Scrambler Block with Bypass Option

- 3. NRZ to NRZI Encoder Block

- 4. Binary to MLT-3 Converter / Common Driver Block

The bypass option for the functional blocks within the 100BASE-TX transmitter provides flexibility for applications where data conversion is not always required. The DP83825I implements the 100BASE-TX transmit state machine diagram as specified in the IEEE 802.3 Standard, Clause 24.

DP838251

SNLS638A - DECEMBER 2018 - REVISED AUGUST 2019

| SNLS638A – DECEMBER | 2018 - | REVISED | AUGUST | 2019 |

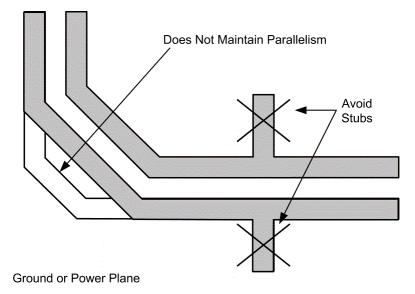

|---------------------|--------|---------|--------|------|