# 安路科技 AL3S10 FPGA 数据手册

DS002 (v1.6) 2018年2月

# 目 录

| 目   | 灵                    |    |

|-----|----------------------|----|

|     | ·<br>简介              |    |

|     | 1 AL3S10 器件资源        | 2  |

| 1.2 | 2 AL3S10 器件特色        | 4  |

| 2   | 硬件设计                 | 5  |

| 2.3 | 1 AL3S10LG144 引脚列表   | 5  |

| 2.2 | 2 AL3S10NG88 引脚列表    | 12 |

| 2.3 | 3 AL3S10LG144 封装尺寸   | 16 |

| 2.4 | 4 AL3S10NG88 封装尺寸    | 17 |

| 2.! | 5 AL3S10LG144 最小硬件系统 | 18 |

| 2.6 | 6 AL3S10NG88 最小硬件系统  | 18 |

| 3   | 使用内部 SDRAM           | 19 |

| 4   | 软件使用向导               | 23 |

| 4.3 | 1 建立工程               | 23 |

| 4 : | 2 特殊 IP 使用           | 28 |

DS002 (v1.6)

2018年2月

### 1 简介

#### 1.1 AL3S10 器件资源

- 灵活的逻辑结构

- 等效 10214 个 4 输入查找表 (LE).

- 低功耗器件

- 先进的 65nm 低功耗工艺

- 静态功耗低至 4mA

- ◆ 丰富的片内存储空间

- 等效 10214 个 4 输入查找表(LE)

- 64Mb SDRAM 存储空间

- 最大 66.5Kb 分布式 RAM

- 48 块 9Kb 嵌入式 RAM(EMB9K),2 块

32Kb 嵌入式 RAM

- 可配置逻辑模块(PLBs)

- 优化的 LUT4/LUT5 组合设计

- 双端口分布式存储器

- 支持算数逻辑运算

- 快速进位链逻辑

- 嵌入式乘法器

- 3个18 x 18 乘法器, 支持9X9模式

- 最高 250MHz

- 高性能,灵活的输入/输出缓冲器

- 支持热插拔

- 可配置上拉/下拉模式

- 片内 100 欧姆差分电阻

- 可配置施密特触发器,最大 0.5V 迟滞

- 时钟资源

- 16 个全局时钟

- 2 个 PLLs 用于频率综合

- 5 路时钟输出

- 分频系数1到128

- 支持 5 路时钟输出级联

- 配置模式

- 主模式串行 SPI (MSPI)

- JTAG 模式 (IEEE-1532)

- BSCAN

- 兼容 IEEE-1149.1

- 封装

- eLQFP144

- QFN88

#### 表 1-1 AL3S10 器件资源

| General feature                 | AL3S10LG144 | AL3S10NG88  |        |

|---------------------------------|-------------|-------------|--------|

| Number of FFs                   | 8,640       | 8,640       |        |

| Number of LUTS                  | 10,368      | 10,368      |        |

| Number of Dis-Ram bits          | 69,120      | 69,120      |        |

| Number of EMB (9k)              | 48          | 48          | - X(1) |

| Number of EMB (32k)             | 2           | 2           | /      |

| Total EBR bits                  | 507,904     | 507,904     | X/     |

| Number of M18x18                | 3           | 3           |        |

| Total Configuration SRAM (bits) | 2,198,020   | 2,198,020   |        |

| PLL                             | 2           | 2           |        |

| Low-skew gclock in chip         | 16          | 16          |        |

| EM SDRAM                        | 2M X 32bits | 2M X 32bits |        |

| User IO Banks                   | 8           | 1           |        |

| Maximum user IOs                | 111         | 60          |        |

|                                 |             |             |        |

#### 表 1-2 AL3S10 FPGA 封装

| Packages                      |   | AL3S10LG144 | AL3S10NG88 |  |

|-------------------------------|---|-------------|------------|--|

| eLQFP144 (18x18, 0.4mm pitch) |   | 111/24+18   | (注)        |  |

| QFN88 (10x10, 0.4mm pitch)    | Y |             | 60/8+7     |  |

|                               |   |             |            |  |

| 3/1                           |   |             |            |  |

|                               |   |             |            |  |

注:表示用户可用 IO 数/用户可用差分输出(LVDS)对

#### 1.2 AL3S10 器件特色

安路最新的 AL3S10 FPGA,是基于安路成熟可靠的低成本、低功耗可编程 FPGA AL3A10,采用最新的 3D 合封技术,与一块 2M X 32bits 的 SDRAM 合封而成。 AL3S10 FPGA 拥有更小,更简单可靠的器件封装,更大的内嵌存储容量,特别适用于大容量,高速数据的采集、传输和变换等应用。

#### 特色优势

- ◆ 多品种,大容量的内置存储空间

- 内置 64Mb SDRAM 存储空间,32 位数据总线宽度,最高 200Mhz 工作频率,最大读写带宽高达 800MB/s

- 内置 48 块 EMB9K 随机读写 RAM,可配置为真双口,简单双口,单口 RAM 和 FIFO工作模式,位宽可配置为 512x18, 1Kx9, 2Kx4, 4Kx2, 8Kx1, 最高频率 250Mhz

- 内置 2 块 32Kb RAM,可配置为单口 RAM,双口 RAM,可独立配置为 2Kx16 或者 4Kx8

- ◆ 更小封装, 更多 IO, 更利于 PCB 布线的引脚排布

- eLQFP144 封装, EPAD 接地, 多达 111 个通用 IO, 4 个可复用 IO

- QFN88 封装, EPAD 接地, 多达 60 个通用 IO, 4 个可复用 IO

- 最多支持 16 对 True LVDS, 最高频率 600Mbps

- eLQFP144 封装为 0.4mm 引脚间距, 18mm X 18mm

- QFN88 封装为 0.4mm 引脚间距, 10mm X 10mm

- / 只需要 1.2V , 3.3V 两组电压供电

- 优化的引脚排布,使得只需要两层 PCB 即可轻松使用器件所有 IO

- 支持简单低成本的 SPI FLASH 配置;上电配置后,FLASH 可作为用户使用。

# 2 硬件设计

# 2.1 AL3S10LG144 引脚列表

表 2-1 AL3S10LG144 FPGA 引脚列表

| IO BANK<br>(注6) | 名称               | 引脚号 | 最小系统<br>需要(注5) | 第二功能        | 功能描述  |

|-----------------|------------------|-----|----------------|-------------|-------|

| BANK1           | IO               | 1   |                |             | 通用 IO |

| BANK1           | IO               | 2   |                |             | 通用 IO |

| BANK1           | IO               | 3   |                | LVDS1_P     | 通用 IO |

| BANK1           | IO               | 4   |                | LVDS1_N     | 通用 IO |

| BANK1           | IO               | 5   |                | X///        | 通用 IO |

| BANK1           | MOSI             | 6   | 是              | 通用 IO (注3)  | MSPI  |

| BANK1           | IO               | 7   |                |             | 通用 IO |

| BANK1           | SPICSN           | 8   | 是              | 通用 IO (注3)  | MSPI  |

| BANK1           | INITN            | 9   | 是              |             | 上电配置  |

| BANK1           | IO               | 10  |                |             | 通用 IO |

| BANK1           | CCLK(注<br>1)     | 11  | 是              | 通用 IO (注 3) | MSPI  |

| BANK1           | D0               | 12  | 是              | 通用 IO (注 3) | MSPI  |

| BANK1           | PROGRAMN<br>(注2) | 13  | 是              |             | 启动配置  |

| BANK1           | TDI              | 14  | 是              |             | JTAG  |

| BANK1           | IO               | 15  |                | LVDS2_P     | 通用 IO |

| BANK1           | TCK              | 16  | 是              |             | JTAG  |

| BANK1           | IO               | 17  |                | LVDS2_N     | 通用 IO |

| BANK1           | IO               | 18  |                | LVDS3_P     | 通用 IO |

| BANK1           | IO               | 19  |                | LVDS3_N     | 通用 IO |

| BANK1 | VCCIO1    | 20 | 是    |                   | 3.3V BANK1 IO<br>电源 |

|-------|-----------|----|------|-------------------|---------------------|

| BANK1 | TMS       | 21 | 是    |                   | JTAG                |

| BANK1 | TDO       | 22 | 是    |                   | JTAG                |

| BANK1 | IO        | 23 |      | GCLKIO_1 (注4)     | 通用 IO               |

| BANK2 | IO        | 24 |      | GCLKIOP_2/LVDS4_P | 通用 IO               |

| BANK2 | IO        | 25 |      | GCLKION_2/LVDS4_N | 通用 IO               |

| BANK2 | IO        | 26 |      |                   | 通用 IO               |

| BANK2 | VCCIO2    | 27 | 是    |                   | 3.3V BANK2 IO       |

|       |           |    |      | />_/              | 电源                  |

| BANK2 | IO        | 28 |      | LVDS5_N           | 通用 IO               |

| BANK2 | IO        | 29 |      | LVDS5_P           | 通用 IO               |

| BANK2 | IO        | 30 | -11X | DPCLKIO_2(注4)     | 通用 IO               |

|       |           |    |      | /LVDS6_P          |                     |

| BANK2 | IO        | 31 | 1X   | LVDS6_N           | 通用 IO               |

| BANK2 | IO        | 32 | 5    | LVDS7_P           | 通用 IO               |

| BANK2 | IO        | 33 |      | LVDS7_N           | 通用 IO               |

| BANK2 | IO        | 34 |      | LVDS8_P           | 通用 IO               |

| BANK2 | IO        | 35 |      | LVDS8_N           | 通用 IO               |

| BANK2 | IO        | 36 |      |                   | 通用 IO               |

| 7_    | VCC_PLLA1 | 37 | 是    |                   | 1.2V PLL1 电源        |

| 7.1   | VCC       | 38 | 是    |                   | 1.2V 核心电源           |

| BANK3 | IO        | 39 |      | GPLL0_CLKIN0(注4)  | 通用 IO               |

| BANK3 | IO        | 40 |      | GPLL0_CLKIN1      | 通用 IO               |

| BANK3 | VCCIO3    | 41 | 是    |                   | 3.3V BANK3 IO       |

|       |           |    |      |                   | 电源                  |

| BANK3 | IO        | 42 |      | E_LVDS1_P         | 通用 IO               |

| BANK3 | IO        | 43 |      | E_LVDS1_N         | 通用 IO               |

| -     |           |    |      |                   |                     |

| BANK3 | IO                                     | 44 |      |              | 通用 IO         |

|-------|----------------------------------------|----|------|--------------|---------------|

| BANK3 | IO                                     | 45 |      | GPLL0_OUTP1/ | 通用 IO         |

|       |                                        |    |      | E_LVDS2_P    |               |

| BANK3 | IO                                     | 46 |      | GPLL0_OUTN1/ | 通用 IO         |

|       |                                        |    |      | E_LVDS2_N    |               |

|       | VCC                                    | 47 | 是    |              | 1.2 V 核心电源    |

| BANK3 | IO                                     | 48 |      |              | 通用 IO         |

| BANK3 | VCCIO3                                 | 49 | 是    |              | 3.3V BANK3 IO |

|       |                                        |    |      | /X           | 电源            |

|       | GND                                    | 50 | 是    |              | 芯片地           |

| BANK3 | IO                                     | 51 |      | - XXx        | 通用 IO         |

| BANK3 | IO                                     | 52 |      | XXXX         | 通用 IO         |

| BANK3 | IO                                     | 53 |      | E_LVDS3_P    | 通用 IO         |

| BANK3 | IO                                     | 54 | ->/- | E_LVDS3_N    | 通用 IO         |

| BANK3 | IO                                     | 55 |      | E_LVDS4_P    | 通用 IO         |

| BANK3 | VCCIO3                                 | 56 | 是    |              | 3.3V BANK3 IO |

|       | 4                                      |    |      |              | 电源            |

| BANK3 | IO                                     | 57 |      | E_LVDS4_N    | 通用 IO         |

| BANK3 | IO                                     | 58 |      |              | 通用 IO         |

| BANK3 | IO                                     | 59 |      | GCLKIOP_3/   | 通用 IO         |

|       | \-\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |    |      | E_LVDS5_P    |               |

| BANK3 | IO                                     | 60 |      | GCLKION_3/   | 通用 IO         |

|       |                                        |    |      | E_LVDS5_N    |               |

| BANK4 | IO                                     | 61 |      | E_LVDS6_P    | 通用 IO         |

| BANK4 | IO                                     | 62 |      | E_LVDS6_N    | 通用 IO         |

|       | VCC                                    | 63 | 是    |              | 1.2V 核心电源     |

| BANK4 | VCCIO4                                 | 64 | 是    |              | 3.3V BANK3 IO |

|       |                                        |    |      |              | 电源            |

| BANK4 | IO                                     | 65 |      | E_LVDS7_P    | 通用 IO         |

|       |                                        |    |      |              |               |

| BANK4 | IO     | 66 |      | E_LVDS7_N          | 通用 IO         |

|-------|--------|----|------|--------------------|---------------|

| BANK4 | IO     | 67 |      |                    | 通用 IO         |

| BANK4 | VCCIO4 | 68 | 是    |                    | 3.3V BANK4 IO |

|       |        |    |      |                    | 电源            |

| BANK4 | IO     | 69 |      |                    | 通用 IO         |

| BANK4 | IO     | 70 |      | E_LVDS8_P          | 通用 IO         |

| BANK4 | IO     | 71 |      | E_LVDS8_N          | 通用 IO         |

|       | VCCAUX | 72 | 是    | 7                  | 3.3V 芯片辅助     |

|       |        |    |      |                    | 电源            |

| BANK5 | IO     | 73 |      | LVDS9_N            | 通用 IO         |

| BANK5 | IO     | 74 |      | LVDS9_P            | 通用 IO         |

| BANK5 | IO     | 75 |      | LVDS10_N           | 通用 IO         |

| BANK5 | IO     | 76 | <1-K | LVDS10_P           | 通用 IO         |

| BANK5 | IO     | 77 |      | LVDS11_N           | 通用 IO         |

| BANK5 | IO     | 78 |      | LVDS11_P           | 通用 IO         |

| BANK5 | IO     | 79 |      | LVDS12_N           | 通用 IO         |

| BANK5 | IO     | 80 | )    | LVDS12_P           | 通用 IO         |

| BANK5 | IO     | 81 |      | LVDS13_N           | 通用 IO         |

| BANK5 | IO     | 82 |      | LVDS13_P           | 通用 IO         |

| BANK5 | VCCIO5 | 83 | 是    |                    | 3.3V BANK5 IO |

| 7 -   |        |    |      |                    | 电源            |

| BANK5 | IO     | 84 |      | LVDS14_N           | 通用 IO         |

| BANK5 | IO     | 85 |      | LVDS14_P           | 通用 IO         |

| BANK5 | IO     | 86 |      |                    | 通用 IO         |

| BANK5 | IO     | 87 |      | LVDS15_N           | 通用 IO         |

| BANK5 | IO     | 88 |      | DPCLKIO_5/LVDS15_P | 通用 IO         |

| BANK5 | IO     | 89 |      | LVDS16_N           | 通用 IO         |

| L     | l      |    | I    |                    |               |

| BANK5 | IO        | 90  |              | LVDS16_P           | 通用 IO               |

|-------|-----------|-----|--------------|--------------------|---------------------|

| BANK5 | IO        | 91  |              | GCLKION_5/LVDS17_N | 通用 IO               |

| BANK5 | IO        | 92  |              | GCLKIOP_5/LVDS17_P | 通用 IO               |

| BANK6 | IO        | 93  |              | GCLKION_6/LVDS18_N | 通用 IO               |

| BANK6 | IO        | 94  |              | GCLKIOP_6/LVDS18_P | 通用 IO               |

| BANK6 | VCCIO6    | 95  | 是            |                    | 3.3V BANK6 IO<br>电源 |

| BANK6 | IO        | 96  |              | LVDS19_N           | 通用 IO               |

| BANK6 | IO        | 97  |              | LVDS19_P           | 通用 IO               |

| BANK6 | IO        | 98  |              | LVDS20_N           | 通用 IO               |

| BANK6 | IO        | 99  |              | LVDS20_P           | 通用 IO               |

| BANK6 | IO        | 100 |              | LVDS21_N           | 通用 IO               |

| BANK6 | IO        | 101 | <b>\</b> J-K | LVDS21_P           | 通用 IO               |

| BANK6 | IO        | 102 |              | LVDS22_N           | 通用 IO               |

| BANK6 | IO        | 103 |              | LVDS22_P           | 通用 IO               |

| BANK6 | IO        | 104 |              |                    | 通用 IO               |

| BANK6 | IO        | 105 |              | DPCLKIO_6/LVDS23_N | 通用 IO               |

| BANK6 | IO        | 106 |              | LVDS23_P           | 通用 IO               |

| BANK6 | IO        | 107 |              | LVDS24_N           | 通用 IO               |

| BANK6 | - IO      | 108 |              | LVDS24_P           | 通用 IO               |

| -/-/- | VCC_PLLA2 | 109 | 是            |                    | 1.2V PLL2 电源        |

| BANK7 | IO        | 110 |              | E_LVDS9_N          | 通用 IO               |

| BANK7 | IO        | 111 |              | DPCLKIO_7/         | 通用 IO               |

|       |           |     |              | E_LVDS9_P          |                     |

| BANK7 | IO        | 112 |              | GPLL2_CLKIN1/      | 通用 IO               |

|       |           |     |              | E_LVDS10_N         |                     |

| BANK7 | IO        | 113 |              | GPLL2_CLKIN0/      | 通用 IO               |

|       |           |     |              | E_LVDS10_P         |                     |

| BANK7 | VCCIO7 | 114 | 是                         |                          | 3.3V BANK7 IO<br>电源 |

|-------|--------|-----|---------------------------|--------------------------|---------------------|

| BANK7 | IO     | 115 |                           | E_LVDS11_N               | 通用 IO               |

| BANK7 | IO     | 116 |                           | E_LVDS11_P               | 通用 IO               |

|       | VCC    | 117 | 是                         |                          | 1.2V 核心电源           |

| BANK7 | IO     | 118 |                           | E_LVDS12_N               | 通用 IO               |

| BANK7 | IO     | 119 |                           | E_LVDS12_P               | 通用 IO               |

| BANK7 | VCCIO7 | 120 | 是                         |                          | 3.3V BANK7 IO<br>电源 |

| BANK7 | IO     | 121 |                           | E_LVDS13_N               | 通用 IO               |

| BANK7 | IO     | 122 |                           | E_LVDS13_P               | 通用 IO               |

| BANK8 | IO     | 123 |                           | -///                     | 通用 IO               |

| BANK8 | IO     | 124 | <1-K                      | GCLKION_8/               | 通用 IO               |

|       |        |     |                           | E_LVDS14_N               |                     |

| BANK8 | IO     | 125 | $\int_{-\infty}^{\infty}$ | GCLKIOP_8/<br>E_LVDS14_P | 通用 IO               |

| BANK8 | IO     | 126 |                           |                          | 通用 IO               |

| BANK8 | IO     | 127 |                           | E_LVDS15_N               | 通用 IO               |

| BANK8 | IO     | 128 |                           | E_LVDS15_P               | 通用 IO               |

| BANK8 | IO     | 129 |                           | E_LVDS16_N               | 通用 IO               |

| BANK8 | IO     | 130 |                           | E_LVDS16_P               | 通用 IO               |

| BANK8 | IO     | 131 |                           |                          | 通用 IO               |

| YX    | VCC    | 132 | 是                         |                          | 1.2V 核心电源           |

| BANK8 | IO     | 133 |                           |                          | 通用 IO               |

| BANK8 | IO     | 134 |                           | E_LVDS17_N               | 通用 IO               |

| BANK8 | IO     | 135 |                           | E_LVDS17_P               | 通用 IO               |

| BANK8 | VCCIO8 | 136 | 是                         |                          | 3.3V BANK8 IO<br>电源 |

| BANK8 | IO     | 137 |   |            | 通用 IO               |

|-------|--------|-----|---|------------|---------------------|

| BANK8 | IO     | 138 |   |            | 通用 IO               |

| BANK8 | VCCIO8 | 139 | 是 |            | 3.3V BANK8 IO<br>电源 |

| BANK8 | IO     | 140 |   | DPCLKIO_8  | 通用 IO               |

| BANK8 | IO     | 141 |   | E_LVDS18_N | 通用 IO               |

| BANK8 | IO     | 142 |   | E_LVDS18_P | 通用 IO               |

|       | VCC    | 143 | 是 |            | 1.2V 核心电源           |

| BANK1 | IO     | 144 |   | . //X      | 通用 IO               |

|       | EPAD   | 145 | 是 | 12,        | 芯片接地                |

注 1 (CCLK): 芯片内部有另外一个通用 IO 与该脚相连,当上电配置后,用户可使用用户逻辑产生 CCLK,访问 FLASH。

注 2(PROGRAMN): 如果用户需要在上电后,控制用户代码触发 FPGA 重新配置,则需要将该 PROGRAMN 与一通用 IO 相连,当相连 IO 拉低则触发 FPGA 重配置。注意在正常工作状态,保持该 IO 为高电平。

注 3: 在上电配置后,这些引脚可以作为用户 IO 使用。

注 4: 参考 AL3 FPGA 手册可知, DPCLK,GCLKIO,GPLL\_CLKIN 均可作为 PLL 专用时钟输入,输入延时固定。

注 5: 这些引脚为芯片最小系统需求,必须保证这些引脚正确连接,芯片才能正常工作。

注 6:除了 IO BANK5,其他 BANK 均有 IO 被 SDRAM 使用,因此推荐 BANK1, BANK2,BANK3,BANK4,BANK6,BANK7,BANK8 使用 3.3V 电压,BANK5 可支持 1.2V,1.5V,1.8V,2.5V,3.3V IO 电平。

# 2.2 AL3S10NG88 引脚列表

#### 表 2-2 AL3S10NG88 FPGA 引脚列表

| 引脚号 | 最小系统需要(注5)                                            | 第二功能                                                                                     | 功能描述       |

|-----|-------------------------------------------------------|------------------------------------------------------------------------------------------|------------|

| 1   |                                                       |                                                                                          | 通用 IO      |

| 2   |                                                       |                                                                                          | 通用 IO      |

| 3   | 是                                                     | 通用 IO (注 3)                                                                              | MSPI (D1)  |

| 4   |                                                       |                                                                                          | 通用 IO      |

| 5   | 是                                                     | 通用 IO (注 3)                                                                              | MSPI       |

| 6   | 是                                                     | - <b>/</b>                                                                               | 上电配置       |

| 7   | 是                                                     | 通用 IO (注3)                                                                               | MSPI       |

| 8   | 是                                                     | 通用 IO (注 3)                                                                              | MSPI (D0)  |

| 9   | 是                                                     |                                                                                          | 启动配置       |

|     |                                                       |                                                                                          |            |

| 10  | 是                                                     | /                                                                                        | JTAG       |

| 11  | 是                                                     |                                                                                          | JTAG       |

| 12  |                                                       |                                                                                          | 通用 IO      |

| 13  | 是                                                     |                                                                                          | JTAG       |

| 14  | 是                                                     |                                                                                          | JTAG       |

| 15  |                                                       | GCLKION_2(注4)                                                                            | 通用 IO      |

| 16  |                                                       |                                                                                          | 通用 IO      |

| 17  |                                                       |                                                                                          | 通用 IO      |

| 18  |                                                       | DPCLKIO_2 (注4)                                                                           | 通用 IO      |

| 19  | 是                                                     |                                                                                          | 3.3V IO 电源 |

| 20  |                                                       | LVDS1_N                                                                                  | 通用 IO      |

| 21  |                                                       | LVDS1_P                                                                                  | 通用 IO      |

| 22  |                                                       | LVDS2_P                                                                                  | 通用 IO      |

|     | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 | 1 (注5) 1 2 3 是 4 5 是 6 是 7 是 8 是 9 是 10 是 11 是 12 13 是 14 是 15 16 15 16 17 18 19 是 20 21 | 1 (注5)     |

| IO        | 23 |      | LVDS2_N      | 通用 IO        |

|-----------|----|------|--------------|--------------|

| VCC_PLLA1 | 24 | 是    |              | 1.2V PLL1 电源 |

| IO        | 25 |      | GPLL0_CLKIN1 | 通用 IO        |

|           |    |      | (注4)         |              |

|           |    |      | ELVDS1_N     |              |

| IO        | 26 |      | GPLL0_CLKIN0 | 通用 IO        |

|           |    |      | ELVDS1_P     |              |

| IO        | 27 |      |              | 通用 IO        |

| IO        | 28 |      | _ (/)        | 通用 IO        |

| IO        | 29 |      | GPLL0_OUTP1  | 通用 IO        |

| VCC       | 30 | 是    |              | 1.2 V 核心电源   |

| VCCIO     | 31 | 是    | X            | 3.3V IO 电源   |

| GND       | 32 | 是    |              | 芯片地          |

| IO        | 33 | - Th |              | 通用 IO        |

| VCCIO     | 34 | 是    |              | 3.3V IO 电源   |

| IO        | 35 |      |              | 通用 IO        |

| IO        | 36 |      |              | 通用 IO        |

| VCCIO     | 37 | 是    |              | 3.3V IO 电源   |

| VCC       | 38 | 是    |              | 1.2V 核心电源    |

| IO        | 39 |      |              | 通用 IO        |

| IO        | 40 |      |              | 通用 IO        |

| IO        | 41 |      | ELVDS2_P     | 通用 IO        |

| IO        | 42 |      | ELVDS2_N     | 通用 IO        |

| IO        | 43 |      | ELVDS3_P     | 通用 IO        |

| IO        | 44 |      | ELVDS3_N     | 通用 IO        |

| VCCAUX    | 45 | 是    |              | 3.3V 辅助电源    |

| IO        | 46 |      |              | 通用 IO        |

|           | I. |      |              | 1            |

| IO                 | 47 |   |                | 通用 IO        |

|--------------------|----|---|----------------|--------------|

| IO                 | 48 |   |                | 通用 IO        |

| IO                 | 49 |   |                | 通用 IO        |

| IO                 | 50 |   | LVDS3_N        | 通用 IO        |

| IO                 | 51 |   | LVDS3_P        | 通用IO         |

| VCCIO              | 52 | 是 |                | 3.3V IO 电源   |

| IO                 | 53 |   | LVDS4_N        | 通用 IO        |

| IO                 | 54 |   | LVDS4_P        | 通用 IO        |

| IO                 | 55 |   | LVDS5_N        | 通用 IO        |

| IO                 | 56 |   | LVDS5_P        | 通用 IO        |

| IO                 | 57 |   | XXXX           | 通用 IO        |

| VCCIO              | 58 | 是 |                | 3.3V IO 电源   |

| IO                 | 59 |   |                | 通用 IO        |

| MSEL2 <b>(注 6)</b> | 60 | 是 |                | 程序加载模式选      |

|                    |    |   | /              | 择            |

| IO                 | 61 |   |                | 通用 IO        |

| IO                 | 62 |   | DPCLKIO_6/LVDS | 通用 IO        |

| - 1                |    |   | 6_N            |              |

| IO                 | 63 |   | LVDS6_P        | 通用 IO        |

| Ю                  | 64 |   | LVDS7_P        | 通用 IO        |

| IO                 | 65 |   | LVDS7_N        | 通用 IO        |

| IO                 | 66 |   | GPLL2_OUTN2/LV | 通用 IO        |

|                    |    |   | DS8_N          |              |

| IO                 | 67 |   | GPLL2_OUTP2/LV | 通用 IO        |

|                    |    |   | DS8_P          |              |

| VCC_PLLA2          | 68 | 是 |                | 1.2V PLL2 电源 |

| VCC                | 69 | 是 |                | 1.2V 核心电源    |

| IO                 | 70 |   | GPLL2_CLKIN0   | 通用 IO        |

| <u> </u>           | •  | • |                |              |

| IO    | 71 |      | ELVDS4_N  | 通用 IO                                   |

|-------|----|------|-----------|-----------------------------------------|

| IO    | 72 |      | ELVDS4_P  | 通用 IO                                   |

| VCCIO | 73 | 是    |           | 3.3V IO 电源                              |

| IO    | 74 |      |           | 通用 IO                                   |

| IO    | 75 |      | GCLKION_7 | 通用 IO                                   |

| IO    | 76 |      | GCLKION_8 | 通用 IO                                   |

|       |    |      | ELVDS5_N  | _ \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| IO    | 77 |      | GCLKIOP_8 | 通用 IO                                   |

|       |    |      | ELVDS5_P  |                                         |

| VCCIO | 78 | 是    |           | 3.3V IO 电源                              |

| IO    | 79 |      | ELVDS6_N  | 通用 IO (D2)                              |

| IO    | 80 | -1.7 | ELVDS6_P  | 通用 IO (D3)                              |

| IO    | 81 |      |           | 通用 IO (D7)                              |

| IO    | 82 |      | ELVDS7_N  | 通用 IO (D5)                              |

| IO    | 83 | 67   | ELVDS7_P  | 通用 IO (D6)                              |

| IO    | 84 |      |           | 通用 IO                                   |

| VCCIO | 85 | 是    |           | 3.3V IO 电源                              |

| IO    | 86 |      |           | 通用 IO (D4)                              |

| IO    | 87 |      |           | 通用 IO                                   |

| VCCIO | 88 | 是    |           | 3.3V IO 电源                              |

| EPAD  | 89 | 是    |           | 芯片 GND                                  |

注1(CCLK): 芯片内部有另外一个通用 IO 与该脚相连,当上电配置后,用户可使用用户逻辑产生CCLK,访问 FLASH。

注 2(PROGRAMN): 如果用户需要在上电后,控制用户代码触发 FPGA 重新配置,则需要将该 PROGRAMN 与一通用 IO 相连,当相连 IO 拉低则触发 FPGA 重配置。注意在正常工作状态,保持该 IO 为高电平。

注 3: 在上电配置后,这些引脚可以作为用户 IO 使用。

注 4: 参考 AL3 FPGA 手册可知, DPCLK,GCLKIO,GPLL\_CLKIN 均可作为 PLL 专用时钟输入,输入延时固定。

注 5: 这些引脚为芯片最小系统需求,必须保证这些引脚正确连接,芯片才能正常工作。

注 6: MSEL2 为程序加载模式选择引脚,默认情况使用主动串行模式,将该引脚直接拉低到 GND.

注7:如果要使用SDRAM,则所有BANK都必须使用3.3VIO电压。

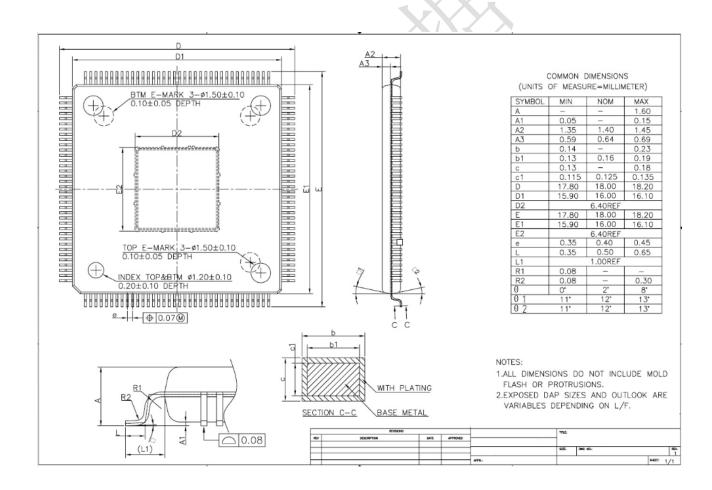

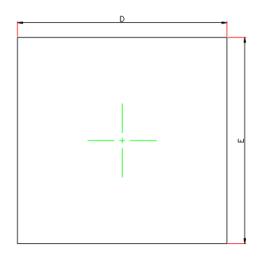

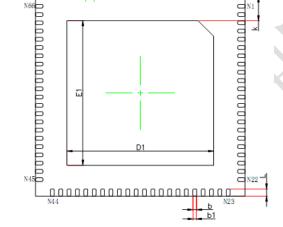

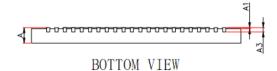

### 2.3 AL3S10LG144 封装尺寸

# 2.4 AL3S10NG88 封装尺寸

N88

TOP VIEW

SIDE VIEW

| Symbol Dimension |           | n Millimeters | Dimensions In Inches |       |

|------------------|-----------|---------------|----------------------|-------|

| Symbol           | MIN.      | MAX.          | MIN.                 | MAX.  |

| Α                | 0.700     | 0.800         | 0.028                | 0.031 |

| A1               | 0.000     | 0.050         | 0.000                | 0.002 |

| A3               | 0.203REF. |               | EF. 0.008REF.        |       |

| D                | 9.924     | 10.076        | 0.391                | 0.397 |

| E                | 9.924     | 10.076        | 0.391                | 0.397 |

| D1               | 6.900     | 7.100         | 0.272                | 0.280 |

| E1               | 6.900     | 7.100         | 0.272                | 0.280 |

| k                | 1.150REF. |               | 0.045                | REF.  |

| b                | 0.150     | 0.250         | 0.006                | 0.010 |

| b1               | 0.100     | 0.200         | 0.004                | 0.008 |

| е                | 0.400BSC. |               | 0.016                | BSC.  |

| L                | 0.274     | 0.426         | 0.011                | 0.017 |

### 2.5 AL3S10LG144 最小硬件系统

AL3S10LG144 FPGA 要正常工作,需要保证如表 2-1 所示的最小系统需要相关的引脚都正确的连接。硬件设计实例请参考附录 AL3S10LG144\_FPGA\_CORE.pdf。

### 2.6 AL3S10NG88 最小硬件系统

AL3S10NG88 FPGA 要正常工作,需要保证如表 2-2 所示的最小系统需要相关的引脚都正确的连接。硬件设计实例请参考附录 AL3S10NG88\_FPGA\_CORE.pdf。

### 3 使用内部 SDRAM

AL3S10 内嵌一片 2M X 32bit 的 SDRAM,最高 200Mhz 工作频率,最大读写带宽高达 800MB/s。SDRAM 与 FPGA 通过软件深度整合,所以如果要使用 SDRAM,只需要在顶层实例化如下 IP 模块即可。该 IP 的原型如下:

AL\_PHY\_SDRAM\_2M\_32 U\_AL\_PHY\_SDRAM\_2M\_32(

```

.clk(SD CLK),

// SDRAM 时钟

1bit 位宽

.ras n(SD RAS N),

// SDRAM 行选 通 1bit 位宽

.cas n(SD CAN N),

//SDRAM 列选 通 1bit 位宽

1bit 位宽

.we n(SD WE N),

//SDRAM 写使能

//SDRAM 地址

.addr(SD SA),

11bits 位宽

// SDRAM BANK 地址 2bits 位宽

.ba(SD_BA),

.dq(SD_DQ),

// SDRAM 数据

32bits 位宽

.dm(1'b0)

// SDRAM 数据屏蔽 1bit 位宽

```

);

| SDRAM 引脚名称 | SDRAM 引脚描述 | 引脚连接          |

|------------|------------|---------------|

| DQ0        | 数据脚 0      | 与IP相连         |

| DQ1        | 数据脚 1      | 与IP相连         |

| DQ2        | 数据脚 2      | 与IP相连         |

| DQ3        | 数据脚 3      | 与IP相连         |

| DQ4        | 数据脚 4      | 与IP相连         |

| DQ5        | 数据脚 5      | 与 IP 相连       |

| DQ6        | 数据脚 6      | 与 IP 相连       |

| DQ7        | 数据脚 7      | 与 IP 相连       |

| DQ8        | 数据脚 8      | 与 IP 相连       |

| DQ9        | 数据脚 9      | 与 IP 相连       |

| DQ10       | 数据脚 10     | 与 IP 相连       |

| DQ11       | 数据脚 11     | 与 IP 相连       |

| DQ12       | 数据脚 12     | 与 IP 相连       |

| DQ13       | 数据脚 13     | 与 IP 相连       |

| DQ14       | 数据脚 14     | 与 IP 相连       |

| DQ15       | 数据脚 15     | 与 IP 相连       |

| DQ16       | 数据脚 16     | 与 IP 相连       |

| DQ17       | 数据脚 17     | 与 IP 相连       |

| DQ18       | 数据脚 18     | <u>与IP 相连</u> |

|   | DQ19 | 数据脚 19 | 与 IP 相连 |

|---|------|--------|---------|

|   | DQ20 | 数据脚 20 | 与IP相连   |

|   | DQ21 | 数据脚 21 | 与IP相连   |

| • | DQ22 | 数据脚 22 | 与IP相连   |

|   | DQ23 | 数据脚 23 | 与 IP 相连 |

|   | DQ24 | 数据脚 24 | 与IP相连   |

|   | DQ25 | 数据脚 25 | 与 IP 相连 |

|   | DQ26 | 数据脚 26 | 与 IP 相连 |

|   | DQ27 | 数据脚 27 | 与 IP 相连 |

|   | DQ28 | 数据脚 28 | 与 IP 相连 |

|   | DQ29 | 数据脚 29 | 与 IP 相连 |

| • | DQ30 | 数据脚 30 | 与 IP 相连 |

|   | DQ31 | 数据脚 31 | 与 IP 相连 |

| • | SA0  | 地址脚 0  | 与 IP 相连 |

|   | SA1  | 地址脚 1  | 与 IP 相连 |

|   | SA2  | 地址脚 2  | 与 IP 相连 |

|   | SA3  | 地址脚 3  | 与 IP 相连 |

|   | SA4  | 地址脚 4  | 与 IP 相连 |

|   | SA5  | 地址脚 5  | 与 IP 相连 |

|   | SA6  | 地址脚 6  | 与 IP 相连 |

|   |      |        |         |

| SA7   | 地址脚 7       | 与IP相连 |

|-------|-------------|-------|

| SA8   | 地址脚 8       | 与IP相连 |

| SA9   | 地址脚 9       | 与IP相连 |

| SA10  | 地址脚 10      | 与IP相连 |

| BAO   | BANK 地址脚 0  | 与IP相连 |

| BA1   | BANK 地址脚 1  | 与IP相连 |

| WE_N  | 写使能         | 与IP相连 |

| RAS_N | 行选通         | 与IP相连 |

| CAS_N | 列选通         | 与IP相连 |

| CLK   | 芯片时钟        | 与IP相连 |

| CS_N  | 片选          | 固定拉低  |

| DM0   | 数据 0-7 屏蔽   | 固定拉低  |

| DM1   | 数据 8-15 屏蔽  | 固定拉低  |

| DM2   | 数据 16-23 屏蔽 | 固定拉低  |

| DM3   | 数据 24-31 屏蔽 | 固定拉低  |

| CKE   | 时钟使能        | 固定拉高  |

# 4 软件使用向导

## 4.1 建立工程

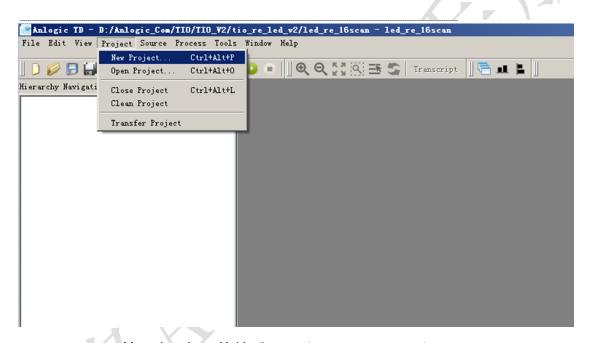

第一步, 打开软件后, Project > New Project

23

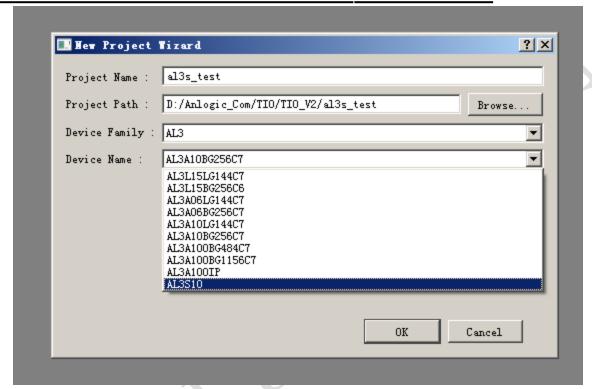

第二步,选择工程路径,并选择器件

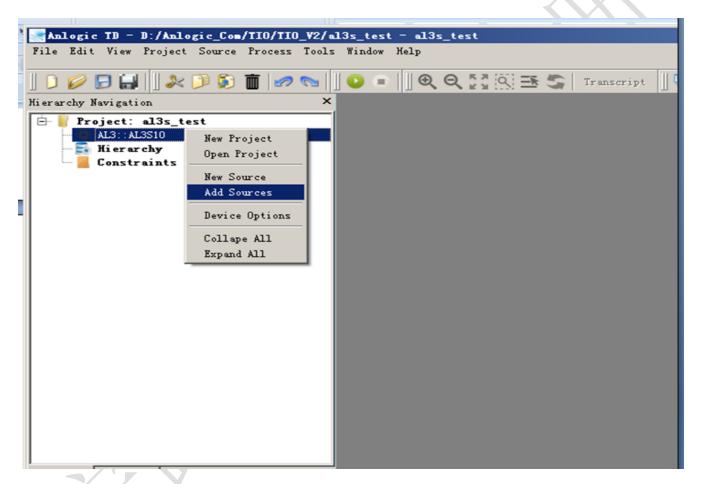

第三步,添加已有文件,或者新建文件

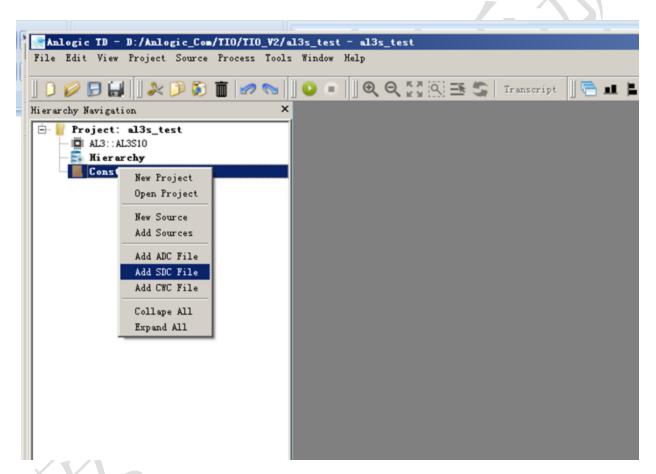

第四步,添加引脚约束文件(ADC File)和时序约束文件(SDC File)

第五步,点键点击对应步骤,然后 Run 相应步骤,也可以直接右键 HDL2Bit\_Flow 跑完所有步骤

### 4.2 特殊 IP 使用

- 一、 IO 延时单元,可使用该单元调节 RGMII 信号的输入延时

AL\_LOGIC\_IDELAY U0\_AL\_LOGIC\_IDELAY(.i(PHY1\_RXDV),.o(rxdv\_int));

defparam U0\_AL\_LOGIC\_IDELAY.INDEL = 0;

单数用于设置延时长度,每增加 1,增加延时 0.1ns。

- 二、 输入双沿采样单元,用于对 RGMII 输入信号的双沿采样

AL\_LOGIC\_IDDR IDDR\_0 (.q1(rxd\_r2g\_tmp[3]), .q2(rxd\_r2g\_tmp[7]), .clk(rxc), .d(rxd[3]), .rst(~rst\_n));

- 三、输出双沿驱动单元,用于对 RGMII 输出信号的双沿驱动

AL\_LOGIC\_ODDR ODDR\_0(.q(txd[0]), .clk(txc\_tmp), .d1(txd\_tmp[4]), .d2(txd\_tmp[0]), .rst(RST\_OUT0));