Now

Reference Design

#### **TRF7970A**

ZHCS363L-AUGUST 2011-REVISED MARCH 2017

# TRF7970A 多协议全集成式 13.56MHz RFID 和近场通信 (NFC) 收发器 IC

#### 器件概述 1

#### 特性 1.1

- 支持近场通信 (NFC) 标准 NFCIP-1 (ISO/IEC 18092) 和 NFCIP-2 (ISO/IEC 21481)

- 完全集成了以下标准的协议处理: ISO/IEC 15693、 ISO/IEC 18000-3、ISO/IEC 14443 A 和 B 以及 FeliCa™

- 集成式编码器、解码器和数据组帧功能,用于 NFC 发起方运行模式以及有源和无源目标方运行模式, 适合所有三种比特率(106kbps、212kbps、 424kbps)以及卡仿真

- 借助带有可编程唤醒电平的射频场检测器,实现 NFC 无源应答器仿真

- 通过射频场检测器避免 NFC 物理碰撞

- 通过集成的状态机实现 ISO/IEC 14443 A 防撞(破 坏的字节) (应答器仿真或 NFC 无源目标)

- 输入电压范围: 2.7VDC 至 5.5VDC

- 可编程输出功率: +20dBm (100mW), +23dBm

#### 1.2 应用范围

- 移动器件 (平板电脑、手机) •

- 安全配对(Bluetooth<sup>®</sup>,Wi-Fi<sup>®</sup>,其他配对无线网 络)

- 公共运输或者赛事票务

- 护照或者付费 (POS) 读取器系统

#### (200mW)

- 从 1.8VDC 至 5.5 VDC 的可编程 I/O 电压电平

- 来自 13.56MHz 或者 27.12MHz 晶振或者振荡器的 可编程系统时钟频率输出 (RF, RF/2, RF/4)

Support &

Community

- 针对其它系统组件(微控制器 (MCU),外设,指示 器)的集成电压稳压器输出,20mA(最大值)

- 可编程调制深度

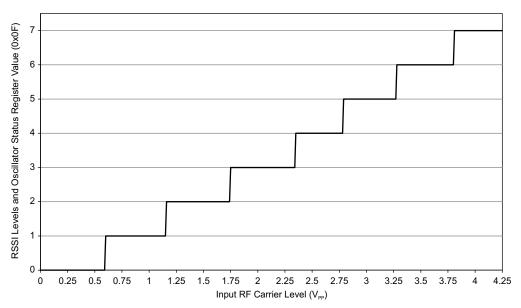

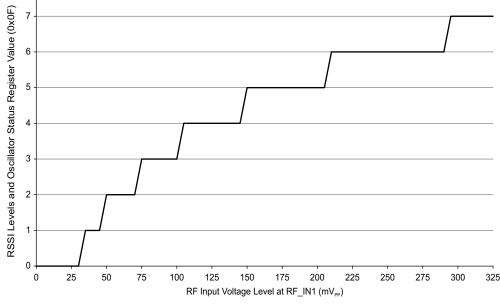

- 具有针对"读取漏洞"消除和邻近读取器系统或者周围 环境频带内噪声检测的具有接收信号强度指示器 (RSSI) 的双接收器架构

- 针对超低功耗系统设计的可编程功率模式(断电时 < 1µA)

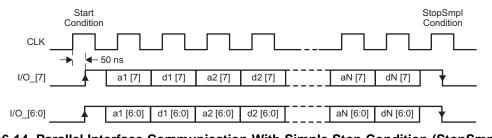

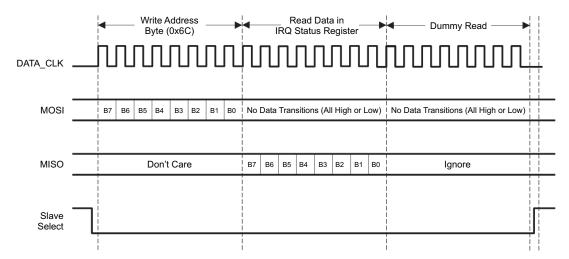

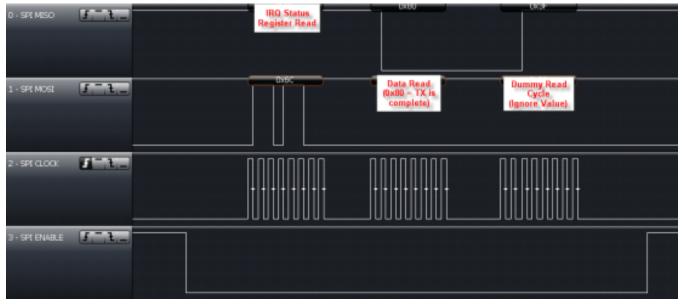

- 并行或 SPI 接口(带有 127 字节 FIFO)

- 温度范围: -40℃ 至 110℃ ٠

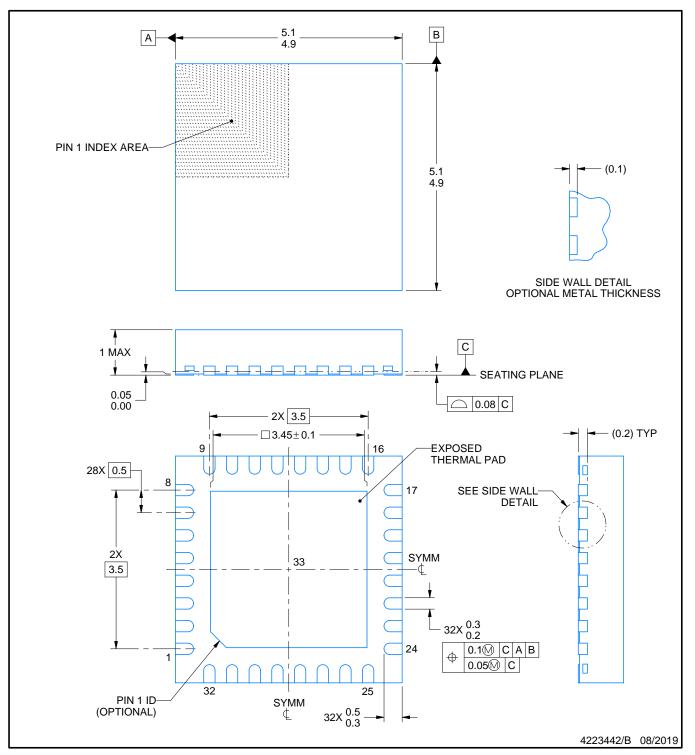

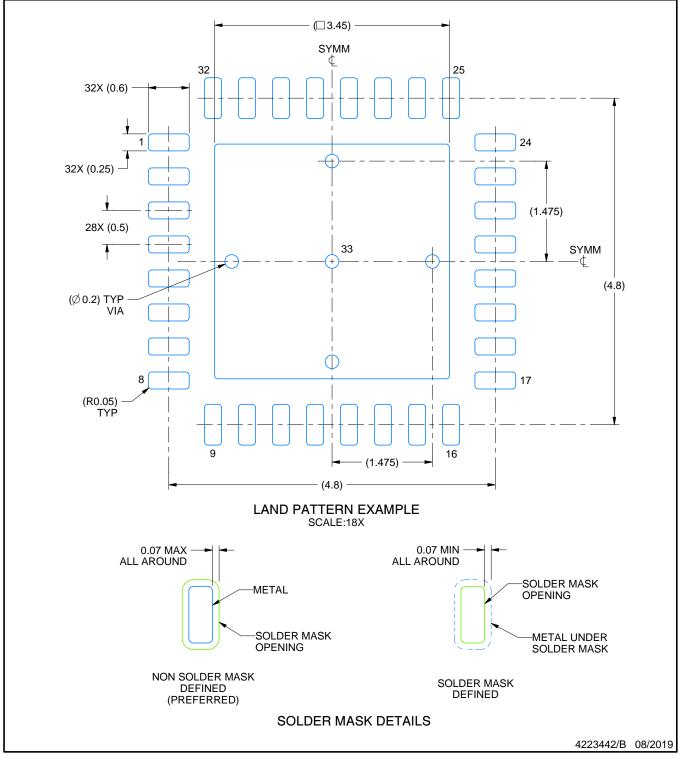

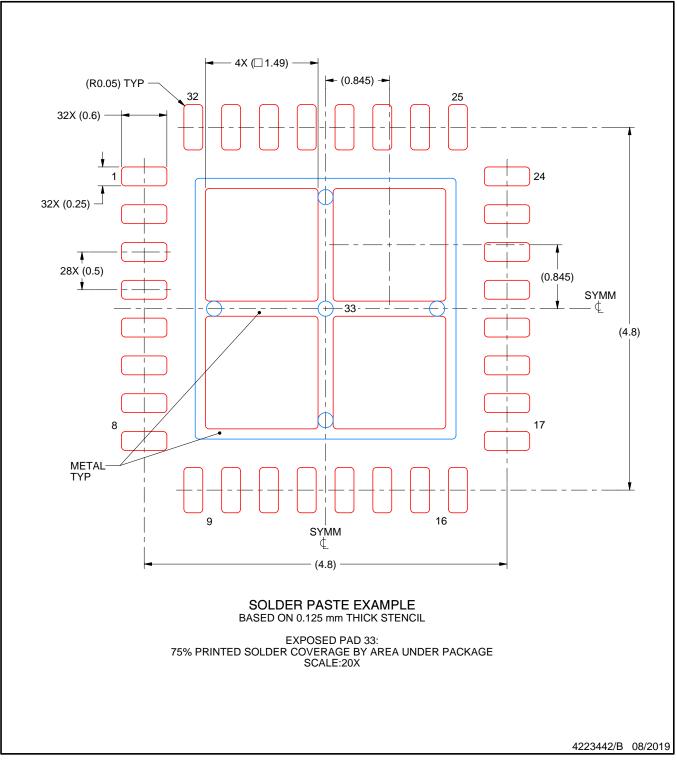

- 32 引脚 QFN 封装 (5mm × 5mm)

- 近程无线通信任务(固件升级)

- 产品识别或者认证

- 医疗设备或者消耗品 .

- 访问控制、数字门锁 •

- 电子业务卡共享

#### 说明 1.3

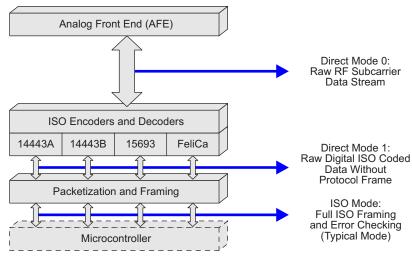

TRF7970A 器件是一款用于 13.56MHz NFC/RFID 系统的集成式模拟前端 (AFE) 和多协议数据组帧器件, 支持所有的三种 NFC 工作模式:读/写器模式、对等模式和卡仿真模式,符合 ISO/IEC 14443 A 和 B、 Sony FeliCa、ISO/IEC 15693、NFCIP-1 (ISO/IEC 18092) 和 NFCIP-2 (ISO/IEC 21481) 等标准。该器件具 有内置的编程选项,因此适合于 NFC、接近和邻近识别系统的广泛 应用。

通过在控制寄存器内选择所需的协议可对此器件进行配置。通过对所有控制寄存器进行直接存取,可根据需 要对不同的读取器参数进行微调。

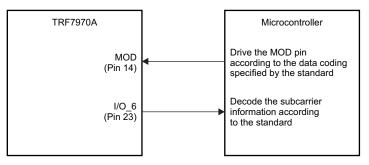

TRF7970A 器件针对所有符合板载 ISO 协议的组帧和同步任务,支持高达 848kbps 的数据速率。 TRF7970A 器件还支持 NFC 论坛标签类型 1、2、3、4 和 5 的读写器模式。可通过使用该器件提供的直接 模式之一来实现其他标准甚至自定义协议。这些直接模式可让用户完全控制 AFE,并且还可以访问原始子载 波数据或者未组帧但已经是 ISO 格式的数据和相关(提取的)时钟信号。

接收器系统具有双输入接收器架构,可最大程度实现通信稳定。接收器还包括多种自动和手动增益控制选 项。在 RSSI 寄存器中可获取从应答器、周围信号源或者内部电平接收到的信号强度。

可使用 SPI 或并行接口进行 MCU 和 TRF7970A 器件间的通信。当使用内置的硬件编码器和解码器时,发 送和接收功能使用一个 127 字节的 FIFO 寄存器。对于直接发送或接收功能,由于编码器或解码器可被旁路 绕开,所以 MCU 可实时地处理数据。

TRF7970A 器件支持 2.7V 至 5.5V 的宽电源电压范围以及 MCU I/O 接口的 1.8V 至 5.5V 数据通信电平。

当使用 5V 电源时,发送器对于 50Ω 负载具有 100mW (+20dBm) 或 200mW (+23dBm) 等效值的可选输出 功率电平,并支持可选调制深度的 OOK 和 ASK 调制。

内置的可编程辅助稳压器为 MCU 和读取器系统内的其他外部电路提供高达 20mA 的电源。

通过具有可编程唤醒电平、八种可选电源模式以及超低功耗运行模式的集成射频场检测器,可以轻松开发可靠、经济高效且电池寿命长的设计。

要评估 TRF7970A 多协议收发器 IC,可使用TRF7970AEVM、TRF7970ATB 或 DLP-7970ABP。

|             | 器件信息      |           |

|-------------|-----------|-----------|

| 器件型号        | 封装        | 封装尺寸      |

| TRF7970ARHB | VQFN (32) | 5mm x 5mm |

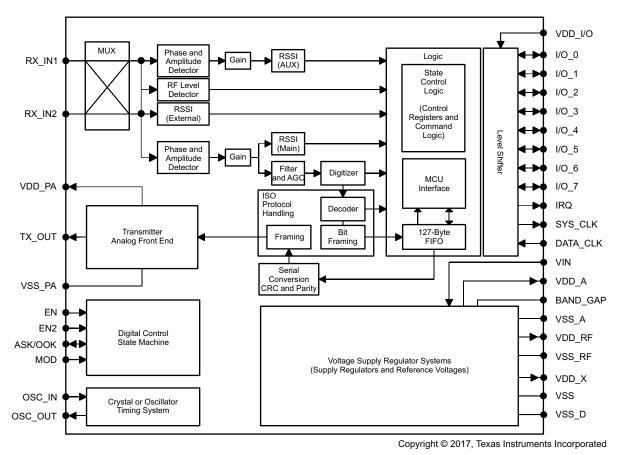

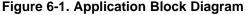

#### **1.4** 功能方框图

图 1-1 显示了方框图。

图 1-1. 方框图

#### TRF7970A ZHCS363L – AUGUST 2011 – REVISED MARCH 2017

# 内容

| 1 | 器件   | 概述 <u>1</u>                           |

|---|------|---------------------------------------|

|   | 1.1  | 特性1                                   |

|   | 1.2  |                                       |

|   | 1.3  | <br>说明 <u>1</u>                       |

|   | 1.4  | 功能方框图 2                               |

| 2 | 修订   | 历史记录 4                                |

| 3 | Devi | ce Characteristics                    |

|   | 3.1  | Related Products                      |

| 4 | Term | ninal Configuration and Functions     |

|   | 4.1  | Pin Diagram                           |

|   | 4.2  | Signal Descriptions                   |

| 5 | Spec | cifications 9                         |

|   | 5.1  | Absolute Maximum Ratings 9            |

|   | 5.2  | ESD Ratings 9                         |

|   | 5.3  | Recommended Operating Conditions 9    |

|   | 5.4  | Electrical Characteristics 10         |

|   | 5.5  | Thermal Resistance Characteristics 11 |

|   | 5.6  | Switching Characteristics 11          |

| 6 | Deta | iled Description <u>12</u>            |

|   | 6.1  | Overview <u>12</u>                    |

|   | 6.2  | System Block Diagram <u>15</u>        |

|   | 6.3  | Power Supplies <u>15</u>              |

|   | 6.4  | Receiver – Analog Section 21          |

|   | 6.5  | Receiver – Digital Section 22         |

|   | 6.6  | Oscillator Section <u>27</u>          |

|   | 6.7  | Transmitter – Analog Section 28       |

|   | 6.8   | Transmitter – Digital Section                             | 29        |

|---|-------|-----------------------------------------------------------|-----------|

|   | 6.9   | Transmitter – External Power Amplifier and                |           |

|   |       | Subcarrier Detector                                       | <u>30</u> |

|   | 6.10  | TRF7970A IC Communication Interface                       | <u>30</u> |

|   | 6.11  | TRF7970A Initialization                                   | <u>48</u> |

|   | 6.12  | Special Direct Mode for Improved MIFARE™<br>Compatibility | 49        |

|   | 6.13  | NFC Modes                                                 | 49        |

|   | 6.14  | Direct Commands from MCU to Reader                        | 51        |

|   | 6.15  | Register Description                                      | 55        |

| 7 | Appli | cations, Implementation, and Layout                       | 75        |

|   | 7.1   | TRF7970A Reader System Using SPI With SS                  |           |

|   |       | Mode                                                      | <u>75</u> |

|   | 7.2   | Layout Considerations                                     | <u>76</u> |

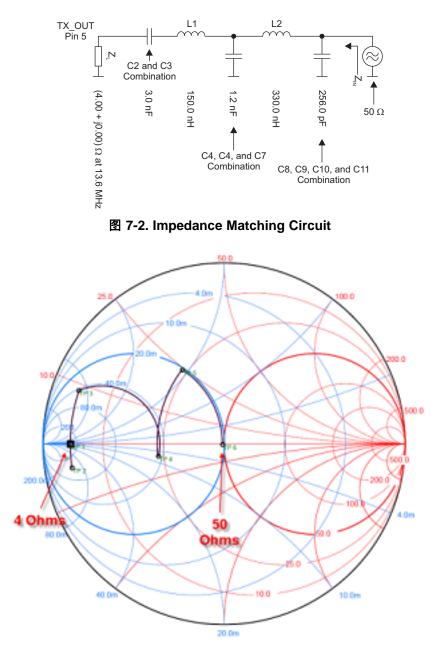

|   | 7.3   | Impedance Matching TX_Out (Pin 5) to 50 $\Omega$          | <u>76</u> |

|   | 7.4   | Reader Antenna Design Guidelines                          | 77        |

| 8 | 器件利   | 和文档支持                                                     | 78        |

|   | 8.1   | 入门和下一步                                                    | 78        |

|   | 8.2   | 器件命名规则                                                    | 78        |

|   | 8.3   | 工具与软件                                                     | 79        |

|   | 8.4   | 文档支持                                                      | 79        |

|   | 8.5   | 社区资源                                                      | 80        |

|   | 8.6   | 商标                                                        | 80        |

|   | 8.7   | 静电放电警告                                                    | 80        |

|   | 8.8   | Glossary                                                  | 80        |

| 9 | 机械、   |                                                           | <u>81</u> |

TEXAS INSTRUMENTS www.ti.com.cn

## 2 修订历史记录

#### 注: 之前版本的页码可能与当前版本有所不同。

#### Changes from April 18, 2014 to March 27, 2017

## Page

| • | 通篇更正了 ISO/IEC 标准代号;例如,将 ISO14443 更改为 ISO/IEC 14443                                                                                                                                                                              |              |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| • | 更改了以下部分的内容: 节 1.3 - <i>说明</i>                                                                                                                                                                                                   |              |

| ٠ | Added Section 3.1, Related Products                                                                                                                                                                                             | <u>    6</u> |

| • | Added Section 3.1, <i>Related Products</i><br>Moved T <sub>STG</sub> from Section 5.2 to Section 5.1, <i>Absolute Maximum Ratings</i><br>Moved Section 5.2 and changed title from <i>Handling Ratings</i> to <i>ESD Ratings</i> | . <u>9</u>   |

| • | Moved Section 5.2 and changed title from Handling Ratings to ESD Ratings                                                                                                                                                        | . <u>9</u>   |

| • | Added V <sub>OL</sub> and V <sub>OH</sub> to Section 5.4, Electrical Characteristics                                                                                                                                            | <u>10</u>    |

| • | Changed the TYP value of the f <sub>D_CLKmax</sub> parameter from 8 to 4 MHz in Section 5.4, <i>Electrical Characteristics</i>                                                                                                  | <u>10</u>    |

| • | Throughout document, removed support for application control of Automatic Gain Control (AGC) and Receiver                                                                                                                       |              |

|   | Gain Adjust, because these features were designed for test functionality and not for production use                                                                                                                             | <u>12</u>    |

| • | Added NFC Type 5 tags to supported list in Section 6.1.1, RFID and NFC Operation – Reader and Writer                                                                                                                            | <u>12</u>    |

| • | Removed the paragraph that started "The desired system of operation (bit rate) is achieved by" from                                                                                                                             |              |

|   | Section 6.1.2, NFC Device Operation – Initiator                                                                                                                                                                                 | <u>13</u>    |

| • | Removed the paragraph that started "The desired system of operation (bit rate) is achieved by" from                                                                                                                             |              |

|   | Section 6.1.3, NFC Device Operation – Target                                                                                                                                                                                    | <u>13</u>    |

| • | Throughout document, changed "tag" emulation or emulator to "card" emulation or emulator                                                                                                                                        | <u>13</u>    |

| • | Added the sentence that starts "For interoperability purposes, TI recommends" in the first bulleted list item in                                                                                                                |              |

|   | Section 6.1.3, NFC Device Operation – Target                                                                                                                                                                                    | <u>14</u>    |

| • | Changed POLLING to SENSF_REQ in the bulleted list item that starts "If the first command is a                                                                                                                                   |              |

|   | SENSF_REQ" and deleted the sentence that started "The POLLING response is sent in" in Section 6.1.3,                                                                                                                            |              |

|   | NFC Device Operation – Target.                                                                                                                                                                                                  | <u>14</u>    |

| • | Updated the bulleted list item that starts "If the first command is ATR_REQ" in Section 6.1.3, NFC Device                                                                                                                       |              |

|   | Operation – Target                                                                                                                                                                                                              | <u>14</u>    |

| • | Changed "coded as ISO14443" to "SENSB_REQ" in the bulleted list item that starts "If the first command is a                                                                                                                     |              |

|   | SENSB_REQ" in Section 6.1.3, NFC Device Operation – Target                                                                                                                                                                      | 14           |

| • | Changed "FeliCa" to "peer-to-peer" in Section 6.1.3.1, Active Target, and Section 6.1.3.2, Passive Target                                                                                                                       | <u>14</u>    |

| • | Updated the paragraph that starts "The transmission of a response must occur after RF collision avoidance" in                                                                                                                   | 4.4          |

| • | Section 6.1.3.1, Active Target<br>Updated the paragraph that starts "The transmit system in passive target mode" in Section 6.1.3.2, Passive                                                                                    | <u>14</u>    |

| - | Target                                                                                                                                                                                                                          | 14           |

| • | Updated the description in Section 6.1.3.3, Card Emulation                                                                                                                                                                      | 15           |

| • | Added the sentence that starts "For applications in which the TRF7970A may be subjected" in the second                                                                                                                          | 10           |

|   | paragraph of † 6.3, Power Supplies                                                                                                                                                                                              | 15           |

| • | Changed $V_{DD,A}$ to $V_{DD,X}$ in the last sentence that reads "The $V_{DD,X}$ output current should not exceed 20 mA." in                                                                                                    | <u></u>      |

|   | the NOTE in Analog Supply Regulator: V <sub>DD_A</sub>                                                                                                                                                                          | 16           |

| • | Removed the paragraph that started "The RF power amplifier regulator" from Digital Supply Regulator: $V_{DD \times \dots}$                                                                                                      | 16           |

| • | Changed 250 mV to 400 mV in "a "Delta Voltage" of 400 mV below V <sub>IN</sub> "                                                                                                                                                | 16           |

| • | Added the paragraph that starts "As $V_{DD_{RF}}$ is increased, the system" in $\ddagger 6.3.2$ , Supply Regulator Settings                                                                                                     | 18           |

| • | Removed the paragraphs that started "The main receiver also has" and "By default, the AGC window                                                                                                                                |              |

|   | comparator" from # 6.4.2, Receiver Gain and Filter Stages                                                                                                                                                                       | 21           |

| • | Changed 表 6-5 to match 表 6-37                                                                                                                                                                                                   | 22           |

| • | Updated <sup>††</sup> 6.5, <i>Receiver – Digital Section</i> , to clarify and remove duplicate content                                                                                                                          | 22           |

| ٠ | Updated the description in <sup>††</sup> 6.5.1.2, <i>External RSSI</i>                                                                                                                                                          | 26           |

| • | Removed "Equivalent Series Resistance" from 表 6-9, Minimum Crystal Recommendations                                                                                                                                              | <u>28</u>    |

| • | Removed mention of 3-wire SPI and replaced "IRQ" with "Slave Select" in the first paragraph of $\ddagger$ 6.10.1,                                                                                                               |              |

|   | General Introduction                                                                                                                                                                                                            | <u>30</u>    |

| • | Updated the description of FIFO level interrupts in <sup>††</sup> 6.10.1.4, <i>FIFO Operation</i>                                                                                                                               | <u>34</u>    |

| • | Added "but recommended" to "It is optional but recommended to read the FIFO Status register" in $\ddagger$ 6.10.3,                                                                                                              |              |

|   | Reception of Air Interface Data                                                                                                                                                                                                 | <u>36</u>    |

| • |                                                                                                                                                                                                                                 | <u>37</u>    |

| • | Removed the sentence that started "The choice of one of these modes over another" from # 6.10.5, Serial                                                                                                                         | _            |

|   | Interface Communication (SPI)                                                                                                                                                                                                   | <u>37</u>    |

| • | Updated the paragraph that starts "TI recommends resetting the FIFO after receiving data" in † 6.10.5.1,                                                                                                                        | 40           |

|   | Serial Interface Mode With Slave Select (SS).                                                                                                                                                                                   | 42           |

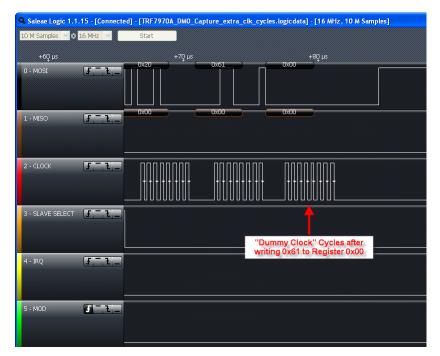

| • | Added the NOTE that starts "An additional direct mode" in <sup>††</sup> 6.10.6, <i>Direct Mode</i>                                                                                                                              | <u>43</u>    |

TEXAS INSTRUMENTS

www.ti.com

| • | Added $\ddagger$ 6.11, <i>TRF7970A Initialization</i>                                                                | <u>48</u>       |

|---|----------------------------------------------------------------------------------------------------------------------|-----------------|

|   | Compatibility                                                                                                        | 49              |

| • | Changed POLLING to SENSF_REQ and updated description in the list item that starts "If the first command is a         |                 |

|   | SENSF_REQ"                                                                                                           | 50              |

| • | Updated the description in the list item that starts "If the first command is ATR_REQ"                               | 50              |

| • | Corrected description of B1 Irq_col in 表 6-18, IRQ Status Register (0x0C) for NFC and Card Emulation                 |                 |

|   | Operation: changed from "(as defined in register 0x01)" to "(as defined in register 0x10)"                           | 51              |

| • | Removed mention of collision avoidance commands from # 6.13.2, Initiator                                             |                 |

| ٠ | Added and updated comments in 表 6-19, Address and Command Word Bit Distribution                                      |                 |

| • | Removed command code 0x15, Close Slot Sequence, from 表 6-19, Address and Command Word Bit                            |                 |

|   | Distribution                                                                                                         | <u>51</u>       |

| • | Added the sentence that starts "This command should be sent after a Software Initialization command" in $	au$        |                 |

|   | 6.14.1.1, Idle (0x00)                                                                                                | <u>52</u>       |

| ٠ | Changed the description in # 6.14.1.3, Initial RF Collision Avoidance (0x04)                                         | <u>53</u>       |

| • | Changed the description in † 6.14.1.4, Response RF Collision Avoidance (0x05)                                        | 53              |

| • | Changed the description in $\ddagger 6.14.1.5$ , Response RF Collision Avoidance (0x06, $n = 0$ )                    | 53              |

| • | Added "This is used by the ISO/IEC 15693 protocol" to <sup>††</sup> 6.14.1.11, <i>Transmit Next Time Slot (0x14)</i> | <u>54</u>       |

| • | Corrected description of B1 Irq_col in 表 6-43, IRQ Status Register (0x0C): changed from "(as defined in              |                 |

|   | register 0x01)" to "(as defined in register 0x10)"                                                                   | <u>66</u>       |

| • | Changed the description of B5:B3 in 表 6-47 from "Auxiliary RSSI represents the signal level at RX_IN2" to            | ~~              |

|   |                                                                                                                      | 68              |

| • | Removed former Section 7.1, TRF7970A Reader System Using Parallel Microcontroller Interface                          | 75              |

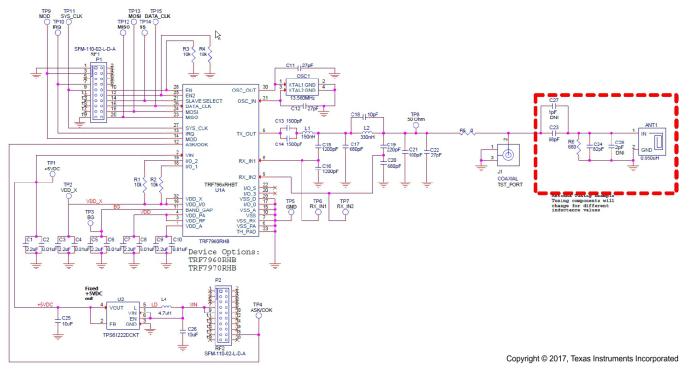

| • | Changed 🛽 7-1, Application Schematic – SPI With SS Mode MCU Interface                                                | 75              |

| • | Updated the description in 节 7.1.2, <i>Schematic</i> 添加了节 8.1"入门和后续步骤"                                               | <u>75</u><br>70 |

| • | 添加了节 8.1"入门和后续步骤"                                                                                                    | <u>/8</u><br>70 |

|   | 添加了节 8.2 <i>番件证名规则</i>                                                                                               | 78<br>79        |

|   | 逐加」 1 6.5 工具种软件<br>更新了节 8.4"文档支持"                                                                                    | 79<br>79        |

| - | 又別」   0.4 久归又汀                                                                                                       | 19              |

#### **3** Device Characteristics

Table 3-1 lists the supported modes of operation for the TRF7970A device.

| P2P INITIATOR OR REA                       | DER/WRITER                           | CARD EN      | IULATION           | P2P TARGET |                    |

|--------------------------------------------|--------------------------------------|--------------|--------------------|------------|--------------------|

| TECHNOLOGY BIT RATE<br>(kbps)              |                                      | TECHNOLOGY   | BIT RATE<br>(kbps) | TECHNOLOGY | BIT RATE<br>(kbps) |

| NFC-A and NFC-B<br>(ISO/IEC 14443 A and B) | 106, 212, 424,<br>848 <sup>(1)</sup> | NFC-A, NFC-B | 106                | NFC-A      | 106                |

| NFC-F (JIS: X6319-4)                       | 212, 424                             | N/A          | N/A                | NFC-F      | 212, 424           |

| NFC-V (ISO/IEC 15693)                      | 6.7, 26.7                            | N/A          | N/A                | N/A        | N/A                |

#### Table 3-1. Supported Modes of Operation

(1) 848 kbps applies to reader/writer mode only.

#### 3.1 Related Products

For information about other devices in this family of products or related products, see the following links.

Products for TI Wireless Connectivity Connect more with the industry's broadest wireless connectivity portfolio.

Products for NFC / RFID TI provides one of the industry's most differentiated NFC and RFID product portfolios and is your solution to meet a broad range of NFC connectivity and RFID identification needs.

Companion Products for TRF7970A Review products that are frequently purchased or used with this product.

Reference Designs for TRF7970A The TI Designs Reference Design Library is a robust reference design library that spans analog, embedded processor, and connectivity. Created by TI experts to help you jump start your system design, all TI Designs include schematic or block diagrams, BOMs, and design files to speed your time to market. Search and download designs at ti.com/tidesigns.

## **4** Terminal Configuration and Functions

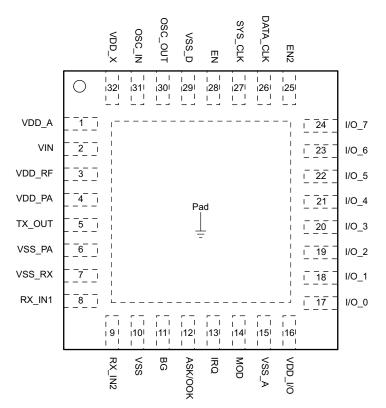

#### 4.1 Pin Diagram

Figure 4-1 shows the pinout for the 32-pin RHB package.

Figure 4-1. 32-Pin RHB Package (Top View)

#### 4.2 Signal Descriptions

Table 4-1 describes the signals.

| TERMINAL           |     | TYPE <sup>(1)</sup> | DECODIDION                                                                                 |  |

|--------------------|-----|---------------------|--------------------------------------------------------------------------------------------|--|

| NAME               | NO. | ITPE ("             | DESCRIPTION                                                                                |  |

| V <sub>DD_A</sub>  | 1   | OUT                 | Internal regulated supply (2.7 V to 3.4 V) for analog circuitry                            |  |

| V <sub>IN</sub>    | 2   | SUP                 | External supply input to chip (2.7 V to 5.5 V)                                             |  |

| V <sub>DD_RF</sub> | 3   | OUT                 | Internal regulated supply (2.7 V to 5 V), normally connected to V <sub>DD_PA</sub> (pin 4) |  |

| V <sub>DD_PA</sub> | 4   | INP                 | Supply for PA; normally connected externally to $V_{DD_{RF}}$ (pin 3)                      |  |

| TX_OUT             | 5   | OUT                 | RF output (selectable output power, 100 mW or 200 mW, with $V_{DD}$ = 5 V)                 |  |

| V <sub>SS_PA</sub> | 6   | SUP                 | Negative supply for PA; normally connected to circuit ground                               |  |

| V <sub>SS_RX</sub> | 7   | SUP                 | gative supply for RX inputs; normally connected to circuit ground                          |  |

| RX_IN1             | 8   | INP                 | in RX input                                                                                |  |

| RX_IN2             | 9   | INP                 | Auxiliary RX input                                                                         |  |

| V <sub>SS</sub>    | 10  | SUP                 | Chip substrate ground                                                                      |  |

| BAND_GAP           | 11  | OUT                 | Bandgap voltage (V <sub>BG</sub> = 1.6 V); internal analog voltage reference               |  |

|                    | 12  | סוס                 | Selection between ASK and OOK modulation (0 = ASK, 1 = OOK) for direct mode 0 or 1.        |  |

| ASK/OOK            | 12  | BID                 | Can be configured as an output to provide the received analog signal output.               |  |

(1) SUP = Supply, INP = Input, BID = Bidirectional, OUT = Output

| Table 4-1. | Terminal | Functions | (continued) | ) |

|------------|----------|-----------|-------------|---|

| 10010 1 11 |          |           | (           | / |

| TERMINAL            |     | TVDE (1)            | DESCRIPTION                                                                                                                                             |  |  |

|---------------------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                             |  |  |

| IRQ                 | 13  | OUT                 | Interrupt request                                                                                                                                       |  |  |

| MOD                 | 14  | INP                 | External data modulation input for direct mode 0 or 1                                                                                                   |  |  |

| MOD                 | 14  | OUT                 | Subcarrier digital data output (see registers 0x1A and 0x1B)                                                                                            |  |  |

| V <sub>SS_A</sub>   | 15  | SUP                 | Negative supply for internal analog circuits; connected to GND                                                                                          |  |  |

| V <sub>DD_I/O</sub> | 16  | INP                 | Supply for I/O communications (1.8 V to $V_{\text{IN}}$ ) level shifter. $V_{\text{IN}}$ should be never exceeded.                                      |  |  |

| I/O_0               | 17  | BID                 | I/O pin for parallel communication                                                                                                                      |  |  |

| I/O_1               | 18  | BID                 | I/O pin for parallel communication                                                                                                                      |  |  |

| 1/0 2               | 10  | חום                 | I/O pin for parallel communication                                                                                                                      |  |  |

| I/O_2               | 19  | BID                 | TX enable (in special direct mode)                                                                                                                      |  |  |

| 1/0.2               | 20  | BID                 | I/O pin for parallel communication                                                                                                                      |  |  |

| I/O_3               | 20  | טוס                 | TX data (in special direct mode)                                                                                                                        |  |  |

| 1/0_4               | 01  | סוס                 | I/O pin for parallel communication                                                                                                                      |  |  |

| I/O_4               | 21  | BID                 | Slave select signal in SPI mode                                                                                                                         |  |  |

|                     | 22  | BID                 | I/O pin for parallel communication                                                                                                                      |  |  |

| I/O_5               | 22  | טוס                 | Data clock output in direct mode 1 and special direct mode                                                                                              |  |  |

|                     |     |                     | I/O pin for parallel communication                                                                                                                      |  |  |

| I/O_6               | 23  | BID                 | MISO for serial communication (SPI)                                                                                                                     |  |  |

|                     |     |                     | Serial bit data output in direct mode 1 or subcarrier signal in direct mode 0                                                                           |  |  |

| I/O_7               | 24  | BID                 | I/O pin for parallel communication.                                                                                                                     |  |  |

| 1/O_7               | 24  | טוס                 | MOSI for serial communication (SPI)                                                                                                                     |  |  |

| EN2                 | 25  | INP                 | Selection of power down mode. If EN2 is connected to $V_{IN}$ , then $V_{DD_X}$ is active during power down mode 2 (for example, to supply the MCU).    |  |  |

| DATA_CLK            | 26  | INP                 | Data clock input for MCU communication (parallel and serial)                                                                                            |  |  |

|                     |     |                     | If EN = 1 (EN2 = don't care) the system clock for MCU is configured. Depending on the crystal that is used, options are as follows (see register 0x09): |  |  |

| SYS_CLK             | 27  | OUT                 | 13.56-MHz crystal: Off, 3.39 MHz, 6.78 MHz, or 13.56 MHz                                                                                                |  |  |

|                     |     |                     | 27.12-MHz crystal: Off, 6.78 MHz, 13.56 MHz, or 27.12 MHz                                                                                               |  |  |

|                     |     |                     | If EN = 0 and EN2 = 1, then system clock is set to 60 kHz                                                                                               |  |  |

| EN                  | 28  | INP                 | Chip enable input (If EN = 0, then chip is in sleep or power-down mode).                                                                                |  |  |

| V <sub>SS_D</sub>   | 29  | SUP                 | Negative supply for internal digital circuits                                                                                                           |  |  |

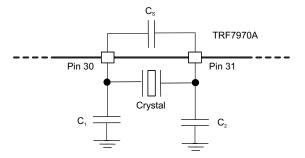

| OSC_OUT             | 30  | OUT                 | Crystal or oscillator output                                                                                                                            |  |  |

| OSC_IN              | 31  | INP                 | Crystal or oscillator input                                                                                                                             |  |  |

|                     |     |                     | Crystal oscillator output                                                                                                                               |  |  |

| V <sub>DD_X</sub>   | 32  | OUT                 | Internally regulated supply (2.7 V to 3.4 V) for digital circuit and external devices (for example, an MCU)                                             |  |  |

| Thermal Pad         | PAD | SUP                 | Chip substrate ground                                                                                                                                   |  |  |

#### **Specifications** 5

#### Absolute Maximum Ratings<sup>(1)</sup> <sup>(2)</sup> 5.1

over operating free-air temperature range (unless otherwise noted)

|                  |                                                |                                                            | MIN | MAX | UNIT |

|------------------|------------------------------------------------|------------------------------------------------------------|-----|-----|------|

| V <sub>IN</sub>  | Input voltage range                            | -0.3                                                       | 6   | V   |      |

| I <sub>IN</sub>  | Maximum current V <sub>IN</sub>                |                                                            | 150 | mA  |      |

| TJ               |                                                | Any condition                                              |     | 140 | °C   |

|                  | Maximum operating virtual junction temperature | Continuous operation, long-term reliability <sup>(3)</sup> |     | 125 | °C   |

| T <sub>STG</sub> | Storage temperature                            | ·                                                          | -55 | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values are with respect to substrate ground terminal V<sub>SS</sub>. The maximum junction temperature for continuous operation is limited by package constraints. Operation above this temperature may (3) result in reduced reliability or lifetime of the device.

#### 5.2 ESD Ratings

|                                            |                                                                             |                                                                                        | VALUE | UNIT |

|--------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000                                                                                  | V     |      |

|                                            | 6                                                                           | Charged-device model (CDM), per JEDEC specification JESD22-C101, all pins $^{\rm (2)}$ | ±500  | V    |

|                                            |                                                                             | Machine model (MM)                                                                     | ±200  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2000 V may actually have higher performance.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V (2) may actually have higher performance.

#### **Recommended Operating Conditions** 5.3

over operating free-air temperature range (unless otherwise noted)

|                 |                                        |                                                             | MIN                          | TYP | MAX                          | UNIT |

|-----------------|----------------------------------------|-------------------------------------------------------------|------------------------------|-----|------------------------------|------|

| V <sub>IN</sub> | Operating input voltage                | 2.7                                                         | 5                            | 5.5 | V                            |      |

| T <sub>A</sub>  | Operating ambient temperature          | -40                                                         | 25                           | 110 | °C                           |      |

| $T_{\rm J}$     | Operating virtual junction temperature | -40                                                         | 25                           | 125 | °C                           |      |

| V <sub>IL</sub> | Input voltage, logic low               | I/O lines, IRQ, SYS_CLK, DATA_CLK,<br>EN, EN2, ASK/OOK, MOD |                              |     | 0.2 ×<br>V <sub>DD_I/O</sub> | V    |

| VIH             | Input voltage threshold, logic high    | I/O lines, IRQ, SYS_CLK, DATA_CLK,<br>EN, EN2, ASK/OOK, MOD | 0.8 ×<br>V <sub>DD_l/O</sub> |     |                              | V    |

#### 5.4 **Electrical Characteristics**

TYP operating conditions are  $T_A = 25^{\circ}$ C, VIN = 5 V, full-power mode (unless otherwise noted)

MIN and MAX operating conditions are over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                       | PARAMETER                                             | TEST CONDITIONS                                                                                                                                  | MIN | TYP                          | MAX | UNIT             |

|-----------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------|-----|------------------|

| V <sub>OL</sub>       | Low-level output voltage                              |                                                                                                                                                  |     | 0.2 ×<br>V <sub>DD_I/O</sub> |     | V                |

| V <sub>OH</sub>       | High-level output voltage                             |                                                                                                                                                  |     | 0.8 ×<br>V <sub>DD_l/O</sub> |     | V                |

| I <sub>PD1</sub>      | Supply current in power down mode 1                   | All building blocks disabled, including<br>supply-voltage regulators; measured after<br>500-ms settling time (EN = 0, EN2 = 0)                   |     | 0.5                          | 5   | μA               |

| I <sub>PD2</sub>      | Supply current in power down mode 2 (sleep mode)      | The SYS_CLK generator and $V_{DD_X}$<br>remain active to support external circuitry;<br>measured after 100-ms settling time<br>(EN = 0, EN2 = 1) |     | 120                          | 200 | μA               |

| I <sub>STBY</sub>     | Supply current in stand-by mode                       | Oscillator running, supply-voltage<br>regulators in low-consumption mode<br>(EN = 1, EN2 = x)                                                    |     | 1.9                          | 3.5 | mA               |

| I <sub>ON1</sub>      | Supply current without antenna driver current         | Oscillator, regulators, RX and AGC active, TX is off                                                                                             |     | 10.5                         | 14  | mA               |

| I <sub>ON2</sub>      | Supply current, TX (half power)                       | Oscillator, regulators, RX and AGC and TX active, P <sub>OUT</sub> = 100 mW                                                                      |     | 70                           | 78  | mA               |

| I <sub>ON3</sub>      | Supply current, TX (full power)                       | Oscillator, regulators, RX and AGC and TX active, $P_{OUT} = 200 \text{ mW}$                                                                     |     | 130                          | 150 | mA               |

| V <sub>POR</sub>      | Power-on-reset voltage                                | Input voltage at V <sub>IN</sub>                                                                                                                 | 1.4 | 2                            | 2.6 | V                |

| V <sub>BG</sub>       | Bandgap voltage (pin 11)                              | Internal analog reference voltage                                                                                                                | 1.5 | 1.6                          | 1.7 | V                |

| V <sub>DD_A</sub>     | Regulated output voltage for analog circuitry (pin 1) | V <sub>IN</sub> = 5 V                                                                                                                            | 3.1 | 3.4                          | 3.8 | V                |

| V <sub>DD_X</sub>     | Regulated supply for external circuitry               | Output voltage pin 32, V <sub>IN</sub> = 5 V                                                                                                     | 3.1 | 3.4                          | 3.8 | V                |

| I <sub>VDD_Xmax</sub> | Maximum output current of V <sub>DD X</sub>           | Output current pin 32, V <sub>IN</sub> = 5 V                                                                                                     |     |                              | 20  | mA               |

|                       |                                                       | Half-power mode, V <sub>IN</sub> = 2.7 V to 5.5 V                                                                                                |     | 8                            | 12  |                  |

| R <sub>RFOUT</sub>    | Antenna driver output resistance (1)                  | Full-power mode, V <sub>IN</sub> = 2.7 V to 5.5 V                                                                                                |     | 4                            | 6   | Ω                |

| R <sub>RFIN</sub>     | RX_IN1 and RX_IN2 input resistance                    |                                                                                                                                                  | 4   | 10                           | 20  | kΩ               |

| V <sub>RF_INmax</sub> | Maximum RF input voltage at RX_IN1 and RX_IN2         | V <sub>RF_INmax</sub> should not exceed V <sub>IN</sub>                                                                                          |     | 3.5                          |     | V <sub>pp</sub>  |

| .,                    | Minimum RF input voltage at RX_IN1                    | f <sub>SUBCARRIER</sub> = 424 kHz                                                                                                                |     | 1.4                          | 2.5 |                  |

| $V_{RF}_{INmin}$      | and RX_IN2 (input sensitivity) <sup>(2)</sup>         | f <sub>SUBCARRIER</sub> = 848 kHz                                                                                                                |     | 2.1                          | 3   | mV <sub>pp</sub> |

| f <sub>SYS_CLK</sub>  | SYS_CLK frequency                                     | In power mode 2, EN = 0, EN2 = 1                                                                                                                 | 25  | 60                           | 120 | kHz              |

| f <sub>C</sub>        | Carrier frequency                                     | Defined by external crystal                                                                                                                      |     | 13.56                        |     | MHz              |

| t <sub>CRYSTAL</sub>  | Crystal run-in time                                   | Time until oscillator stable bit is set (register 0x0F) <sup>(3)</sup>                                                                           |     | 3                            |     | ms               |

| f <sub>D_CLKmax</sub> | Maximum DATA_CLK frequency <sup>(4)</sup>             | Depends on capacitive load on the I/O lines, TI recommends 2 MHz <sup>(4)</sup>                                                                  | 2   | 4                            | 10  | MHz              |

| R <sub>OUT</sub>      | Output resistance I/O_0 to I/O_7                      |                                                                                                                                                  |     | 500                          | 800 | Ω                |

| R <sub>SYS_CLK</sub>  | Output resistance R <sub>SYS CLK</sub>                |                                                                                                                                                  |     | 200                          | 400 | Ω                |

Antenna driver output resistance (1)

Measured with subcarrier signal at RX\_IN1 or RX\_IN2 and measured the digital output at MOD pin with register 0x1A bit 6 = 1. (2)

(3) (4)

Depends on the crystal parameters and components TI recommends a DATA\_CLK speed of 2 MHz. Higher data clock depends on the capacitive load. Maximum SPI clock speed should not exceed 10 MHz. This clock speed is acceptable only when external capacitive load is less than 30 pF. MISO driver has a typical output resistance of 400  $\Omega$  (12-ns time constant when 30-pF load used).

www.ti.com

#### 5.5 Thermal Resistance Characteristics

| PACKAGE      | 0               | θ <sub>JA</sub> <sup>(1)</sup> | POWER RATING <sup>(2)</sup> |                       |  |

|--------------|-----------------|--------------------------------|-----------------------------|-----------------------|--|

|              | θ <sup>JC</sup> | UJA`´                          | T <sub>A</sub> ≤ 25°C       | T <sub>A</sub> ≤ 85°C |  |

| RHB (32 pin) | 31°C/W          | 36.4°C/W                       | 2.7 W                       | 1.1 W                 |  |

(1) This data was taken using the JEDEC standard high-K test PCB.

(2) Power rating is determined with a junction temperature of 125°C. This is the temperature at which distortion starts to increase substantially. Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance and long-term reliability.

## 5.6 Switching Characteristics

TYP operating conditions are  $T_A = 25^{\circ}$ C, VIN = 5 V, full-power mode (unless otherwise noted) MIN and MAX operating conditions are over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

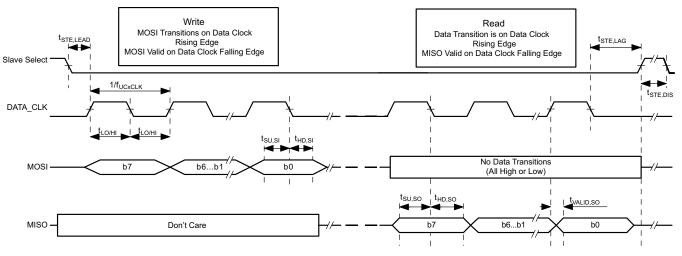

|                       | PARAMETER                                                                             | TEST CONDITIONS                                            | MIN | TYP  | MAX | UNIT |

|-----------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------|-----|------|-----|------|

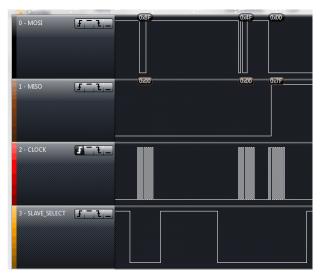

| t <sub>LO/HI</sub>    | DATA_CLK time high or low, one half of DATA_CLK at 50% duty cycle                     | Depends on capacitive load on the I/O lines <sup>(1)</sup> | 250 | 62.5 | 50  | ns   |

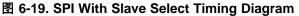

| t <sub>STE,LEAD</sub> | Slave select lead time, slave select low to clock                                     |                                                            |     | 200  |     | ns   |

| t <sub>STE,LAG</sub>  | Slave select lag time, last clock to slave select high                                |                                                            |     | 200  |     | ns   |

| t <sub>STE,DIS</sub>  | Slave select disable time, slave select rising edge to next slave select falling edge |                                                            | 300 |      |     | ns   |

| t <sub>SU,SI</sub>    | MOSI input data setup time                                                            |                                                            | 15  |      |     | ns   |

| t <sub>HD,SI</sub>    | MOSI input data hold time                                                             |                                                            | 15  |      |     | ns   |

| t <sub>SU,SO</sub>    | MISO input data setup time                                                            |                                                            | 15  |      |     | ns   |

| t <sub>HD,SO</sub>    | MISO input data hold time                                                             |                                                            | 15  |      |     | ns   |

| t <sub>VALID,SO</sub> | MISO output data valid time                                                           | DATA_CLK edge to MISO valid,<br>$C_L \le 30 \text{ pF}$    | 30  | 50   | 75  | ns   |

(1) TI recommends a DATA\_CLK speed of 2 MHz. Higher data clock depends on the capacitive load. Maximum SPI clock speed should not exceed 10 MHz. This clock speed is acceptable only when external capacitive load is less than 30 pF. MISO driver has a typical output resistance of 400 Ω (12-ns time constant when 30-pF load used).

## 6 Detailed Description

#### 6.1 Overview

#### 6.1.1 RFID and NFC Operation – Reader and Writer

The TRF7970A is a high-performance 13.56-MHz HF RFID and NFC transceiver IC composed of an integrated analog front end (AFE) and a built-in data framing engine for ISO/IEC 15693, ISO/IEC 14443 A and B, and FeliCa. This includes data rates up to 848 kbps for ISO/IEC 14443 with all framing and synchronization tasks on board (in default mode). The TRF7970A also supports NFC tag type 1, 2, 3, 4, and 5 operations. This architecture lets the customer build a complete cost-effective yet high-performance multiprotocol 13.56-MHz RFID and NFC system together with a low-cost microcontroller.

Other standards and even custom protocols can be implemented by using either of the direct modes that the device offers. These direct modes (0 and 1) allow the user to fully control the analog front end (AFE) and also gain access to the raw subcarrier data or the unframed but already ISO formatted data and the associated (extracted) clock signal.

The receiver system has a dual input receiver architecture. The receivers also include various automatic and manual gain control options. The received input bandwidth can be selected to cover a broad range of input subcarrier signal options.

The received signal strength from transponders, ambient sources, or internal levels is available through the RSSI register. The receiver output is selectable among a digitized subcarrier signal and any of the integrated subcarrier decoders. The selected subcarrier decoder delivers the data bit stream and the data clock as outputs.

The TRF7970A also includes a receiver framing engine. This receiver framing engine performs the CRC or parity check, removes the EOF and SOF settings, and organizes the data in bytes for ISO/IEC 14443 A and B, ISO/IEC 15693, and FeliCa protocols. Framed data is then accessible to the microcontroller (MCU) through a 127-byte FIFO register.

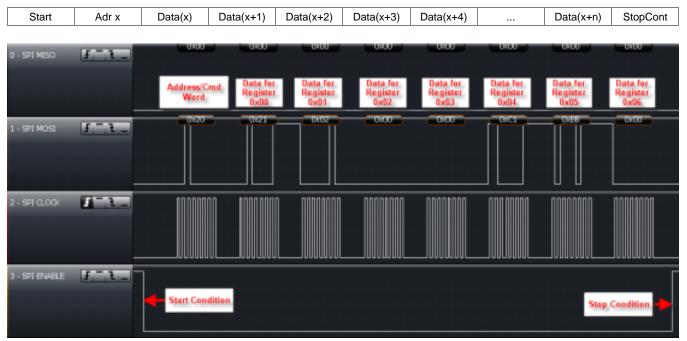

A parallel or serial interface (SPI) can be used for the communication between the MCU and the TRF7970A reader. When the built-in hardware encoders and decoders are used, transmit and receive functions use a 127-byte FIFO register. For direct transmit or receive functions, the encoders and decoders can be bypassed so that the MCU can process the data in real time. The TRF7970A supports data communication voltage levels from 1.8 V to 5.5 V for the MCU I/O interface. The transmitter has selectable output-power levels of 100 mW (+20 dBm) or 200 mW (+23 dBm) equivalent into a 50- $\Omega$  load when using a 5-V supply.

The transmitter supports OOK and ASK modulation with selectable modulation depth. The TRF7970A also includes a data transmission engine that comprises low-level encoding for ISO/IEC 15693, ISO/IEC 14443 A and B, and FeliCa. Included with the transmit data coding is the automatic generation of Start Of Frame (SOF), End Of Frame (EOF), Cyclic Redundancy Check (CRC), and parity bits.

Several integrated voltage regulators ensure a proper power-supply noise rejection for the complete reader system. The built-in programmable auxiliary voltage regulator  $V_{DD_X}$  (pin 32), is able to deliver up to 20 mA to supply a microcontroller and additional external circuits within the reader system.

#### 6.1.2 NFC Device Operation – Initiator

The transmitting system includes an RF level detector (programmable level) which is used for initial (or response) RF collision avoidance. The RF collision avoidance sequence is started by sending a direct command. If successful, the NFC initiator can send the data or commands, the MCU has loaded in the FIFO register. The coding of this data is done by hardware coders in ISO/IEC 14443 A and B, or FeliCa format. The coders also provide CRC and parity bits (if required) and automatically add preambles, SOF, EOF, and synchronization bytes as defined by selected protocol.

The receiver system offers the same analog features (AGC, AM or PM, bandwidth selection, and so on) as described previously in RFID and NFC reader and writer description. The system comprises integrated decoders for passive targets (ISO/IEC 14443 A or ISO/IEC 14443 B tag or FeliCa) or active targets (ISO/IEC 14443 A or ISO/IEC 14443 B reader or FeliCa). For all this options, the system also supports framing including CRC and parity check and removal of SOF, EOF, and synchronization bytes as specified by the selected protocol.

#### 6.1.3 NFC Device Operation – Target

The activation of NFC target is done when a sufficient RF field level is detected on the antenna. The level needed for wake-up is selectable and is stored in a nonvolatile register.

When the activation occurs, the system performs automatic power-up and waits for the first command to be received. Based on this command, the system knows if it should operate as passive or active target and at what bit rate. After activation, the receiver system offers the same analog features (for example, AGC, AM/PM, and bandwidth selection) as in the case of an RFID reader.

When used as the NFC target, the chip is typically in a power down or standby mode. If EN2 = H, the chip keeps the supply system on. If EN2 = L and EN = L, the chip is in complete power down. To operate as NFC target or card emulator, the MCU must load a value different from zero (0) in the Target Detection Level register (B0-B2) to enable the RF measurement system (supplied by VEXT, so it can also operate during complete power down and consume only 3.5  $\mu$ A). The RF measurement constantly monitors the RF signal on the antenna input. When the RF level on the antenna input exceeds the level defined in the in Target Detection Level register, the chip is automatically activated (EN is internally forced high).

When the voltage supply system and the oscillator are started and are stable,  $osc_ok$  goes high (B6 of RSSI Level and Oscillator Status register) and IRQ is sent with bit B2 = 1 of IRQ register (field change). Bit B7 NFC Target Protocol in register directly displays the status of RF level detection (running constantly also during normal operation). This informs the MCU that the chip should start operation as NFC TARGET device. When the first command from the INITIATOR is received, another IRQ sent with B6 (RX start) set in the IRQ register. The MCU must set EN = H (confirm the power up) in the time between the two IRQs, because the internal power-up ends after the second IRQ. The type and coding of the first initiator (or reader in the case of a card emulator) command defines the communication protocol type that the target must use. Therefore, the communication protocol type is available in the NFC Target Protocol register immediately after receiving the first command.

Based on the first command from the INITIATOR, the following actions are taken:

- If the first command is SENS\_REQ or ALL\_REQ, the TARGET must enter the SDD protocol for 106-kbps passive communication to begin; afterward, the baud rate can be changed to 212 kbps or 424 kbps, which is determined by the NFC initiator device. If bit B5 in the NFC Target Detection Level register is not set, the MCU handles the SDD and the command received is send to FIFO. For interoperability purposes, TI recommends allowing the MCU to handle the SDD process rather than use the TRF7970A Auto-SDD feature to ensure interoperability with other NFC devices. If the RF field is turned off (B7 in NFC Target Protocol register is low) at any time, the system sends an IRQ to the MCU with bit B2 (RF field change) in the IRQ register set high. This informs the MCU that the procedure was aborted and the system must be reset. The clock extractor is automatically activated in this mode.

- If the command is SENS\_REQ or ALL\_REQ and the card emulation bit in ISO Control register is set, the system emulates an ISO/IEC 14443 A or ISO/IEC 14443 B tag. The procedure does not differ from the one previously described for the case of a passive target at 106 kbps. The clock extractor is automatically activated in this mode.

- If the first command is a SENSF\_REQ, the system becomes the TARGET in passive communication using 212 kbps or 424 kbps. The SDD is relatively simple and is handled by the MCU directly.

- If the first command is ATR\_REQ, the system operates as an active TARGET using the same communication speed and bit coding as used by the INITIATOR. Again, all of the replies are handled by the MCU. The MCU should handle the timing requirements for collision avoidance. This is done by using external RSSI to detect external RF fields before enabling RF on the TRF7970A.

- If the first command is a SENSB\_REQ request and the card emulation bit is set in the ISO Control register, the system enters ISO/IEC 14443 B emulation mode. The anticollision must be handled by the MCU, and the chip provides all physical level coding, decoding, and framing for this protocol.

#### 6.1.3.1 Active Target

If the first command received by the RF interface defines the system as an active target, then the receiver selects the appropriate data decoders (ISO/IEC 14443 A or ISO/IEC 14443 B reader or peer-to-peer) and framing option. Only the raw (decoded) data is forwarded to the MCU through the FIFO. SOF, EOF, preamble, sync bytes, CRC, and parity bytes are checked by the framer and discarded.

The transmission of a response must occur after RF collision avoidance has been processed. The recommended method for RF collision avoidance is to use external RSSI to detect any external RF field. If successful, the NFC initiator can send the data that the MCU has loaded in the FIFO register. The coding of this data is done by hardware coders either in ISO/IEC 14443 A format (106-kbps system) or in peer-to-peer format for (212-kbps and 424-kbps systems). The coders also provide CRC and parity bits (if required) and automatically add preambles, SOF, EOF, and synchronization bytes as defined by selected protocol.

#### 6.1.3.2 Passive Target

If the first command received by the RF interface defines the system as a passive target, then the receiver selects the appropriate data decoders (ISO/IEC 14443 A or ISO/IEC 14443 B reader or peer-to-peer) and framing option. Again, only the raw (decoded) data is forwarded to the MCU through the FIFO; SOF, EOF, preamble, sync bytes, CRC, and parity bytes are checked by the framer and discarded. The receiver works same as in the case of an active target.

The transmit system in passive target mode differs from active target and operates similar to the standard tag. There is no RF collision avoidance sequence, and encoders are used to code the data for ISO/IEC 14443 A or ISO/IEC 14443 B tag (at 106 kbps, to start) or peer-to-peer (at 212 kbps, to start) format. The coding system adds all of the SOF, EOF, CRC, parity bits, and synchronization bytes that are required by protocol. The response is transmitted over-the-air with a method known as load modulation.

#### 6.1.3.3 Card Emulation

The chip can enter this mode by setting appropriate option bits. The chip can emulate ISO/IEC 14443 A and B card types. For ISO/IEC 14443 A and B, the emulation supports 106-kbps data rate to start. For ISO/IEC 14443 A, the anticollision algorithm can be performed using an internal state machine, which relieves the MCU of any real-time tasks; however, this method can present interoperability challenges with other NFC devices due to timing requirements. To ensure best interoperability, TI recommends allowing the MCU to manage the anticollision process, instead. The unique ID required for anticollision is provided by the MCU after wakeup of the system.

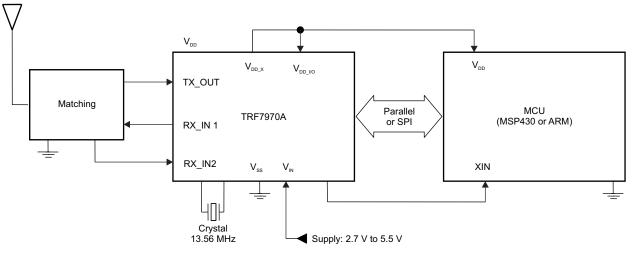

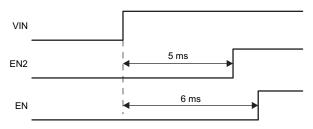

#### 6.2 System Block Diagram

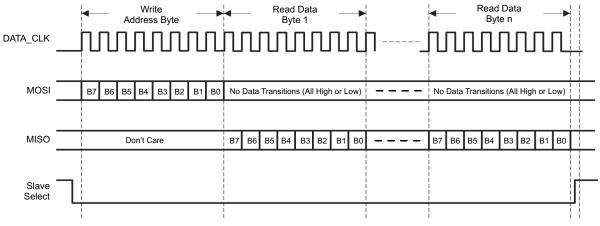

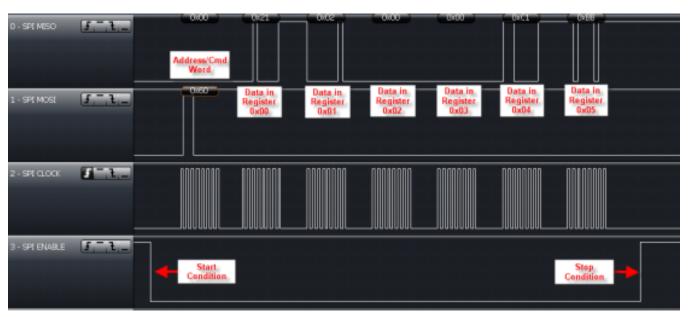

8 6-2 shows a block diagram of the TRF7970A.

Copyright © 2017, Texas Instruments Incorporated

图 6-2. System Block Diagram

## 6.3 Power Supplies

The TRF7970A positive supply input V<sub>IN</sub> (pin 2) sources three internal regulators with output voltages  $V_{DD\_RF}$ ,  $V_{DD\_A}$  and  $V_{DD\_X}$ . All regulators use external bypass capacitors for supply noise filtering and must be connected as indicated in reference schematics. These regulators provide a high power supply reject ratio (PSRR) as required for RFID reader systems. All regulators are supplied by  $V_{IN}$  (pin 2).

The regulators are not independent and have common control bits in register 0x0B for output voltage setting. The regulators can be configured to operate in either automatic or manual mode (register 0x0B, bit 7). The automatic regulator setting mode ensures an optimal compromise between PSRR and the highest possible supply voltage for RF output (to ensure maximum RF power output). The manual mode allows the user to manually configure the regulator settings. For applications in which the TRF7970A may be subjected to external noise, manually reducing the regulator settings can improve RF performance.

版权 © 2011-2017, Texas Instruments Incorporated

#### 6.3.1 Supply Arrangements

#### Regulator Supply Input: V<sub>IN</sub>

The positive supply at V<sub>IN</sub> (pin 2) has an input voltage range of 2.7 V to 5.5 V. V<sub>IN</sub> provides the supply input sources for three internal regulators with the output voltages  $V_{DD_RF}$ ,  $V_{DD_A}$ , and  $V_{DD_X}$ . External bypass capacitors for supply noise filtering must be used (per reference schematics).

#### RF Power Amplifier Regulator: V<sub>DD\_RF</sub>

The  $V_{DD\_RF}$  (pin 3) regulator is supplying the RF power amplifier. The voltage regulator can be set for either 5-V or 3-V operation. External bypass capacitors for supply noise filtering must be used (per reference schematics). When configured for 5-V manual-operation, the  $V_{DD\_RF}$  output voltage can be set from 4.3 V to 5 V in 100-mV steps. In 3-V manual-operation, the output can be programmed from 2.7 V to 3.4 V in 100-mV steps. The maximum output current capability for 5-V operation is 150 mA and for 3-V operation is 100 mA.

#### Analog Supply Regulator: V<sub>DD\_A</sub>

> 注 The configuration of  $V_{DD_A}$  and  $V_{DD_X}$  regulators are not independent from each other. The  $V_{DD_X}$  output current should not exceed 20 mA.

#### Digital Supply Regulator: V<sub>DD\_X</sub>

The digital supply regulator  $V_{DD_X}$  (pin 32) provides the power for the internal digital building blocks and can also be used to supply external electronics within the reader system. When configured for 3-V operation, the output voltage can be set from 2.7 to 3.4 V in 100-mV steps. External bypass capacitors for supply noise filtering must be used (per reference schematics).

注 The configuration of the  $V_{DD_A}$  and  $V_{DD_X}$  regulators are not independent from each other. The  $V_{DD_X}$  output current should not exceed 20 mA.

By default, the regulators are set in automatic regulator setting mode. In this mode, the regulators are automatically set every time the system is activated by setting EN input High or each time the automatic regulator setting bit, B7 in register 0x0B is set to a 1. The action is started on the 0 to 1 transition. This means that, if the user wants to rerun the automatic setting from a state in which the automatic setting bit is already high, the automatic setting bit (B7 in register 0x0B) should be changed: 1-0-1.

By default, the regulator setting algorithm sets the regulator outputs to a "Delta Voltage" of 400 mV below  $V_{IN}$ , but not higher than 5 V for  $V_{DD_RF}$  and 3.4 V for  $V_{DD_A}$  and  $V_{DD_A}$ .

#### Power Amplifier Supply: V<sub>DD\_PA</sub>

The power amplifier of the TRF7970A is supplied through  $V_{DD_PA}$  (pin 4). The positive supply pin for the RF power amplifier is externally connected to the regulator output  $V_{DD_RF}$  (pin 3).

#### I/O Level Shifter Supply: V<sub>DD I/O</sub>

The TRF7970A has a separate supply input  $V_{DD_{L}/O}$  (pin 16) for the built-in I/O level shifter. The supported input voltage ranges from 1.8 V to  $V_{IN}$ , not exceeding 5.5 V. Pin 16 is used to supply the I/O interface pins (I/O\_0 to I/O\_7), IRQ, SYS\_CLK, and DATA\_CLK pins of the reader. In typical applications,  $V_{DD_{L}/O}$  is directly connected to  $V_{DD_{L}X}$ , while  $V_{DD_{L}X}$  also supplies the MCU. This ensures that the I/O signal levels of the MCU match the logic levels of the TRF7970A.

#### Negative Supply Connections: V<sub>SS</sub>, V<sub>SS\_TX</sub>, V<sub>SS\_RX</sub>, V<sub>SS\_A</sub>, V<sub>SS\_PA</sub>

The negative supply connections  $V_{SS X}$  of each functional block are all externally connected to GND.

The substrate connection is V<sub>SS</sub> (pin 10), the analog negative supply is V<sub>SS\_A</sub> (pin 15), the logic negative supply is V<sub>SS\_D</sub> (pin 29), the RF output stage negative supply is V<sub>SS\_PA</sub> (pin 6), and the negative supply for the RF receiver V<sub>SS\_RX</sub> (pin 7).

## 6.3.2 Supply Regulator Settings

The input supply voltage mode of the reader needs to be selected. This is done in the Chip Status Control register (0x00). Bit 0 in register 0x00 selects between 5-V or 3-V input supply voltage. The default configuration is 5 V, which reflects an operating supply voltage range of 4.3 V to 5.5 V. If the supply voltage is below 4.3 V, the 3-V configuration should be used.

As  $V_{DD_{RF}}$  is increased, the system can become more susceptible to noise coupling on the RX lines. For minimum noise coupling, TI recommends using the value of 0x00. For improved range, higher  $V_{DD_{RF}}$  voltages may be set, but complete system testing is required to determine the value which provides optimal performance.

The various regulators can be configured to operate in automatic or manual mode. This is done in the Regulator and I/O Control register (0x0B), as shown in  $\frac{1}{5}$  6-1 and  $\frac{1}{5}$  6-2.

| REGISTER         |           |     |    |    |    |    |    | ER <sup>(1)</sup> |                                                                                       |

|------------------|-----------|-----|----|----|----|----|----|-------------------|---------------------------------------------------------------------------------------|

| ADDRESS<br>(hex) | B7        | B6  | B5 | B4 | B3 | B2 | B1 | B0                | COMMENTS                                                                              |

| Automatic Mod    | de (defau | lt) |    |    |    |    |    |                   |                                                                                       |

| 0B               | 1         | х   | х  | х  | х  | х  | 0  | 0                 | Automatic regulator setting 400-mV difference                                         |

| Manual Mode      |           |     |    |    |    |    |    |                   |                                                                                       |

| 0B               | 0         | х   | х  | х  | х  | 1  | 1  | 1                 | $V_{DD_{RF}} = 5 \text{ V}, V_{DD_{A}} = 3.4 \text{ V}, V_{DD_{X}} = 3.4 \text{ V}$   |

| 0B               | 0         | х   | х  | х  | х  | 1  | 1  | 0                 | $V_{DD_RF} = 4.9 \text{ V}, V_{DD_A} = 3.4 \text{ V}, V_{DD_X} = 3.4 \text{ V}$       |

| 0B               | 0         | х   | x  | x  | x  | 1  | 0  | 1                 | $V_{DD\_RF} = 4.8 \text{ V}, V_{DD\_A} = 3.4 \text{ V}, V_{DD\_X} = 3.4 \text{ V}$    |

| 0B               | 0         | х   | х  | х  | х  | 1  | 0  | 0                 | $V_{DD_RF} = 4.7 \text{ V}, V_{DD_A} = 3.4 \text{ V}, V_{DD_X} = 3.4 \text{ V}$       |

| 0B               | 0         | х   | х  | х  | х  | 0  | 1  | 1                 | $V_{DD_RF} = 4.6 \text{ V}, V_{DD_A} = 3.4 \text{ V}, V_{DD_X} = 3.4 \text{ V}$       |

| 0B               | 0         | х   | х  | х  | х  | 0  | 1  | 0                 | $V_{DD_RF} = 4.5 \text{ V}, V_{DD_A} = 3.4 \text{ V}, V_{DD_X} = 3.4 \text{ V}$       |

| 0B               | 0         | х   | х  | х  | x  | 0  | 0  | 1                 | $V_{DD_{RF}} = 4.4 \text{ V}, V_{DD_{A}} = 3.4 \text{ V}, V_{DD_{X}} = 3.4 \text{ V}$ |

| 0B               | 0         | x   | х  | х  | x  | 0  | 0  | 0                 | $V_{DD_{RF}}$ = 4.3 V, $V_{DD_{A}}$ = 3.4 V, $V_{DD_{X}}$ = 3.4 V                     |

#### 表 6-1. Supply Regulator Setting: 5-V System

(1) x = Don't care

#### 表 6-2. Supply Regulator Setting: 3-V System

| REGISTER         | OPT        | ION BITS | SETTING | IN REGU |    | ONTROL | REGISTE | ER <sup>(1)</sup> |                                                                                       |

|------------------|------------|----------|---------|---------|----|--------|---------|-------------------|---------------------------------------------------------------------------------------|

| ADDRESS<br>(hex) | B7         | B6       | B5      | B4      | B3 | B2     | B1      | B0                | COMMENTS                                                                              |

| Automatic Mod    | de (defaul | t)       |         |         |    |        |         |                   |                                                                                       |

| 0B               | 1          | х        | х       | х       | х  | х      | 0       | 0                 | Automatic regulator setting 400-mV difference                                         |

| Manual Mode      |            |          |         |         |    |        |         |                   |                                                                                       |

| 0B               | 0          | х        | х       | х       | х  | 1      | 1       | 1                 | $V_{DD_RF} = 3.4 \text{ V}, V_{DD_A} = 3.4 \text{ V}, V_{DD_X} = 3.4 \text{ V}$       |

| 0B               | 0          | х        | х       | х       | х  | 1      | 1       | 0                 | $V_{DD_{RF}} = 3.3 \text{ V}, V_{DD_{A}} = 3.3 \text{ V}, V_{DD_{X}} = 3.3 \text{ V}$ |

| 0B               | 0          | х        | х       | х       | х  | 1      | 0       | 1                 | $V_{DD_RF} = 3.2 \text{ V}, V_{DD_A} = 3.2 \text{ V}, V_{DD_X} = 3.2 \text{ V}$       |

| 0B               | 0          | х        | х       | х       | х  | 1      | 0       | 0                 | $V_{DD_{RF}} = 3.1 \text{ V}, V_{DD_{A}} = 3.1 \text{ V}, V_{DD_{X}} = 3.1 \text{ V}$ |

| 0B               | 0          | х        | х       | х       | х  | 0      | 1       | 1                 | $V_{DD_RF} = 3.0 \text{ V}, V_{DD_A} = 3.0 \text{ V}, V_{DD_X} = 3.0 \text{ V}$       |

| 0B               | 0          | х        | х       | х       | х  | 0      | 1       | 0                 | $V_{DD_RF} = 2.9 \text{ V}, V_{DD_A} = 2.9 \text{ V}, V_{DD_X} = 2.9 \text{ V}$       |

| 0B               | 0          | х        | х       | х       | х  | 0      | 0       | 1                 | $V_{DD_{RF}} = 2.8 \text{ V}, V_{DD_{A}} = 2.8 \text{ V}, V_{DD_{X}} = 2.8 \text{ V}$ |

| 0B               | 0          | х        | x       | x       | x  | 0      | 0       | 0                 | $V_{DD_{RF}} = 2.7 \text{ V}, V_{DD_{A}} = 2.7 \text{ V}, V_{DD_{X}} = 2.7 \text{ V}$ |

(1) x = Don't care

The regulator configuration function adjusts the regulator outputs by default to 400 mV below  $V_{IN}$  level, but not higher than 5 V for  $V_{DD_RF}$ , 3.4 V for  $V_{DD_A}$  and  $V_{DD_X}$ . This ensures the highest possible supply voltage for the RF output stage while maintaining an adequate PSRR (power supply rejection ratio).

#### 6.3.3 Power Modes

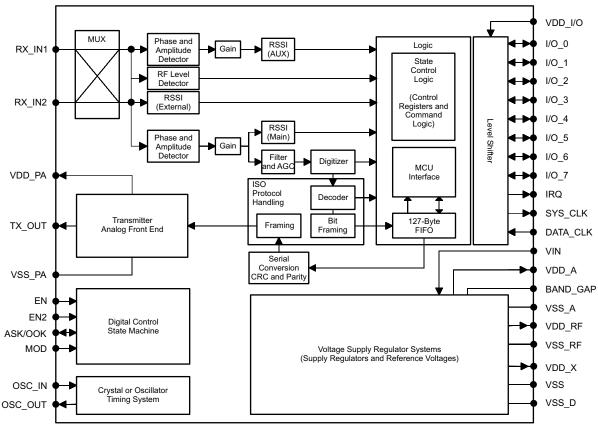

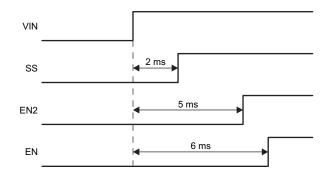

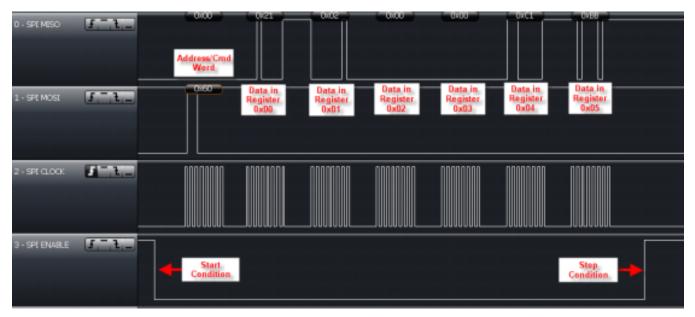

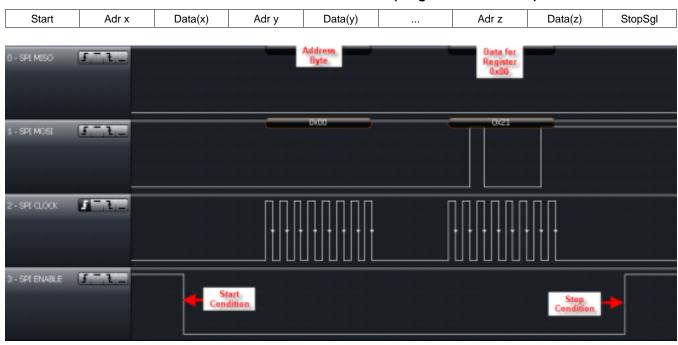

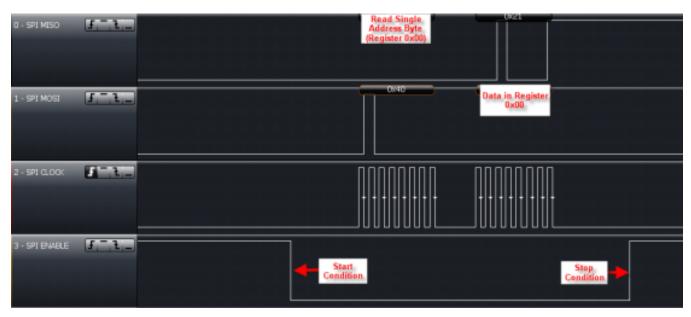

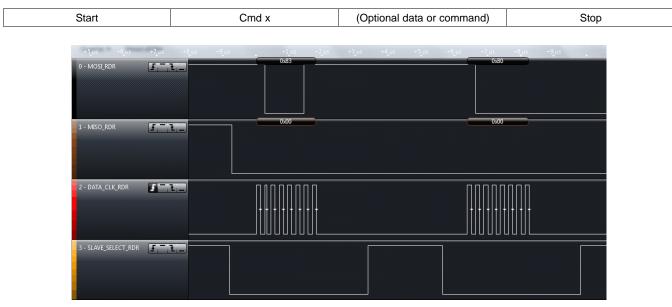

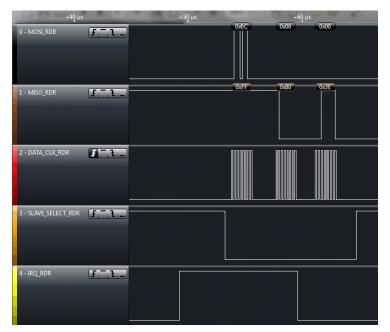

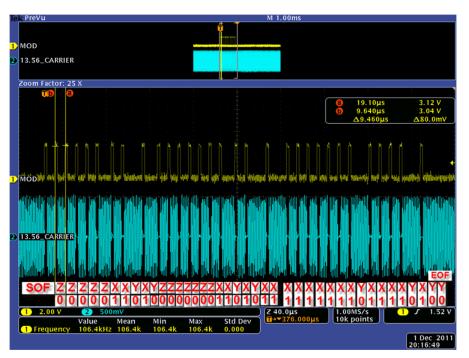

The chip has several power states, which are controlled by two input pins (EN and EN2) and several bits in the chip status control register (0x00) (see  $\frac{1}{5}$  6-3 and  $\frac{1}{5}$  6-4).