## **RLSO8A2.84LV Series**

### ULTRA LOW CAPACITANCE TVS/ESD ARRAY

### **Description**

The RLSO8A2.84LV series of transient voltage suppressors are designed to protect low voltage, stateof-the-art CMOS semiconductors from transients caused by electrostatic discharge (ESD), cable discharge events (CDE), lightning and other induced voltage surges.

The devices are constructed using Semtech's proprietary EPD process technology. The EPD process provides low standoff voltages with significant reductions in leakage currents and capacitance over siliconavalanche diode processes. The RLSO8A2.84LV features integrated low capacitance compensation diodes that reduce the typical capacitance to 5pF per line. This, combined with low leakage current, means signal integrity is preserved in high-speed applications such as 10/100 Ethernet.

The RLSO8A2.84LV is in an SO-8 package and may be used to protect two high-speed line pairs. The "flow-thru" design minimizes trace inductance and reduces voltage overshoot associated with ESD events. The lowclamping voltage of the RLSO8A2.84LV minimizes the stress on the protected IC.

The RLSO8A2.84LV series TVS diodes will meet the surge requirements of IEC 61000-4-2, Level 4.

#### **Features**

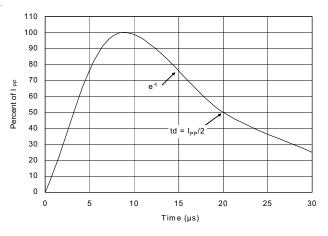

- 400 Watts peak pulse power (tp = 8/20µs)

- Transient protection for high speed data lines to IEC 61000-4-2 (ESD) ±15kV (air), ±8kV (contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 24A (8/20µs)

- Protects two line pairs (four lines)

- · Comprehensive pin out for easy board layout

- Low capacitance

- · Low leakage current

- · Low operating and clamping voltages

- Solid-state EPD TVS process technology

### **Mechanical Characteristics**

- JEDEC SO-8 package

- Molding compound flammability rating: UL 94V-0

- Marking : Part number, date code, logo

- Packaging : Tape and Reel

### **Applications**

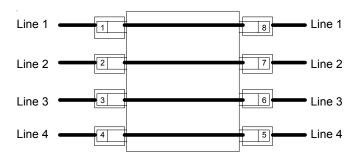

- 10/100 Ethernet

- WAN/LAN Equipment

- Switching Systems

- Desktops, Servers, and Notebooks

- Instrumentation

- Base Stations

- Analog Inputs

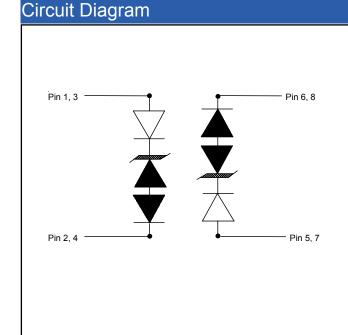

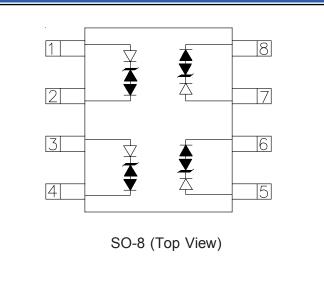

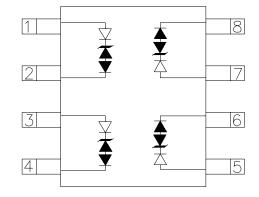

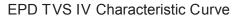

### Schematic & PIN Configuration

# Absolute Maximum Rating

| Rating                                                         | Symbol           | Value         | Units |

|----------------------------------------------------------------|------------------|---------------|-------|

| Peak Pulse Power (tp =8/20µs)                                  | P <sub>PK</sub>  | 400           | Watts |

| Peak Pulse Current (tp =8/20µs)                                | I <sub>PP</sub>  | 24            | А     |

| ESD per IEC 61000-4-2 (Air)<br>ESD per IEC 61000-4-2 (Contact) | V <sub>ESD</sub> | 25<br>15      | kV    |

| Lead Soldering Temperature                                     | Τ <sub>κ</sub>   | 260 (10 sec.) | °C    |

| Operating Temperature                                          | Т <sub>Ј</sub>   | -55 to +125   | °C    |

| Storage Temperature                                            | T <sub>STG</sub> | -55 to +150   | °C    |

# **Electrical Characteristics**

| RLSO8A2.84LV |

|--------------|

|--------------|

| Parameter                 | Symbol          | Conditions                                                  | Minimum | Typical | Maximum | Units |

|---------------------------|-----------------|-------------------------------------------------------------|---------|---------|---------|-------|

| Reverse Stand-Off Voltage | $V_{RWM}$       | -                                                           | -       | -       | 2.8     | V     |

| Punch-Through Voltage     | V <sub>PT</sub> | Ι <sub>ΡΤ</sub> =2μΑ                                        | 3.0     | -       | -       | V     |

| Snap-Back Voltage         | $V_{SB}$        | I <sub>SB</sub> =50mA                                       | 2.8     | -       | -       | V     |

| Reverse Leakage Current   | I <sub>R</sub>  | V <sub>RWM</sub> =2.8V ,T=25°C<br>(Each Line)               | -       | -       | 1       | μA    |

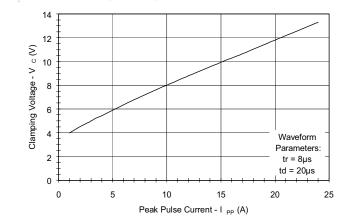

| Clamping Voltage          | V <sub>C</sub>  | I <sub>PP</sub> =1A,t <sub>p</sub> = 8/20μs<br>(Each Line)  | -       | -       | 5.5     | V     |

| Clamping Voltage          | V <sub>C</sub>  | I <sub>PP</sub> =5A,t <sub>p</sub> = 8/20μs<br>(Each Line)  | -       | -       | 8.5     | V     |

| Clamping Voltage          | V <sub>C</sub>  | I <sub>PP</sub> =24A,t <sub>p</sub> = 8/20µs<br>(Each Line) | -       | -       | 15      | V     |

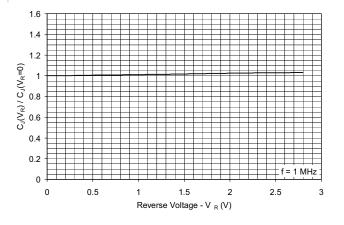

| Junction Capacitance      | C <sub>j</sub>  | V <sub>R</sub> = 0V, f = 1MHz<br>(Each Line)                | -       | 5       | -       | pF    |

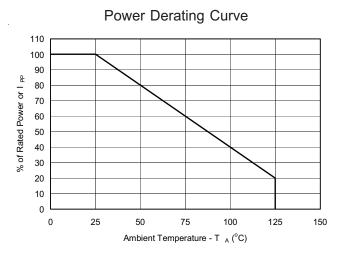

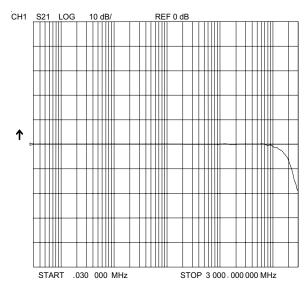

## Typical Characteristics

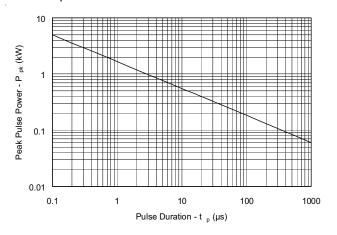

#### Non-Repetitive Peak Pulse Power vs. Pulse Time

Clamping Voltage vs. Peak Pulse Current

Pulse Waveform

Normalized Capacitance vs. Reverse Voltage

#### Applications Information

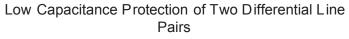

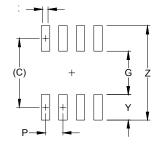

Device Connection for Protection of Four Data Lines Electronic equipment is susceptible to transient disturbances from a variety of sources including: ESD to an open connector or interface, direct or nearby lightning strikes to cables and wires, and charged cables "hot plugged" into I/O ports. The RLSO8A2.84LV is designed to protect sensitive components from damage and latchup which may result from such transient events. The RLSO8A2.84LV can be configured to protect two highspeed line pairs. The device is connected as follows:

Protection of two high-speed line pairs: The RLSO8A2.84LV is designed such that the data lines are routed through the device. The irst line pair enters at pins 1 and 2 and exit at pins 8 and 7 respectively. The second line pair enters at pins 3 and 4 and exits at pins 6 and 5. The traces must be connected at the bottom of the device as shown.

Circuit Board Layout Recommendations for Suppression of ESD.

Good circuit board layout is critical for the suppression of ESD induced transients. The following guidelines are recommended:

- \* Place the RLSO8A2.84LV near the input terminals or connectors to restrict transient coupling.

- Minimize the path length between the TVS and the protected line.

- \* Minimize all conductive loops including power and ground loops.

- \* The ESD transient return path to ground should be kept as short as possible.

- \* Never run critical signals near board edges.

- \* Use ground planes whenever possible.

# Typical Applications

#### Applications Information

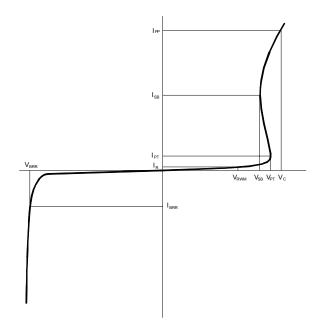

#### **EPD TVS Characteristics**

The RLSO8A2.84LV is constructed using Semtech's proprietary EPD technology. The structure of the EPD TVS is vastly different from the traditional pn-junction devices. At voltages below 5V, high leakage current and junction capacitance render conventional avalanche technology impractical for most applications. However, by utilizing the EPD technology, the RLSO8A2.84LV can effectively operate at 2.8V while maintaining excellent electrical characteristics.

The EPD TVS employs a complex nppn structure in contrast to the pn structure normally found in traditional silicon-avalanche TVS diodes. The EPD mechanism is achieved by engineering the center region of the device such that the reverse biased junction does not avalanche, but will "punchthrough" to a conducting state. This structure results in a device with superior dc electrical parameters at low voltages while maintaining the capability to absorb high transient currents.

The IV characteristic curve of the EPD device is shownin Figure 1. The device represents a high impedance to the circuit up to the working voltage (V<sub>RWM</sub>). During a transient event, the device will begin to conduct as it is biased in the reverse direction. When the punchthrough voltage  $(V_{PT})$  is exceeded, the device enters a low impedance state, diverting the transient current away from the protected circuit. When the device is conducting current, it will exhibit a slight "snapback" or negative resistance characteristic due to its structure. This must be considered when connecting the device to a power supply rail. To return to a non-conducting state, the current through the device must fall below the snap-back current (approximately < 50mA).

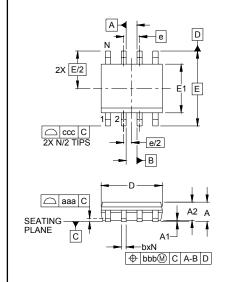

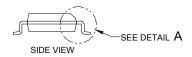

# Outline Drawing - SO-8

|      | DIMENSIONS |      |      |             |        |      |

|------|------------|------|------|-------------|--------|------|

| DIM  | INCHES     |      |      | MILLIMETERS |        |      |

| וויו | MIN        | NOM  | MAX  | MIN         | NOM    | MAX  |

| Α    | .053       | -    | .069 | 1.35        | -      | 1.75 |

| A1   | .004       | -    | .010 | 0.10        | -      | 0.25 |

| A2   | .049       | -    | .065 | 1.25        | -      | 1.65 |

| b    | .012       | -    | .020 | 0.31        | -      | 0.51 |

| С    | .007       | -    | .010 | 0.17        | -      | 0.25 |

| D    | .189       | .193 | .197 | 4.80        | 4.90   | 5.00 |

| E1   | .150       | .154 | .157 | 3.80        | 3.90   | 4.00 |

| E    | .236 BSC   |      |      | 6.00 BSC    |        |      |

| е    | .050 BSC   |      |      | 1.27 BSC    |        |      |

| h    | .010       | -    | .020 | 0.25        | -      | 0.50 |

| L    | .016       | .028 | .041 | 0.40        | 0.72   | 1.04 |

| L1   | (.041)     |      |      |             | (1.04) |      |

| Ν    | 8          |      |      | 8           |        |      |

| θ1   | 0°         | -    | 8°   | 0°          | -      | 8°   |

| aaa  | .004       |      |      | 0.10        |        |      |

| bbb  | .010       |      |      | 0.25        |        |      |

| CCC  | .008       |      |      |             | 0.20   |      |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-

- 3. DIMENSIONS "E1" AND "D" DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 4. REFERENCE JEDEC STD MS-012, VARIATION AA.

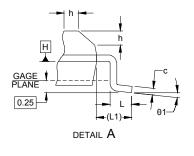

|     | DIMENSIONS |             |  |  |  |

|-----|------------|-------------|--|--|--|

| DIM | INCHES     | MILLIMETERS |  |  |  |

| С   | (.205)     | (5.20)      |  |  |  |

| G   | .118       | 3.00        |  |  |  |

| Р   | .050       | 1.27        |  |  |  |

| X   | .024       | 0.60        |  |  |  |

| Y   | .087       | 2.20        |  |  |  |

| Z   | .291       | 7.40        |  |  |  |

#### NOTES:

- 1. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 2. REFERENCE IPC-SM-782A, RLP NO. 300A.

RUILONG.YUAN CO.,LTD Tel: +86- 0755-82908296 Fax: +86- 0755-82908002 Email: jack@ruilon.com Website: http://www.ruilon.com

RuiLongYuan Electronics are trademarks.

Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. RUILONYUAN Electronics reserves the right to change or update, without notice, any information contained in this publication; to change, without notice, the design, construction, processing, or specification of any product; and to discontinue or limit production or distribution of any product. This publication supersedes and replaces all information previously supplied. Without expressed or written consent by an officer of RUILONYUAN Electronics, RUILONYUAN Electronics does not authorize the use of any of its products as components in nuclear facility applications, aerospace, or in critical life support devices or systems. RUILONYUAN Electronics expressly disclaims all implied warranties regarding the information contained herein, including, but not limited to, any implied warranties of merchantability or fitness for a particular purpose. RUILONYUAN Electronics' only obligations are those in the RUILONYUAN Electronics Standard Terms and Conditions of Sale and in no case will RUILONYUAN Electronics be liable for any incidental, indirect, or consequential damages.