### UCC28600

SLUS646K-NOVEMBER 2005-REVISED AUGUST 2015

## UCC28600 8-Pin Quasi-Resonant Flyback Green-Mode Controller

Technical

Documents

Sample &

Buv

#### Features 1

- Green-Mode Controller With Advanced Energy Saving Features

- Quasi-Resonant Mode Operation for Reduced EMI and Low Switching Losses (Low-Voltage Vallev Switching)

- Low Standby Current for Minimum System No-Load Power Consumption

- Low Start-up Current: 25-µA Maximum

- Programmable Line and Load Over-Voltage Protection

- Internal Over-Temperature Protection

- **Current Limit Protection**

- Cycle-by-Cycle Power Limit

- Primary-Side Over-Current Hiccup Restart Mode

- 1-A Sink. –0.75-A Source TrueDrive<sup>™</sup> Gate Drive Output

- Programmable Soft-Start

- Green-Mode Status Pin (PFC Disable Function)

## 2 Applications

- Bias Supplies for LCD-Monitors, LCD-TV, PDP-TV, and Set Top Boxes

- AC-to-DC Adapters and Off-Line Battery Chargers

- Energy Efficient Power Supplies up to 200 W

## 3 Description

Tools &

Software

The UCC28600 is a PWM controller with advanced energy features to meet stringent world-wide energy efficiency requirements.

Support &

UCC28600 integrates built-in advanced energy saving features with high-level protection features to provide cost-effective solutions for energy-efficient power supplies. UCC28600 incorporates frequency fold-back and green-mode operation to reduce the switching losses at light-load and no-load conditions.

UCC28600 is available in the 8-pin SOIC package. Operating junction temperature range is -40°C to +105°C.

The UCC28600 Design Calculator, (SLVC104), located in the Tools and Software section of the UCC28600 product folder, provides a user-interactive process selecting iterative for recommended component values for an optimal design.

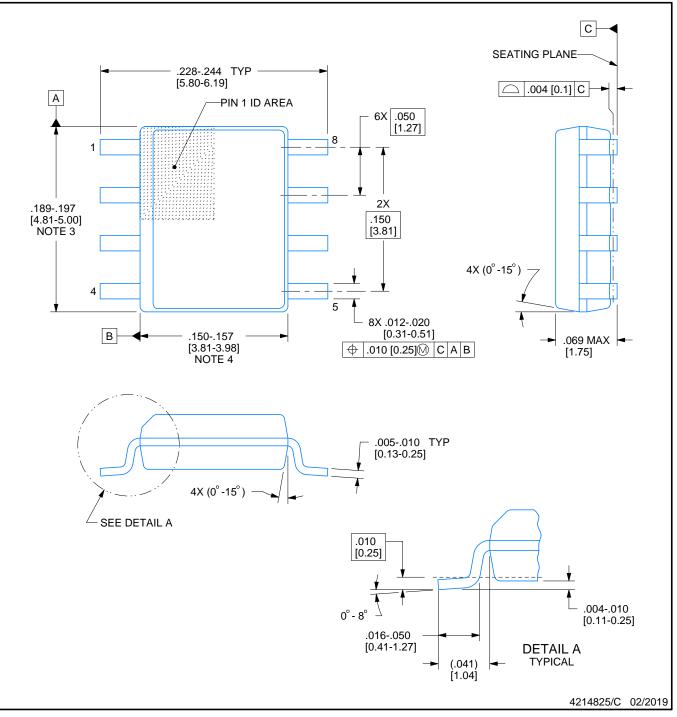

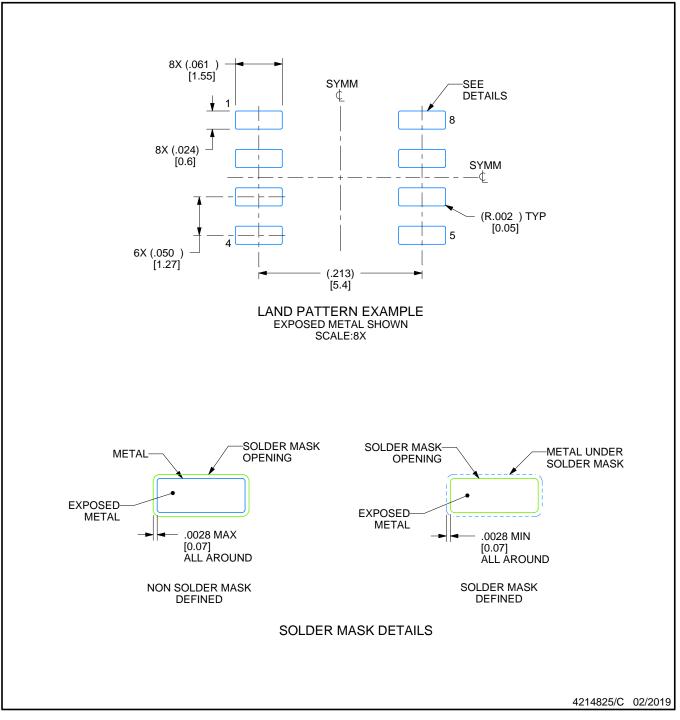

#### Device Information <sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------------|----------|-------------------|

| UCC28600    | SOIC (8) | 4.90 mm × 3.91 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

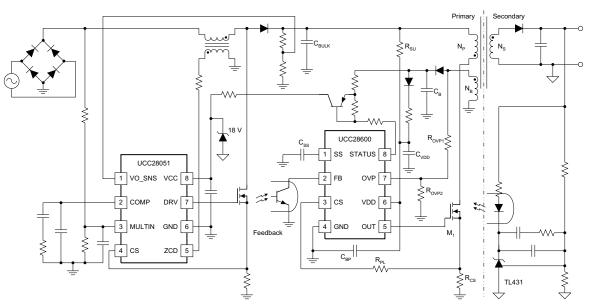

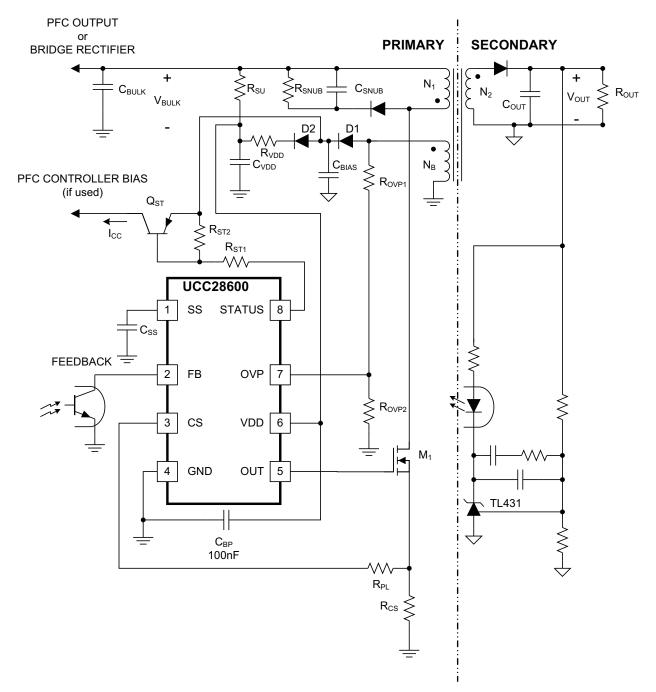

## Typical Application Diagram

Features ..... 1

Applications ..... 1

Description ..... 1

Revision History..... 2

Pin Configuration and Functions ...... 3

Specifications...... 4

6.1 Absolute Maximum Ratings ...... 4

6.6 Timing Requirements ...... 6

6.7 Typical Characteristics ...... 7

Detailed Description ...... 8

7.3 Feature Description..... 11

ESD Ratings ..... 4

Recommended Operating Conditions ...... 4

Thermal Information ...... 4

## **Table of Contents**

| 7.4  | Device Functional Modes                                                                                      | 18                                         |

|------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| App  | lication and Implementation                                                                                  | 21                                         |

| 8.1  | Application Information                                                                                      | 21                                         |

| 8.2  | Typical Application                                                                                          | 21                                         |

| 8.3  | Do's and Don'ts                                                                                              | 33                                         |

| Pow  | er Supply Recommendations                                                                                    | 34                                         |

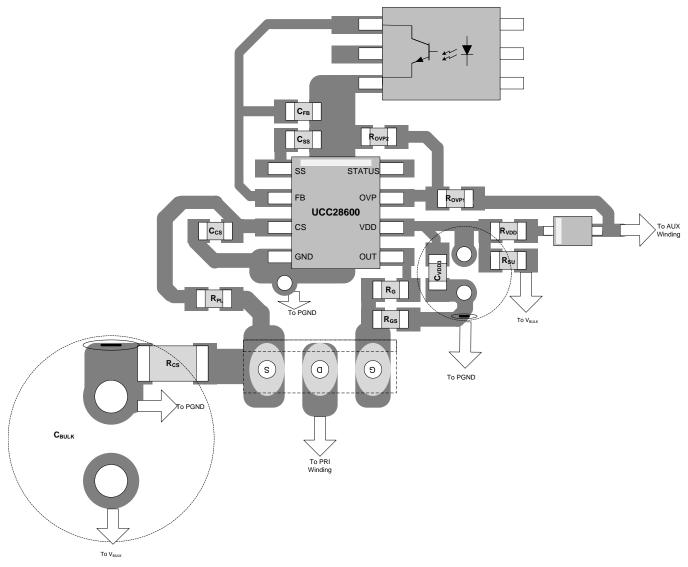

| Lay  | out                                                                                                          | 34                                         |

| 10.1 | Layout Guidelines                                                                                            | 34                                         |

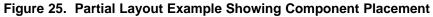

| 10.2 | Layout Example                                                                                               | 35                                         |

| Dev  | ice and Documentation Support                                                                                | 36                                         |

| 11.1 | Device Support                                                                                               | 36                                         |

| 11.2 | Documentation Support                                                                                        | 36                                         |

| 11.3 | Trademarks                                                                                                   | 36                                         |

| 11.4 | Electrostatic Discharge Caution                                                                              | 36                                         |

| 11.5 | Glossary                                                                                                     | 36                                         |

| Мес  | hanical, Packaging, and Orderable                                                                            |                                            |

|      |                                                                                                              | 37                                         |

|      | App<br>8.1<br>8.2<br>8.3<br>Pow<br>Lay<br>10.1<br>10.2<br>Dev<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>Mec | <ul> <li>8.2 Typical Application</li></ul> |

## 4 Revision History

1

2

3

4

5

6

7

6.2

6.3

6.4

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision J (July 2011) to Revision K

| • | Added Pin Configuration and Functions section, ESD table, Feature Description section, Device Functional Modes,<br>Application and Implementation section, Power Supply Recommendations section, Layout section, Device and<br>Documentation Support section, and Mechanical, Packaging, and Orderable Information section. | 1  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Changed Functional Block diagram                                                                                                                                                                                                                                                                                            | 8  |

| • | Changed Control Flow Chart diagram                                                                                                                                                                                                                                                                                          | 11 |

| • | Changed QR Detect Details image.                                                                                                                                                                                                                                                                                            | 13 |

| • | Changed Oscillator Details image.                                                                                                                                                                                                                                                                                           | 14 |

| • | Changed Fault Logic Details image                                                                                                                                                                                                                                                                                           | 16 |

| • | Changed Mode Control with FB Pin Voltage image.                                                                                                                                                                                                                                                                             | 18 |

|   | Changed Operation Mode Switching Frequencies image.                                                                                                                                                                                                                                                                         |    |

#### Changes from Revision H (November 2005) to Revision I

| • | Changed Equation 35 | 29 |

|---|---------------------|----|

Product Folder Links: UCC28600

www.ti.com

Page

Page

## 5 Pin Configuration and Functions

|     | 8-F | Packa<br>Pin SC<br>op Vie | DĪC     |

|-----|-----|---------------------------|---------|

| SS  | 1   | 8                         | ]STATUS |

| FB  | 2   | 7                         | ]OVP    |

| CS  | 3   | 6                         | ]VDD    |

| GND | 4   | 5                         | ]OUT    |

#### **Pin Functions**

| Р      | IN  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CS     | 3   | I   | Current sense input. Also programs power limit, and used to control modulation and activate overcurrent protection. The CS voltage input originates across a current sense resistor and ground. Power limit is programmed with an effective series resistance between this pin and the current sense resistor.                                                                                                                                                                                                                                          |

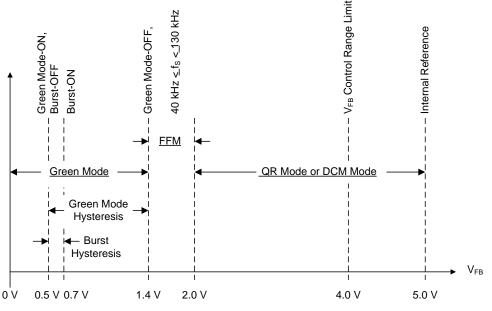

| FB     | 2   | I   | Feedback input or control input from the optocoupler to the PWM comparator used to control the peak current in the power MOSFET. An internal 20-k $\Omega$ resistor is between this pin and the internal 5-V regulated voltage. Connect the collector of the photo-transistor of the feedback optocoupler directly to this pin; connect the emitter of the photo-transistor to GND. The voltage of this pin controls the mode of operation in one of the three modes: quasi resonant (QR), frequency foldback mode (FFM) and green mode (GM).           |

| GND    | 4   | -   | Ground for internal circuitry. Connect a ceramic $0.1-\mu F$ bypass capacitor between VDD and GND, with the capacitor as close to these two pins as possible.                                                                                                                                                                                                                                                                                                                                                                                           |

| OUT    | 5   | 0   | 1-A sink (TrueDrive <sup>™</sup> ) and 0.75-A source gate drive output. This output drives the power MOSFET and switches between GND and the lower of VDD or the 13-V internal output clamp.                                                                                                                                                                                                                                                                                                                                                            |

| OVP    | 7   | I   | Over voltage protection (OVP) input senses line-OVP, load-OVP and the resonant trough for QR turn-on. Detect line, load and resonant conditions using the primary bias winding of the transformer, adjust sensitivity with resistors connected to this pin.                                                                                                                                                                                                                                                                                             |

| SS     | 1   | I   | Soft-start programming pin. Program the soft-start rate with a capacitor to ground; the rate is determined by the capacitance and the internal soft-start charge current. The soft-start capacitor should be placed as close as possible to the SS pin and GND, keeping trace length to a minimum. All faults discharge the SS pin to GND through an internal MOSFET with an $R_{DS(on)}$ of approximately 100 $\Omega$ . The internal modulator comparator reacts to the lowest of the SS voltage, the internal FB voltage and the peak current limit. |

| STATUS | 8   | 0   | ACTIVE HIGH open drain signal that indicates the device has entered standby mode. This pin can be used to disable the PFC control circuit (high impedance = green mode). STATUS pin is high during UVLO, (VDD < start-up threshold), and softstart, (SS < FB).                                                                                                                                                                                                                                                                                          |

| VDD    | 6   | I   | Provides power to the device. Use a ceramic 0.1-µF by-pass capacitor for high-frequency filtering of the VDD pin, as described in the GND pin description. Operating energy is usually delivered from auxiliary winding. To prevent hiccup operation during start-up, a larger energy storage cap is also needed between VDD and GND.                                                                                                                                                                                                                   |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                          |                                                              | MIN  | MAX  | UNIT |

|--------------------------|--------------------------------------------------------------|------|------|------|

| VDD                      | Supply voltage range, I <sub>DD</sub> < 20 mA                |      | 32   | V    |

| I <sub>DD</sub>          | Supply current                                               |      | 20   | mA   |

| I <sub>OUT(sink)</sub>   | Output sink current (peak)                                   |      | 1.2  | А    |

| I <sub>OUT(source)</sub> | Output source current (peak)                                 |      | -0.8 | А    |

|                          | Analog inputs: FB, CS, SS                                    | -0.3 | 6.0  | V    |

| V <sub>OVP</sub>         |                                                              | -1.0 | 6.0  | V    |

| I <sub>OVP(source)</sub> |                                                              |      | -1.0 | mA   |

| V <sub>STATUS</sub>      | VDD = 0 V  to  30 V                                          |      | 30   | V    |

|                          | Power dissipation, SOIC-8 package, $T_A = 25^{\circ}C$       |      | 650  | mW   |

| T <sub>LEAD</sub>        | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |      | 300  | °C   |

| TJ                       | Operating junction temperature                               | -55  | 150  | °C   |

| T <sub>stg</sub>         | Storage temperature                                          | -65  | 150  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                        | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------------------------------------------------|-------|------|

| M                  | Electrostatia discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins $^{(1)}$                  | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins $^{\rm (2)}$ | ±1500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                | MIN | NOM | MAX | UNIT |

|------------------|--------------------------------|-----|-----|-----|------|

| VDD              | Input voltage                  |     |     | 21  | V    |

| C <sub>VDD</sub> | VDD bypass capacitor           | 0.1 | 1.0 |     | μF   |

| C <sub>FB</sub>  | FB filter capacitor            |     |     | 390 | pF   |

| TJ               | Operating junction temperature | -40 |     | 105 | °C   |

### 6.4 Thermal Information

|                       |                                              | UCC28600 |      |

|-----------------------|----------------------------------------------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | UNIT |

|                       |                                              | 8 PINS   |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 108.9    | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 55.5     | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 48.9     | °C/W |

| TLΨ                   | Junction-to-top characterization parameter   | 10.5     | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 48.5     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

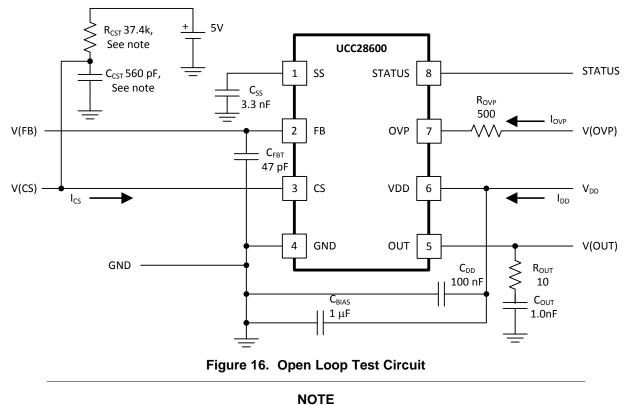

VDD = 15 V, 0.1- $\mu$ F capacitor from VDD to GND, 3.3-nF capacitor from SS to GND charged over 3.5 V, 500- $\Omega$  resistor from OVP to -0.1 V, FB = 4.8 V, STATUS = not connected, 1-nF capacitor from OUT to GND, CS = GND, T<sub>A</sub> = -40°C to +105°C, (unless otherwise noted)

|                             | PARAMETER                    | TEST CONDITIONS                                      | MIN  | TYP  | MAX  | UNIT |

|-----------------------------|------------------------------|------------------------------------------------------|------|------|------|------|

| ISTARTUP                    | Start-up current             | $VDD = V_{UVLO} - 0.3 V$                             |      | 12   | 25   | μA   |

| ISTANDBY                    | Standby current              | V <sub>FB</sub> = 0 V                                |      | 350  | 550  | μA   |

|                             |                              | Not switching                                        |      | 2.5  | 3.5  | mA   |

| I <sub>DD</sub>             | Operating current            | 130 kHz, QR mode                                     |      | 5.0  | 7.0  | mA   |

|                             | VDD clamp                    | $FB = GND, I_{DD} = 10 mA$                           | 21   | 26   | 32   | V    |

| UNDERVOLT                   | AGE LOCKOUT                  |                                                      |      |      |      |      |

| VDD <sub>(uvlo)</sub>       | Start-up threshold           | VDD increasing                                       | 10.3 | 13.0 | 15.3 | V    |

| VDD <sub>(uvlo)</sub>       | Stop threshold               | VDD decreasing                                       | 6.3  | 8    | 9.3  | V    |

| ΔVDD <sub>(uvlo)</sub>      | Hysteresis                   |                                                      | 4.0  | 5.0  | 6.0  | V    |

| PWM (RAMP                   | ) <sup>(1)</sup>             | · · · ·                                              |      |      |      |      |

| D <sub>MIN</sub>            | Minimum duty cycle           | $V_{SS} = GND, V_{FB} = 2 V$                         |      |      | 0%   |      |

| D <sub>MAX</sub>            | Maximum duty cycle           | QR mode, f <sub>S</sub> = max, (open loop)           |      | 99%  |      |      |

| OSCILLATO                   | R (OSC)                      | · · · · ·                                            |      |      |      |      |

| f <sub>QR(max)</sub>        | Maximum QR and DCM frequency |                                                      | 117  | 130  | 143  | kHz  |

| f <sub>QR(min)</sub>        | Minimum QR and FFM frequency | V <sub>FB</sub> = 1.3 V                              | 32   | 40   | 48   | kHz  |

| f <sub>SS</sub>             | Soft start frequency         | V <sub>SS</sub> = 2.0 V                              | 32   | 40   | 48   | kHz  |

| dT <sub>S</sub> /dFB        | VCO gain                     | $T_{S}$ for 1.6 V < V <sub>FB</sub> < 1.8 V          | -38  | -30  | -22  | µs/V |

| FEEDBACK                    | (FB)                         | · · · · ·                                            |      |      |      |      |

| R <sub>FB</sub>             | Feedback pullup resistor     |                                                      | 12   | 20   | 28   | kΩ   |

| V <sub>FB</sub>             | FB, no load                  | QR mode                                              | 3.30 | 4.87 | 6.00 | V    |

|                             | Green-mode ON threshold      | V <sub>FB</sub> threshold                            | 0.3  | 0.5  | 0.7  | V    |

|                             | Green-mode OFF threshold     | V <sub>FB</sub> threshold                            | 1.2  | 1.4  | 1.6  | V    |

|                             | Green-mode hysteresis        | V <sub>FB</sub> threshold                            | 0.7  | 0.9  | 1.1  | V    |

|                             | FB threshold burst-ON        | V <sub>FB</sub> during green mode                    | 0.3  | 0.5  | 0.7  | V    |

|                             | FB threshold burst-OFF       | V <sub>FB</sub> during green mode                    | 0.5  | 0.7  | 0.9  | V    |

|                             | Burst Hysteresis             | V <sub>FB</sub> during green mode                    | 0.13 | 0.25 | 0.42 | V    |

| STATUS                      |                              | ·                                                    |      |      | L    |      |

| R <sub>DS(on)</sub>         | STATUS on resistance         | V <sub>STATUS</sub> = 1 V                            | 1.0  | 2.4  | 3.8  | kΩ   |

| I <sub>STATUS(leakage</sub> | ) STATUS leakage/off current | V <sub>FB</sub> = 0.44 V, V <sub>STATUS</sub> = 15 V | -0.1 |      | 2.0  | μA   |

(1) R<sub>CST</sub> and C<sub>CST</sub> are not connected in the circuit for maximum and minimum duty cycle tests, current sense tests, and power limit tests.

## **Electrical Characteristics (continued)**

VDD = 15 V, 0.1- $\mu$ F capacitor from VDD to GND, 3.3-nF capacitor from SS to GND charged over 3.5 V, 500- $\Omega$  resistor from OVP to -0.1 V, FB = 4.8 V, STATUS = not connected, 1-nF capacitor from OUT to GND, CS = GND, T<sub>A</sub> = -40°C to +105°C, (unless otherwise noted)

|                        | PARAMETER                                         | TEST CONDITIONS                                                  | MIN  | TYP  | MAX      | UNIT |

|------------------------|---------------------------------------------------|------------------------------------------------------------------|------|------|----------|------|

| CURRENT S              | ENSE (CS) <sup>(1)</sup>                          |                                                                  | .1   |      | P        |      |

| A <sub>CS(FB)</sub>    | Gain = $\Delta V_{FB} / \Delta V_{CS}$            | QR mode                                                          |      | 2.5  |          | V/V  |

|                        | Shutdown threshold                                | V <sub>FB</sub> = 2.4 V, V <sub>SS</sub> = 0 V                   | 1.13 | 1.25 | 1.38     | V    |

|                        | CS discharge impedance                            | CS = 0.1 V, V <sub>SS</sub> = 0 V                                | 25   | 115  | 250      | Ω    |

| V <sub>CS(os)</sub>    | CS offset                                         | SS mode, $V_{SS} \le 2.0 V$                                      | 0.35 | 0.40 | 0.45     | V    |

| POWER LIM              | IT (PL) <sup>(1)</sup>                            |                                                                  |      |      | L.       |      |

| I <sub>PL(cs)</sub>    | CS current                                        | OVP = -300 μA                                                    | -165 | -150 | -135     | μA   |

|                        | Peak CS voltage                                   | QR mode                                                          | 0.70 | 0.81 | 0.92     | V    |

| V <sub>PL</sub>        | PL threshold                                      | Peak CS voltage + CS offset                                      | 1.05 | 1.20 | 1.37     | V    |

| SOFT STAR              | T (SS)                                            |                                                                  | 1    |      | <b>t</b> |      |

| I <sub>SS(chg)</sub>   | Softstart charge current                          | V <sub>SS</sub> = GND                                            | -8.3 | -6.0 | -4.5     | μA   |

| I <sub>SS(dis)</sub>   | Softstart discharge current                       | V <sub>SS</sub> = 0.5 V                                          | 2.0  | 5.0  | 10       | mA   |

| V <sub>SS</sub>        | Switching ON threshold                            | Output switching start                                           | 0.8  | 1.0  | 1.2      | V    |

| OVERVOLT               | AGE PROTECTION (OVP)                              |                                                                  |      |      | ·        |      |

| I <sub>OVP(line)</sub> | Line overvoltage protection                       | I <sub>OVP</sub> threshold, OUT = HI                             | -512 | -450 | -370     | μA   |

| V <sub>OVP(on)</sub>   | OVP voltage at OUT = HIGH                         | $V_{FB}$ = 4.8 V, $V_{SS}$ = 5.0 V,<br>$I_{OVP(on)}$ , = -300 µA | -125 |      | -25      | mV   |

| V <sub>OVP(load)</sub> | Load overvoltage protection                       | $V_{OVP}$ threshold, OUT = LO                                    | 3.37 | 3.75 | 4.13     | V    |

|                        | ROTECTION (TSP)                                   |                                                                  |      |      | L.       |      |

|                        | Thermal shutdown (TSP) temperature <sup>(2)</sup> |                                                                  | 130  | 140  | 150      | °C   |

|                        | Thermal shutdown hysteresis                       |                                                                  |      | 15   |          | °C   |

(2) Ensured by design. Not production tested.

### 6.6 Timing Requirements

|                   |                                                                     | MIN | NOM | MAX | UNIT |

|-------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| CURREN            | T SENSE (CS) <sup>(1)</sup>                                         |     |     |     |      |

|                   | CS to output delay time (power limit), CS = 1.0 $V_{PULSE}$         | 100 | 175 | 300 | ns   |

|                   | CS to output delay time (over current fault), CS = 1.45 $V_{PULSE}$ | 50  | 100 | 150 | ns   |

| OUT               |                                                                     |     |     |     |      |

| t <sub>RISE</sub> | Rise time, 10% to 90% of 13-V typical OUT clamp                     |     | 50  | 75  | ns   |

| t <sub>FALL</sub> | Fall time                                                           |     | 10  | 20  | ns   |

(1) R<sub>CST</sub> and C<sub>CST</sub> are not connected in the circuit for maximum and minimum duty cycle tests, current sense tests, and power limit tests.

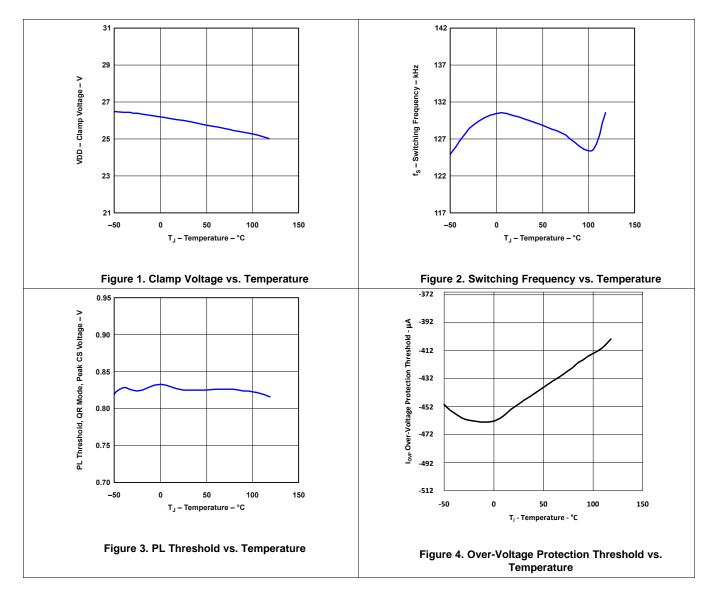

## 6.7 Typical Characteristics

## 7 Detailed Description

## 7.1 Overview

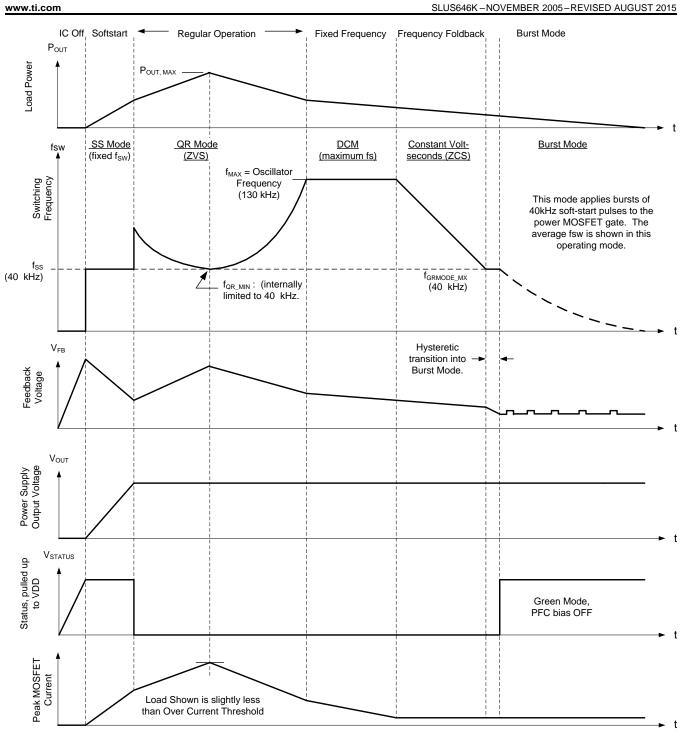

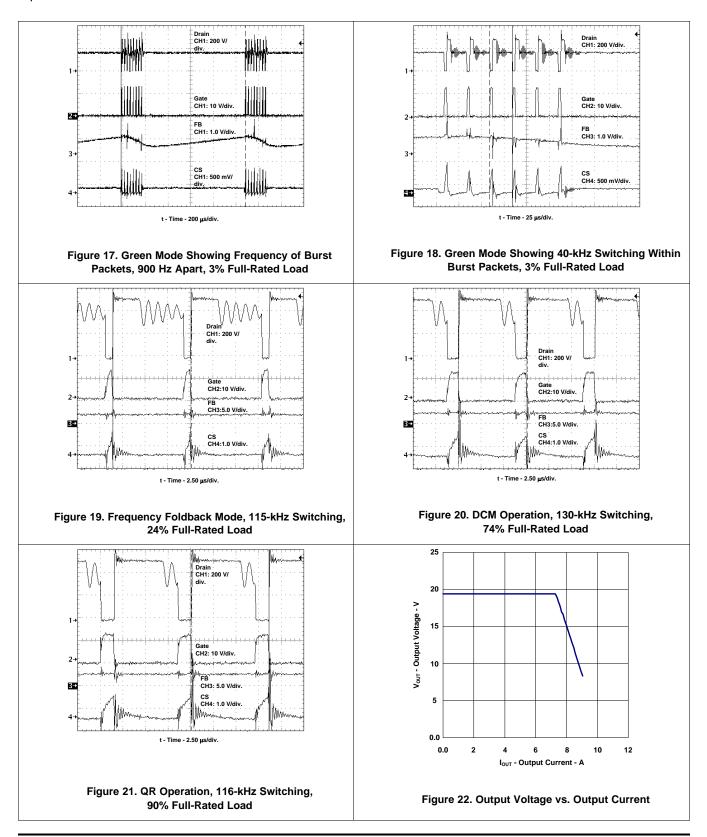

The UCC28600 is a flyback power supply controller that operates in different operating modes, modulating the peak primary current and/or the switching frequency, depending upon the line and load conditions. The controller will operate in burst mode operation, or green mode (GM) driving the primary side MOSFET with packets of 40-kHz pulses, at fixed peak primary current for light-load conditions. As the load increases, the 40-kHz switching will become consistent and the controller will transition to frequency fold-back mode (FFM), where the peak primary current is held constant and the switching frequency is modulated from 40 kHz up to 130 kHz, in order to maintain regulation. At higher loads, the UCC28600 will operate in either DCM, where the peak primary current is modulated but the switching frequency is maintained at its maximum value, or quasi-resonant mode (QRM), where the switching frequency and the peak primary current are both modulated in order to maintain regulation.

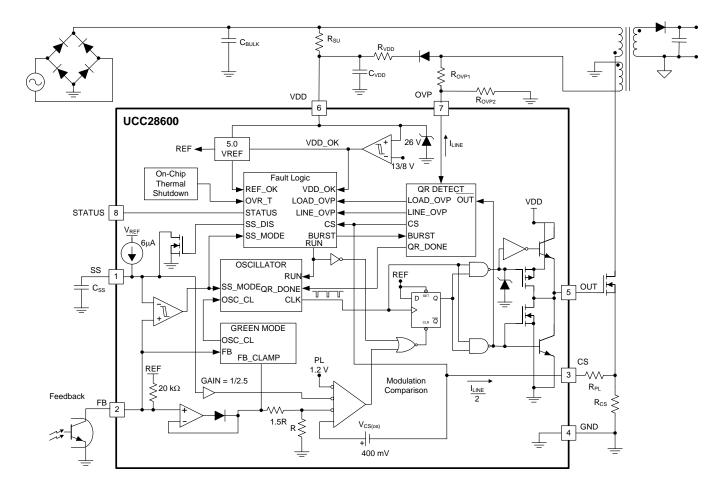

## 7.2 Functional Block Diagram

## **Functional Block Diagram (continued)**

### 7.2.1 Terminal Components

| PIN      |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|----------|---|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| NAME NO. |   |   | DESCRIPTION <sup>(1)</sup> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

| CS       | 3 | I | $\begin{split} &R_{CS} = \frac{\left(V_{PL} - V_{CS(os)}\left(I_{CS(2)} - I_{CS(1)}\right)\right)}{I_{CS(2)} - I_{P(1)} - I_{CS(1)} - I_{P(2)}} \\ &R_{PL} = \frac{\left(V_{PL} - V_{CS(os)}\left(I_{P(2)} - I_{P(1)}\right)\right)}{I_{CS(1)} - I_{P(2)} - I_{CS(2)} - I_{P(1)}\right)} \\ & \text{where:} \\ \bullet  I_{P(1)} \text{ is the peak primary current at low line, full load}^{(2)} \\ \bullet  I_{P(2)} \text{ is the peak primary current at high line, full load}^{(2)} \\ \bullet  I_{CS(1)} \text{ is the power limit current that is sourced at the CS pin at low-line voltage}^{(2)} \\ \bullet  I_{CS(2)} \text{ is the power limit current that is sourced at the CS pin at high-line voltage}^{(2)} \\ \bullet  V_{PL} \text{ is the Power Limit (PL) threshold}^{(1)} \\ \bullet  V_{CS(os)} \text{ is the CS offset voltage}^{(1)} \end{split}$                                                                                               | (1)<br>(2)        |

| FB       | 2 | I | Opto-isolator collector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

| GND      | 4 | _ | Bypass capacitor to VDD, $C_{BP} = 0.1 \ \mu F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| OUT      | 5 | 0 | Power MOSFET gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| OVP      | 7 | I | $\begin{split} & R_{OVP1} = \frac{1}{I_{OVP(line)}} \begin{pmatrix} N_{B} \; V_{BULK(ov)} \end{pmatrix} \\ & R_{OVP2} = R_{OVP1} \begin{pmatrix} \frac{V_{OVP(line)}}{N_{P}} \langle V_{OUT(shutdown)} + V_{F} \rangle - V_{OVP(load)} \end{pmatrix} \\ & \text{where:} \\ & I_{OVP(line)} \; is \; OVP_{line} \; \text{current threshold} \; ^{(1)} \\ & V_{BULK(ov)} \; is \; \text{the allowed input over- voltage level} \; ^{(2)} \\ & V_{OVP(load)} \; is \; OVP_{load} \; ^{(1)} \\ & V_{OUT(shutdown)} \; \text{is the allowed output over-voltage level} \; ^{(2)} \\ & V_{F} \; is \; \text{the forward voltage of the secondary rectifier} \\ & N_{B} \; \text{is the number of turns on the bias winding} \; ^{(2)} \\ & N_{F} \; \text{is the number of turns on the primary windings} \; ^{(2)} \\ & N_{P} \; \text{is the number of turns on the primary windings} \; ^{(2)} \end{split}$                                                                | (3)<br>(4)        |

| SS       | 1 | I | $\begin{split} &C_{SS} > I_{SS} \times \frac{t_{SS(min)}\left(duepowerlimit\right)}{A_{CS(FB)} \times \left(V_{PL} - V_{CS(os)}\right)} \\ &\text{where } t_{SS(min)} \text{ is the greater of:} \\ &t_{SS(min)} = \left[\frac{-R_{LOAD(ss)}C_{OUT}}{2} \ln \frac{V_{OUT} - \Delta V_{OUT(step)}}{R_{LOAD(ss)}P_{OUT(max)limit}}\right] \\ &\text{or} \\ &t_{SS(min)} = \left[\frac{C_{OUT}V_{OUT}^2}{2P_{LM}}\right] \\ &\text{e}  R_{LOAD(ss)} \text{ is the effective load impedance during soft-start} \ ^{(2)} \\ &\Delta V_{OUT(step)} \text{ is the allowed change in } V_{OUT} \text{ due to a load step} \ ^{(2)} \\ &\text{e}  P_{OUT(max)limit)} \text{ Programmed power limit level, in W} \ ^{(2)} \\ &A_{CS(FB)} \text{ is the current sense gain} \ ^{(1)} \\ &V_{CS(os)} \text{ is the CS offset voltage} \ ^{(1)} \\ &I_{SS} \text{ is the soft-start charging current} \ ^{(1)} \\ &V_{PL} \text{ is the power limit threshold} \ ^{(1)} \end{split}$ | (5)<br>(6)<br>(7) |

#### **Table 1. Terminal Components**

Refer to the *Electrical Characteristics* for constant parameters.

Refer to the UCC28600 Design Calculator (SLVC104) or laboratory measurements for currents, voltages and times in the operational circuit.

NSTRUMENTS

Texas

## Functional Block Diagram (continued)

| PIN    |     | 1/0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |

|--------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| NAME   | NO. | I/O | DESCRIPTION <sup>(1)</sup> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |

| STATUS | 8   | 0   | $\begin{split} & R_{ST2} = \frac{V_{\text{BE(off)}}}{I_{STATUS(leakage)}} \\ & R_{ST1} = \frac{R_{ST2} \times \left[ VDD_{(uvlo-on)} - V_{\text{BE(sat)}} - R_{DS(on)} \times \left( \frac{I_{CC}}{\beta_{sat}} \right) \right] - R_{DS(on)} V_{\text{BE(sat)}}}{\left( \left( \frac{I_{CC}}{\beta_{sat}} \right) \times R_{ST2} \right) + V_{\text{BE(sat)}}} \\ & \text{where:} \\ &  \beta_{SAT} \text{ is the gain of transistor } Q_{ST} \text{ in saturation} \\ &  V_{\text{BE(sat)}} \text{ is the base-emitter voltage of transistor } Q_{ST} \text{ in saturation} \\ &  VDD_{(uvlo-on)} \text{ is the start-up threshold } ^{(1)} \\ &  I_{CC} \text{ is the collector current of } Q_{ST} \\ &  I_{\text{STATUS}(leakage)} \text{ is the maximum leakage/off current of the STATUS pin } ^{(1)} \\ &  V_{\text{BE(off)}} \text{ is the maximum allowable voltage across the base emitter junction that will not turn } Q_{ST} \text{ on} \\ &  R_{DS(on)} \text{ is the } R_{DS(on)} \text{ of STATUS } ^{(1)} \\ \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (8)<br>(9)                   |

| VDD    | 6   | 1   | $\begin{split} & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ \\ & \begin{array}{l} & \end{array} \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ \\ & \begin{array}{l} & \end{array} \\ & \end{array} \\ \\ & \begin{array}{l} & \end{array} \\ \\ & \end{array} \\ \\ & \begin{array}{l} & \end{array} \\ \\ & \end{array} \\ \\ & \end{array} \\ \\ \\ & \begin{array}{l} & \end{array} \\ \\ & \end{array} \\ \\ & \begin{array}{l} & \end{array} \\ \\ & \end{array} \\ \\ & \end{array} \\ \\ \\ \\ & \begin{array}{l} & \end{array} \\ \\ & \end{array} \\ \\ \\ \\ & \end{array} \\ \\ \\ \\ & \end{array} \\ \\ \\ \\$ | (10)<br>(11)<br>(12)<br>(13) |

### 7.3 Feature Description

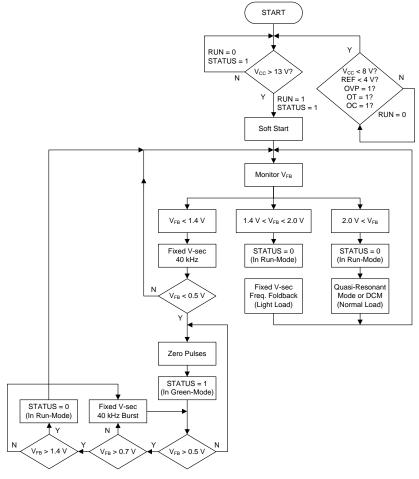

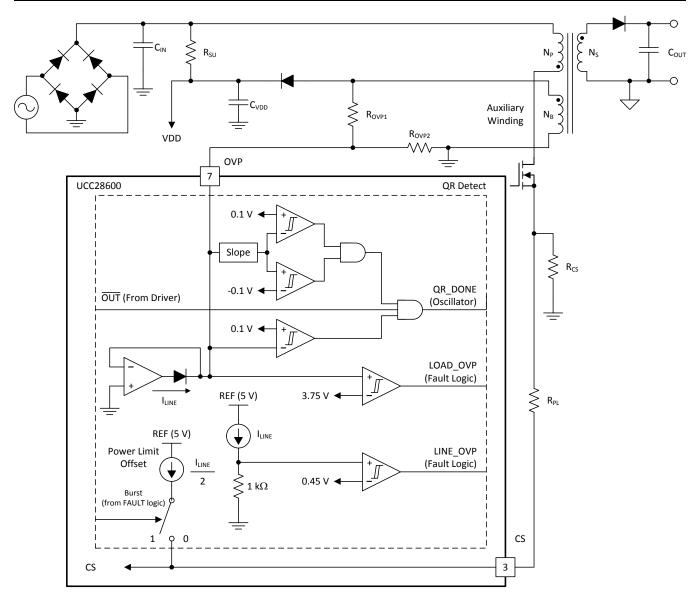

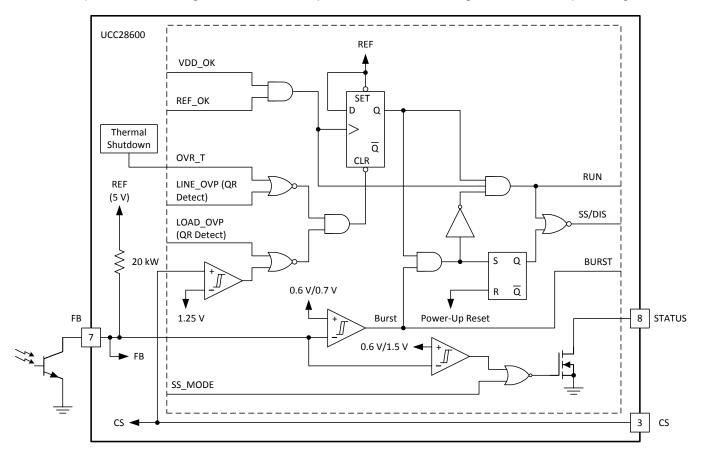

The UCC28600 is a multi-mode controller, as illustrated in Figure 5 and Figure 12. The mode of operation depends upon line and load conditions. Under all modes of operation, the UCC28600 terminates the OUT = HI signal based on the switch current. Thus, the UCC28600 always operates in current mode control so that the power MOSFET current is always limited.

Under normal operating conditions, the FB pin commands the operating mode of the UCC28600 at the voltage thresholds shown in the control flow chart, Figure 11. Soft-start and fault responses are the exception. During soft start, the converter switching frequency is fixed at 40 kHz and FB is set to 5V. The soft-start mode is latched-OFF when  $V_{SS}$  becomes greater than  $V_{FB}$  for the first time after UVLO<sub>ON</sub>. The soft-start state cannot be recovered until after passing UVLO<sub>OFF</sub>, and then, UVLO<sub>ON</sub>.

From 100% to approximately 30% full rated power the UCC28600 controls the converter in quasi-resonant mode (QRM) or discontinuous conduction mode (DCM), where DCM operation is at the clamped maximum switching frequency (130 kHz). For loads that are between approximately 30% and 10% full rated power, the converter operates in frequency foldback mode (FFM), where the peak switch current is constant and the output voltage is regulated by modulating the switching frequency for a given and fixed  $V_{IN}$ . Effectively, operation in FFM results in the application of constant volt-seconds to the flyback transformer each switching cycle. Voltage regulation in FFM is achieved by varying the switching frequency in the range from 130 kHz to 40 kHz. For extremely light loads (below approximately 10% full rated power), the converter is controlled using bursts of 40-kHz pulses.

Figure 5. Control Flow Chart

UCC28600

SLUS646K - NOVEMBER 2005 - REVISED AUGUST 2015

### Feature Description (continued)

Details of the functional boxes in the Block Diagram/Typical Application drawing are shown in Figure 8, Figure 6, Figure 7 and Figure 10. These figures conceptualize how the UCC28600 executes the command of the FB voltage to have the responses that are shown in Figure 11, Figure 5 and Figure 12. The details of the functional boxes also conceptualize the various fault detections and responses that are included in the UCC28600. During all modes of operation, this controller operates in current mode control. This allows the UCC28600 to monitor the FB voltage to determine and respond to the varying load levels such as heavy, light or ultra-light.

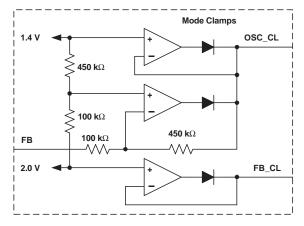

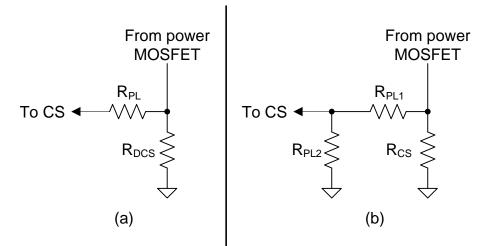

Quasi-resonant mode and DCM occurs for feedback voltages  $V_{FB}$  between 2.0 V and 4.0 V, respectively. In turn, the CS voltage is commanded to be between 0.4 V and 0.8 V. A cycle-by-cycle power limit imposes a fixed 0.8-V limit on the CS voltage. An overcurrent shutdown threshold in the fault logic gives added protection against high-current, slew-rate shorted winding faults, shown in Figure 10. The power limit feature in the QR DETECT circuit of Figure 7 adds an offset to the CS signal that is proportional to the line voltage. The power limit feature is programmed with  $R_{PL}$ , as shown in the *Typical Application Diagram*.

Figure 6. Mode Clamp Details

Figure 7. QR Detect Details

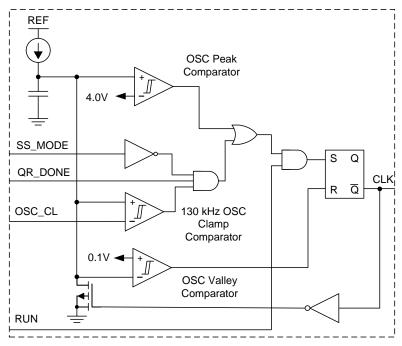

#### 7.3.1 Oscillator

The oscillator, shown in Figure 8, is internally set and trimmed so it is clamped by the circuit in Figure 8 to a nominal 130-kHz maximum operating frequency. It also has a minimum frequency clamp of 40 kHz. If the FB voltage tries to drive operation to less than 40 kHz, the converter operates in green mode.

Figure 8. Oscillator Details

#### 7.3.2 Status

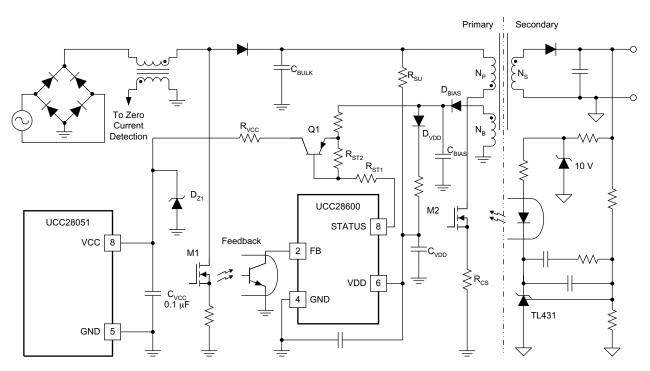

The STATUS pin is an open drain output, as shown in Figure 10. The status output goes into the OFF-state when FB falls below 0.5 V and it returns to the ON-state (low impedance to GND) when FB rises above 1.4 V. This pin is used to control bias power for a PFC stage, as shown in Figure 9. Key elements for implementing this function include Q1,  $R_{ST1}$  and  $R_{ST2}$ , as shown in Figure 9. Resistors  $R_{ST1}$  and  $R_{ST2}$  are selected to saturate Q1 when it is desirable for the PFC to be operational. During green mode, the STATUS pin becomes a high impedance and  $R_{ST2}$  causes Q1 to turn-OFF, thus saving bias power. If necessary, use a Zener diode and a resistor ( $D_{Z1}$  and  $R_{VCC}$ ) to maintain VCC in the safe operating range of the PFC controller.

# $\label{eq:NOTE} \begin{array}{c} \text{NOTE} \\ \text{The } D_{\text{VDD}} - C_{\text{VDD}} \text{ combination is in addition to the standard } D_{\text{BIAS}} - C_{\text{BIAS}} \text{ components.} \end{array}$

This added stage is required to isolate the STATUS circuitry from the start-up resistor,  $R_{SU}$ , to ensure there is no conduction through STATUS when VDD is below the UVLO turn-on threshold.

Figure 9. Using STATUS for PFC Shut-Down During Green Mode

#### 7.3.3 Fault Logic

Advanced logic control coordinates the fault detections to provide proper power supply recovery. This provides the conditioning for the thermal protection. Line overvoltage protection (line OVP) and load OVP are implemented in this block. It prevents operation when the internal reference is below 4.5 V. If a fault is detected in the thermal shutdown, line OVP, load OVP, or REF, the UCC28600 undergoes a shutdown/retry cycle.

Refer to the fault logic diagram in Figure 10 and the QR detect diagram in Figure 7 to program line OVP and load OVP. To program the load OVP, select the  $R_{OVP1} - R_{OVP2}$  divider ratio to be 3.75 V at the desired output shutdown voltage. To program line OVP, select the impedance of the  $R_{OVP1} - R_{OVP2}$  combination to draw 450  $\mu$ A when the V<sub>OVP</sub> is 0.45 V during the ON-time of the power MOSFET at the highest allowable input voltage.

Figure 10. Fault Logic Details

#### 7.3.4 Protection Features

The UCC28600 has many protection features that are found only on larger, full featured controllers. Refer to the *Functional Block Diagram*, *Typical Application Diagram*, Figure 6, Figure 7, Figure 8, Figure 10, Figure 11, and Figure 12 for detailed block descriptions that show how the features are integrated into the normal control functions.

#### 7.3.5 Overtemperature

Overtemperature lockout typically occurs when the substrate temperature reaches 140°C. Retry is allowed if the substrate temperature reduces by the hysteresis value. Upon an overtemperature fault, C<sub>SS</sub> on softstart is discharged and STATUS is forced to a high impedance.

#### 7.3.6 Cycle-by-Cycle Power Limit

The cycle terminates when the CS voltage plus the power limit offset exceeds 1.2 V.

In order to have power limited over the full line voltage range of the QR Flyback converter, the CS pin voltage must have a component that is proportional to the primary current plus a component that is proportional to the line voltage due to predictable switching frequency variations due to line voltage. At power limit, the CS pin voltage plus the internal CS offset is compared against a constant 1.2-V reference in the PWM comparator. Thus during cycle-by-cycle power limit, the peak CS voltage is typically 0.8 V.

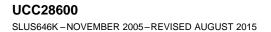

The current that is sourced from the OVP pin ( $I_{LINE}$ ) is reflected to a dependent current source of ½  $I_{LINE}$ , that is connected to the CS pin. The power limit function can be programmed by a resistor,  $R_{PL}$ , that is between the CS pin and the current sense resistor. The current,  $I_{LINE}$ , is proportional to line voltage by the transformer turns ratio  $N_B/N_P$  and resistor  $R_{OVP1}$ . Current  $I_{LINE}$  is programmed to set the line over voltage protection. Resistor  $R_{PL}$  results in the addition of a voltage to the current sense signal that is proportional to the line voltage. The proper amount of additional voltage has the effect of limiting the power on a cycle-by-cycle basis. Note that  $R_{CS}$ ,  $R_{PL}$ ,  $R_{OVP1}$  and  $R_{OVP2}$  must be adjusted as a set due to the functional interactions.

#### 7.3.7 Primary Current Protection

When the primary current exceeds maximum current level which is indicated by a voltage of 1.25 V at the CS pin, the device initiates a shutdown. Retry occurs after a  $UVLO_{OFF}$  or  $UVLO_{ON}$  cycle. Because the device will initiate cycle-by-cycle power limit first, primary side current protection is not intended to protect against output short circuit conditions. However, this feature does protect the MOSFET against extreme conditions such as transformer saturation.

#### 7.3.8 Over-Voltage Protection

Line and load over voltage protection is programmed with the transformer turn ratios, R<sub>OVP1</sub> and R<sub>OVP2</sub>. The OVP pin has a 0-V voltage source that can only source current; OVP cannot sink current.

Line over voltage protection occurs when the OVP pin is clamped at 0 V. When the bias winding is negative, during OUT = HI or portions of the resonant ring, the 0-V voltage source clamps OVP to 0 V and the current that is sourced from the OVP pin is mirrored to the Line\_OVP comparator and the QR detection circuit. The Line\_OVP comparator initiates a shutdown-retry sequence if OVP sources any more than 450  $\mu$ A.

Load-over voltage protection occurs when the OVP pin voltage is positive. When the bias winding is positive, during demagnetization or portions of the resonant ring, the OVP pin voltage is positive. If the OVP voltage is greater than 3.75 V, the device initiates a shutdown. Retry occurs after a UVLO<sub>OFF</sub> or UVLO<sub>ON</sub> cycle.

#### 7.3.9 Undervoltage Lockout

Protection is provided to guard against operation during unfavorable bias conditions. Undervoltage lockout (UVLO) always monitors VDD to prevent operation below the UVLO threshold.

### 7.4 Device Functional Modes

Depending upon the line and load conditions, the UCC28600 controls the converter using different modes of operation, which are defined as quasi-resonant (QR mode), discontinuous conduction mode (DCM), frequency foldback mode (FFM) and green mode (GM), determined by the voltage on the FB pin, as shown in Figure 11.

For extremely light loads (below approximately 10% full rated power), the converter is controlled using bursts of 40-kHz pulses. As the load increases, the number of pulses in these burst packets increases until the converter is switching consistently at 40 kHz, at which point it transitions into the next operating mode, called frequency foldback. Frequency foldback mode (FFM) typically begins at loads that are between approximately 10% and up to 30% full rated power, the peak primary side switch current is constant and the output voltage is regulated by modulating the switching frequency from 40 kHz up to 130 kHz. From approximately 30% to 100% full rated power, the UCC28600 controls the converter in either quasi-resonant mode (QRM) or discontinuous conduction mode (DCM). In QRM, the switching frequency (130 kHz). The valley detection circuitry is active during FFM, DCM, and QRM operation.

Keep in mind that the aforementioned boundaries of steady-state operation are approximate because they are subject to converter design parameters.

Figure 11. Mode Control with FB Pin Voltage

UCC28600

#### 7.4.1 Quasi-Resonant and DCM Control

During this control mode, the rising edge of OUT will occur just after the valley of the resonant ring when the transformer is fully demagnetized. Resonant valley switching is an integral part of QR operation. In this mode, the flyback converter operates at the boundary of discontinuous conduction mode and continuous conduction mode. By adjusting both the peak current and the switching frequency, the output power is adjusted to match the load requirement. When the load increases, the peak current increases and the switching frequency decreases. The minimum switching frequency of the converter is limited to 40 kHz. The transformer magnetizing inductor value has to be designed accordingly so that the converter can deliver the maximum required power while maintaining a switching frequency that is greater than the  $f_{QR(min)}$  over the entire input operating range.

As the load decreases from its designed maximum output power, the UCC28600 will demand a higher switching frequency and decreased peak current. The converter's maximum switching frequency will be limited to 130 kHz. At this maximum switching frequency, the converter enters DCM control. At DCM control, the peak current is adjusted to control the output power. Slight frequency dithering between resonant valleys will occur as the valley detection is active in DCM control.

Quasi-resonant (QR) and DCM operation occur for feedback voltages,  $V_{FB}$ , between 2.0 V and 3.0 V. In turn, the peak CS voltage is commanded to be between 0.4 V and 0.8 V. The CS pin has an internal dependent current source, 1/2 I<sub>LINE</sub>. This current source adds a proportional step offset (power limit offset) to the CS signal and is part of the cycle-by-cycle power limit function that is discussed in the *Protection Features* section.

#### 7.4.2 Frequency Foldback Mode Control

Operation in FFM results in the application of constant volt-seconds to the flyback transformer during each switching cycle. During frequency foldback mode, as the load decreases, the MOSFET peak current is kept constant and the switching frequency is reduced (foldback) to reduce the output power. In this mode, the flyback converter will always operate in discontinuous conduction mode. When the FB voltage is between 1.4 V and 2.0 V, the voltage controlled oscillator restricts the operating frequency between 40 kHz and 130 kHz and the CS is clamped to 0.4 V, including the power limit offset. Valley detection is active during FFM.

### 7.4.3 Green-Mode Control

During green mode, the converter operates at a fixed switching frequency of 40 kHz and fixed peak current. The output power is adjusted by the converter ON/OFF durations, which is also known as burst mode. When the FB voltage is between 1.4 V and 0.5 V, the controller is commanding an excess of energy to be transferred to the load which in turn, drives the error higher and FB lower. When FB reaches 0.5 V, the OUT pulses are terminated and do not resume until FB reaches 0.7 V. In this mode, the converter operates in hysteretic control with the OUT pulse terminated at a fixed CS voltage level of 0.4 V. The power limit offset is turned OFF during Green mode and it returns to ON when FB is above 1.4 V. Green mode reduces the average switching frequency in order to minimize switching losses and increase the efficiency at light-load conditions.

#### 7.4.4 Operating Mode Programming

Boundaries of the operating modes are programmed by the flyback transformer and the four components R<sub>PL</sub>, R<sub>CS</sub>, R<sub>OVP1</sub> and R<sub>OVP2</sub>; shown in the *Functional Block Diagram* and *Typical Application Diagram* drawing.

The transformer characteristics that predominantly affect the modes are the magnetizing inductance of the primary and the magnitude of the output voltage, reflected to the primary. To a lesser degree (yet significant), the boundaries are affected by the MOSFET output capacitance and transformer leakage inductance. The design procedure here is to select a magnetizing inductance and a reflected output voltage that operates at the DCM/CCM boundary at maximum load and maximum line. The actual inductance should be noticeably smaller to account for the ring between the magnetizing inductance and the total stray capacitance measured at the drain of the power MOSFET. This programs the QR/DCM boundary of operation. All other mode boundaries are preset with the thresholds in the oscillator and green-mode blocks.

The four components  $R_{PL}$ ,  $R_{CS}$ ,  $R_{OVP1}$  and  $R_{OVP2}$  must be programmed as a set due to the interactions of the functions. The use of the UCC28600 design calculator, SLVC104, is highly recommended in order to achieve the desired results with a careful balance between the transformer parameters and the programming resistors.

## 8 Application and Implementation

#### NOTE

Information in the following Applications section is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The UCC28600 device is a flyback controller that operates in a mode that is determined by the FB voltage. Line and load conditions set the FB voltage and the controller will operate in Green Mode (GM) under light-load conditions, Frequency Foldback Mode (FFM) when operating at loads approximately between 10% and 30% full rated load, and Quasi-Resonant (QR) or Discontinuous Mode (DCM) at higher loads. Valley switching under all modes, except green mode, reduces switching losses and improves efficiency. Valley skipping also helps reduce EMI. A dedicated STATUS pin is used in higher power applications that use a power factor corrected (PFC) front end. Under light-load conditions, the STATUS signal can be used to disconnect the bias power to the PFC controller, reducing light-load power consumption.

#### 8.2 Typical Application

A typical application for the UCC28600 is an off-line flyback controller from 65 W to 120 W, using a PFC output voltage as its input, as shown in Figure 13. The PFC stage is assumed to operate from a universal AC input and can be controlled by a device such as the UCC28051. The auxiliary winding provides the bias to the controllers and provides over voltage protection and valley switching information, as well as bias to the UCC28600 and UCC28051. The UCC28600 will disable the PFC controller during green mode operation, improving light-load system efficiency. The series resistor connected between the current sense pin and the current sense resistor programs the power limit of the converter. Low valley voltage switching and multi-mode operation will keep the efficiency curve high over the entire operation range. Typical applications include bias supplies for LCD monitors, LCD and PDP televisions, set top boxes, AC-DC adaptors, and energy efficient power supplies up to 200 W.

## **Typical Application (continued)**

Figure 13. Simplified Application

## **Typical Application (continued)**

## 8.2.1 Design Requirements

The following table illustrates a typical set of performance requirements for an off-line flyback converter.

|                       | PARAMETER                 | CONDITIONS                                                               | MIN  | NOM     | MAX   | UNIT             |

|-----------------------|---------------------------|--------------------------------------------------------------------------|------|---------|-------|------------------|

| V <sub>IN</sub>       | AC line input voltage     | Input to PFC stage                                                       | 85   | 115/230 | 265   | V <sub>RMS</sub> |

| f <sub>LINE</sub>     | Line frequency            |                                                                          | 47   | 50/60   | 63    | Hz               |

| PFC <sub>OUTPUT</sub> | PFC output voltage        |                                                                          | 350  | 390     | 400   | V                |

| PFC                   | Input power factor        | $V_{IN} = 115 V_{RMS}, I_{OUT} = 6.2 A$                                  |      |         | 0.998 |                  |

|                       |                           | $V_{IN} = 230 V_{RMS}, I_{OUT} = 6.2 A$                                  |      |         | 0.97  |                  |

| V <sub>OUT</sub>      | Output voltage            | 85 $V_{RMS} \le V_{IN} \le 265 V_{RMS}$ ,<br>0 A $\le I_{OUT} \le 6.2 A$ | 19.0 | 19.4    | 19.8  | V                |

| I <sub>OUT</sub>      | Output load current       | 85 $V_{RMS} \le V_{IN} \le 265 V_{RMS}$                                  | 0    |         | 6.2   | А                |

| V <sub>RIPPLE</sub>   | Output voltage ripple     | 85 $V_{RMS} \le V_{IN} \le 265 V_{RMS}$ ,<br>$I_{OUT} = 6.2 A$           |      | 250     |       | mV               |

| V <sub>OVP</sub>      | Output over voltage limit | V <sub>IN</sub> = 115 V <sub>RMS</sub> , I <sub>OUT</sub> = 6.2 A        |      | 23.4    |       | V                |

|                       |                           | $V_{IN} = 230 V_{RMS}, I_{OUT} = 6.2 A$                                  |      | 23.6    |       | V                |

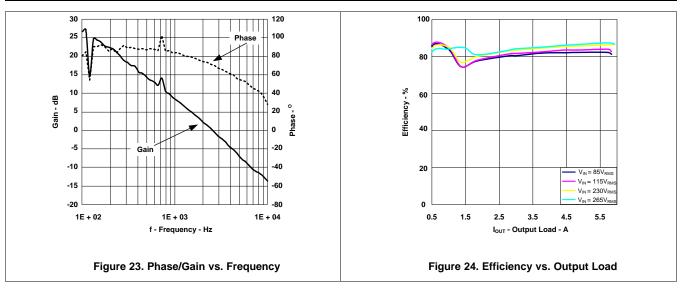

| f <sub>CO</sub>       | Control loop bandwidth    | V <sub>IN</sub> = 115 V <sub>RMS</sub> , I <sub>OUT</sub> = 3 A          |      | 2.6     |       | kHz              |

|                       | Phase margin              | V <sub>IN</sub> = 115 V <sub>RMS</sub> , I <sub>OUT</sub> = 3 A          |      | 70      |       | degrees          |

| $\eta_{PEAK}$         | Peak efficiency           | $V_{IN} = 265 V_{RMS}, I_{OUT} = 6 A$                                    |      | 87.4%   |       |                  |

| η                     | Full load efficiency      | V <sub>IN</sub> = 115 V <sub>RMS</sub> , I <sub>OUT</sub> = 6.2 A        |      | 82.7%   |       |                  |

|                       |                           | $V_{IN} = 230 V_{RMS}, I_{OUT} = 6.2 A$                                  |      | 86.4%   |       |                  |

|                       | No load power consumption | V <sub>IN</sub> = 115 V <sub>RMS</sub> , I <sub>OUT</sub> = 0 A          |      | 230     |       | mW               |

|                       |                           | V <sub>IN</sub> = 230 V <sub>RMS</sub> , I <sub>OUT</sub> = 0 A          |      | 420     |       | mW               |

#### Table 2. Design Example Performance Requirements

#### UCC28600

SLUS646K-NOVEMBER 2005-REVISED AUGUST 2015

8.2.2 Detailed Design Procedure

Submit Documentation Feedback

24