TMP107

SBOS716D -MAY 2015-REVISED JANUARY 2020

# TMP107 Digital Temperature Sensor With Bidirectional UART One-Wire Interface and EEPROM

#### 1 Features

- High Accuracy (Without Calibration):

- ±0.4°C (max) from –20°C to +70°C

- ±0.55°C (max) from –40°C to +100°C

- ±0.7°C (max) from –55°C to +125°C

- High Resolution: 14 Bits (0.015625°C)

- UART-Compatible, SMAART Wire™ Interface:

- Allows Up To 32 Daisy-Chained Devices

- EEPROM Memory for Unique Addressing, Trip Level Programming, and General-Purpose Storage

- Continuous Conversion and Shutdown Mode for Power Savings

- One-Shot Conversion Mode for Custom Update Rates and Power Savings

- · Programmable Alert Feature

- Operating Temperature Range: -55°C to +125°C

- Operating Supply Range: 1.7 V to 5.5 V

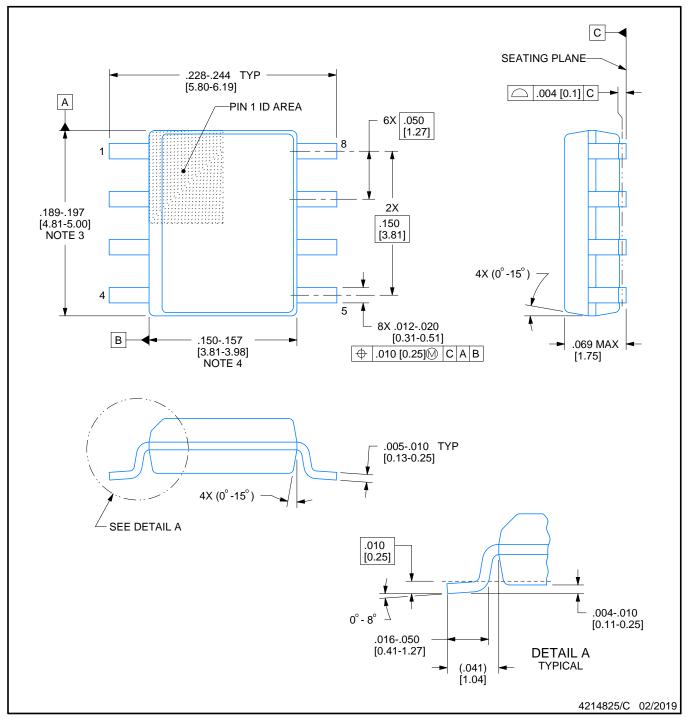

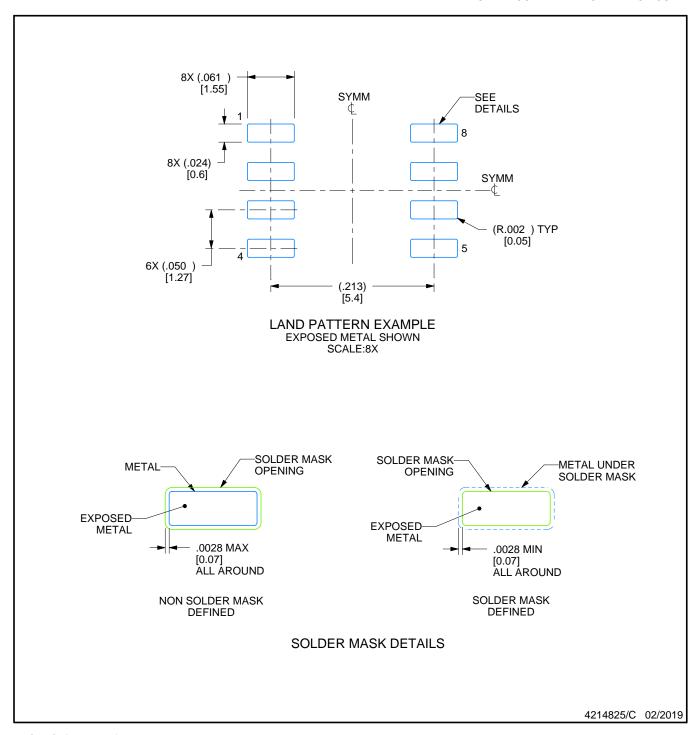

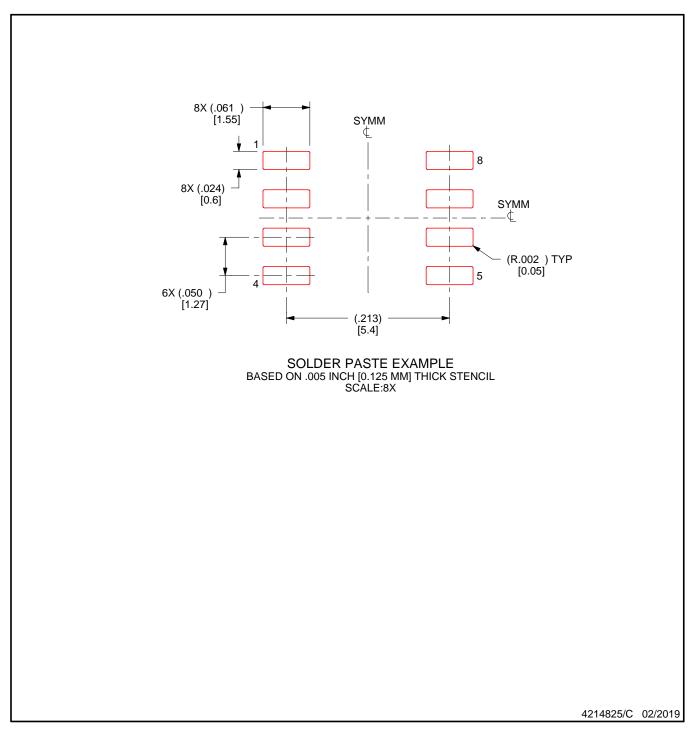

- Package: SOIC-8

# 2 Applications

- · Cold-Chain Logistics

- Distributed Temperature Sensing

- Power-Supply and Battery Thermal Protection

- Servers and Telecommunication Systems

- · Building Automation and HVAC

- Agricultural Equipment

- Medical Devices

- Industrial Process Control

# 3 Description

The TMP107 digital output temperature sensor supports a total of 32 daisy-chained devices. Each sensor has a unique 5-bit address stored in electrically-erasable programmable memory (EEPROM). The TMP107 is capable of reading temperatures with a resolution of 0.015625°C, and is accurate to within ±0.4°C in the range from -20°C to +70°C. The TMP107 is ideal for replacing NTC and PTC thermistors where high accuracy is required.

The unique 5-bit address stored in the EEPROM is determined during the automated address assignment operation, and is based on the position of each sensor relative to the SMAART wire host. Multiple operating modes provide maximum flexibility in selecting between low power consumption for battery operation, and high update rates for real-time control applications.

The TMP107 is ideal for extended temperature measurement in a variety of industrial, instrumentation, communication, and environmental applications. The TMP107 is available in an 8-pin SOIC package and is specified for operation over a temperature range of -55°C to +125°C.

# **Device Information**(1)

| DEVICE NAME | PACKAGE  | BODY SIZE         |

|-------------|----------|-------------------|

| TMP107      | SOIC (8) | 4.90 mm × 3.90 mm |

For all available packages, see the package option addendum at the end of the datasheet.

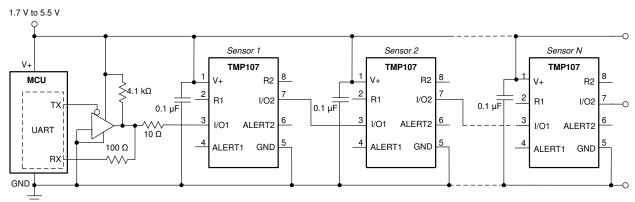

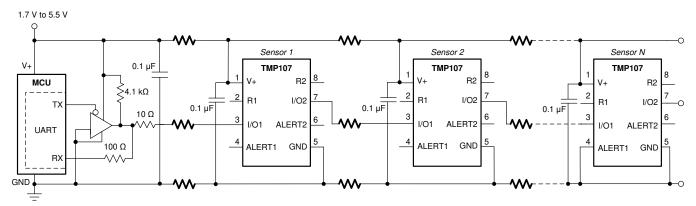

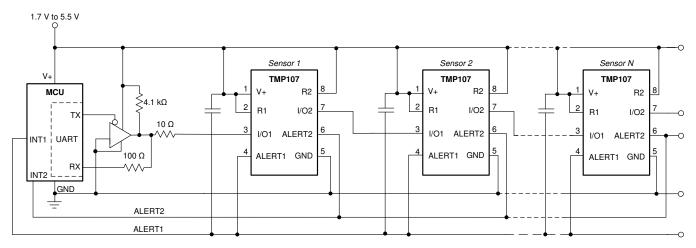

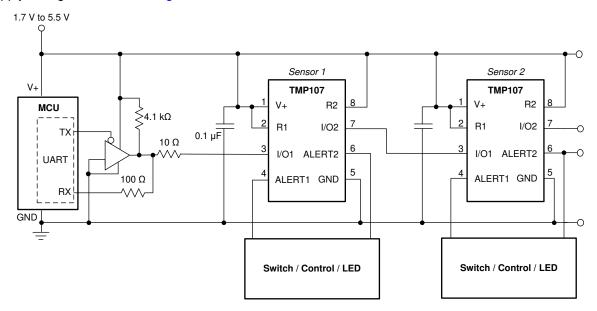

# **Typical Application**

All figures shown as TMP107 represent TMP107-Q1 as well.

Page

| Table ( | of C | onte | nts |

|---------|------|------|-----|

|---------|------|------|-----|

| 1   | Features 1                                                              |         | 7.5 Programming                                    | 21     |

|-----|-------------------------------------------------------------------------|---------|----------------------------------------------------|--------|

| 2   | Applications 1                                                          |         | 7.6 Register Map                                   | 22     |

| 3   | Description 1                                                           | 8       | Application and Implementation                     | 28     |

| 4   | Revision History2                                                       |         | 8.1 Application Information                        |        |

| 5   | Pin Configuration and Functions 3                                       |         | 8.2 Typical Applications                           | 28     |

| 6   | Specifications4                                                         | 9       | Power Supply Recommendations                       | 32     |

| -   | 6.1 Absolute Maximum Ratings 4                                          | 10      | Layout                                             | 32     |

|     | 6.2 ESD Ratings                                                         |         | 10.1 Layout Guidelines                             | 32     |

|     | 6.3 Recommended Operating Conditions 4                                  |         | 10.2 Layout Example                                | 32     |

|     | 6.4 Thermal Information                                                 | 11      | Device and Documentation Support                   | 33     |

|     | 6.5 Electrical Characteristics5                                         |         | 11.1 Documentation Support                         | 33     |

|     | 6.6 Timing Requirements6                                                |         | 11.2 Receiving Notification of Documentation Updat | tes 33 |

|     | 6.7 Typical Characteristics                                             |         | 11.3 Community Resources                           | 33     |

| 7   | Detailed Description 10                                                 |         | 11.4 Trademarks                                    | 33     |

| -   | 7.1 Overview                                                            |         | 11.5 Electrostatic Discharge Caution               | 33     |

|     | 7.2 Functional Block Diagram                                            |         | 11.6 Glossary                                      | 33     |

|     | 7.3 Feature Description                                                 | 12      | Mechanical, Packaging, and Orderable               |        |

|     | 7.4 Device Functional Modes                                             |         | Information                                        | 33     |

|     | Revision History  Iges from Revision C (October 2018) to Revision D     |         |                                                    | Page   |

| Α   | dded footnote for biased operation up to 150°C                          |         |                                                    | 4      |

| har | nges from Revision B (September 2015) to Revision C                     |         |                                                    | Page   |

| С   | hanged text 'The baud rate is 9600 Kbps' to: The baud rate is           | s 9600  | ) bps                                              | 30     |

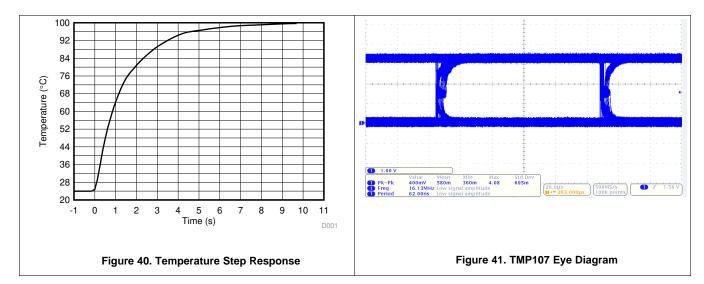

| С   | hanged text 'Excellent eye diagram parameters are maintain              | ed at 9 | 9600 Kbps speed.' to: Excellent eye diagram        |        |

|     | arameters are maintained at 9600 bps speed                              |         |                                                    | 30     |

| Α   | dded Receiving Notification of Documentation Updates section            | on      |                                                    | 33     |

|     | adda                                                                    |         |                                                    | 00     |

| har | ges from Revision A (August 2015) to Revision B                         |         |                                                    | Page   |

| С   | hanged baud values in <i>Individual Read</i> and <i>Global Read</i> sec | ctions  | rom 2.5 to 1.5                                     | 19     |

Submit Documentation Feedback

Changes from Original (May 2015) to Revision A

Copyright © 2015–2020, Texas Instruments Incorporated

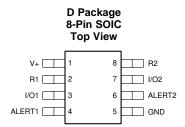

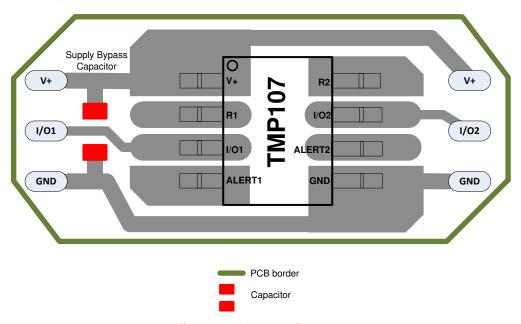

# 5 Pin Configuration and Functions

# **Pin Functions**

|     | PIN I/O |     | DESCRIPTION                                                                                      |

|-----|---------|-----|--------------------------------------------------------------------------------------------------|

| NO. | NAME    | 1/0 | DESCRIPTION                                                                                      |

| 1   | V+      | _   | Supply voltage, 1.7 V to 5.5 V                                                                   |

| 2   | R1      | I   | Built-in pullup resistor for ALERT1; float or connect to V+                                      |

| 3   | I/O1    | I/O | SMAART wire input, output 1                                                                      |

| 4   | ALERT1  | 0   | Over- and undertemperature alert. Open-drain output; internally connected to pullup resistor R1. |

| 5   | GND     | _   | Ground                                                                                           |

| 6   | ALERT2  | 0   | Over- and undertemperature alert. Open-drain output; internally connected to pullup resistor R2. |

| 7   | I/O2    | I/O | SMAART wire input, output 2                                                                      |

| 8   | R2      | I   | Built-in pullup resistor for ALERT2; float or connect to V+                                      |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                    |                           | MIN  | MAX        | UNIT |

|--------------------|---------------------------|------|------------|------|

| Supply voltage, V+ |                           |      | 6          | V    |

|                    | I/O1, I/O2                | -0.3 | (V+) + 0.3 |      |

| Input voltage      | R1, R2                    | -0.3 | 6          | V    |

|                    | ALERT1, ALERT2            | -0.3 | 6          |      |

| Sink current       | ALERT1, ALERT2            |      | 10         | mA   |

| T                  | Operating junction (2)    | -55  | 150        | ۰,0  |

| Temperature        | Storage, T <sub>stg</sub> | -60  | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                                       | VALUE | UNIT     |

|--------------------|-------------------------|-------------------------------------------------------------------------------------------------------|-------|----------|

| .,                 |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                                                | ±2000 | V        |

| V <sub>(ESD)</sub> | Electrostatic discharge | ectrostatic discharge  Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |       | <b>v</b> |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                | MIN | NOM | MAX | UNIT |

|------------------------------------------------|-----|-----|-----|------|

| Supply voltage, V+                             | 1.7 | 3.3 | 5.5 | V    |

| Operating free-air temperature, T <sub>A</sub> | -55 |     | 125 | °C   |

#### 6.4 Thermal Information

|                        |                                              | TMP107   |      |

|------------------------|----------------------------------------------|----------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | UNIT |

|                        |                                              | 8 PINS   |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 116.3    | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 62.5     | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 56.6     | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 14.6     | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 56.0     | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | N/A      | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> The TMP107 is able to sustain bias operations up to 150°C for limited durations, without affecting its accuracy or functionality when conditions return to the recommended operating range. The highest temperature value the TMP107 can report is 127.984°C, beyond which and up to 150°C, the TMP107 continues to read 127.984°C.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics

At  $T_A = -55$ °C to 125°C and V+ = +1.7 V to +5.5 V (unless otherwise noted). Typical values at  $T_A = 25$ °C and V+ = 3.3 V.

|                 | PARAMETER                         | TEST CONDITIONS                                                       | MIN        | TYP        | MAX        | UNIT   |

|-----------------|-----------------------------------|-----------------------------------------------------------------------|------------|------------|------------|--------|

| TEMP            | ERATURE INPUT                     |                                                                       |            |            |            |        |

|                 | Temperature range                 |                                                                       | -55        |            | 125        | °C     |

|                 | Temperature resolution            |                                                                       |            | 0.015625   |            | °C     |

|                 |                                   | -20°C to +70°C; one-shot mode, bus inactive                           |            | ±0.125     | ±0.4       |        |

|                 | Temperature accuracy (error)      | -40°C to +100°C; one-shot mode, bus inactive                          |            | ±0.125     | ±0.55      | °C     |

|                 |                                   | –55°C to +125°C; one-shot mode, bus inactive                          |            | ±0.5       | ±0.7       |        |

|                 | ADC resolution                    |                                                                       |            | 14         |            | Bits   |

| DIGIT           | AL OUTPUT (ALERT1, ALERT2         | 2)                                                                    |            |            |            |        |

| $V_{OL}$        | Low-level output voltage          | $I_{OUT} = -1 \text{ mA}$                                             | 0          | 0.02       | 0.4        | V      |

| I <sub>OH</sub> | High-level output leakage current | V <sub>O</sub> = V+                                                   |            | 0.1        | 1          | μΑ     |

| $R_{PU}$        | Pullup resistors                  |                                                                       | 75         | 100        | 125        | kΩ     |

| DIGIT           | AL INPUT/OUTPUT (I/O1, I/O2)      |                                                                       |            |            |            |        |

| $V_{IH}$        | High-level input voltage          |                                                                       | 0.7 (V+)   |            | (V+) + 0.3 | V      |

| $V_{IL}$        | Low-level input voltage           |                                                                       | -0.3       |            | 0.3 (V+)   | V      |

| $I_{IN}$        | Input current                     | 0 V < V <sub>IN</sub> < (V+) + 0.3 V                                  | -1         |            | 1          | μΑ     |

| $V_{OL}$        | Low-level output voltage          | I <sub>OUT</sub> = -1 mA                                              | 0          | 0.1        | 0.4        | V      |

| $V_{OH}$        | High-level output voltage         | I <sub>OUT</sub> = 1 mA                                               | (V+) - 0.4 | (V+) - 0.1 | V+         | V      |

|                 | Short-circuit current             | Short-circuit I/O1 and I/O2 to ground or V+, V+ = 5 V                 |            | 60         |            | mA     |

| DEVIC           | CE TIMING                         |                                                                       |            |            |            |        |

|                 | Conversion time                   | One-shot mode                                                         | 12         | 15         | 18         | ms     |

|                 | Conversion rate                   | Programmable                                                          | 1/16       |            | 62         | Conv/s |

|                 | Device timeout time               | Any communication                                                     |            | 35         | 40         | ms     |

|                 | Device timeout time               | Global address-initialize command                                     |            | 1          | 1.25       | s      |

| EEPR            | OM                                |                                                                       |            |            |            |        |

|                 | Programming time                  | V+ > 1.8 V                                                            |            | 7          |            | ms     |

|                 | Number of writes                  | V+ > 1.8 V                                                            | 1000       | 100,000    |            | Times  |

|                 | Data retention time               |                                                                       | 10         |            |            | Years  |

| POWE            | ER SUPPLY                         | ,                                                                     |            |            |            |        |

| V+              | Operating supply range            |                                                                       | 1.7        | 3.3        | 5.5        | V      |

| V 1             | Operating supply range            | EEPROM write                                                          | 1.8        | 3.3        | 5.5        | V      |

|                 |                                   | ADC conversion on,<br>SMAART wire bus inactive                        |            | 200        | 400        |        |

|                 |                                   | ADC conversion on, SMAART wire bus active (bus baud rate = 57.6 kBd)  |            | 300        |            |        |

| lQ              | Quiescent current                 | ADC conversion off, SMAART wire bus active (bus baud rate = 57.6 kBd) |            | 100        |            | μΑ     |

|                 |                                   | 1 conversion per second average,<br>SMAART wire bus inactive          |            | 16         | 35         |        |

|                 |                                   | EEPROM write (ADC conversion off)                                     |            | 400        |            |        |

| I <sub>SD</sub> | Shutdown current                  | SMAART wire bus inactive (I/O1, I/O2 = V+)                            |            | 3.8        | 10         | μΑ     |

|                 | Power-on reset voltage            | Supply voltage rising                                                 |            | 1.4        |            | ·V     |

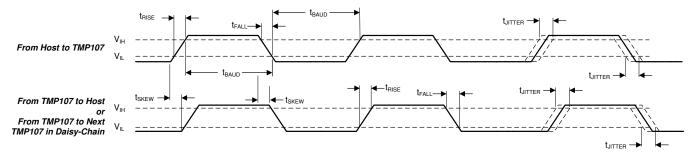

# 6.6 Timing Requirements

|                                         |                                                               | MIN | NOM | MAX   | UNIT          |

|-----------------------------------------|---------------------------------------------------------------|-----|-----|-------|---------------|

| FROM HOST 1                             | O THE TMP107                                                  |     |     |       |               |

| 1/t <sub>BAUD</sub>                     | SMAART bus baud rate                                          | 4.8 |     | 115.4 | kBd           |

| t <sub>RISE</sub> + t <sub>JITTER</sub> | SMAART bus transition from low to high + edge timing variance |     |     | 15    | % of (1/baud) |

| t <sub>FALL</sub> + t <sub>JITTER</sub> | SMAART bus transition from high to low + edge timing variance |     |     | 15    | % of (1/baud) |

| FROM THE TM                             | IP107 TO HOST OR NEXT TMP107 IN DAISY-CHAIN                   |     |     |       |               |

| t <sub>JITTER</sub>                     | Edge timing variance                                          |     |     | 1     | μs            |

| t <sub>SKEW</sub>                       | Average phase shift between IO1 and IO2                       |     | 33  |       | ns            |

| t <sub>RISE</sub>                       | SMAART bus transition from low to high, 10-pF load            |     | 10  |       | ns            |

| t <sub>FALL</sub>                       | SMAART bus transition from high to low, 10-pF load            |     | 10  |       | ns            |

Figure 1. Timing Diagram

Submit Documentation Feedback

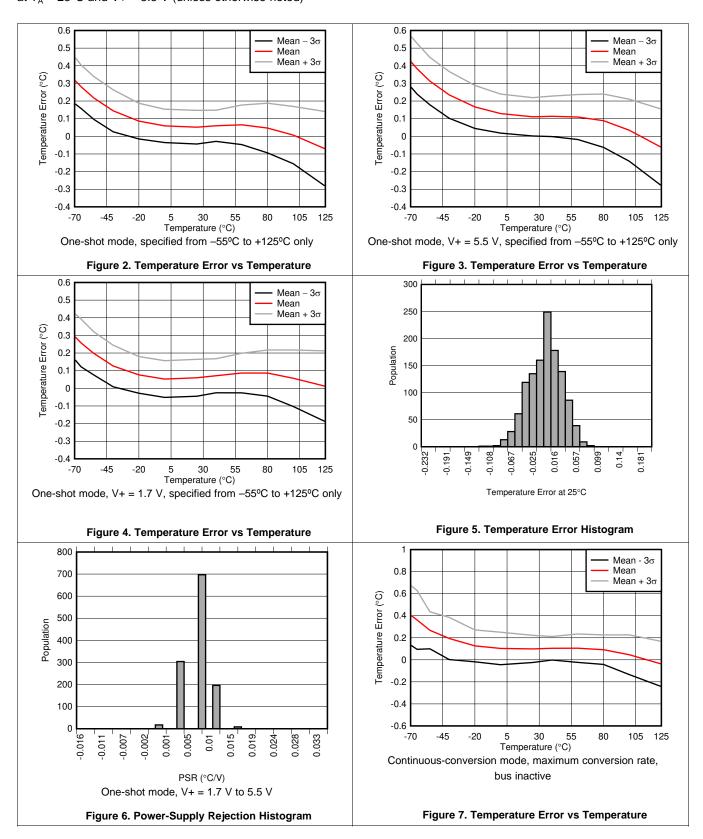

# 6.7 Typical Characteristics

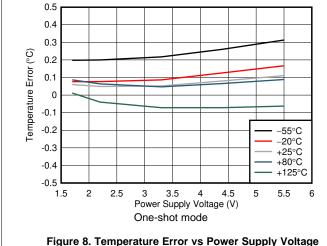

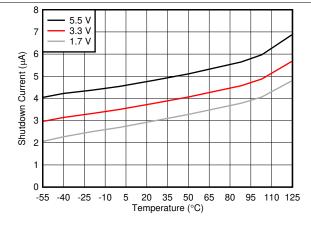

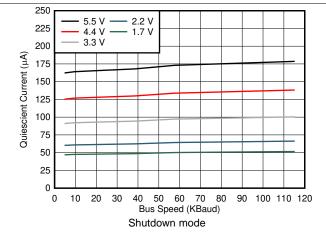

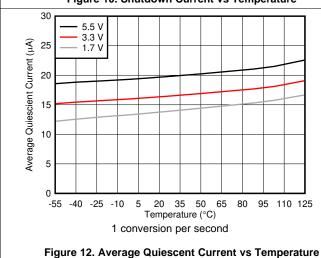

at  $T_A = 25$ °C and V+ = 3.3 V (unless otherwise noted)

# **INSTRUMENTS**

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C and V+ = 3.3 V (unless otherwise noted)

330 5.5V 315 3.3V 300 1.7V 285 270 255 Quiescent Current 240 225 210 195 180 165 150 135 120 -55 -40 -25 -10 20 35 50 Temperature (°C) No bus communication

Figure 8. Temperature Error vs Power Supply Voltage

Figure 9. Continuous-Conversion Current vs Temperature

Figure 10. Shutdown Current vs Temperature

Figure 11. Quiescent Current vs SMAART Wire™ Bus Speed

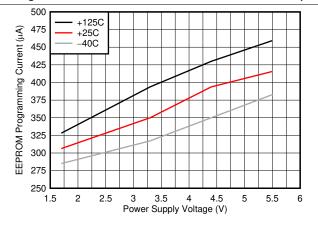

Figure 13. EEPROM Programming (Write) Current vs Power Supply Voltage

Submit Documentation Feedback

Copyright © 2015-2020, Texas Instruments Incorporated

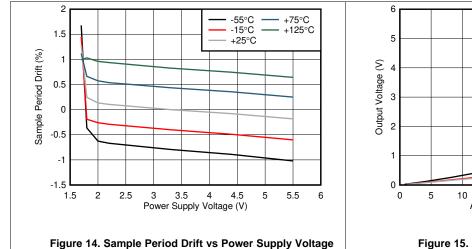

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C and V+ = 3.3 V (unless otherwise noted)

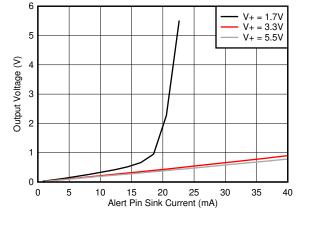

Figure 15. Alert Pin Sink Current Capability

Submit Documentation Feedback

# 7 Detailed Description

#### 7.1 Overview

The TMP107 is a digital temperature sensor that is optimal for thermal monitoring of large areas over long distances. The robust UART-compatible SMAART wire interface transfers data over a single wire at distances of up to 1000 feet (300 meters) between consecutive devices in the chain, and is capable of communicating in a daisy-chained configuration with up to 32 devices on a single bus.

The TMP107 supports individual commands to a specific device in the daisy chain, and also supports global commands that allow multiple TMP107s in the chain to respond to a single command.

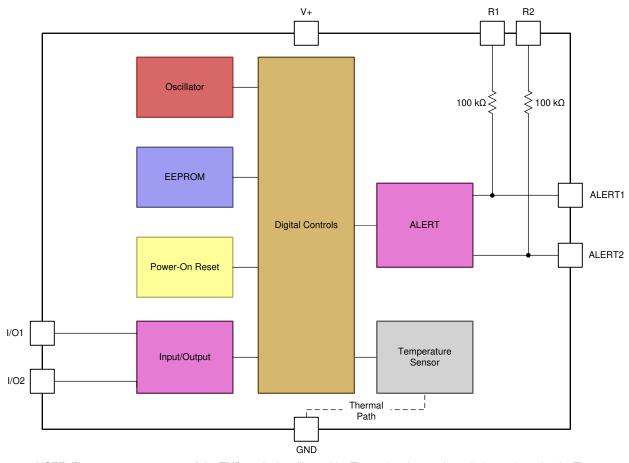

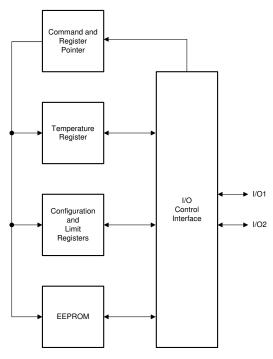

# 7.2 Functional Block Diagram

NOTE: The temperature sensor of the TMP107 is the silicon chip. Thermal paths run through the package leads. The lower thermal resistance of metal enables the leads to provide the primary thermal path.

Submit Documentation Feedback

#### 7.3 Feature Description

#### 7.3.1 Digital Temperature Output

The 14-bit digital output from each temperature measurement conversion is stored in the temperature register. Read two bytes to obtain the data. Table 1 summarizes the temperature data format. Negative numbers are represented in binary twos complement format. The temperature sensor resolution is 0.015625°C/LSB.

**Table 1. Temperature Data Format**

|                  | DIGITAL OUTPUT    |      |  |  |  |  |

|------------------|-------------------|------|--|--|--|--|

| TEMPERATURE (°C) | BINARY            | HEX  |  |  |  |  |

| 127.984          | 01 1111 1111 1111 | 1FFF |  |  |  |  |

| 100              | 01 1001 0000 0000 | 1900 |  |  |  |  |

| 80               | 01 0100 0000 1000 | 1408 |  |  |  |  |

| 75               | 01 0010 1100 0000 | 12C0 |  |  |  |  |

| 50               | 00 1100 1000 0000 | C80  |  |  |  |  |

| 25               | 00 0110 0100 0000 | 640  |  |  |  |  |

| 0.25             | 00 0000 0001 0000 | 10   |  |  |  |  |

| 0                | 00 0000 0000 0000 | 0    |  |  |  |  |

| -0.25            | 11 1111 1111 0000 | 3FF0 |  |  |  |  |

| -25              | 11 1001 1100 0000 | 39C0 |  |  |  |  |

| <b>-55</b>       | 11 0010 0100 0000 | 3240 |  |  |  |  |

Use the following rules to obtain the data for a given temperature, and vice versa.

To convert positive temperatures to a digital data format.

Divide the temperature by the resolution. Then, convert the result to binary code with a 14-bit, left-justified format

Example: (50°C) / (0.015625°C / LSB) = 3200 = C80h = 00 1100 1000 0000 = C80h

To convert a positive digital data format to temperature:

Convert the 14-bit, left-justified, binary temperature result to a decimal number. Then, multiply the decimal number by the resolution to obtain the positive temperature.

Example: 00 1100 1000 0000 = C80h =  $3200 \times (0.015625^{\circ}\text{C} / \text{LSB}) = 50^{\circ}\text{C}$

To convert negative temperatures to a digital data format.

Divide the absolute value of the temperature by the resolution and convert the result to binary code with a 14-bit, left-justified format. Then, generate the twos complement of the result by complementing the binary number and adding one.

Example:  $(|-25^{\circ}C|) / (0.015625^{\circ}C / LSB) = 1600 = 640h = 00 0110 0100 0000$

Twos complement format: 11 1001 1011 1111 + 1 = 11 1001 1100 0000 = 39C0h

To convert a negative digital data format to temperature:

Generate the twos complement of the 14-bit, left-justified binary number of the temperature result by complementing the binary number and adding one. This number is the binary representation of the absolute value of the temperature. Convert to a decimal number and multiply by the resolution to obtain the absolute temperature, then multiply by -1 for the negative sign.

Example: 11 1001 1100 0000 has a twos complement of 00 0110 0011 1111 + 1 = 00 0110 0100 0000

Convert to temperature: 00 0110 0100 0000 = 640h = 1600; 1600 × (0.015625°C / LSB) = 25°C = (|-25°C|); (|-25°C|) × (-1) = -25°C

#### 7.3.2 Temperature Limits and Alert

The TMP107 has two ALERTx pins (ALERT1 and ALERT2) for under- and overtemperature monitor functions. Both pins have independent, dynamically-programmable limits. At the end of each conversion, the temperature result is compared with the high limit and low limit registers. If the temperature is outside the limit window, the respective ALERTx pin trips. There are two polarity bits that set the active state of the ALERTx pin. The TMP107 has two flag bits (FHx and FLx) for each alert condition to indicate in which direction the temperature has moved outside of the limit window.

There are two operating modes used for alerts and flags: therm and alert. In therm mode, the ALERTx pins and FHx and FLx flags are outputs of a transparent comparator. In alert mode, the ALERTx pins and FHx and FLx flags are latched interrupts. Select between alert mode or therm mode by using the Tx/Ax (T1/A1 and T2/A2) bits in the configuration register.

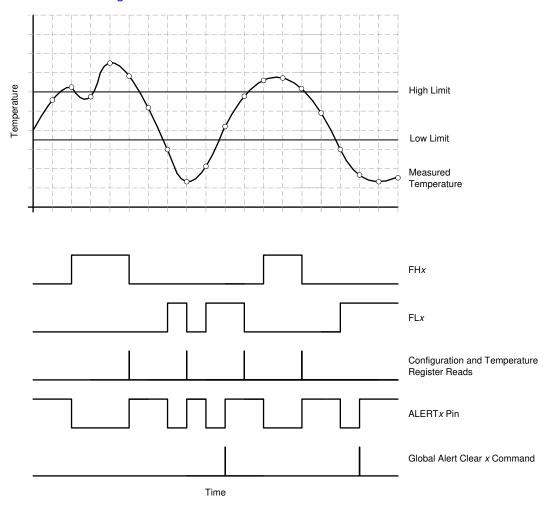

In alert mode (Tx/Ax = 0, default), the high and low limits form a temperature window. At the end of a conversion, if the temperature result exceeds the high limit or is less than the low limit, the respective flag (either FHx or FLx) and the ALERTx pin are asserted. If the alert outputs of multiple TMP107s are connected together, the TMP107 tripped alerts are still identifiable. To clear the ALERTx pin, issue a global alert clear x command, or read the configuration register as shown in Figure 16. To clear the FHx or FLx flag, read the configuration register. Alert-mode operation is shown in Figure 16.

Figure 16. ALERTx Pin Behavior in Alert Mode (POLx = 0)

Submit Documentation Feedback

Copyright © 2015–2020, Texas Instruments Incorporated

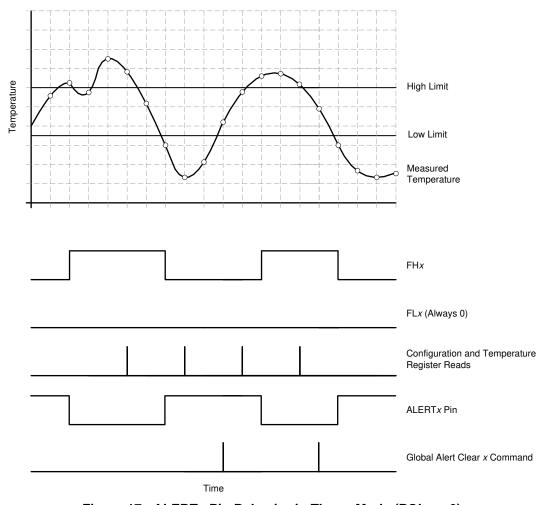

In therm mode (Tx/Ax = 1), the high and low limits are used to form an upper-limit threshold detector. If the temperature result exceeds the high limit, the FHx flag and the ALERTx pin are asserted. The FHx flag and the ALERTx pin are then deasserted only after the temperature falls below the low limit. In therm mode, only the FHx flag is active. The FLx flag always reads 0. In therm mode, ALERTx and the flags are asserted and deasserted only at the end of a conversion and cannot be cleared by a configuration register read or global alert clear x command. Figure 17 shows therm-mode operation.

Figure 17. ALERTx Pin Behavior in Therm Mode (POLx = 0)

The limit registers default values are programmed in the EEPROM, and are acquired during power up or reset. The values can be dynamically changed by writing to the register. Disable alert and flag functionality by programming the high limit register to the highest temperature (7FFCh) and the low limit register to the lowest temperature (8000h). When disabled, the alert pins can still be controlled by polarity bits POL1 and POL2 (bit 7 and bit 3, respectively, in the configuration register) so that they work like general-purpose outputs (GPOs).

#### 7.3.2.1 ALERT1, ALERT2, R1, and R2 Pins

ALERT1 and ALERT2 are open-drain output pins that require pullup resistors to operate properly. The TMP107 contains internal  $100-k\Omega$  pullup resistors connected between pins ALERT1 and R1, and pins ALERT2 and R2. To use the internal pullup resistors, connect pins R1 and R2 to V+, or to a voltage suitable for use with pullup resistors in the system. If external pullup resistors are used, float pins R1 and R2.

Product Folder Links: TMP107

Submit Documentation Feedback

Address Operation

#### 7.3.3 SMAART Wire™ Communication Interface

The TMP107 uses a TI proprietary, one-wire, UART-compatible, bidirectional, communication protocol called SMAART wire. It is a true one-wire communication protocol where the host can communicate with multiple daisy-chained TMP107 devices. The host device can be an off-the-shelf UART transceiver, or a microcontroller in which communication is performed by bit banging of the GPIO pins. When bit banging, follow the communication protocol format and specified parameters. All TMP107 devices have the default device addresses set to 0h.

After the devices are assembled in a daisy-chain configuration per the application requirements, the host must send the address-initialize command. This command initializes the daisy-chain so that all of the devices in the chain are assigned a unique incremental address respective to their position from the host controller (see the *Address Initialize* section for more information). The generated device addresses are stored in the internal EEPROM memory of each TMP107 in the chain. After the address initialization process is completed, the TMP107 devices restore their addresses from their respective EEPROM memories upon reset events.

After the daisy-chain is initialized with the address-initialize command operation, the host device can perform individual read and write operations to any device in the daisy chain by directly addressing that device. The host can also perform global read, global write, or global software reset operations on all devices in the daisy chain.

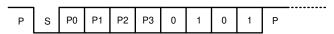

The inactive state of the bus is logic high. Every communication operation in the SMAART wire protocol consists of multiple 10-bit words. Each word is transferred least significant bit (LSB) first, with a start bit that is logic low in the beginning, a stop bit that is logic high in the end, and 8-bit data located between the start and stop bits. Each phase consists of one or more words that are transferred least significant word first. By using a start bit and stop bit for each word, the TMP107 devices can detect the start of every word and maintain synchronous communication. SMAART wire protocol communication is divided into two categories: address operations and command operations. Address operations are used to perform individual and multiple device read and write operations. Command operations are address initialize, last device polling, and global software reset operations.

Figure 18 shows the top-level phase sequences for the two types of operation. Detailed descriptions with timing diagrams are provided.

# Calibration Phase Command and Address Phase Register Pointer Phase Data Phase Command Operation Calibration Phase Command and Address Phase Data Phase

Figure 18. Address and Command Operations

#### 7.3.3.1 Communication Protocol

Only the host initiates communication. Before communication begins, all the daisy-chained devices are in transparent mode. In this mode, all the host operations are sequentially transferred to all the devices in the chain. The devices in the chain cannot communicate with each other with the exception of the address initialize command. After initialization, the devices in the chain are in one of the following four modes:

- wait for a command from the host (default mode)

- transmit the device data back to the host

- transmit the commands from the host to the subsequent device in the chain

- transmit the data from the subsequent device back to the host

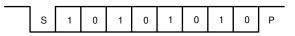

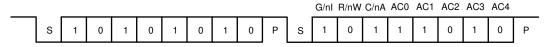

#### 7.3.3.1.1 Calibration Phase

The calibration phase is the first phase of every communication, and consists of the host sending 10-bits, as shown in Figure 19. Pull the line low in the beginning to notify each device that the host is initiating communication. Next, the host transmits calibration sequence 55h at the desired communication baud rate. The connected devices receive this calibration byte and calculate the baud rate to communicate with the host. This calibration byte is sent at the beginning of every operation; therefore, each address or command operation can be performed at a different baud rate.

Figure 19. Calibration Phase

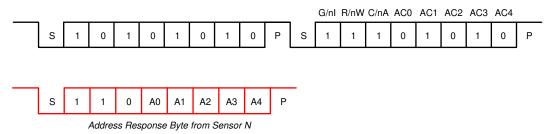

#### 7.3.3.1.2 Command and Address Phase

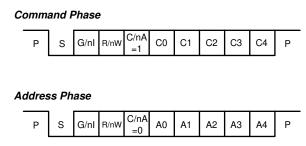

The second phase of every communication is the command and address phase. The values of the bits in this phase determine the format and structure of subsequent phases in the communication operation. Table 2 lists the command and address phase values.

**Table 2. Command and Address Phase Values**

|                       | COMMAND AND ADDRESS PHASE VALUES |      |      |     |     |     |     |              |                       |

|-----------------------|----------------------------------|------|------|-----|-----|-----|-----|--------------|-----------------------|

| COMMAND AND           | 0                                | 1    | 2    | 3   | 4   | 5   | 6   | 7            | HEX VALUE             |

| ADDRESS OPERATIONS    | G/nI<br>(LSB)                    | R/nW | C/nA | AC0 | AC1 | AC2 | AC3 | AC4<br>(MSB) | TIEX VALUE            |

| Address initialize    | 1                                | 0    | 1    | 0   | 1   | 0   | 0   | 1            | 95                    |

| Last device poll      | 1                                | 1    | 1    | 0   | 1   | 0   | 1   | 0            | 57                    |

| Global software reset | 1                                | 0    | 1    | 1   | 1   | 0   | 1   | 0            | 5D                    |

| Global alert clear 1  | 1                                | 0    | 1    | 0   | 1   | 1   | 0   | 1            | B5                    |

| Global alert clear 2  | 1                                | 0    | 1    | 0   | 1   | 1   | 1   | 0            | 75                    |

| Global read           | 1                                | 1    | 0    | A0  | A1  | A2  | А3  | A4           | Varies based on A0-A4 |

| Global write          | 1                                | 0    | 0    | A0  | A1  | A2  | А3  | A4           | Varies based on A0-A4 |

| Individual read       | 0                                | 1    | 0    | A0  | A1  | A2  | А3  | A4           | Varies based on A0-A4 |

| Individual write      | 0                                | 0    | 0    | A0  | A1  | A2  | А3  | A4           | Varies based on A0-A4 |

#### 7.3.3.1.2.1 Global or Individual (G/nl) Bit

The G/nl bit indicates if the communication is a global operation (intended for more than one device) or individual (intended for only one device).

All command operations are global; therefore, for command operations, always set the G/nl bit to 1.

For read and write address operations to multiple devices in the daisy chain simultaneously, set this bit to 1. To access an individual device, set the G/nI bit to 0.

During global operation, the host sets the address portion of the command to the maximum address required to perform the communication. For example, to perform a write to the high-limit register of all devices between addresses 1h to 5h in the daisy chain, set the G/nI bit to 1 and the address field to 5h. For individual accesses, set the address field to the desired device address.

#### 7.3.3.1.2.2 Read/Write (R/nW) Bit

The R/nW bit indicates whether the operation is read or write to the TMP107 device.

#### 7.3.3.1.2.3 Command or Address (C/nA) Bit:

The C/nA bit indicates whether the current communication is a command operation or address operation. The C/nA bit = 1 indicates a command operation. The codes for specific commands in the TMP107 are listed in Table 2. Codes other than those listed in Table 2 are reserved for factory use only.

The C/nA bit = 0 indicates an address operation. The five bits following the C/nA bit (A4 to A0) are the address bits of the device or devices that the host intends to communicate with in the chain, as shown in Figure 20.

Figure 20. Command and Address Phase

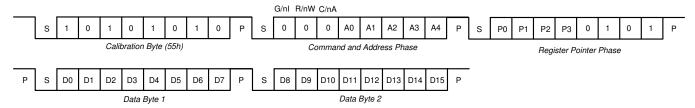

#### 7.3.3.1.3 Register Pointer Phase

The register pointer phase is provided only if the communication is an address operation. This phase of the communication shows the register pointer of the device that the host in going to write to or read from. The pointer byte has special identification code bits, as shown in Figure 21.

Figure 21. Register Pointer Phase

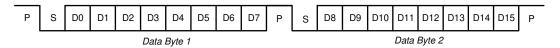

#### 7.3.3.1.4 Data Phase

The data phase is the last phase of communication. Every register location consists of two words of data. Therefore, this last phase of communication consists of at least two bytes of data with the least significant byte sent first, followed by the most significant byte.

For a write operation, the host sends data to the device or devices at the specified register pointer location.

For a read operation, the specified device or devices respond back with the data from the location specified in the register pointer phase.

Depending on the value of G/nl bit in the command and address phase, the data in this phase are either written to a targeted individual device, or to multiple devices in the daisy-chain. Individual and global read or write operations are explained in more detail in subsequent sections. Figure 22 shows a diagram of the data phase.

Figure 22. Data Phase for an Individual Read or Write Scenario

#### 7.3.3.2 SMAART Wire™ Operations

This section describes various types of communication operations and is illustrated with timing diagrams. The diagrams in this section are used only to understand functional aspects of the communication; for timing aspects, see the *Timing Requirements* table. The color of the phases in Figure 23 through Figure 29 indicates the direction of the communication. The communication phases marked in black indicate the host controller is driving the bus. The communication phases marked in red indicate one of the devices in the daisy chain is responding to the host by driving the bus. The device communicates to the host controller through intermediate devices. The intermediate devices are automatically configured as buffers to allow data to pass through from the I/O2 pin to the I/O1 pin, and vice versa.

#### 7.3.3.2.1 Command Operations

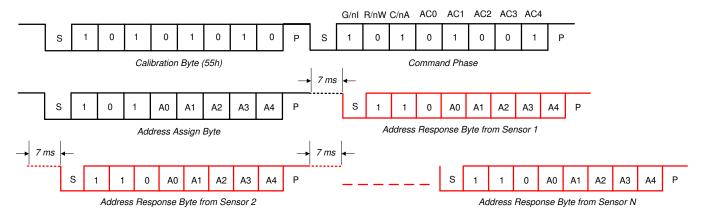

#### 7.3.3.2.1.1 Address Initialize

The address-initialize command initializes the addresses of the devices in the daisy chain. This command must be performed one time because the addresses are stored in the devices EEPROM and loaded on every reset event.

After the address-initialize command phase, the host provides one word of address-assign, command-byte data, as shown in Figure 23. This word contains the desired address of the first device on the daisy chain in the A4:A0 field. Although any value from 0 to 31 is allowed for this field, it is recommended to keep first device address at 01h. The last device address must never exceed 31. After the address-assign command bytes have been transmitted by the host, the daisy chain goes through a sequence of position detection and self-programming events where the devices in the chain identify their respective locations on the bus. During this process, the host receives incremental address response data from the individual TMP107 devices in the daisy chain that indicate the point in the chain up to which the address assignment has been completed. These responses arrive at intervals of 7 ms. This procedure is represented in Figure 23.

Figure 23. Address-Initialize Command

Until the initialization process is completed, daisy-chain communication is directed toward the host. Do not send any new commands to the chain during this period. If the address initialization sequence is interrupted as a result of glitches or disconnects in the daisy chain, the devices stall communication. In the event of a stall, each device has an internal timeout of one second (only for the address-initialize command). After one second, the communication interface in the TMP107 device resets, and the host regains control of the chain. Float the I/O2 pin of the last device in the chain. The address initialization procedure occurs serially from one device to the next; therefore, the maximum current consumed by the chain must not exceed the current required to initialize one device.

#### 7.3.3.2.1.2 Last Device Poll

When the host issues a last-device-poll command, the last sensor on the initialized daisy chain responds back with the last device address, as shown in Figure 24. The last-device-poll command is also used to check if the daisy-chain address set is intact. If the daisy chain is not intact, the host does not receive a response to the last-device-poll command. This command only works if the last device in the chain was the last device during initialization. For example, if there are ten devices in the chain during address initialization and two devices are removed, running this command does not provide the host with the address of device eight. Device eight was not the last device during chain initialization, so it cannot report that device eight is the last device in the chain. In this example, the command is not answered.

Figure 24. Last-Device-Poll Command

#### 7.3.3.2.1.3 Global Software Reset

Use the global-software-reset command to issue a software reset to the chain in order for the devices to load the power-on reset values from EEPROM and clear the temperature result register. This command performs the same function as writing a 1 to RST (bit 1 in the configuration register). The sequence of this command is shown in Figure 25.

Figure 25. Global Software Reset Command

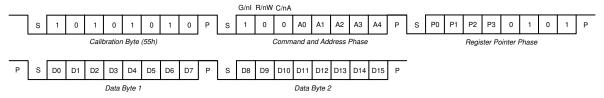

#### 7.3.3.2.2 Address Operations

#### 7.3.3.2.2.1 Individual Write

Use the individual write operation to write data to a specific register in a specific device in the daisy chain, as shown in Figure 26.

Figure 26. Individual Write Operation

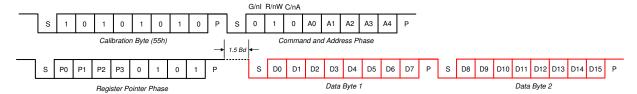

#### 7.3.3.2.2.2 Individual Read

Use the individual read operation to read the value of a register in a single device in the daisy chain, as shown in Figure 27. There is delay of up to 1.5 baud before the device responds back to the host. The host reads the data from the device by synchronizing to the falling edge of the start bit.

Figure 27. Individual Read Address Operation

#### 7.3.3.2.2.3 Global Write

Use the global write operation to write data to a specific register in multiple parts. The sequence of the communication is shown in Figure 28. Data in this operation are written to the registers in all the devices from the first device to the address specified in the address field of the command and address phase.

Figure 28. Global Write Operation

#### 7.3.3.2.2.4 Global Read

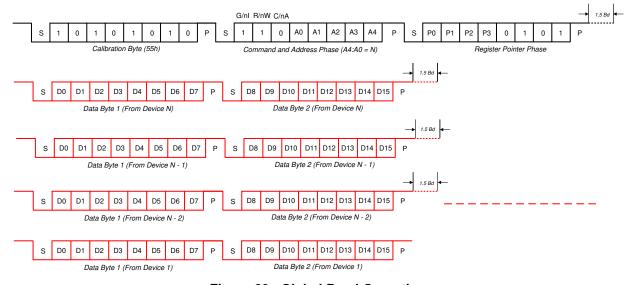

Use the global read address operation to read the value of the register pointed to by the *Register Pointer Phase* section. The daisy chain returns data starting from the address specified in the command or address phase, and ending with the address of the first device in the daisy chain. The data phase of the global read address operation is different from other address operations because the data phase consists of data read back from every device on the bus between the addressed device and first device, as shown in Figure 29. If the address specified exceeds the address of the last device, the operation halts and the bus times out after 35 ms. There is a delay of up to 1.5 baud before the devices respond back to the host. The host reads the data from the devices by synchronizing to the falling edge of the start bits.

Figure 29. Global Read Operation

Product Folder Links: TMP107

Submit Documentation Feedback

#### 7.4 Device Functional Modes

#### 7.4.1 Continuous-Conversion Mode

Continuous conversion is the default operating mode for the TMP107. In continuous-conversion mode, the TMP107 continuously measures temperature (see Table 6). After each temperature conversion, the temperature register updates with the conversion result, and the configuration register updates with the alert flags.

#### 7.4.2 Shutdown Mode

Shutdown mode minimizes power dissipation because the TMP107 shuts down all of the internal active circuitry except for those that are required to allow communication with the device. During shutdown mode, all registers can be read from or written to. To trigger a single temperature conversion in shutdown mode, issue a one-shot command (see the *One-Shot Mode* section for more details). When the conversion is complete, the TMP107 returns to shutdown mode.

#### 7.4.3 One-Shot Mode

One-shot mode triggers single temperature measurements by writing a 1 to OS (bit 12 in the configuration register) when the device is in shutdown mode. Following the completion of the single temperature conversion, the TMP107 returns to shutdown mode. Reading the OS bit always results in a 0. Use one-shot mode to achieve the lowest power consumption. For highest power savings and accuracy, do not communicate through the I/O bus during this mode.

Copyright © 2015–2020, Texas Instruments Incorporated Product Folder Links: *TMP107*

#### 7.5 Programming

#### **7.5.1 EEPROM**

The TMP107 has an internal EEPROM that is used to program and store values for writable registers, such as the configuration, high limit, and low limit registers. The EEPROM also has eight, 16-bit locations of general-purpose memory. By programming the configuration register, the EEPROM is used to store critical, system information, such as unique calibration information for the host, unique system serial ID, or a user-specific conversion rate. During the reset event, the data from the EEPROM are copied into the corresponding registers. Two registers that are not updated by the EEPROM are the temperature register and die identification register.

The electrical and timing specifications for the EEPROM are provided in the *Specifications* section. See Table 3 for the register map to the eight, internal EEPROM locations (register addresses 6h to Dh).

#### 7.5.2 EEPROM Operations

#### 7.5.2.1 EEPROM Unlock

After power up, the EEPROM is locked for programming by default. When locked, all writes to the EEPROM are ignored. In order to program the EEPROM, first unlock the memory for programming by writing logic 1 to NUS (bit 0 in the temperature register) using a regular write communication. EEPROM locations are readable whether locked or unlocked. Locking the EEPROM by default is a protection provided to prevent unintentional triggering of EEPROM programming during normal device operations.

#### 7.5.2.2 EEPROM Lock

If the EEPROM is unlocked for programming, make sure to lock the EEPROM after the programming operations. Lock the EEPROM by writing logic 0 to NUS (bit 0 in the temperature register).

#### 7.5.2.3 EEPROM Programming

After the EEPROM is unlocked, a write to any EEPROM-associated register triggers EEPROM programming. A programming event takes up to 16 ms, depending on the device conditions; therefore, space out successive commands in 16-ms write periods.

Poll BUSY (bit 1 in the temperature register) to check the EEPROM programming status. The BUSY bit = 1 when the EEPROM program is in progress. The BUSY bit = 0 after programming is complete and the EEPROM is ready for another program operation. While the EEPROM is being programmed, writes to every other register are prevented in order to protect device data from corruption until programming is complete.

When the global write operation is issued to program the EEPROM locations, all of the devices in the daisy chain specified within the address field perform the programming simultaneously. This simultaneous programming leads to an increase in current in the supply wire of the daisy chain, and may create a drop in the supply voltage. It is important to maintain the supply voltage at greater than 1.8 V during the EEPROM programming in order to program devices in the daisy chain.

# 7.5.2.4 EEPROM Acquire or Read

The EEPROM locations that store the power-on reset values of the registers are automatically loaded into the corresponding registers at reset. The general-purpose EEPROM locations are readable even when the EEPROM is locked. While a read is performed on an EEPROM location in the register map, there is a slightly longer delay in the stop bit (~100 µs) between the pointer phase and the phase data in the communication in order to allow the EEPROM to be read. The standard UART protocol allows for such delays when the UART transceiver is being used. The amount of current consumption from the EEPROM read is negligible compared to the current consumption from communication.

# 7.6 Register Map

Figure 30 shows the internal register structure of the TMP107.

Figure 30. Register Structure

Table 3 describes the registers available with their addresses, followed by the description of the bits in each register. All register default values (except for the temperature register and die ID register) can be modified by writing to the EEPROM. All reset values listed are the factory-default values.

Table 3. Register Map and Pointer Addresses

| P3 | P2 | P1 | P0 | ADDRESS<br>(HEX) | REGISTER NAME                  |

|----|----|----|----|------------------|--------------------------------|

| 0  | 0  | 0  | 0  | 0h               | Temperature register           |

| 0  | 0  | 0  | 1  | 1h               | Configuration register         |

| 0  | 0  | 1  | 0  | 2h               | High limit 1                   |

| 0  | 0  | 1  | 1  | 3h               | Low limit 1                    |

| 0  | 1  | 0  | 0  | 4h               | High limit 2                   |

| 0  | 1  | 0  | 1  | 5h               | Low limit 2                    |

| 0  | 1  | 1  | 0  | 6h               | EEPROM 1 register              |

| 0  | 1  | 1  | 1  | 7h               | EEPROM 2 register              |

| 1  | 0  | 0  | 0  | 8h               | EEPROM 3 register              |

| 1  | 0  | 0  | 1  | 9h               | EEPROM 4 register              |

| 1  | 0  | 1  | 0  | Ah               | EEPROM 5 register              |

| 1  | 0  | 1  | 1  | Bh               | EEPROM 6 register              |

| 1  | 1  | 0  | 0  | Ch               | EEPROM 7 register              |

| 1  | 1  | 0  | 1  | Dh               | EEPROM 8 register              |

| 1  | 1  | 1  | 1  | Fh               | Die identification (read only) |

Submit Documentation Feedback

#### 7.6.1 Temperature Register (address = 0h) [reset = 0h]

The temperature register of the TMP107 is configured as a 16-bit register that stores the output of the most recent conversion and two status bits. Two bytes must be read to obtain data, and they are described in Figure 31. The upper 14 bits are used to indicate temperature. One LSB equals 0.015625°C. The temperature is represented in binary twos complement format. Following power-up or reset, the temperature register reads 0°C until the first conversion is complete. The remaining two bits indicate the EEPROM status. When the EEPROM is locked, the EEPROM cannot be programmed and all writes to the EEPROM addresses are ignored. By default, the EEPROM is locked for programming at power-on reset and must be unlocked in order to be programmed.

Figure 31. Temperature Register

| 15  | 14   | 13   | 12  | 11 | 10 | 9  | 8  |  |  |

|-----|------|------|-----|----|----|----|----|--|--|

| T13 | T12  | T11  | T10 | T9 | Т8 | T7 | T6 |  |  |

|     | R-0h |      |     |    |    |    |    |  |  |

| 7   | 6    | 5    | 4   | 3  | 2  | 1  | 0  |  |  |

| T5  | T4   | BUSY | NUS |    |    |    |    |  |  |

|     |      |      |     |    |    |    |    |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### **Table 4. Temperature Register Field Descriptions**

| Bit  | Field  | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                       |

|------|--------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-2 | T13-T0 | R    | 0h    | Temperature result (resolution of 0.015625°C). Range: -128°C to +128°C.                                                                                                                                                                                                                                                                           |

| 1    | BUSY   | R    | Oh    | This bit indicates the status of the EEPROM.  0: Indicates that the EEPROM is ready; the EEPROM has finished the last transaction and is ready to accept new commands.  1: Indicates that the EEPROM is busy completing a command and must not be given more commands. Any new commands given to the EEPROM are ignored by the EEPROM controller. |

| 0    | NUS    | R/W  | 0h    | EEPROM unlock state. 0: EEPROM locations are locked for programming. 1: EEPROM locations are unlocked for programming.                                                                                                                                                                                                                            |

# 7.6.2 Configuration Register (address = 1h) [reset = A000h]

The configuration register is a read and write register used to store bits that control the part operation. The format and power-up or reset value of the configuration register for the TMP107 is shown in Figure 32 and Table 5. When the NUS bit is 0, all writes to this register are stored in register logic. When NUS is 1, then all writes to this register program the EEPROM location that stores the configuration bits. Writes to this location are followed by a 16-ms wait period for programming the EEPROM. When the configuration register is written, the current conversion is aborted and new action is taken based on the new written bits. Thus, if the TMP107 is put into shutdown, the device goes into shutdown immediately. If the conversion rate is changed, any ongoing conversion is aborted and a new conversion starts with the new conversion rate.

Figure 32. Configuration Register

| 15     | 14     | 13   | 12     | 11     | 10       | 9    | 8        |

|--------|--------|------|--------|--------|----------|------|----------|

| CR2    | CR1    | CR0  | os     | SD     | FH1      | FL1  | T1/A1    |

|        | R/W-5h |      | R/W-0h | R/W-0h | R-0h     | R-0h | R/W-0h   |

| 7      | 6      | 5    | 4      | 3      | 2        | 1    | 0        |

| POL1   | FH2    | FL2  | T2/A2  | POL2   | Reserved | RST  | Reserved |

| R/W-0h | R-0h   | R-0h | R/W-0h | R/W-0h | R-0h     | W-0h | R-0h     |

LEGEND: R/W = Read/Write; R = Read only; W = Write only; -n = value after reset

#### **Table 5. Configuration Register Field Descriptions**

| D:4   | Field   |      |       | Passintian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|---------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Field   | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15-13 | CR2-CR0 | R/W  | 5h    | Conversion rate. The conversion rate bits control the update rate of the analog-to-digital converter (ADC). Table 6 describes the relationship between the values of the conversion rate bits and the corresponding conversion time and average quiescent current. These bits only affect continuous-conversion mode and not one-shot mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12    | os      | R/W  | Oh    | One-shot mode. 0: Default. 1: Starts a single temperature conversion if the SD bit is set to 1. The TMP107 returns to the shutdown state at the completion of the single conversion. When the configuration register is read, OS always reads zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11    | SD      | R/W  | Oh    | Shutdown mode. 0: The TMP107 is in continuous-conversion mode. 1: The TMP107 is in shutdown mode. Initiate a conversion by writing a 1 to the OS bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10    | FH1     | R    | 0h    | High limit 1 flag. 0: Indicates that the temperature result does not exceed high limit 1. 1: Indicates when the temperature result exceeds high limit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9     | FL1     | R    | 0h    | Low limit 1 flag. In therm mode, this bit is not used and always reads 0.  0: In alert mode, this bit indicates that the temperature result is greater than low limit 1.  1: In alert mode, this bit indicates when the temperature result is less than low limit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8     | T1/A1   | R/W  | Oh    | Alert and therm mode 1.  0: Alert mode: In this mode, the high limit 1 and low limit 1 form a window. If the temperature result is greater than high limit 1 or less than low limit 1, the respective flag (either FH1 or FL1) is asserted. After the flag is asserted, clear the flag by reading the configuration register.  1: Therm mode: In this mode, the limits are used to form an upper limit threshold detector. If the temperature result is greater than high limit 1, the FH1 flag is asserted. The FH1 flag is then deasserted only after the temperature drops below low limit 1. In therm mode, only the FH1 flag is active. The FL1 flag always reads 0. In this mode, the flags are asserted and deasserted only at the end of a conversion and cannot be cleared by a configuration register read. |

| 7     | POL1    | R/W  | 0h    | 0: Polarity of the ALERT1 pin is active low. 1: Polarity of the ALERT1 pin is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6     | FH2     | R    | 0h    | High limit 2 flag. 0: Indicates that the temperature result does not exceed high limit 2. 1: Indicates when the temperature result exceeds high limit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5     | FL2     | R    | Oh    | Low Limit 2 Flag. In therm mode, this bit is not used and always reads 0.  0: In alert mode, this bit indicates that the temperature result is greater than low limit 2.  1: In alert mode, this bit indicates when the temperature result is less than low limit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Table 5. Configuration Register Field Descriptions (continued)

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | T2/Ā2    | R/W  | Oh    | Alert and therm mode 2.  0: Alert mode: in this mode, the high limit 2 and low limit 2 form a window. If the temperature result is greater than high limit 2 or less than low limit 2, the respective flag (either FH2 or FL2) is asserted. After the flag is asserted, clear the flag by reading the configuration register.  1: Therm mode: in this mode, the limits are used to form an upper limit threshold detector. If the temperature result is greater than high limit 2, the FH2 flag is asserted. The FH2 flag is then deasserted only after the temperature drops below low limit 2. In therm mode, only the FH2 flag is active. The FL2 flag always reads 0. In this mode, the flags are asserted and deasserted only at the end of a conversion and cannot be cleared by a configuration register read. |

| 3   | POL2     | R/W  | 0h    | O: Polarity of the ALERT2 pin is active low.     Polarity of the ALERT2 pin is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | Reserved | R    | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1   | RST      | W    | Oh    | Software reset. 0: Default. 1: Reset. This bit is a write-only bit and is used to perform a software reset on the TMP107.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | Reserved | R/W  | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **Table 6. Conversion Rates**

| CR2 | CR1 | CR0 | CONVERSION PERIOD | CONVERSIONS PER SECOND | AVERAGE I <sub>Q</sub><br>(V+ = 3.3 V) |

|-----|-----|-----|-------------------|------------------------|----------------------------------------|

| 0   | 0   | 0   | 15 ms             | 62                     | 200 μΑ                                 |

| 0   | 0   | 1   | 50 ms             | 20                     | 20 μΑ                                  |

| 0   | 1   | 0   | 100 ms            | 10                     | 15 μΑ                                  |

| 0   | 1   | 1   | 250 ms            | 4                      | 11 μΑ                                  |

| 1   | 0   | 0   | 500 ms            | 2                      | 9 μΑ                                   |

| 1   | 0   | 1   | 1 s (default)     | 1 (default)            | 7 μΑ                                   |

| 1   | 1   | 0   | 4 s               | 0.25                   | 6 μΑ                                   |

| 1   | 1   | 1   | 16 s              | 0.0625                 | 5 μΑ                                   |

# 7.6.3 High Limit 1 Register (address = 2h) [reset = 7FFCh]

# Figure 33. High Limit 1 Register

| 15     | 14     | 13     | 12     | 11    | 10    | 9     | 8     |

|--------|--------|--------|--------|-------|-------|-------|-------|

| TH1_13 | TH1_12 | TH1_11 | TH1_10 | TH1_9 | TH1_8 | TH1_7 | TH1_6 |

|        |        |        |        |       |       |       |       |

| 7      | 6      | 5      | 4      | 3     | 2     | 1     | 0     |

| TH1_5  | TH1_4  | TH1_0  | Rese   | erved |       |       |       |

|        |        |        | R-     | -0h   |       |       |       |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Table 7. High Limit 1 Register Field Descriptions

| Bit  | Field        | Туре | Reset | Description                                                                                 |

|------|--------------|------|-------|---------------------------------------------------------------------------------------------|

| 15-2 | TH1_13-TH1_0 | R/W  | 1FFFh | High limit for alert function 1. Resolution is 0.015625°C. Data is in twos complement form. |

| 1-0  | Reserved     | R    | 0h    | Reserved                                                                                    |

# 7.6.4 Low Limit 1 Register (address = 3h) [reset = 8000h]

# Figure 34. Low Limit 1 Register

| 15     | 14          | 13     | 12     | 11    | 10    | 9     | 8     |  |  |

|--------|-------------|--------|--------|-------|-------|-------|-------|--|--|

| TL1_13 | TL1_12      | TL1_11 | TL1_10 | TL1_9 | TL1_8 | TL1_7 | TL1_6 |  |  |

|        | R/W-80h     |        |        |       |       |       |       |  |  |

| 7      | 7 6 5 4 3 2 |        |        |       |       |       |       |  |  |

| TL1_5  | TL1_4       | TL1_0  | Rese   | erved |       |       |       |  |  |

|        |             |        | R-     | -0h   |       |       |       |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Table 8. Low Limit 1 Register Field Descriptions

| Bit  | Field        | Туре | Reset | Description                                                                                |

|------|--------------|------|-------|--------------------------------------------------------------------------------------------|

| 15-2 | TL1_13-T1_L0 | R/W  | 2000h | Low limit for alert function 1. Resolution is 0.015625°C. Data is in twos complement form. |

| 1-0  | Reserved     | R    | 0h    | Reserved                                                                                   |

# 7.6.5 High Limit 2 Register (address = 4h) [reset = 7FFCh]

# Figure 35. High Limit 2 Register

| 15      | 14     | 13     | 12     | 11    | 10    | 9           | 8 |

|---------|--------|--------|--------|-------|-------|-------------|---|

| TH2_13  | TH2_12 | TH2_11 | TH2_10 | TH2_9 | TH2_8 | TH2_7 TH2_6 |   |

| R/W-7Fh |        |        |        |       |       |             |   |

| 7       | 6      | 2      | 1      | 0     |       |             |   |

| TH2_5   | TH2_4  | TH2_0  | Rese   | erved |       |             |   |

|         |        |        |        |       |       |             |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Table 9. High Limit 2 Register Field Descriptions

| Bit  | Field        | Туре | Reset | Description                                                                                 |

|------|--------------|------|-------|---------------------------------------------------------------------------------------------|

| 15-2 | TH2_13-TH2_0 | R/W  | 1FFFh | High limit for alert function 2. Resolution is 0.015625°C. Data is in twos complement form. |

| 1-0  | Reserved     | R    | 0h    | Reserved                                                                                    |

# 7.6.6 Low Limit 2 Register (address = 5h) [reset = 8000h]