# High and Low Side Driver

### Features

- Gate drive supplies up to 20V per channel

- Undervoltage lockout for V<sub>CC</sub>, V<sub>BS</sub>

- 3.3 V, 5V, 15V input logic compatible

- Tolerant to negative transient voltage

- Designed for use with bootstrap power supplies

- Matched propagation delays

- Output in phase with the Inputs

- -40°C to 125°C operating range

- RoHS compliant

#### Description

The IRS2005 is a high voltage, high speed power MOSFET and IGBT driver with independent high and low side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The logic input is compatible with standard CMOS or LSTTL output, down to 3.3V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high side configuration which operates up to 200 V. Propagation delays are matched to simplify the HVIC's use in high frequency applications.

#### **Product Summary**

| Voffset                                   | ≤ 200V        |

|-------------------------------------------|---------------|

| Vout                                      | 10 V – 20V    |

| I <sub>o+</sub> & I <sub>o-</sub> (typ.)  | 290mA & 600mA |

| t <sub>ON</sub> & t <sub>OFF</sub> (typ.) | 160ns & 150ns |

| Delay matching (max.)                     | 50ns          |

### **Package Options**

### **Typical Applications**

- Appliance motor drives

- Servo drives

- Micro inverter drives

- General purpose three phase inverters

| Daga Dart Number | Deckers True     | Standar       | d Pack | Onderskie Derf Norsken |

|------------------|------------------|---------------|--------|------------------------|

| Base Part Number | Package Type     | Form Quantity |        | Orderable Part Number  |

|                  |                  | Tube/Bulk     | 95     | IRS2005SPBF            |

| IRS2005SPBF      | 8-Lead SOIC      | Tape and Reel | 2500   | IRS2005STRPBF          |

| IRS2005MPBF      | 14-Lead MLPQ 4x4 | Tape and Reel | 3000   | IRS2005MTRPBF          |

# International

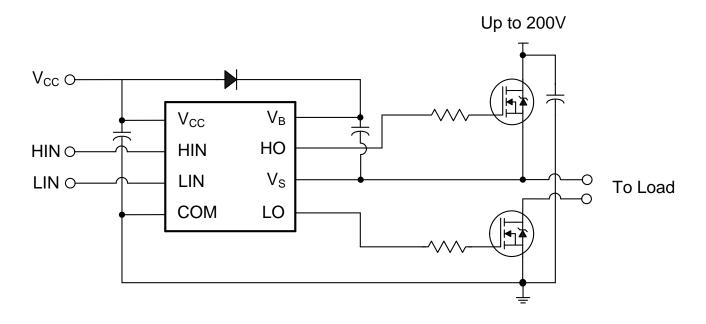

# **Typical Connection Diagram**

(Refer to Lead Assignments for correct pin configuration). This diagram shows electrical connections only. Please refer tour Application Notes & DesignTips for proper circuit board layout.

#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM unless otherwise stated in the table. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol            | Definition                                 | Min.             | Max.                 | Units                 |       |

|-------------------|--------------------------------------------|------------------|----------------------|-----------------------|-------|

| Vcc               | Low side supply voltage                    |                  | -0.3                 | $25^{\dagger}$        |       |

| VIN               | Logic input voltage                        |                  | COM - 0.3            | V <sub>CC</sub> + 0.3 |       |

| VB                | High-side floating well supply voltage     | je               | -0.3                 | 225                   |       |

| Vs                | High-side floating well supply return      | n voltage        | V <sub>B</sub> - 25  | V <sub>B</sub> + 0.3  | V     |

| Vно               | Floating gate drive output voltage         |                  | Vs - 0.3             | V <sub>B</sub> + 0.3  |       |

| VLO               | Low-side output voltage                    |                  | COM - 0.3            | Vcc + 0.3             |       |

| COM               | Power ground                               |                  | V <sub>CC</sub> - 25 | V <sub>CC</sub> + 0.3 |       |

| dVs/dt            | Allowable Vs offset supply transient       | relative to COM  | _                    | 50                    | V/ns  |

| P                 | Package power dissipation @ T <sub>A</sub> | 8-Lead SOIC      | —                    | 0.625                 | 10/   |

| PD                | ≤+25°C                                     | 14-Lead MLPQ 4x4 | —                    | 2.08                  | - W   |

| Dil               | Thermal resistance, junction to            | 8-Lead SOIC      | _                    | 200                   | 00004 |

| Rth <sub>JA</sub> | ambient                                    | 14-Lead MLPQ 4x4 | _                    | 36                    | •C/W  |

| TJ                | Junction temperature                       |                  | _                    | 150                   |       |

| Ts                | Storage temperature                        |                  | -55                  | 150                   | °C    |

| ΤL                | Lead temperature (soldering, 10 se         | conds)           | _                    | 300                   |       |

† All supplies are tested at 25V.

#### **Recommended Operating Conditions**

For proper operation, the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to COM unless otherwise stated in the table. The offset rating is tested with supplies of ( $V_{CC}$  - COM) = ( $V_B$  -  $V_S$ ) = 15V.

| Symbol          | Definition                                                 | Min                  | Max   | Units |

|-----------------|------------------------------------------------------------|----------------------|-------|-------|

| Vcc             | Low-side supply voltage                                    | 10                   | 20    | V     |

| VIN             | Logic input voltage                                        | 0                    | Vcc   |       |

| VB              | High-side floating well supply voltage                     | Vs+10                | Vs+20 |       |

| Vs              | High-side floating well supply offset voltage <sup>†</sup> | COM - 8 <sup>†</sup> | 200   |       |

| Vно             | Floating gate drive output voltage                         | Vs                   | VB    |       |

| V <sub>LO</sub> | Low-side output voltage                                    | СОМ                  | Vcc   |       |

| TA              | Ambient temperature                                        | -40                  | 125   | °C    |

† Logic operation for VS of -8 V to 200 V. Logic state held for V<sub>S</sub> of -8 V to -V<sub>BS</sub>. Please refer to Design Tip DT97-3 for more details.

#### **Static Electrical Characteristics**

$(V_{CC} - COM) = (V_B - V_S) = 15V$ .  $T_A = 25^{\circ}C$  unless otherwise specified. The V<sub>IN</sub> and I<sub>IN</sub> parameters are referenced to COM. The V<sub>O</sub> and I<sub>O</sub> parameters are referenced to respective V<sub>S</sub> and COM and are applicable to the respective output leads HO or LO. The V<sub>CCUV</sub> parameters are referenced to COM. The V<sub>BSUV</sub> parameters are referenced to V<sub>S</sub>.

| Symbol              | Definition                                                        | Min. | Тур. | Max. | Units | Test Conditions                                         |

|---------------------|-------------------------------------------------------------------|------|------|------|-------|---------------------------------------------------------|

| V <sub>BSUV+</sub>  | V <sub>BS</sub> supply undervoltage positive going threshold      | 8.0  | 8.9  | 9.8  |       |                                                         |

| V <sub>BSUV</sub> - | V <sub>BS</sub> supply undervoltage negative going threshold      | 7.4  | 8.2  | 9    |       |                                                         |

| V <sub>BSUVHY</sub> | V <sub>BS</sub> supply undervoltage hysteresis                    | —    | 0.7  | _    | N N   |                                                         |

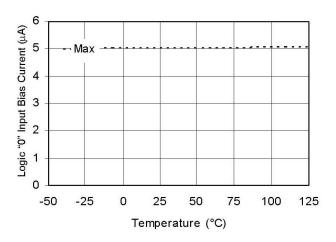

| V <sub>CCUV+</sub>  | V <sub>CC</sub> supply undervoltage positive going threshold      | 8.0  | 8.9  | 9.8  | V     |                                                         |

| V <sub>CCUV</sub> - | V <sub>CC</sub> supply undervoltage negative going threshold      | 7.4  | 8.2  | 9    |       |                                                         |

| V <sub>CCUVHY</sub> | Vcc supply undervoltage hysteresis                                | _    | 0.7  | _    |       |                                                         |

| I <sub>LK</sub>     | High-side floating well offset supply leakage                     |      | _    | 50   |       | $V_B = V_S = 200V$                                      |

| I <sub>QBS</sub>    | Quiescent V <sub>BS</sub> supply current                          | _    | 45   | 75   | μA    | All inputs are in the off state                         |

| I <sub>QCC</sub>    | Quiescent V <sub>CC</sub> supply current                          |      | 300  | 520  |       |                                                         |

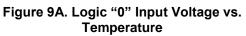

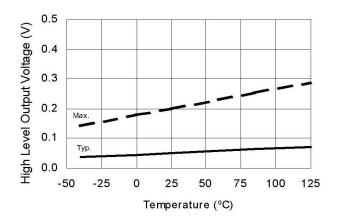

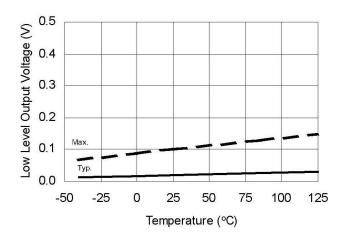

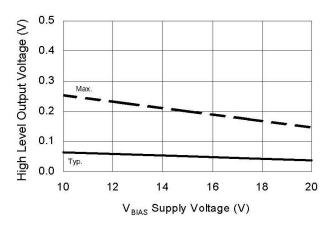

| V <sub>OH</sub>     | High level output voltage drop, V <sub>BIAS</sub> -V <sub>O</sub> | —    | 0.05 | 0.2  | V     | L 0 m 4                                                 |

| V <sub>OL</sub>     | Low level output voltage drop, Vo                                 |      | 0.02 | 0.1  | V     | $I_0 = 2 \text{ mA}$                                    |

| I <sub>o+</sub>     | Output high short circuit pulsed current                          | 200  | 290  | _    | m (   | V <sub>O</sub> = 0V, V <sub>IN</sub> = 0V<br>PW ≤ 10µs  |

| I <sub>0-</sub>     | Output low short circuit pulsed current                           | 420  | 600  | _    | mA    | V <sub>O</sub> = 15V, V <sub>IN</sub> = 5V<br>PW ≤ 10µs |

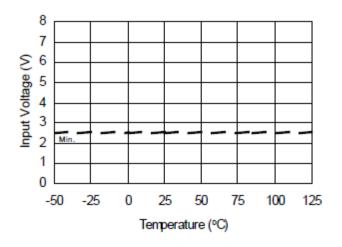

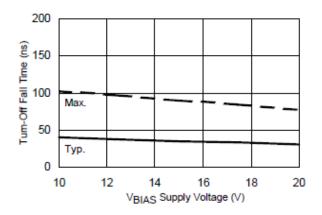

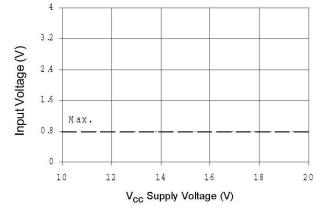

| V <sub>IH</sub>     | Logic "1" input voltage                                           |      | —    | _    | V     |                                                         |

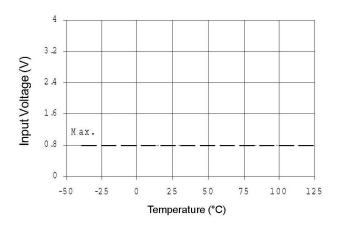

| VIL                 | Logic "0" input voltage                                           |      | _    | 0.8  | V     |                                                         |

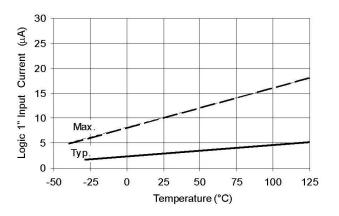

| I <sub>IN+</sub>    | Input bias current (HO = High)                                    | _    | 3    | 10   |       | $V_{IN} = 5V$                                           |

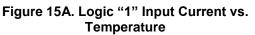

| I <sub>IN-</sub>    | Input bias current (HO = Low)                                     | —    | _    | 5    | μA    | $V_{IN} = 0V$                                           |

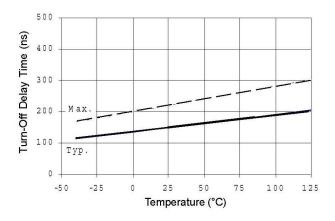

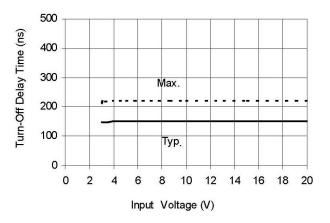

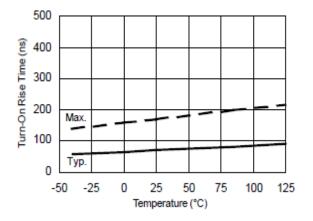

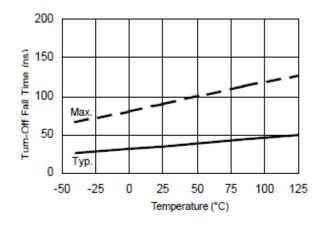

#### **Dynamic Electrical Characteristics**

$V_{CC} = V_B = 15V$ ,  $V_S = COM$ ,  $T_A = 25^{\circ}C$ , and  $C_L = 1000pF$  unless otherwise specified.

| Symbol         | Definition                                                | Min. | Тур. | Max. | Units | Test Conditions |

|----------------|-----------------------------------------------------------|------|------|------|-------|-----------------|

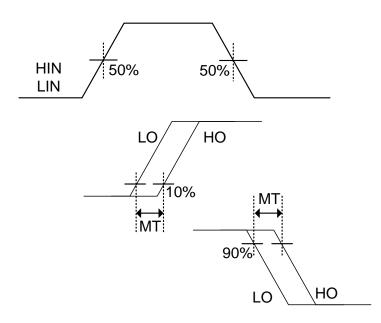

| ton            | Turn-on propagation delay                                 |      | 160  | 220  |       | Vs = 0V or 200V |

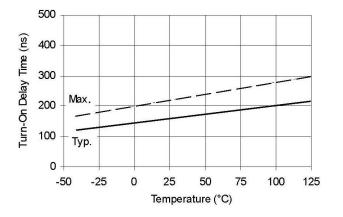

| toff           | Turn-off propagation delay                                |      | 150  | 220  |       | VS = 0V 0I 200V |

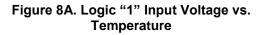

| t <sub>R</sub> | Turn-on rise time                                         | —    | 70   | 170  | 20    |                 |

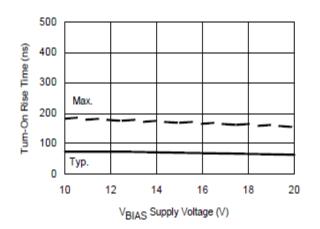

| t⊨             | Turn-off fall time                                        | _    | 30   | 90   | ns    | $V_{S} = 0V$    |

| tril           | Minimum pulse input filter time                           | _    | 300  | _    |       |                 |

| MT             | Delay matching time (t <sub>ON</sub> , t <sub>OFF</sub> ) | —    | _    | 50   |       |                 |

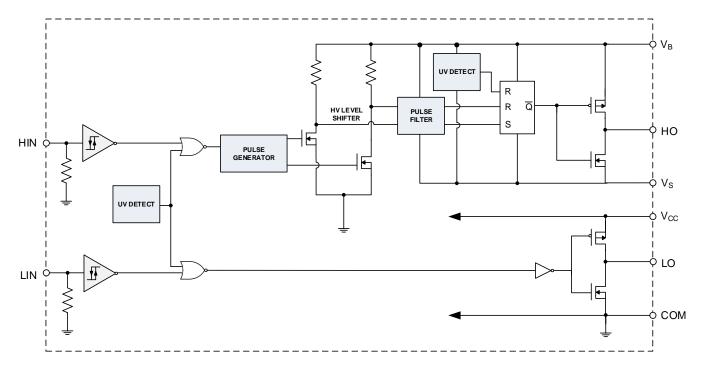

## **Functional Block Diagram**

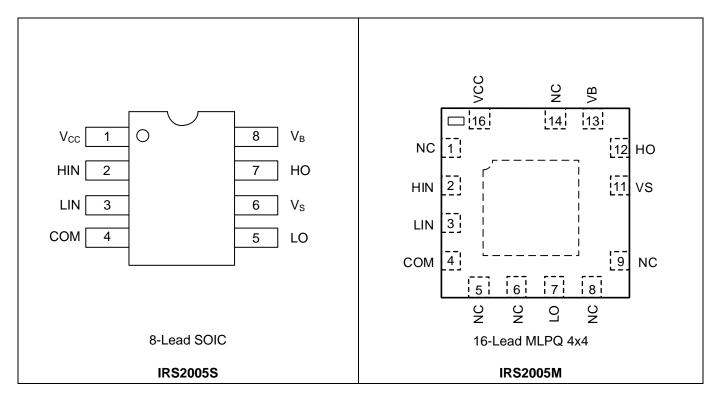

## Lead Definitions

| Symbol | Description                                                  |  |

|--------|--------------------------------------------------------------|--|

| VCC    | Low-side and logic supply voltage                            |  |

| VB     | High-side gate drive floating supply                         |  |

| VS     | High voltage floating supply return                          |  |

| HIN    | Logic inputs for high-side gate driver output (HO), in phase |  |

| LIN    | Logic inputs for low-side gate driver output (LO), in phase  |  |

| НО     | High-side driver output                                      |  |

| LO     | Low-side driver output                                       |  |

| СОМ    | Low-side gate drive return                                   |  |

## Lead Assignments

# **Application Information and Additional Details**

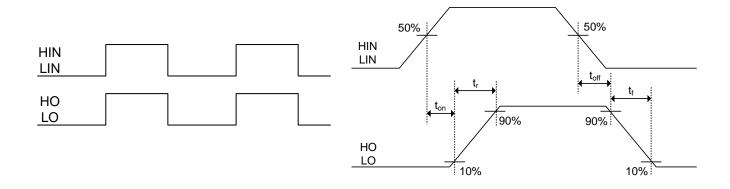

#### Figure 1. Input/Output Timing Diagram

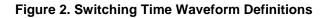

Figure 3. Delay Matching Waveform Definitions

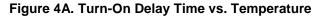

Figure 4C. Turn-On Delay Time vs. Input Voltage

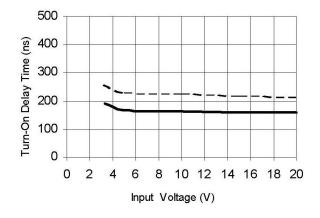

Figure 5B. Turn-Off Delay Time vs. Supply Voltage

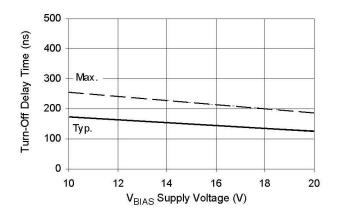

Figure 4B. Turn-On Delay Time vs. Supply Voltage

Figure 5A. Turn-Off Delay Time vs. Temperature

Figure 6A. Turn-On Rise Time vs. Temperature

Figure 7A. Turn-Off Fall Time vs. Temperature

Figure 6B. Turn-On Rise Time vs. Voltage

Figure 7B. Turn-Off Fall Time vs. Voltage

Figure 8B. Logic "1" Input Voltage vs. Voltage

# International

# IRS2005(S,M)PBF

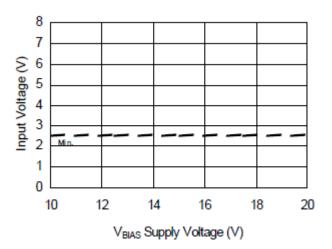

Figure 9B. Logic "0" Input Voltage vs. Supply Voltage

Figure 10B. High Level Output vs. Supply Voltage

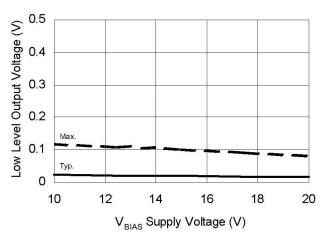

Figure 11B. Low Level Output vs. Supply Voltage

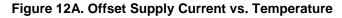

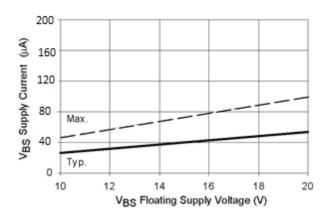

Figure 13A. V<sub>BS</sub> Supply Current vs. Temperature

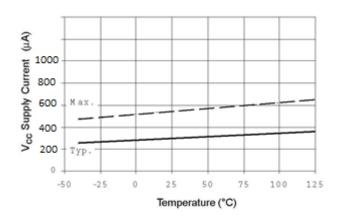

Figure 14A.  $V_{\text{CC}}$  Supply Current vs. Temperature

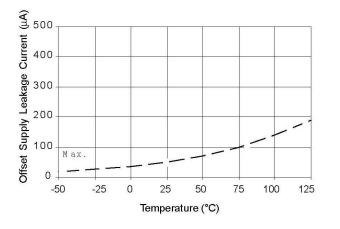

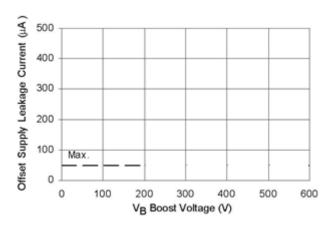

Figure 12B. Offset Supply Current vs. Voltage

Figure 13B. V<sub>BS</sub> Supply Current vs. Voltage

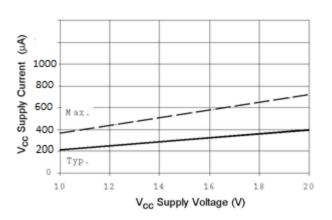

Figure 14B. V<sub>CC</sub> Supply Current vs. Voltage

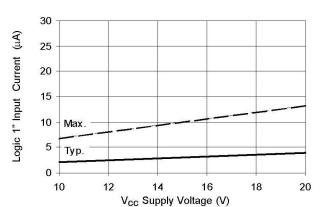

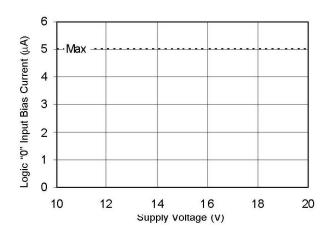

Figure 16A. Logic "0" Input Bias Current

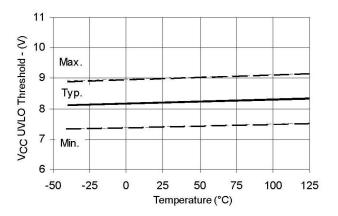

Figure 17A. V<sub>CC</sub>\V<sub>BS</sub> Undervoltage Threshold(+) vs. Temperature

Figure 15B. Logic "1" Input Current vs. Voltage

Figure 16B. Logic "0" Input Bias Current

Figure 17B.  $V_{CC}$  V<sub>BS</sub> Undervoltage Threshold(-) vs. Temperature

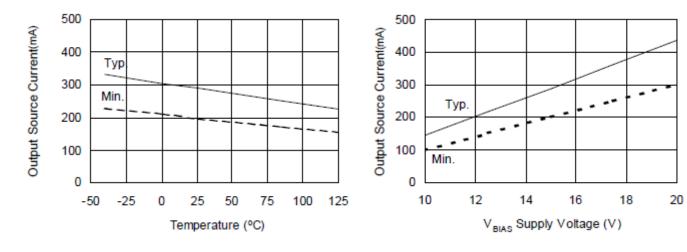

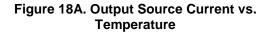

Figure 19A. Output Sink Current vs. Temperature

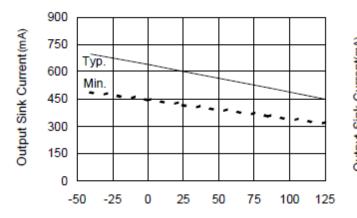

Figure 18B. Output Source Current vs. Supply Current

Figure 19B. Output Sink Current vs. Supply Voltage

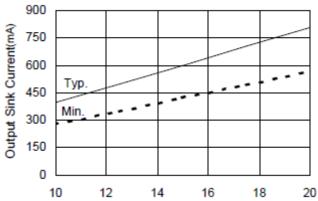

## Package Details: 8-Lead SOIC

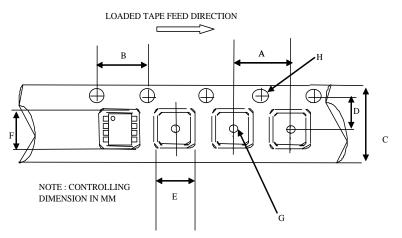

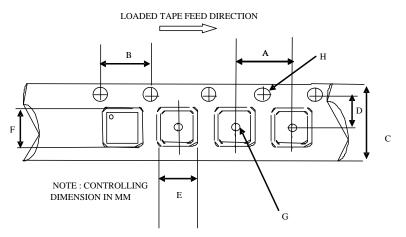

# Tape and Reel Details: 8-Lead SOIC

#### CARRIER TAPE DIMENSION FOR 8SOICN

|      | Metric |       | Imp   | erial |

|------|--------|-------|-------|-------|

| Code | Min    | Max   | Min   | Max   |

| A    | 7.90   | 8.10  | 0.311 | 0.318 |

| В    | 3.90   | 4.10  | 0.153 | 0.161 |

| С    | 11.70  | 12.30 | 0.46  | 0.484 |

| D    | 5.45   | 5.55  | 0.214 | 0.218 |

| E    | 6.30   | 6.50  | 0.248 | 0.255 |

| F    | 5.10   | 5.30  | 0.200 | 0.208 |

| G    | 1.50   | n/a   | 0.059 | n/a   |

| Н    | 1.50   | 1.60  | 0.059 | 0.062 |

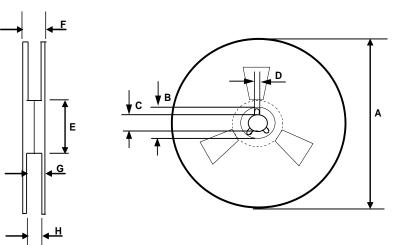

#### REEL DIMENSIONS FOR 8SOICN

|                       | Metric |        | Imperial |        |

|-----------------------|--------|--------|----------|--------|

| Code                  | Min    | Max    | Min      | Max    |

| A                     | 329.60 | 330.25 | 12.976   | 13.001 |

| В                     | 20.95  | 21.45  | 0.824    | 0.844  |

| С                     | 12.80  | 13.20  | 0.503    | 0.519  |

| D                     | 1.95   | 2.45   | 0.767    | 0.096  |

| B<br>C<br>D<br>H<br>F | 98.00  | 102.00 | 3.858    | 4.015  |

|                       | n/a    | 18.40  | n/a      | 0.724  |

| G<br>H                | 14.50  | 17.10  | 0.570    | 0.673  |

| Н                     | 12.40  | 14.40  | 0.488    | 0.566  |

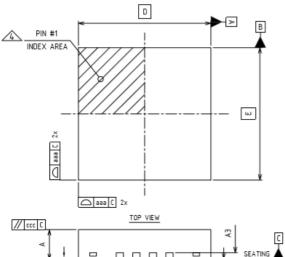

# Package Details: 14-Lead MLPQ 4x4

NOTE:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-2009.

- 2. All dimensions are in millimeters.

- 3. N is the total number of terminals.

- 4. The location of the marked terminal #1 identifier is within the hatched area.

- 5. ND and NE refer to the number of terminals on each D and E side respectively.

- Dimension b applies to the metalized terminal and is measured between 0.15mm and 0.30mm from the terminal tip. If the terminal has a radius on the other end of it, dimension b should not be measured in that radius area.

Coplanarity applies to the terminals and all other bottom surface metalization.

|                     | Dimension Table |          |         |   |  |

|---------------------|-----------------|----------|---------|---|--|

| Thickness<br>Symbol | V               |          | NOTE    |   |  |

| "nbol               | MINIMUM         | NOMINAL  | MAXIMUM |   |  |

| A                   | 0.80            | 0.90     | 1.00    |   |  |

| A1                  | 0.00            | 0.02     | 0.05    |   |  |

| A3                  |                 | 0.20 Ref |         |   |  |

| b                   | 0.18            | 0.25     | 0.30    | 6 |  |

| D                   |                 | 4.00 BSC |         |   |  |

| E                   |                 | 4.00 BSC |         |   |  |

| e                   |                 | 0.50 BSC |         |   |  |

| D2                  | 1.725           | 1.875    | 1.975   |   |  |

| E2                  | 1.725           | 1.875    | 1.975   |   |  |

| к                   | 0.20            |          |         |   |  |

| L                   | 0.25            | 0.35     | 0.45    |   |  |

| aaa                 |                 | 0.05     |         |   |  |

| bbb                 |                 | 0.10     |         |   |  |

| CCC                 |                 | 0.10     |         |   |  |

| ddd                 | 0.05            |          |         |   |  |

| eee                 | 0.08            |          |         |   |  |

| N                   | 14              |          |         | 3 |  |

| ND                  | SEE FIGURE      |          |         | 5 |  |

| NE                  |                 |          |         | , |  |

| NOTES               |                 | 1, 2     |         |   |  |

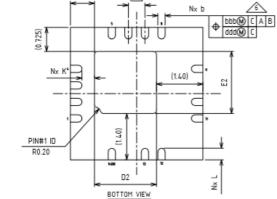

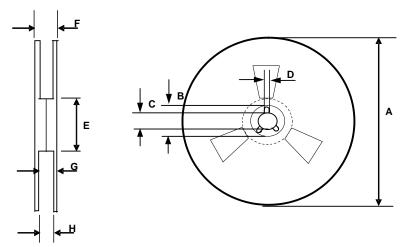

# Tape and Reel Details: 14-Lead MLPQ 4x4

CARRIER TAPE DIMENSION FOR MLPQ4x4

|      | М     | etric | Im    | perial |

|------|-------|-------|-------|--------|

| Code | Min   | Max   | Min   | Max    |

| А    | 7.90  | 8.10  | 0.311 | 0.358  |

| В    | 3.90  | 4.10  | 0.153 | 0.161  |

| С    | 11.70 | 12.30 | 0.461 | 0.484  |

| D    | 5.45  | 5.55  | 0.215 | 0.219  |

| E    | 4.25  | 4.45  | 0.168 | 0.176  |

| F    | 4.25  | 4.45  | 0.168 | 0.176  |

| G    | 1.50  | n/a   | 0.069 | n/a    |

| Н    | 1.50  | 1.60  | 0.069 | 0.063  |

| REEL D | MENSIONS FOR MLPQ4x4 |

|--------|----------------------|

|        |                      |

|      | Metric |        | Imperial |        |

|------|--------|--------|----------|--------|

| Code | Min    | Max    | Min      | Max    |

| А    | 329.60 | 330.25 | 12.976   | 13.001 |

| В    | 20.95  | 21.45  | 0.824    | 0.844  |

| С    | 12.80  | 13.20  | 0.503    | 0.519  |

| D    | 1.95   | 2.45   | 0.767    | 0.096  |

| E    | 98.00  | 102.00 | 3.858    | 4.015  |

| F    | n/a    | 18.40  | n/a      | 0.724  |

| G    | 14.50  | 17.10  | 0.570    | 0.673  |

| Н    | 12.40  | 14.40  | 0.488    | 0.566  |

International **IOR** Rectifier AN INFINEON TECHNOLOGIES COMPAN

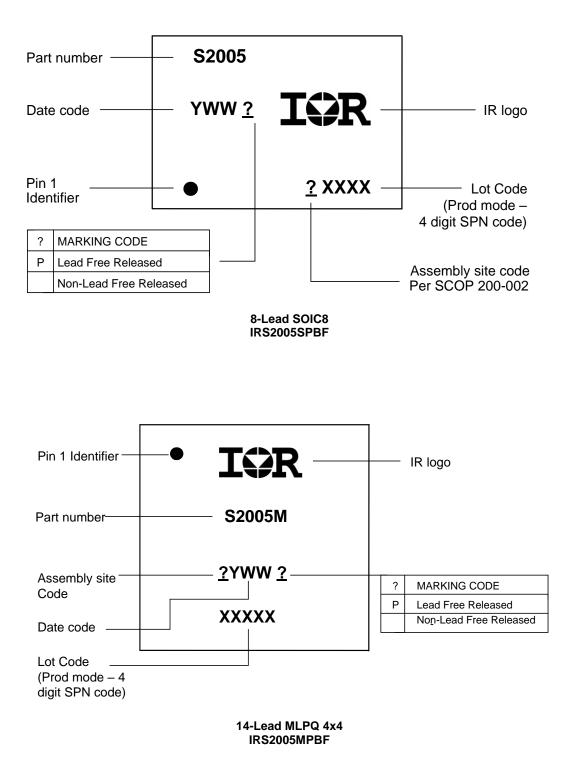

## **Part Marking Information**

#### **Qualification Information<sup>+</sup>**

| Qualification Level        |                  |                          | Industrial <sup>+†</sup>                                                                                                                                            |  |  |

|----------------------------|------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                            |                  | qualification. IR's Cons | Comments: This family of ICs has passed JEDEC's Industrial qualification. IR's Consumer qualification level is granted by extension of the higher Industrial level. |  |  |

| Moisture Sensitivity Level |                  | 8 Lead SOIC              | MSL2 <sup>†††</sup> , 260°C<br>(per IPC/JEDEC J-STD-020)                                                                                                            |  |  |

|                            |                  | 14-Lead MLPQ 4x4         |                                                                                                                                                                     |  |  |

| ESD                        | Human Body Model | (per JEDE)               | Class 2<br>(per JEDEC standard JESD22-A114)                                                                                                                         |  |  |

|                            | Machine Model    | (per EIA/JEDE            | Class A<br>(per EIA/JEDEC standard EIA/JESD22-A115)                                                                                                                 |  |  |

| IC Latch-Up Test           |                  |                          | Class I<br>(per JESD78)                                                                                                                                             |  |  |

| RoHS Compliant             |                  |                          | Yes                                                                                                                                                                 |  |  |

Qualification standards can be found at International Rectifier's web site http://www.irf.com/

† †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

Higher MSL ratings may be available for the specific package types listed here. Please contact your International ††† Rectifier sales representative for further information.