# Integrated MCU Power Solution for C2000<sup>™</sup> Microcontrollers

Check for Samples: TPS75005

## **FEATURES**

- Optimized to Supply TI's C2000 MCU Series: F2833x ( DELFINO<sup>™</sup>), F2823x, F281x, and F280x/F2801x

- **Dual 500-mA Voltage Regulators with** • Dedicated Supply Voltage Supervisors (SVSs)

- **One Auxiliary SVS** •

- LDO1 and SVS1 for 1.8 V/1.9 V (Selectable): • ±5% Specified with PG

- LDO2 and SVS2 for 3.3 V: ٠ ±5% Specified with PG

- Input Voltage Range: 3.75 V to 6.5 V .

- Independent Soft-Start for LDO1 and LDO2

- Preset Power-Up and Power-Down Sequencing for C2000 MCUs

- Supports C2000 MCU Transient with Two . 10-µF Ceramic Output Capacitors

- 5-mm × 5-mm QFN Package (1)

## APPLICATIONS

- **C2000 MCUs**

- **DSPs/FPGAs/ASICs**

- 16-Pin HTSSOP package can be supported but minimum (1)quantity may be required; contact sales representative.

## DESCRIPTION

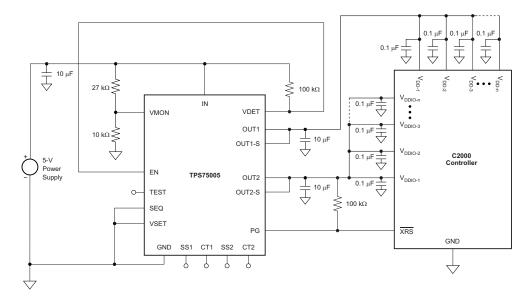

The TPS75005 is a complete power management solution for Texas Instruments' C2000 real-time microcontrollers and other DSP, FPGA, and ASIC MCUs. The device has been tested with and meets TI's F2833x (DELFINO), F2823x, F281x, and F280x/F2801x power requirements.

All of these C2000 controllers require ±5% power-rail accuracy. With the combination of high-accuracy, low-dropout regulators (LDOs) and dedicated SVSs, the device allows for a ±5% power supply to the C2000 with a power-good (PG) signal. (For more details, see Application Report SBVA032, LDO+SVS Combined Accuracy.)

Two power outputs are controlled by an integrated sequencer circuit. A single EN logic input signal makes sure that the power-up and power-down requirements of the C2000 controllers are met. The sequencer includes a soft-start for both LDOs to avoid inrush current. A third rail monitor is provided for general-purpose monitoring (for example, to monitor input voltage).

A quick-start guide (SBVA030) is available with stepby-step instructions for connection to a C2000 controller.

The TPS75005 is available in a 5-mm × 5-mm QFN package, yielding a compact total solution size with high power dissipation capability.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of ÆÀ Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. C2000, DELFINO are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

# **TPS75005**

### SBVS144C -NOVEMBER 2011-REVISED APRIL 2012

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT                 | V <sub>OUT1</sub>               | V <sub>OUT2</sub>              | V <sub>SVS2</sub> | V <sub>SVS3</sub> |                             |         |  |

|-------------------------|---------------------------------|--------------------------------|-------------------|-------------------|-----------------------------|---------|--|

|                         | VSET = L VSE                    | T = H                          | VSET = H          | VSET = L          | 0.004                       |         |  |

| TPS75005 <sup>(2)</sup> |                                 | 3.333 V<br>19 V (101%)<br>01%) | 1.764 V<br>(98%)  | 1.862 V<br>(98%)  | 3.234<br>(98%)              | 1.206 V |  |

| TPS75005ADJ             | Adjustable,<br>greater than 1.2 |                                | ,                 | stable,<br>VOUT1  | Adjustable,<br>97% of VOUT2 |         |  |

## VOLTAGE INFORMATION<sup>(1)</sup>

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

(2) VOUT1 and VSVS1 are selectable by VSET pin logic with the TPS75005.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

At  $T_{.1} = -40^{\circ}$ C to  $+125^{\circ}$ C (unless otherwise noted).

|                                  |                                                         | VA   | UNIT                                 |    |

|----------------------------------|---------------------------------------------------------|------|--------------------------------------|----|

|                                  |                                                         | MIN  | MAX                                  |    |

|                                  | IN, OUT1, OUT2, VMON, VSET, SEQ, OUT1_S, OUT2_S         | -0.3 | +7.0                                 | V  |

| Voltage <sup>(2)</sup>           | CT1 CT2, SS1, SS2                                       | -0.3 | +3.6                                 | V  |

|                                  | EN, VDET, PG, TEST                                      | -0.3 | V <sub>IN</sub> + 0.3 <sup>(3)</sup> | V  |

| Output current                   |                                                         | Ir   | nternally limited <sup>(4)</sup>     |    |

| Temperature                      | Storage, T <sub>stg</sub>                               | -55  | +150                                 | °C |

| Electrostatic                    | Human body model (HBM) QSS 009-105 (JESD22-A114A)       |      | 2                                    | kV |

| discharge ratings <sup>(5)</sup> | Charge device model (CDM) QSS 009-147 (JESD22-C101B.01) |      | 500                                  | V  |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

(2) All voltages are with respect to network ground terminal.

(3) Absolute maximum rating of these pins is  $V_{IN}$  + 0.3 V or + 7.0 V, whichever is smaller.

(4) See Electrical Characteristics.

(5) ESD testing is performed according to the respective JESD22 JEDEC standard.

## THERMAL INFORMATION

|                         |                                                             | TPS75005                 |       |

|-------------------------|-------------------------------------------------------------|--------------------------|-------|

|                         | THERMAL METRIC <sup>(1)(2)</sup>                            | RGW (QFN) <sup>(3)</sup> | UNITS |

|                         |                                                             | 20 PINS                  |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(4)</sup>       | 35.1                     |       |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance <sup>(5)</sup>    | 31.9                     |       |

| θ <sub>JB</sub>         | Junction-to-board thermal resistance <sup>(6)</sup>         | 14.4                     | °C/W  |

| ΨJT                     | Junction-to-top characterization parameter <sup>(7)</sup>   | 0.4                      | °C/W  |

| Ψјв                     | Junction-to-board characterization parameter <sup>(8)</sup> | 14.5                     |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(9)</sup> | 3.7                      |       |

- For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953A.

- For thermal estimates of this device based on PCB copper area, see the TI PCB Thermal Calculator. (2)

- Thermal data for the RGW package is derived by thermal simulations based on JEDEC-standard methodology as specified in the (3) JESD51 series. The following assumptions are used in the simulations:

- (a) RGW: The exposed pad is connected to the PCB ground layer through a 4 x 4 thermal via array.

- (b) Each of top and bottom copper layers has a dedicated pattern for 4% copper coverage.

- (c) These data were generated with only a single device at the center of a JEDEC high-K (2s2p) board with 3in × 3in copper area. To understand the effects of the copper area on thermal performance, refer to the Power Dissipation and Estimating Junction Temperature sections.

- (4) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the top of the package. No specific JEDEC-(5) standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (6) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data to obtain  $\theta_{JA}$  using a procedure described in JESD51-2a (sections 6 and 7).

- (8) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data to obtain  $\theta_{JA}$  using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific

- (9)JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

SBVS144C -NOVEMBER 2011-REVISED APRIL 2012

www.ti.com

## **ELECTRICAL CHARACTERISTICS**

Over operating temperature range of  $T_J = -40$  °C to +125 °C, with 4.0 V  $\leq V_{IN} \leq 6.5$  V,  $V_{OUT1_S} = V_{OUT1}$ ,  $V_{OUT2_S} = V_{OUT2}$ ,  $V_{EN} = V_{IN}$ , CT1 = OPEN, CT2 = OPEN, SS1 = OPEN, SS2 = OPEN, PG = pulled up to  $V_{OUT2}$  through 100-k $\Omega$  resistor, TEST = pulled up to  $V_{OUT2}$  through 100-k $\Omega$  resistor,  $V_{DET}$  = pulled up to  $V_{IN}$  through 100-k $\Omega$  resistor,  $V_{OUT1} = 10 \ \mu$ F,  $C_{OUT2} = 10 \ \mu$ F,  $R_{OUT1} = 1 \ k\Omega$  to GND<sup>(1)</sup>,  $R_{OUT2} = 1 \ k\Omega$  to GND<sup>(1)</sup>, and  $V_{SET} = SEQ = GND$ , unless otherwise noted.

|                                     | PARAMETER                                    | TEST CONDITIONS                                                                                                       | MIN            | TYP             | MAX             | UNIT  |

|-------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----------------|-------|

| COMPLETE DE                         | VICE                                         |                                                                                                                       |                |                 |                 |       |

| V <sub>IN</sub>                     | Input voltage range                          |                                                                                                                       | 3.75           |                 | 6.5             | V     |

| I <sub>GND</sub>                    | GND current                                  | $I_{OUT1} = I_{OUT2} = 500 \text{ mA}, V_{SET} = V_{IN} \text{ or GND}$                                               |                |                 | 500             | μA    |

| l <sub>Q</sub>                      | Quiescent GND current                        | I <sub>OUT1</sub> = I <sub>OUT2</sub> = 0 A, V <sub>SET</sub> = V <sub>IN</sub> or GND                                |                | 175             |                 | μΑ    |

| I <sub>SHDN</sub>                   | Shutdown ground current                      | V <sub>IN</sub> = 6.5 V, no pull-up resistors at PG, VDET, TEST pins                                                  |                | 17              | 40              | μA    |

| V <sub>SVS3</sub>                   | VMON supervisor threshold                    |                                                                                                                       | 1.181          | 1.206           | 1.230           | V     |

| ΔV <sub>SVS3</sub>                  | VMON supervisor hysteresis                   | Relative to V <sub>SVS3</sub>                                                                                         |                | + 4             |                 | mV    |

| V <sub>IH</sub>                     | High-level input voltage                     | For EN, SEQ, and VSET pins                                                                                            | 2.0            |                 |                 | V     |

| VIL                                 | Low-level input voltage                      | For EN, SEQ, and VSET pins                                                                                            | 0              |                 | 0.8             | V     |

|                                     |                                              | For SEQ and VSET pins, V <sub>SEQ</sub> = V <sub>SET</sub> = 2.0 V                                                    | - 0.1          |                 | 0.1             |       |

| I <sub>IN</sub>                     | Logic input current                          | For EN pin                                                                                                            | - 0.2          |                 | 0.2             | μA    |

| V <sub>OL</sub>                     | Low-level output voltage                     | Load current 1 mA into PG, TEST, and VDET pins force V <sub>OUT1</sub> < V <sub>SVS1</sub> , V <sub>MON</sub> = 0.5 V |                |                 | 0.3             | V     |

| 11/1 0                              |                                              | Releasing: V <sub>IN</sub> rising                                                                                     | 3.4            |                 | 3.75            | V     |

| UVLO                                | Undervoltage lock out                        | Locking: hysteresis, V <sub>IN</sub> falling                                                                          |                | 60              |                 | mV    |

| -                                   |                                              | Temperature rising to shutdown                                                                                        |                | +165            |                 | °C    |

| T <sub>TSD</sub>                    | Thermal shutdown temperature                 | Hysteresis, temperature falling to release shutdown                                                                   |                | +145            |                 | °C    |

| t <sub>DVS</sub>                    | VSET transition time <sup>(2)</sup>          |                                                                                                                       |                | 40              |                 | μs    |

| LDO1 (1.8 V or                      | 1.9 V Selectable by VSET Pin)                | l                                                                                                                     | 1              |                 | 1               |       |

| .,                                  |                                              | $V_{SET}$ = H, 4.0 V ≤ $V_{IN}$ ≤ 6.5 V, 1 mA ≤ $I_{OUT1}$ ≤ 500 mA                                                   | 1.881<br>(99%) | 1.919<br>(101%) | 1.957<br>(103%) | V     |

| V <sub>OUT1</sub>                   | LDO1 output voltage accuracy                 | $V_{SET}$ = L, 4.0 V ≤ $V_{IN}$ ≤ 6.5 V, 1 mA ≤ $I_{OUT1}$ ≤ 500 mA                                                   | 1.782<br>(99%) | 1.818<br>(101%) | 1.854<br>(103%) | V     |

| $\Delta V_{OUT1} / \Delta V_{IN}$   | LDO1 line regulation                         | $4.0 \text{ V} \le \text{V}_{\text{IN}} \le 6.5 \text{ V}, \text{ I}_{\text{OUT1}} = 1 \text{ mA}$                    |                |                 | 122             | μV/V  |

| $\Delta V_{OUT1} / \Delta I_{OUT1}$ | LDO1 load regulation                         | $1 \text{ mA} \le I_{\text{OUT1}} \le 500 \text{ mA}$                                                                 |                |                 | 29              | μV/mA |

| I <sub>CL1</sub>                    | LDO1 current limit                           | V <sub>OUT1</sub> = 0.9 × V <sub>OUT1(NOM)</sub> , 4.5 V < V <sub>IN</sub> < 6.5 V                                    |                | 900             |                 | mA    |

|                                     |                                              | $V_{SET}$ = H, 4.0 V ≤ $V_{IN}$ ≤ 6.5 V<br>Force $V_{OUT1}$ (decreasing)                                              | 1.805<br>(95%) |                 | 1.881<br>(99%)  | V     |

| V <sub>SVS1</sub>                   | LDO1 supervisor threshold                    | $V_{SET}$ = L, 4.0 V ≤ V <sub>IN</sub> ≤ 6.5 V<br>Force V <sub>OUT1</sub> (decreasing)                                | 1.710<br>(95%) |                 | 1.782<br>(99%)  | V     |

| ΔV <sub>SVS1</sub>                  | LDO1 supervisor hysteresis                   | Relative to V <sub>SVS1</sub>                                                                                         |                | 0.3             |                 | %     |

| t <sub>W(SVS1)</sub>                | LDO1 supervisor minimum pulse width to Sense | $V_{OUT1} = 100\% \rightarrow 90\% \rightarrow 100\%$                                                                 |                | 3.3             |                 | μs    |

| t <sub>D(SVS1)</sub>                | LDO1 supervisor delay time                   | From (V <sub>OUT1</sub> > V <sub>SVS1</sub> ) event to PG $\uparrow$ with SEQ = H, C <sub>CT1</sub> = (open)          |                | 33              |                 | μs    |

| I <sub>CT1</sub>                    | CT1 charging current                         | Any capacitor connected between CT1 and GND, 0.2 V $\leq$ V <sub>CT1</sub> $\leq$ 1.0 V                               | 0.3            |                 | 1               | μA    |

| V <sub>CT1</sub>                    | CT1 timeout threshold                        | Any capacitor connected between CT1 and GND                                                                           | 1.05           | 1.206           | 1.35            | V     |

| t <sub>SS1</sub>                    | LDO1 soft-start time                         | V <sub>OUT1</sub> waveform from 0% to 95%, C <sub>SS1</sub> = (open)                                                  |                | 260             |                 | μs    |

| I <sub>SS1</sub>                    | SS1 charging current                         | Any capacitor connected between SS1 and GND, 0.2 V $\leq$ V_{SS1} $\leq$ 1.0 V                                        | 0.3            |                 | 0.8             | μA    |

| R <sub>PD1</sub>                    | LDO1 active pull-down ON resistance          | EN = GND, V <sub>OUT1</sub> = 1.8 V                                                                                   | 225            | 360             | 475             | Ω     |

| V <sub>DOWN1</sub>                  | LDO1 power-down detector<br>accuracy         |                                                                                                                       |                | 0.3             |                 | V     |

(1) These 1-k $\Omega$  resistors are disconnected when the test conditions specify an output current of LDO1 or LDO2.

(2) With recommended usage of TPS75005, VSET does not need to be controlled on-the-fly. VSET transition time varies significantly depending on application conditions. Stated typical value is almost the fastest transition.

## **ELECTRICAL CHARACTERISTICS (continued)**

Over operating temperature range of  $T_J = -40$  °C to +125 °C, with 4.0 V  $\leq V_{IN} \leq 6.5$  V,  $V_{OUT1_S} = V_{OUT1}$ ,  $V_{OUT2_S} = V_{OUT2}$ ,  $V_{EN} = V_{IN}$ , CT1 = OPEN, CT2 = OPEN, SS1 = OPEN, SS2 = OPEN, PG = pulled up to  $V_{OUT2}$  through 100-k $\Omega$  resistor, TEST = pulled up to  $V_{OUT2}$  through 100-k $\Omega$  resistor,  $V_{DET}$  = pulled up to  $V_{IN}$  through 100-k $\Omega$  resistor,  $V_{OUT1} = 10 \ \mu$ F,  $C_{OUT2} = 10 \ \mu$ F,  $R_{OUT1} = 1 \ k\Omega$  to GND<sup>(1)</sup>,  $R_{OUT2} = 1 \ k\Omega$  to GND<sup>(1)</sup>, and  $V_{SET} = SEQ = GND$ , unless otherwise noted.

| PARAMETER                                      |                                              | TEST CONDITIONS                                                                                              | MIN            | TYP             | MAX             | UNIT  |

|------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----------------|-------|

| LDO2 (3.3 V)                                   |                                              |                                                                                                              |                |                 |                 |       |

| V <sub>OUT2</sub> LDO2 output voltage accuracy |                                              | 4.0 V $\leq$ V <sub>IN</sub> $\leq$ 6.5 V, 1mA $\leq$ I <sub>OUT2</sub> $\leq$ 500 mA                        | 3.267<br>(99%) | 3.333<br>(101%) | 3.399<br>(103%) | V     |

| $\Delta V_{OUT2} / \Delta V_{IN}$              | LDO2 line regulation                         | $4.0 \text{ V} \le \text{V}_{\text{IN}} \le 6.5 \text{ V}, \text{ I}_{\text{OUT2}} = 1 \text{ mA}$           |                |                 | 461             | μV/V  |

| $\Delta V_{OUT2} / \Delta I_{OUT1}$            | LDO2 load regulation                         | 1 mA ≤ I <sub>OUT2</sub> ≤ 500 mA                                                                            |                |                 | 50              | µV/mA |

| I <sub>CL2</sub>                               | LDO2 current limit                           | $V_{OUT2} = 0.9 \times V_{OUT2(NOM)}, 4.5 \text{ V} < V_{IN} < 6.5 \text{ V}$                                |                | 900             |                 | mA    |

| V <sub>SVS2</sub>                              | LDO2 supervisor threshold                    | 4.0 V $\leq V_{IN} \leq 6.5$ V<br>force V <sub>OUT2</sub> (decreasing)                                       | 3.135<br>(95%) |                 | 3.267<br>(99%)  | V     |

| $\Delta V_{SVS2}$                              | LDO2 supervisor hysteresis                   | Relative to V <sub>SVS2</sub>                                                                                |                | 0.3             |                 | %     |

| t <sub>W(SVS2)</sub>                           | LDO2 supervisor minimum pulse width to sense | $V_{OUT2} = 100\% \rightarrow 90\% \rightarrow 100\%$                                                        |                | 3.3             |                 | μs    |

| t <sub>D(SVS2)</sub>                           | LDO2 supervisor delay time                   | From (V <sub>OUT2</sub> > V <sub>SVS2</sub> ) event to PG $\uparrow$ with SEQ = L, C <sub>CT2</sub> = (open) |                | 33              |                 | μs    |

| I <sub>CT2</sub>                               | CT2 charging current                         | Any capacitor connected between CT2 and GND, 0.2 V $\leq$ V_{CT2} $\leq$ 1.0 V                               | 0.3            |                 | 1               | μA    |

| V <sub>CT2</sub>                               | CT2 timeout threshold                        | Any capacitor connected between CT2 and GND                                                                  | 1.05           | 1.206           | 1.35            | V     |

| t <sub>SS2</sub>                               | LDO2 soft-start time                         | V <sub>OUT2</sub> waveform from 0% to 95%, C <sub>SS2</sub> = (open)                                         |                | 260             |                 | μs    |

| I <sub>SS2</sub>                               | SS2 charging current                         | Any capacitor connected between SS2 and GND, 0.2 V $\leq V_{SS2} \leq$ 1.0 V                                 | 0.3            |                 | 0.8             | μA    |

| R <sub>PD2</sub>                               | LDO2 active pull-down ON resistance          | EN = L, V <sub>OUT2</sub> = 3.3 V                                                                            | 225            | 360             | 475             | Ω     |

| V <sub>DOWN2</sub>                             | LDO2 power-down detector accuracy            |                                                                                                              |                | 0.3             |                 | V     |

SBVS144C -NOVEMBER 2011-REVISED APRIL 2012

www.ti.com

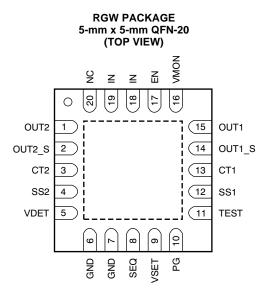

## **PIN CONFIGURATION**

### **PIN DESCRIPTIONS**

| PIN    |               |                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME   | RGW<br>QFN-20 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| CT1 13 |               | SVS1 internal-power-good delay setting. Leave this pin open for the default delay setting or connect capacitor between this node and GND to program the delay. <b>Do not connect a regular oscilloscope probe for monitoring.</b>                                                                                                                                                                  |  |  |  |  |  |

| CT2    | 3             | SVS2 internal-power-good delay setting. Leave this pin open for the default delay setting or connect a capacitor between this pin and GND to program the delay. <b>Do not connect a regular oscilloscope probe for monitoring.</b>                                                                                                                                                                 |  |  |  |  |  |

| EN     | 17            | Enable inputs. Logic-H input to this pin triggers power-up sequence. Logic-L triggers power-down sequence.<br>NOTE: The sequencing logic will automatically prevent powering up until the TPS75005 pulls the output rails to GNE<br>This ensures a proper startup every time.                                                                                                                      |  |  |  |  |  |

| GND    | 6, 7          | Ground. Tie these pins to the thermal pad and maximize the copper in this area for optimal performance.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| IN     | 18, 19        | Power supply to the device. Connect a 10-µF X5R or X7R dielectric capacitor between IN and GND close to the device.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| NC     | 20            | Not internally connected. This pin can be either tied to IN or GND to simplify layout.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| OUT1   | 15            | LDO1 output voltage. Connect a 10-µF X5R or X7R capacitor between this pin and ground close to the device.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| OUT1_S | 14            | LDO1 output voltage sense input. Connect directly to output capacitor close to pin 15.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| OUT2   | 1             | LDO2 output voltage. Connect a 10-µF X5R or X7R capacitor between this pin and ground close to the device.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| OUT2_S | 2             | LDO2 output voltage sense input. Connect directly to output capacitor close to pin 1.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| PG     | 10            | Power-Good output. This is an open-drain output terminal and a pull-up resistor is required. The typical connection is 100 kΩ to OUT2. When $V_{OUT1} > V_{SVS1}$ and $V_{OUT2} > V_{SVS2}$ , this pin outputs logic-H.                                                                                                                                                                            |  |  |  |  |  |

| SEQ    | 8             | Sequence select pin. Logic-L input to this pin powers-up two LDOs in this order: LDO1 first, and then LDO2. Logic-L also powers-down LDO2 first, and then LDO1.<br>Logic-H to this pin powers-up two LDOs in this order: LDO2 first, and then LDO1. Logic-H also powers-down LDO1 first, and then LDO2.<br>SEQ should be hard-wired to either IN or GND depending on the sequencing mode required. |  |  |  |  |  |

| SS1    | 12            | LDO1 soft-start setting. Leave this pin open for the default ramp up setting or connect a capacitor, 10 nF or less, between this pin and GND to program V <sub>OUT1</sub> ramp-up slew rate. <b>Do not connect a regular oscilloscope probe for monitoring.</b>                                                                                                                                    |  |  |  |  |  |

| SS2    | 4             | LDO2 soft-start setting. Leave this pin open for the default ramp up setting or connect a capacitor between this pin and GND to program $V_{OUT2}$ ramp-up slew rate. <b>Do not connect a regular oscilloscope probe for monitoring.</b>                                                                                                                                                           |  |  |  |  |  |

| TEST   | 11            | Test pin for test and debugging purposes only. Do not connect this pin.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| VDET   | 5             | Output of SVS3. This is an open-drain output terminal and a pull-up resistor is required. The typical connection is 100 k $\Omega$ to IN. When V <sub>MON</sub> > V <sub>SVS3</sub> , VDET outputs logic-H; when V <sub>MON</sub> < V <sub>SVS3</sub> , VDET is logic-L.                                                                                                                           |  |  |  |  |  |

| VMON   | 16            | Monitor input voltage of third voltage detector. A resistor divider on this pin between the voltage rail to be monitored and GND sets the threshold voltage. The detect threshold is 1.206 V.                                                                                                                                                                                                      |  |  |  |  |  |

| VSET   | 9             | LDO1 output voltage setting. Logic-H input sets V <sub>OUT1</sub> to 1.9 V. Logic-L sets V <sub>OUT1</sub> to 1.8 V. It is recommended t this pin either to IN or GND depending on voltage required for the application.                                                                                                                                                                           |  |  |  |  |  |

| Therm  | nal pad       | Pad for thermal dissipation. Tie this pin to GND with vias through the board to internal heat spreading layers as well as the back side of the PCB.                                                                                                                                                                                                                                                |  |  |  |  |  |

6

Copyright © 2011–2012, Texas Instruments Incorporated

TSD

CL1

CL2

GND

$\downarrow$

C

$\bigcirc$

$\cap$

SBVS144C - NOVEMBER 2011 - REVISED APRIL 2012

## www.ti.com

SS2 | SS1

**T**-

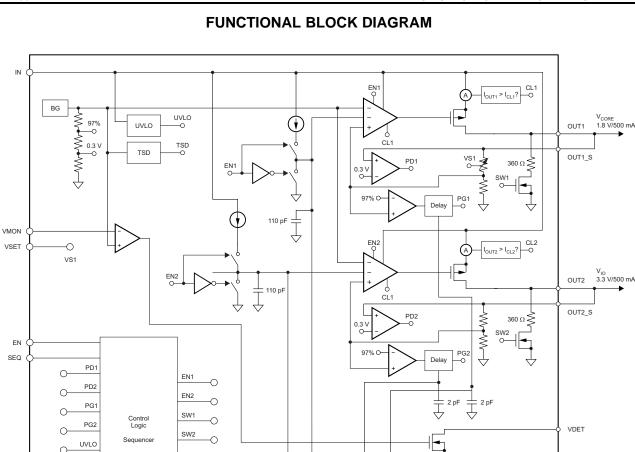

Figure 1. Functional Block Diagram

Ē

CT2 CT1

Ī-Ī

(Optional)

TEST

PG

$\forall$

Ą

╟╾

SBVS144C -NOVEMBER 2011-REVISED APRIL 2012

www.ti.com

G00<sup>-</sup>

G003

G005

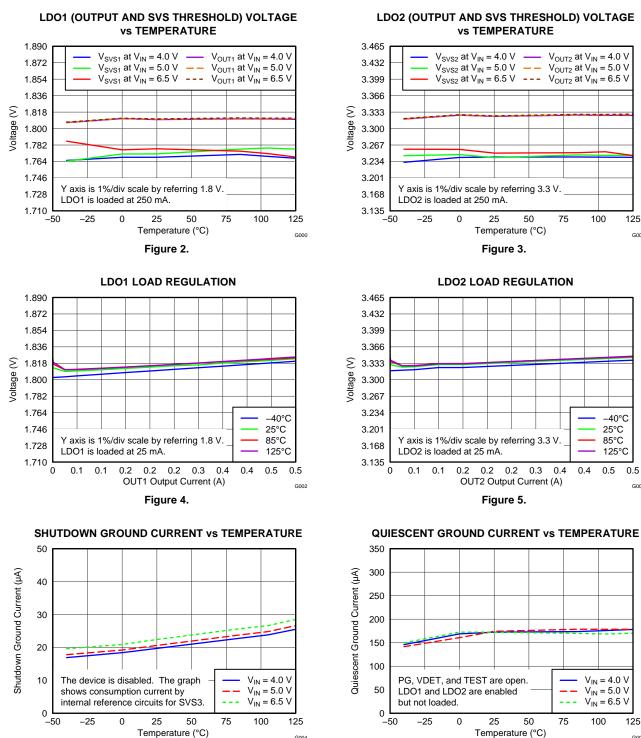

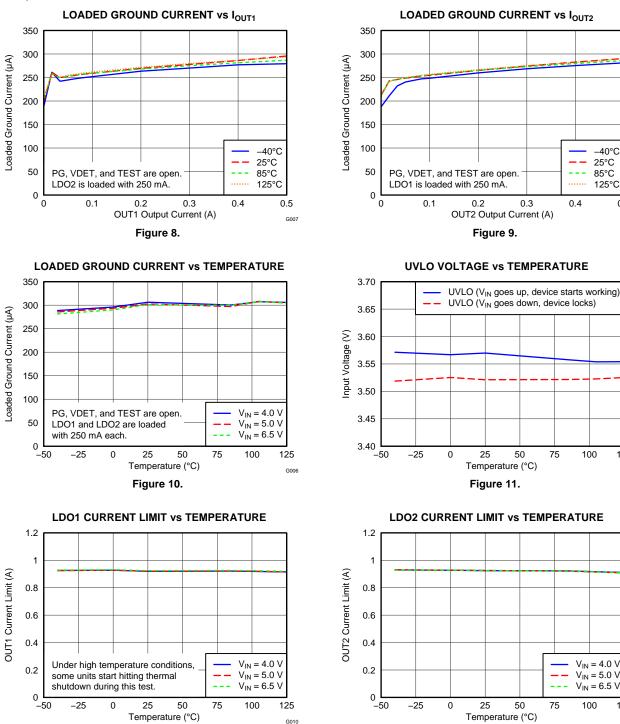

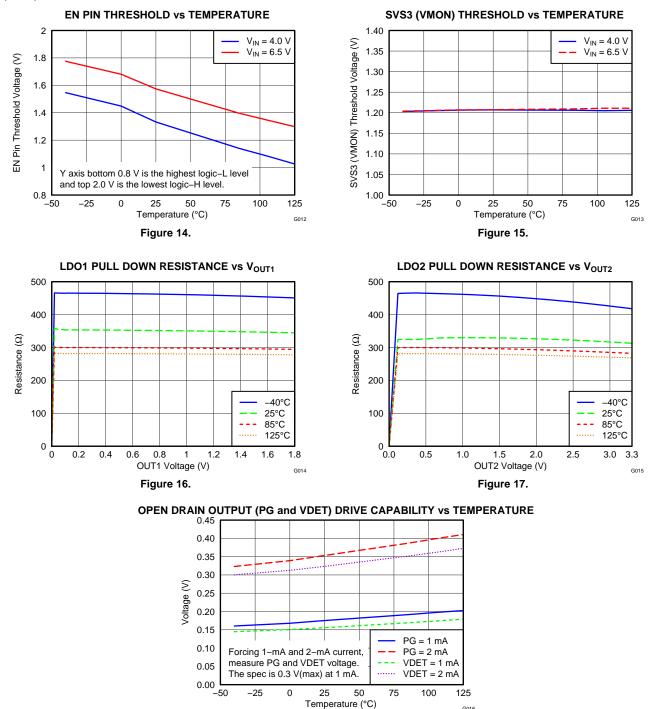

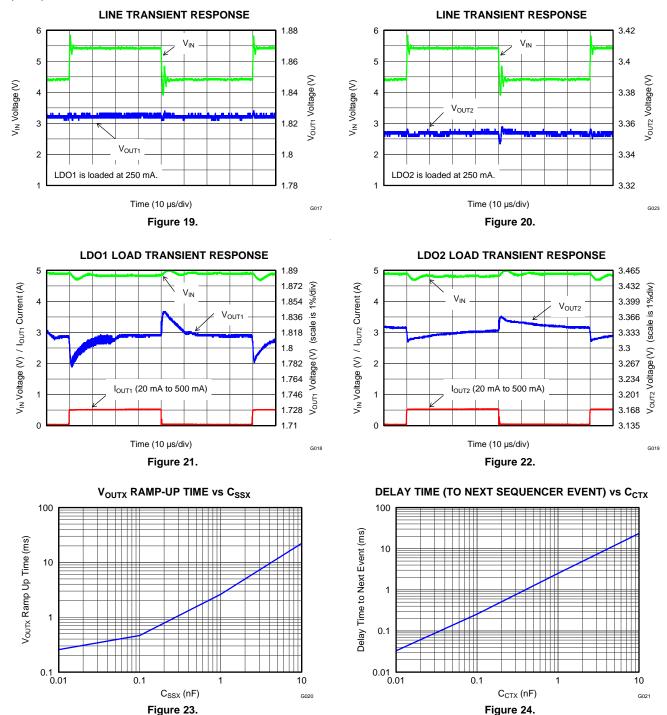

## **TYPICAL CHARACTERISTICS**

At  $T_J = +25^{\circ}C$ ,  $V_{IN} = 5$  V,  $V_{(EN)} = V_{IN}$ ,  $C_{IN} = 22 \ \mu$ F,  $C_{OUT1} = C_{OUT2} = 10 \ \mu$ F,  $C_{(SS1)} = C_{(SS2)} = C_{(CT1)} = C_{(CT2)} = (open)$ ,  $V_{SET} = 0$  V,  $V_{SNS1} = V_{OUT1}$ ,  $V_{SNS2} = V_{OUT2}$ , PG pin pulled up to  $V_{OUT2}$  with 100-k $\Omega$  pull-up resistor, and VDET pin pulled up to VIN with 100-k $\Omega$ kΩ pull-up resistor, unless otherwise noted.

8

Figure 6.

Figure 7.

G004

-40°C

125°C

0.5

G008

25°C

- - -85°C

0.4

100

$V_{IN} = 4.0 V$

V<sub>IN</sub> = 5.0 V

V<sub>IN</sub> = 6.5 V

125

G011

100

125

G009

#### SBVS144C - NOVEMBER 2011 - REVISED APRIL 2012

#### www.ti.com

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = +25^{\circ}C$ ,  $V_{IN} = 5$  V,  $V_{(EN)} = V_{IN}$ ,  $C_{IN} = 22 \ \mu$ F,  $C_{OUT1} = C_{OUT2} = 10 \ \mu$ F,  $C_{(SS1)} = C_{(SS2)} = C_{(CT1)} = C_{(CT2)} =$  (open),  $V_{SET} = 0$  V,  $V_{SNS1} = V_{OUT1}$ ,  $V_{SNS2} = V_{OUT2}$ , PG pin pulled up to  $V_{OUT2}$  with 100-k $\Omega$  pull-up resistor, and VDET pin pulled up to VIN with 100-k $\Omega$  pull-up resistor. kΩ pull-up resistor, unless otherwise noted.

Figure 12.

SBVS144C-NOVEMBER 2011-REVISED APRIL 2012

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = +25^{\circ}C$ ,  $V_{IN} = 5$  V,  $V_{(EN)} = V_{IN}$ ,  $C_{IN} = 22 \ \mu$ F,  $C_{OUT1} = C_{OUT2} = 10 \ \mu$ F,  $C_{(SS1)} = C_{(SS2)} = C_{(CT1)} = C_{(CT2)} = (open)$ ,  $V_{SET} = 0$  V,  $V_{SNS1} = V_{OUT1}$ ,  $V_{SNS2} = V_{OUT2}$ , PG pin pulled up to  $V_{OUT2}$  with 100-k $\Omega$  pull-up resistor, and VDET pin pulled up to VIN with 100-k $\Omega$ kΩ pull-up resistor, unless otherwise noted.

G016

Figure 18.

www.ti.com

#### SBVS144C-NOVEMBER 2011-REVISED APRIL 2012

#### www.ti.com

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = +25^{\circ}$ C,  $V_{IN} = 5$  V,  $V_{(EN)} = V_{IN}$ ,  $C_{IN} = 22 \ \mu$ F,  $C_{OUT1} = C_{OUT2} = 10 \ \mu$ F,  $C_{(SS1)} = C_{(SS2)} = C_{(CT1)} = C_{(CT2)} = (open)$ ,  $V_{SET} = 0$  V,  $V_{SNS1} = V_{OUT1}$ ,  $V_{SNS2} = V_{OUT2}$ , PG pin pulled up to  $V_{OUT2}$  with 100-k $\Omega$  pull-up resistor, and VDET pin pulled up to VIN with 100-k $\Omega$  pull-up resistor, unless otherwise noted.

## **APPLICATION INFORMATION**

## **Design Guidelines**

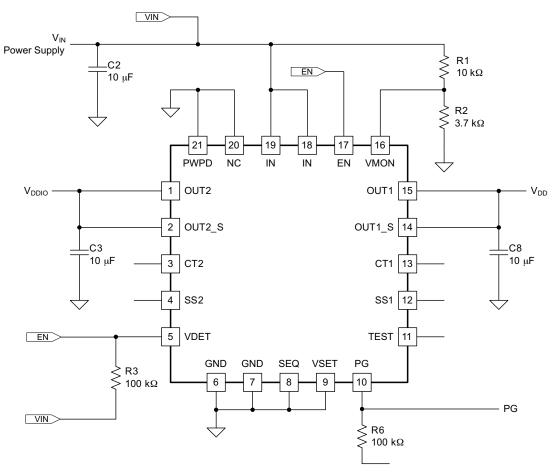

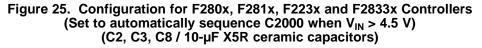

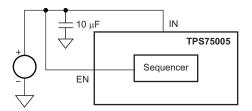

Figure 25 and Figure 26 show a basic schematic and PCB layout for applications using the internal default settings for power-good delay and rise time of the LDO1 and LDO2 outputs at turn on. This configuration is typical for applications involving the targeted C2000 microcontrollers. The unused adjustment pins, CT1, CT2, SS1, and SS2, are left open or floating. Connecting the SEQ and VSET pins to ground selects the turn-on sequence and the output voltage of LDO1. The open-drain outputs at PG and VDET are pulled up to the input voltage through 100-k $\Omega$  resistors. VDET is connected to enable the TPS75005 when the input voltage exceeds the SVS voltage set by resistor divider R1 and R2 to VMON. For highly dynamic loads, like that of the C2000 microcontroller, the input capacitor, C2, and the output capacitors, C3 and C8, are specified to be 10- $\mu$ F, X5R or X7R, 10-V, ceramic capacitors in order to meet transient performance requirements.

**TPS75005**

The PCB layout of Figure 26 shows that the input and output capacitors C2, C3, and C8 are located near the respective pins and interconnected with a wide, low-inductance, ground plane that includes the device ground and the thermal pad ground of the device.

**NOTE** The input capacitor ground is routed under the device package through NC, pin-20.

Figure 26. TPS75005EVM-023 Recommended Layout

The PCB typically consists of four layers, minimum. The top (surface) layer and one internal layer are used for trace/signal routing. One internal layer as well as the bottom layer are devoted to be ground planes that also function as *spreading* planes for dissipating heat away from the TPS75005 device. It is very important for proper function of the device and long-term reliability to conduct heat away from the device. The PowerPAD is soldered to a ground pad on the PCB that conducts heat away from the device through nine plated vias to the spreading planes beneath. The internal spreading layer in this case consists of four square inches of 1-ounce copper, and the bottom layer consists of an equal area of 2-ounce copper. Additional spreading layers should be added, if necessary, to a given application.

## LDO BLOCKS

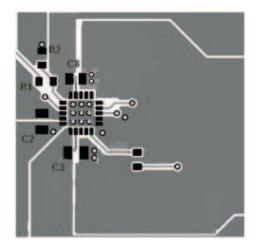

The TPS75005 integrates two high-bandwidth LDOs for powering the  $V_{DD}$  and  $V_{DDIO}$  pins of the C2000 controllers.

#### Input Capacitor

Although an input capacitor is not required for LDO stability, it is recommended to connect a 10-µF capacitor across the input supply near the device. In addition to input capacitor consideration, pay attention to the printed circuit board (PCB) design in order to reduce source impedance.

X5R- and X7R-type capacitors are highly recommended because they have minimal variation in value and ESR over temperature. Maximum ESR should be less than 1.0  $\Omega$ .

#### **Output Capacitors**

The TPS75005 is designed to be stable using standard ceramic capacitors with capacitance values 4.7  $\mu$ F or greater. In order to meet C2000 transient requirements, a 10- $\mu$ F output capacitor at each of OUT1 and OUT2 is recommended.

X5R- and X7R-type capacitors are highly recommended because they have minimal variation in value and ESR over temperature. Maximum ESR should be less than 1.0  $\Omega$ .

See the Sense Pins (OUT1\_S AND OUT2\_S) section for more details.

### Sense Pins (OUT1\_S AND OUT2\_S)

The TPS75005 has output voltage sensing pins OUT1\_S and OUT2\_S. OUT1\_S should be connected to OUT1 at the output capacitor of LDO1, and OUT2\_S to OUT2 at the output capacitor of LDO2. Both output capacitors should be placed close to the device to minimize OUT1\_S and OUT2\_S trace. Figure 27 shows capacitor placement.

Figure 27. Output Capacitors Placement and Sense Pins

When the C2000 controller is placed far from the TPS75005 on a PCB, it is recommended to connect the output capacitors of OUT1 and OUT2 as close as possible to the TPS75005 device in order to route OUT1 and OUT2 node to a C2000 controller, and to place  $0.1-\mu$ F ceramic capacitors for each of the V<sub>DD</sub> and V<sub>DDIO</sub> pins.

#### Soft-Start (SS1 and SS2)

The TPS75005 has a soft-start (or slow-start) function for LDO1 and LDO2 that work independently of one another. The ramp-up time for LDO1 and LDO2 is by default 260 µs due to the internal 110-pF capacitors. By connecting an external capacitor(s) at the SS1 and/or SS2 pins, the ramp-up time for the LDOs increases proportionately by following this equation:

$$t_{\text{RAMPUP}}(s) = \frac{C_{\text{SSx}}(F) + 110 \times 10^{-12}(F)}{0.5 \times 10^{-6}(A)} \times 1.2 (V)$$

(1)

where:

$t_{RAMPUP} = ramp up time$

$C_{SSx}$  = external capacitor value at SS1 or SS2 pin

See Figure 23 for an actual measurement curve.

To ensure that these circuits are discharged during power down, the capacitors used can have a maximum value of 10 nF approximately 24 ms of ramping time. When an application circuit must control a much larger timing period, use the supervisor delay setting in addition to the soft-start mechanism. See and find  $T_{SSx}$  and  $T_{d(SVSx)}$  in Figure 32. See the Delay Setting (CT1 and CT2) section for details.

All supported C2000 controllers work well with the TPS75005 default setting (without external soft-start capacitors). In case a large number of output capacitors are connected for a specific application reason, it is recommended to connect capacitors at SS1 and/or SS2 so that inrush current (into the TPS75005) does not cause a large input voltage droop. This can be mitigated by increasing the bulk capacitance at  $V_{IN}$ .

#### NOTE

SS1 and SS2 are very high impedance nodes with very low values of constant current source. These two terminals cannot be monitored by regular oscilloscope probes. Connecting such regular probes to SS1 or SS2 changes the behavior of the soft-start function and no valid waveform can be monitored.

To monitor these terminals, use high-impedance probes, such as active FET probes.

SBVS144C - NOVEMBER 2011 - REVISED APRIL 2012

#### SBVS144C-NOVEMBER 2011-REVISED APRIL 2012

#### Internal Enable Signals and Pull-Down Switches

As shown in Figure 1, LDO1 is controlled by the internal signal EN1, and LDO2 is controlled by EN2. SW1 and SW2 are the inverse signals of EN1 and EN2, respectively. Whenever LDO1 and LDO2 are disabled, that means EN1 and EN2 are logic-L, respectively. The corresponding output node(s) is discharged by an internal MOSFET and  $360-\Omega$  resistor controlled by SW1 and SW2.

These pull-down switches ensure that every power-down sequence is completed in a reasonable, finite time. See the Power-Down Monitoring section for a very important notice.

### LDO1 Voltage Setting (VSET)

LDO1 can be configured as either a 1.8-V regulator or a 1.9-V regulator by the configuration of the VSET pin. When VSET is connected to ground, LDO1 outputs 1.8 V; when VSET is connected to the level of logic-H, LDO1 outputs 1.9 V.

#### Current Limit

The TPS75005 internal current limit helps protect the regulator during unexpected fault conditions. During current limit, the output sources a fixed 900mA. If kept in current limit for an extended period of time, the device will thermally shutdown.

TPS75005

(2)

#### www.ti.com

#### MONITOR BLOCKS

#### Supply Voltage Supervisors (SVS1 and SVS2)

The TPS75005 integrates two supply voltage supervisors (SVSs) to monitor the  $V_{DD}$  and  $V_{DDIO}$  pins of the C2000 controllers.

#### Delay Setting (CT1 and CT2)

The TPS75005 has a programmable delay function for both SVS1 and SVS2 that work independently of each other. By default, both CT1 and CT2 are open, and both SVS1 and SVS2 take approximately 33 µs of delay time from the comparator trip event to its output. By connecting an external capacitor(s) at the CT1 and/or CT2 pins, the SVS delay time increases proportionately, as shown in the following equation:

$$t_{d}(s) = \frac{C_{SSx}(F)}{0.5 \times 10^{-6} (A)} \times 1.2 (V)$$

where:

t<sub>d</sub> = delay time

$C_{CTx}$  = external capacitor value at CT1 or CT2 pin

See Figure 24 for an actual measurement curve.

For a long delay setting, use a very low leakage current capacitor such as X5R- or X7R-type to minimize calculation errors from the previous equation.

All supported C2000 controllers work well with the TPS75005 default settings (without external delay capacitors).

### NOTE

As with the SS1 and SS2 terminals, CT1 and CT2 are very high-impedance nodes with very low values of constant current source. These two terminals cannot be monitored by regular oscilloscope probes. Connecting such regular probes to CT1 or CT2 changes the behavior of the soft-start function and no valid waveform can be monitored.

To monitor these terminals, use high-impedance probes, such as active FET probes.

#### Spike Noise Sensitivity

Application Report SBVA033, TPS75005 Advanced Information: Voltage Monitor Noise Immunity, explains TPS75005 noise immunity performance.

### **Power-Down Monitoring**

The TPS75005 monitors both OUT1 and OUT2 to become 0.3 V in power-down sequence so that next power-up sequence starts from below 0.3 V.

See the **SEQUENCER BLOCK** section for more details.

#### NOTE

In any application circuit, a diode or two diodes in series should not be placed from OUT1 (anode, 1.8 V) to OUT2 (cathode, 3.3 V). Such diode(s) prevent the TPS75005 from pulling OUT2 below 0.3 V; the device stays in a power-down sequence and will not power up again.

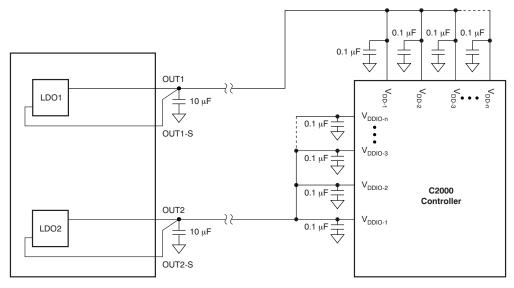

## Auxiliary Voltage Monitor (SVS3)

The TPS75005 has an independent supply voltage supervisor (SVS3) for an auxiliary purpose. The input voltage to the VMON pin is compared with the 1.206 V internal reference and VDET is the output.

One of the most common uses of this feature is to monitor the input voltage. For example, many applications may need to monitor the input voltage at a level higher than the UVLO. Figure 28 shows this type of example. At the VMON pin, use a proper voltage divider to set a target voltage, calculated by the following equation:

(SVS3 Detection Voltage Target) = 1.206 (V) ×

$$\frac{R_1 + R_2}{R_2}$$

(3)

By pulling up VDET to VIN, the VDET output can be connected to the EN pin.

Figure 28. SVS (VMON and VDET) Connection

## Thermal Shutdown (TSD)

The thermal protection feature disables the device outputs when the junction temperature rises to approximately +165°C, allowing the device to cool. When the junction temperature cools to approximately +145°C, the output circuitry is enabled. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits the dissipation of the regulator, protecting it from damage because of overheating.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heat spreading layers. For reliable operation, junction temperature should be limited to +125°C maximum by using the appropriate area of heat spreading layers.

The internal protection circuitry of the TPS75005 is designed to protect against overload conditions, and is not intended to replace proper PCB design. Continuously running the TPS75005 into thermal shutdown degrades device reliability.

This thermal shutdown function disables both LDO1 and LDO2, regardless of sequencer status. Releasing the TSD restarts the power-up sequence.

**NSTRUMENTS**

FXAS

**TPS75005**

www.ti.com

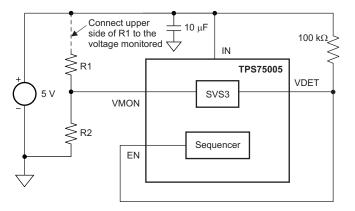

#### Undervoltage Lockout (UVLO)

The TPS75005 uses an undervoltage lockout (UVLO) circuit to keep the output shut off until the internal circuitry is operating properly. The UVLO circuit has a hysteresis feature so that short undershoot transients are typically ignored.

See Figure 11 for the actual measurement. See the section for how to set a custom threshold voltage for the input voltage.

Within the TPS75005, UVLO is combined with EN to create an internal enable signal. A logic AND operation of the EN input signal and internal UVLO signal is used to control the sequencer. By connecting EN to VIN, a logic input buffer for the EN and UVLO circuit refer to the same electric node and the device can be controlled by UVLO function because  $V_{UVLO}$  is greater than  $V_{IH(EN)}$ . Figure 29 shows how to control the TPS75005 without a signal source to the EN pin.

Figure 29. TPS75005 without EN Signal Control

SBVS144C-NOVEMBER 2011-REVISED APRIL 2012

## SEQUENCER BLOCK

The TPS75005 integrates a sequencer logic circuit to control the power-up and power-down sequences of the two output voltage rails ( $V_{DD}$  and  $V_{DDIO}$ ) for C2000 controllers.

Application Report SBVA031, TPS75005 Advanced Information: Sequencer and State Machine, explains a state machine of this sequencer logic in detail.

### **C2000 Power Sequencing**

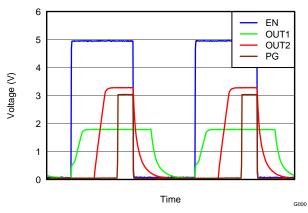

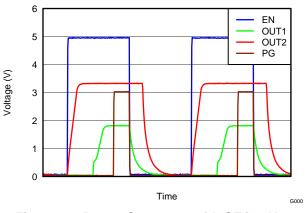

Depending on the C2000 controller series, the required power-up and power-down order of  $V_{DD}$  and  $V_{DDIO}$  can be different, as shown in Table 1. Figure 30 and Figure 31 shows the typical waveforms of two different sequencing cycles set by the SEQ pin.

|                     | POWER-L                  | IP ORDER                 | POWER-DO                  | WN ORDER                  |                         |                     |

|---------------------|--------------------------|--------------------------|---------------------------|---------------------------|-------------------------|---------------------|

| C2000<br>CONTROLLER | 1ST CHANNEL<br>TURNED ON | 2ND CHANNEL<br>TURNED ON | 1ST CHANNEL<br>TURNED OFF | 2ND CHANNEL<br>TURNED OFF | TPS75005<br>SEQ SETTING | TYPICAL<br>WAVEFORM |

| F280x/F2801x        | V <sub>DD</sub>          | V <sub>DDIO</sub>        | V <sub>DDIO</sub>         | V <sub>DD</sub>           | Logic-L                 | Figure 30           |

| F281x               | V <sub>DDIO</sub>        | V <sub>DD</sub>          | V <sub>DD</sub>           | V <sub>DDIO</sub>         | Logic-H                 | Figure 31           |

| F2823x              | V <sub>DD</sub>          | V <sub>DDIO</sub>        | V <sub>DDIO</sub>         | V <sub>DD</sub>           | Logic-L                 | Figure 30           |

| F2833X              | V <sub>DD</sub>          | V <sub>DDIO</sub>        | V <sub>DDIO</sub>         | V <sub>DD</sub>           | Logic-L                 | Figure 30           |

Table 1. Required Power-Up and Power-Down Sequence of C2000 Controllers

Figure 30. Power Sequence with SEQ = L

Figure 31. Power Sequence with SEQ = H

#### SBVS144C - NOVEMBER 2011 - REVISED APRIL 2012

TPS75005

#### www.ti.com

#### Normal Power-Up and Power-Down Sequence

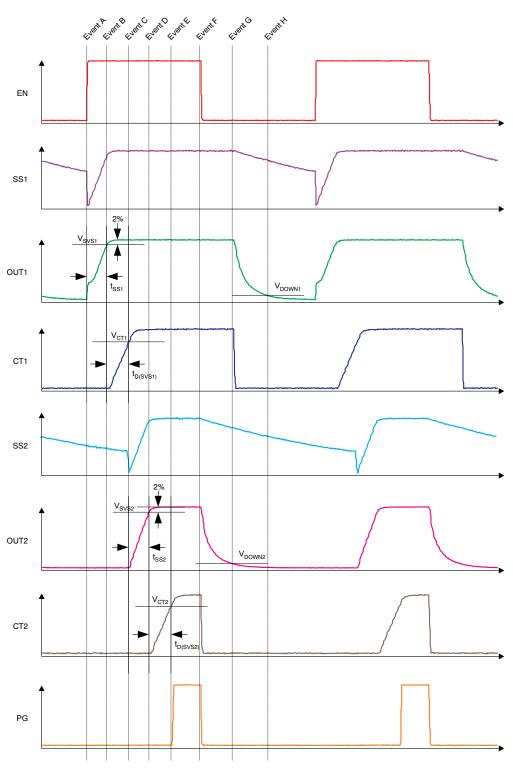

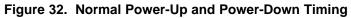

Figure 32 shows oscilloscope waveforms of the TPS75005 in a normal power-up and power-down sequence with SEQ = L. Refer to the time lines labeled Event A through Event H.

1. Before Event A, the TPS75005 is idle, waiting for an enable event.

#### (Power-Up Sequence Begins)

- At Event A, EN goes to logic-H and the device immediately discharges a soft-start capacitor (C<sub>SS1</sub>) by using a one-shot circuit. Then, the LDO1 soft-start circuit starts charging C<sub>SS1</sub>. The OUT1 voltage follows the SS1 voltage. Time between Event A and Event B is defined as t<sub>SS1</sub> and can be programmed by C<sub>SS1</sub>.

- 3. At Event B, the OUT1 voltage exceeds the  $V_{SVS1}$  threshold and the SVS1 delay circuit starts charging  $C_{CT1}$ . Time between Event B and Event C is defined as  $t_{d(SVS1)}$  and can be programmed by  $C_{CT1}$ .

- 4. At Event C, the CT1 voltage exceeds the V<sub>CT1</sub> threshold to discharge a soft-start capacitor (C<sub>SS2</sub>) using a one-shot circuit. Then, the LDO2 soft-start circuit starts charging C<sub>SS2</sub>. The OUT2 voltage follows the SS2 voltage. Time between Event C and Event D is defined as t<sub>SS2</sub> and can be programmed by C<sub>SS2</sub>.

- 5. At Event D, the OUT2 voltage exceeds the  $V_{SVS2}$  threshold and the SVS2 delay circuit starts charging  $C_{CT2}$ . Time between Event D and Event E is defined as  $t_{d(SVS2)}$  and can be programmed by  $C_{CT2}$ .

#### (Power-Up Sequence Ends)

6. At Event E, the CT2 voltage exceeds the V<sub>CT2</sub> threshold and PG goes high to enable the C2000 controller. The TPS75005 is up and running as long as a disable or an error event occurs.

#### (Power-Down Sequence Begins)

- 7. At Event F, EN goes to logic-L and the device immediately turns PG to logic-L so that the C2000 controller is disabled. Then, an internal signal EN2 goes to logic-L in order to disable LDO2. Because the active pull-down switch is enabled by SW2 (= EN2) signal, the OUT2 voltage starts decreasing (note that this ramp-down speed depends on the application circuits).

- At Event G, the OUT2 voltage underruns the V<sub>DOWN2</sub> threshold and an internal signal EN1 goes into logic-L in order to disable LDO1. Because the active pull-down switch is enabled by SW1 (= EN1) signal, the OUT1 voltage starts decreasing (note that this ramp-down speed is depends on the application circuits).

- 9. At Event H, the OUT1 voltage underruns the V<sub>DOWN1</sub> threshold to return back to the idle state.

(Power-Down Sequence Ends)

SBVS144C-NOVEMBER 2011-REVISED APRIL 2012

www.ti.com

#### THERMAL INFORMATION

#### **Power Dissipation**

Knowing the device power dissipation and proper sizing of the thermal plane that is connected to the tab or pad is critical to avoiding thermal shutdown and ensuring reliable operation.

Power dissipation of the device depends on input voltage and load conditions and can be calculated using Equation 4:

$$P_{D} = (V_{IN} - V_{OUT}) I_{OUT}$$

Power dissipation can be minimized and greater efficiency can be achieved by using the lowest possible input voltage necessary to achieve the required output voltage regulation.

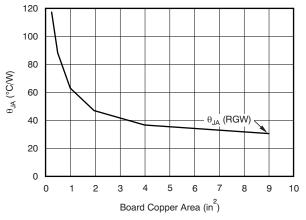

On the QFN (RGW) package, the primary conduction path for heat is through the exposed pad to the printed circuit board (PCB). The pad can be connected to ground or be left floating; however, it should be attached to an appropriate amount of copper PCB area to ensure the device does not overheat. The maximum junction-toambient thermal resistance depends on the maximum ambient temperature, maximum device junction temperature, and power dissipation of the device and can be calculated using Equation 5:

$$\mathsf{R}_{\theta \mathsf{J}\mathsf{A}} = \left(\frac{+125^{\circ}\mathsf{C} - \mathsf{T}_{\mathsf{A}}}{\mathsf{P}_{\mathsf{D}}}\right) \tag{5}$$

Knowing the maximum R<sub>BJA</sub>, the minimum amount of PCB copper area needed for appropriate heat sinking can be estimated using Figure 33.

NOTE:  $\theta_{JA}$  value at a board size of 9-in<sup>2</sup> (that is, 3-in x 3-in) is a JEDEC standard.

Copyright © 2011–2012, Texas Instruments Incorporated

#### Figure 33. $\theta_{JA}$ vs Board Size

Figure 33 shows the variation of  $\theta_{JA}$  as a function of ground plane copper area in the board. It is intended only as a guideline to demonstrate the effects of heat spreading in the ground plane and should not be used to estimate actual thermal performance in real application environments.

**NOTE:** When the device is mounted on an application PCB, it is strongly recommended to use  $\Psi_{JT}$  and  $\Psi_{JB}$ , as explained in the Estimating Junction Temperature section.

(4)

SBVS144C - NOVEMBER 2011 - REVISED APRIL 2012

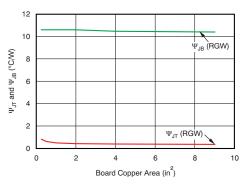

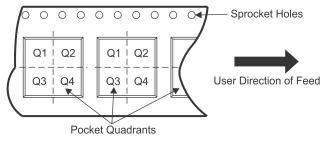

### **Estimating Junction Temperature**

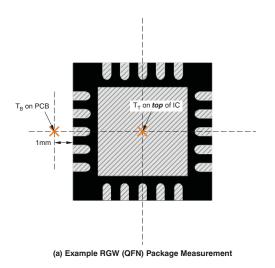

Using the thermal metrics  $\Psi_{JT}$  and  $\Psi_{JB}$ , as shown in the *Thermal Information* table, the junction temperature can be estimated with corresponding formulas (given in Equation 6). For backwards compatibility, an older  $\theta_{JC}$ , *Top* parameter is listed as well.

$\Psi_{\mathsf{JT}}: \quad \mathsf{T}_{\mathsf{J}} = \mathsf{T}_{\mathsf{T}} + \Psi_{\mathsf{JT}} \bullet \mathsf{P}_{\mathsf{D}}$

$\Psi_{JB}$ :  $T_J = T_B + \Psi_{JB} \bullet P_D$

Where:

P<sub>D</sub> is the power dissipation shown by Equation 5

$T_T$  is the temperature at the center-top of the device

$T_B$  is the PCB temperature measured 1 mm away from the device *on the PCB surface* (as Figure 35 shows). (6)

**NOTE:** Both T<sub>T</sub> and T<sub>B</sub> can be measured on actual application boards using an infrared thermometer.

For more information about measuring  $T_T$  and  $T_B$ , see Application Report SBVA025, Using New Thermal Metrics, available for download at www.ti.com.

By looking at Figure 34, the new thermal metrics ( $\Psi_{JT}$  and  $\Psi_{JB}$ ) have very little dependency on board size. That is, using  $\Psi_{JT}$  or  $\Psi_{JB}$  with Equation 6 is a good way to estimate  $T_J$  by simply measuring  $T_T$  or  $T_B$ , regardless of the application board size.

Figure 34.  $\Psi_{JT}$  and  $\Psi_{JB}$  vs Board Size

For a more detailed discussion of why TI does not recommend using  $\theta_{JC(top)}$  to determine thermal characteristics, refer to Application Report SBVA025, *Using New Thermal Metrics*, available for download at www.ti.com. For further information, refer to Application Report SPRA953, *IC Package Thermal Metrics*, also available on the TI website.

Page

Page

www.ti.com

#### SBVS144C - NOVEMBER 2011 - REVISED APRIL 2012

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision B (March 2012) to Revision C Pa      | age |

|----|-----------------------------------------------------------|-----|

| •  | Changed Voltage Information table                         | 2   |

| •  | Added new note 2 to Thermal Information table             | . 3 |

| •  | Changed note 3(b) copper coverage value from 20% to 4%    | 3   |

| •  | Changed test condition for t <sub>D(SVS1)</sub> parameter | . 4 |

| •  | Changed test condition for t <sub>D(SVS2)</sub> parameter | 5   |

| •  | Changed functional block diagram                          | . 7 |

### Changes from Revision A (February 2012) to Revision B

| • | Changed Thermal Information table values | 3 |

|---|------------------------------------------|---|

| • | Changed functional block diagram         | 7 |

#### Changes from Original (November 2011) to Revision A

| • | Changed all "PowerPAD" to "thermal pad".                                  | . 1 |

|---|---------------------------------------------------------------------------|-----|

| • | Added application report links to Description section                     | . 1 |

| • | Changed "VIN" to "IN" in front page diagram                               | . 1 |

| • | Changed "V <sub>IN</sub> " to "IN"                                        | . 6 |

| • | Changed "VIN" to "input voltage"                                          | 12  |

| • | Changed caption for Figure 25                                             | 12  |

| • | Changed Voltage Monitor Blocks section title and updated subsection order | 17  |

| • | Changed "VIN" to "IN" in Figure 28                                        | 18  |

| • | Changed "VIN" to "IN" in Figure 29                                        | 19  |

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                      |              |                         |         |

| TPS75005RGWR     | NRND          | VQFN         | RGW                | 20   | 3000           | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR  | -40 to 125   | PPMQ                    |         |

| TPS75005RGWT     | NRND          | VQFN         | RGW                | 20   | 250            | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR  | -40 to 125   | PPMQ                    |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

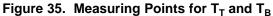

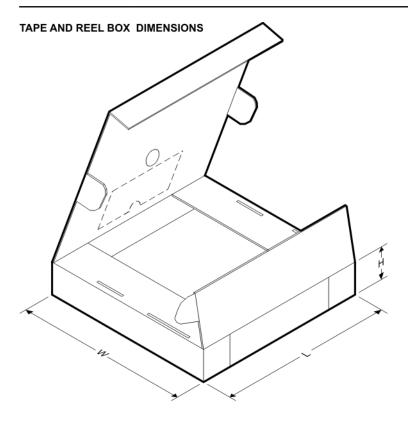

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

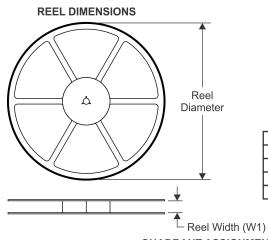

## TAPE AND REEL INFORMATION

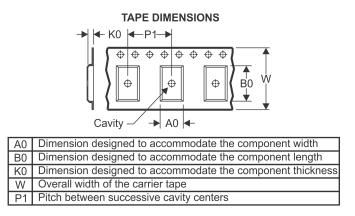

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS75005RGWR                | VQFN            | RGW                | 20 | 3000 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS75005RGWT                | VQFN            | RGW                | 20 | 250  | 180.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

29-Sep-2019

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS75005RGWR | VQFN         | RGW             | 20   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS75005RGWT | VQFN         | RGW             | 20   | 250  | 210.0       | 185.0      | 35.0        |

# **RGW 20**

5 x 5, 0.65 mm pitch

# **GENERIC PACKAGE VIEW**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

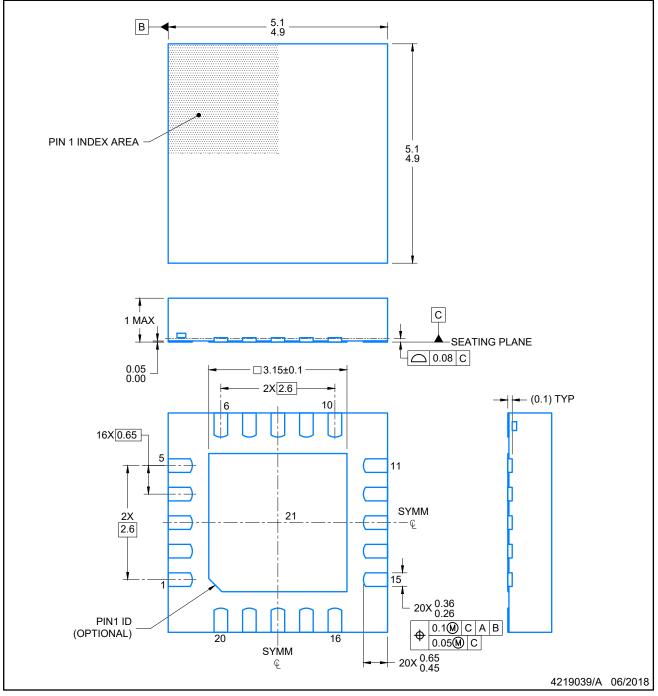

# **RGW0020A**

# **PACKAGE OUTLINE**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

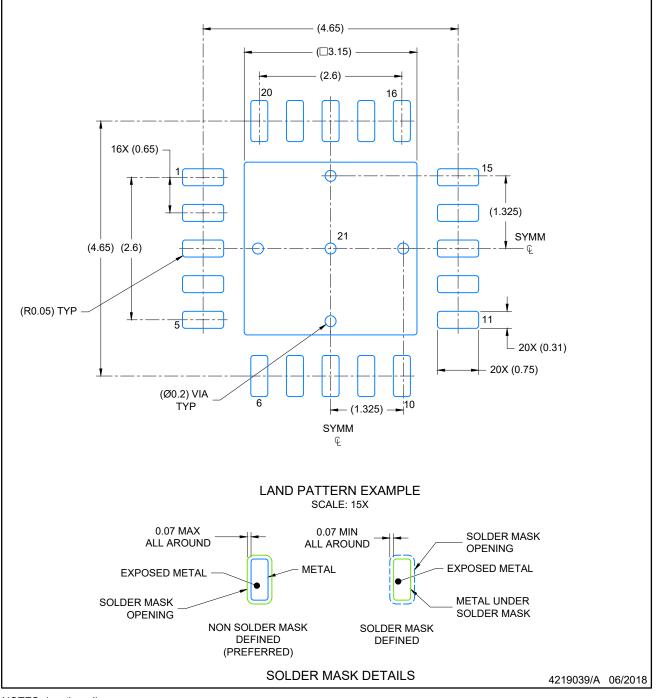

# **RGW0020A**

# **EXAMPLE BOARD LAYOUT**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

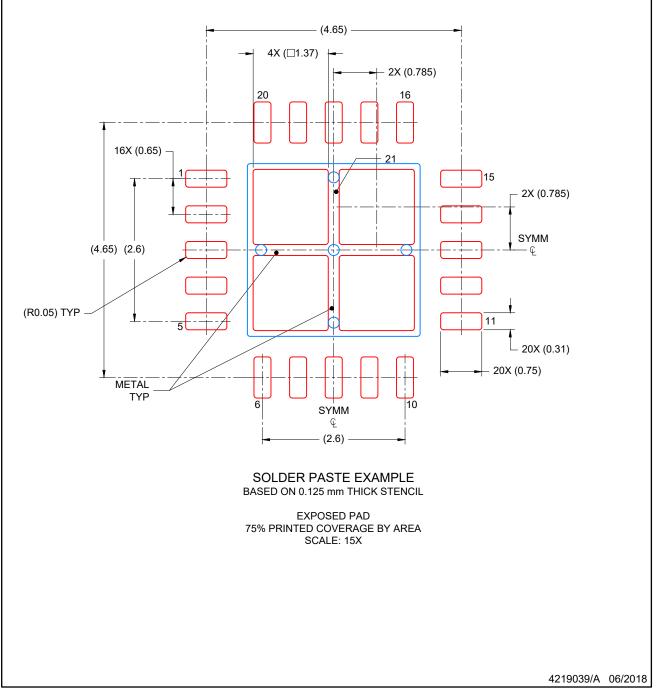

# **RGW0020A**

# **EXAMPLE STENCIL DESIGN**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated