# XQTyer 评估板例程使用手册

#### 版本记录

| 版本   | 版本说明 | 作者     | 日期        |

|------|------|--------|-----------|

| V1.0 | 初始版本 | Martin | 2022-11-1 |

# 目录

| XQ | Tyer ' | 评估极例    | 桯使用于卌                 | 1        |

|----|--------|---------|-----------------------|----------|

| 1  | 目白     | 勺       |                       | 4        |

| 2  | 软件     | 井版本说明   | fl                    | 4        |

| 3  | ZYN    | Q与DSF   | <sup>9</sup> 之间通信例程   | 5        |

|    | 3.1    | ZYN     | IQ 与 DSP 之间 SRIO 通信   | 5        |

|    |        | 3.1.1   | 例程位置                  | 5        |

|    |        | 3.1.2   | 功能简介                  | <u>5</u> |

|    |        | 3.1.3   | 例程使用                  | 5        |

|    | 3.2    | ZYN     | IQ 与 DSP 之间 EMIF16 通信 | 20       |

|    |        | 3.2.1   | 例程位置                  | 20       |

|    |        | 3.2.2   | 功能简介<br>例程使用          | 20       |

|    |        | 3.2.3   | 例程使用                  | 21       |

|    | 3.3    | ZYN     | IQ 与 DSP 之间 uPP 通信    | 27       |

|    |        | 3.3.1   | 例程位置                  | 27       |

|    |        | 3.3.2   | 功能简介                  | 27       |

|    |        | 3.3.3   | 例程使用                  |          |

|    | 3.4    | ZYN     | IQ 与 DSP 之间 GPIO 通信   |          |

|    |        | 3.4.1   | 例程位置                  |          |

|    |        | 3.4.2   | 功能简介                  |          |

|    |        |         | 例程使用                  |          |

| 4  |        |         | ₹                     |          |

|    | 4.1    |         | , 以太网通信               |          |

|    |        | 4.1.1   | 例程位置                  |          |

|    |        | 4.1.2   | 功能简介                  |          |

|    |        | 4.1.3   | 例程使用                  |          |

|    | 4.2    |         | PUARTO 串口通信           |          |

|    |        | 4.2.1   | 例程位置                  |          |

|    |        | 4.2.2   | 功能简介                  |          |

|    |        | 4.2.3   | 例程使用                  |          |

|    | 4.3    |         | ,GPIO LED 示例          |          |

|    |        | 4.3.1   | 例程位置                  |          |

|    |        | 4.3.2   | 功能简介                  |          |

|    |        | 4.3.3   | 例程使用                  |          |

|    | 4.4    | DSP     | ,DDR3 内存读写测试          | 54       |

|    |        | Xines — |                       |          |

|      | 4.4.1   | 例程位置                             | 54  |

|------|---------|----------------------------------|-----|

|      | 4.4.2   | 功能简介                             | 54  |

|      | 4.4.3   | 例程使用                             | 55  |

| 4.5  | 5 D     | SP DDR3 初始化以及内存读写测试              | 59  |

|      | 4.5.1   | 例程位置                             | 59  |

|      | 4.5.2   | 功能简介                             | 59  |

|      | 4.5.3   | 例程使用                             | 61  |

| 4.6  | 5 D     | SP IPC 核间通信之 NOTIFY              | 65  |

|      | 4.6.1   | 例程位置                             | 65  |

|      | 4.6.2   | 功能简介                             | 65  |

|      | 4.6.3   | 例程使用                             | 68  |

| 4.7  | ' D     | SP IPC 核间通信之 MessageQ            |     |

|      | 4.7.1   | 例程位置                             |     |

|      | 4.7.2   | 功能简介                             | 74  |

|      | 4.7.3   | 例程使用                             |     |

| 5 ZY | NQ PL 单 | 9独例程                             | 82  |

| 5.1  | _ Z`    | YNQ PL Cameralink 回环例程           | 82  |

|      | 5.1.1   | 例程位置                             | 82  |

|      | 5.1.2   | 功能简介                             |     |

|      | 5.1.3   | Cameralink 接口时序说明                | 83  |

|      | 5.1.4   | 管脚约束                             | 85  |

|      | 5.1.5   | 例程使用                             | 85  |

| 5.2  | 2 Z`    | YNQ PL SFP 光口通信例程                | 89  |

|      | 5.2.1   | 例程位置                             | 89  |

|      | 5.2.2   | 功能简介                             | 89  |

|      | 5.2.3   | 管脚约束                             | 91  |

|      | 5.2.4   | 例程使用                             | 92  |

| 5.3  | 3 Z`    | YNQ PL SFP 光口 IBERT 链路误码测试       | 97  |

|      | 5.3.1   | 例程位置                             | 97  |

|      | 5.3.2   | 功能简介                             | 97  |

|      | 5.3.3   | 例程使用                             | 98  |

| 5.4  | l Z'    | YNQ PL M.2 接口验证例程                | 106 |

|      | 5.4.1   | 例程位置                             | 106 |

|      | 5.4.2   | 功能简介                             | 106 |

|      | 5.4.3   | 管脚约束                             | 108 |

|      | 5.4.4   | 例程使用                             | 109 |

| 5.5  | 5 Z'    | YNQ PL M.2 接口之 NVMe Host IP 例程说明 | 113 |

|      | 5.5.1   | 例程声明                             | 113 |

|      | 5.5.2   | 设计目的                             | 113 |

|      | 5.5.3   | NVMe Host FPGA IP 核简介            | 114 |

|      | 5.5.4   | 资源消耗                             | 115 |

|      | 5.5.5   | NVMe Host FPGA IP 测试截图和说明        | 116 |

| 5.6  | 5 Z'    | YNQ PL FMC 之 6 路 ADC 采集例程        | 123 |

|      | 5.6.1   | 例程位置                             | 123 |

|   |     | 5.6.2    | 功能简介                | 123 |

|---|-----|----------|---------------------|-----|

|   |     | 5.6.3    | 管脚约束                | 124 |

|   |     | 5.6.4    | 例程使用                | 126 |

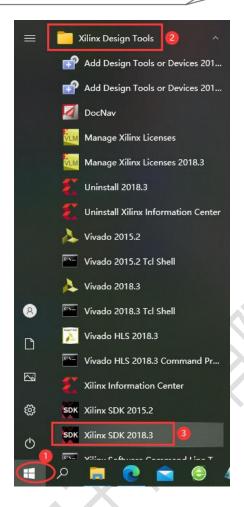

| 6 | ZYN | IQ PS 单独 | 独例程                 | 130 |

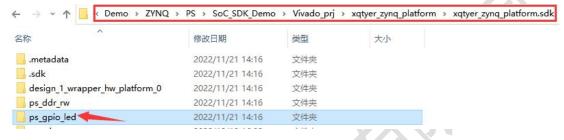

|   | 6.1 | ZYN      | NQ PS GPIO LED 驱动实验 | 130 |

|   |     | 6.1.1    | 例程位置                | 130 |

|   |     | 6.1.2    | 功能简介                | 130 |

|   |     | 6.1.3    | 例程使用                | 130 |

|   | 6.2 | ZYN      | NQ PS 串口中断实验        | 136 |

|   |     | 6.2.1    | 例程位置                | 136 |

|   |     | 6.2.2    | 功能简介                | 137 |

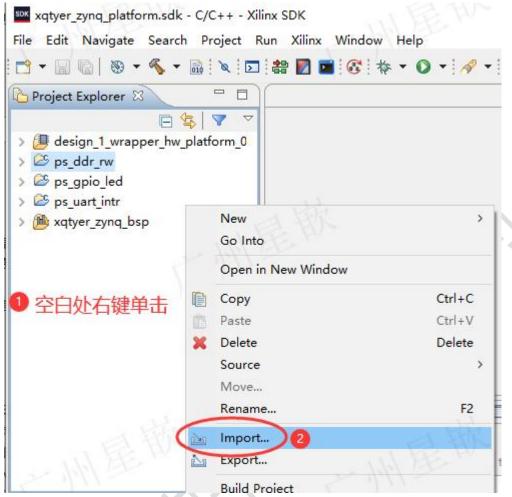

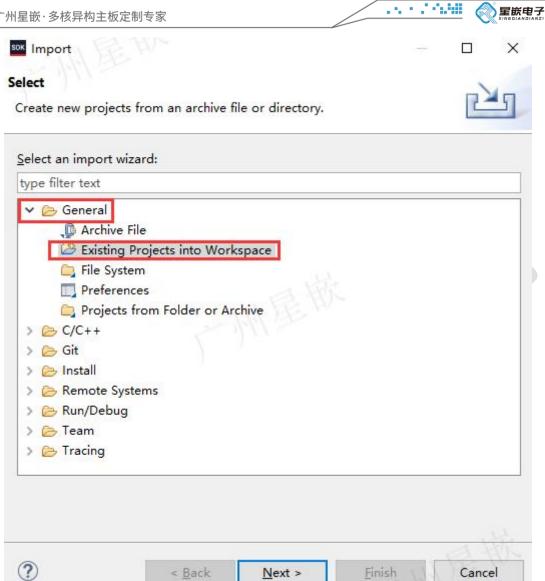

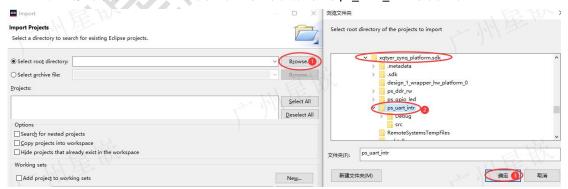

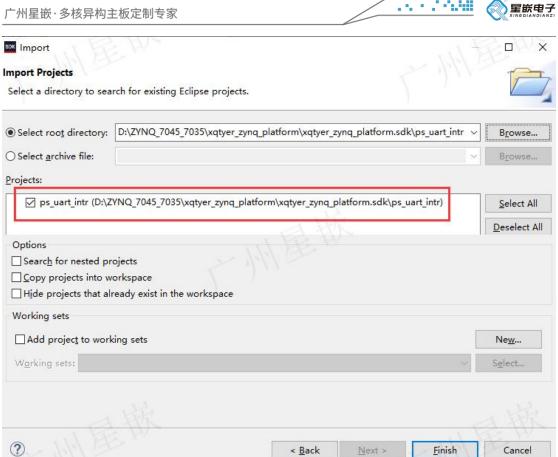

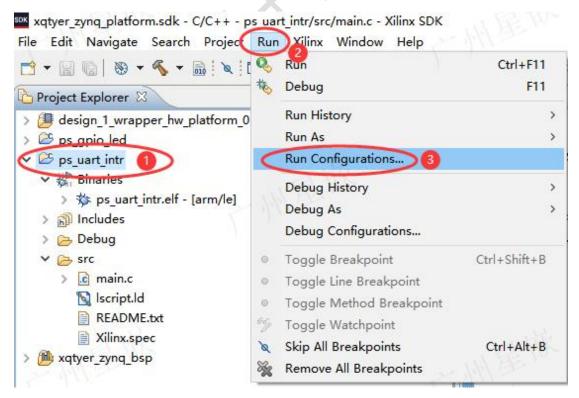

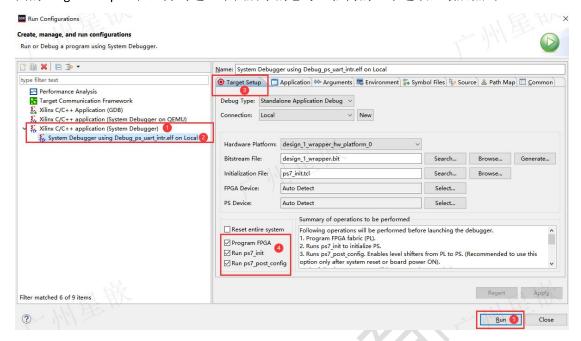

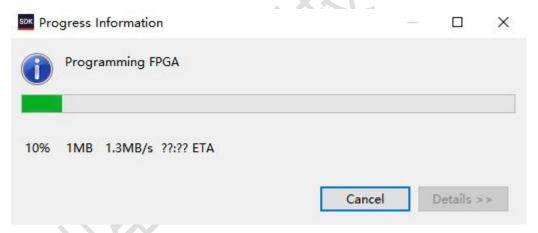

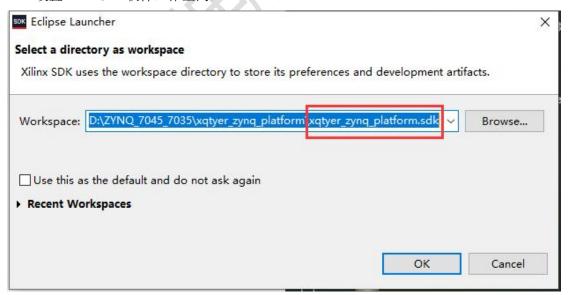

|   |     | 6.2.3    | 例程使用                | 137 |

|   | 6.3 | ZYN      | NQ PS DDR 内存读写实验    | 146 |

|   |     | 6.3.1    | 例程位置                | 146 |

|   |     | 6.3.2    | 功能简介                | 146 |

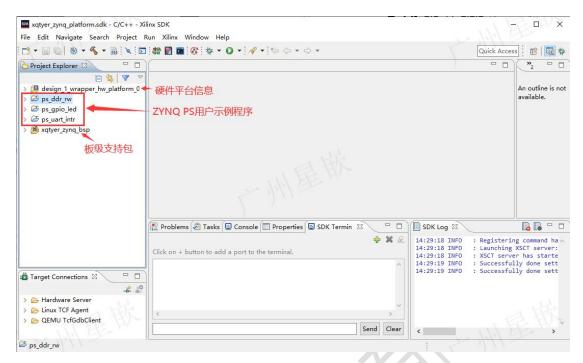

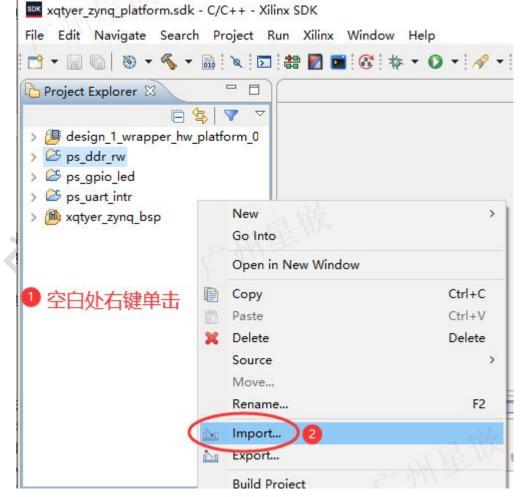

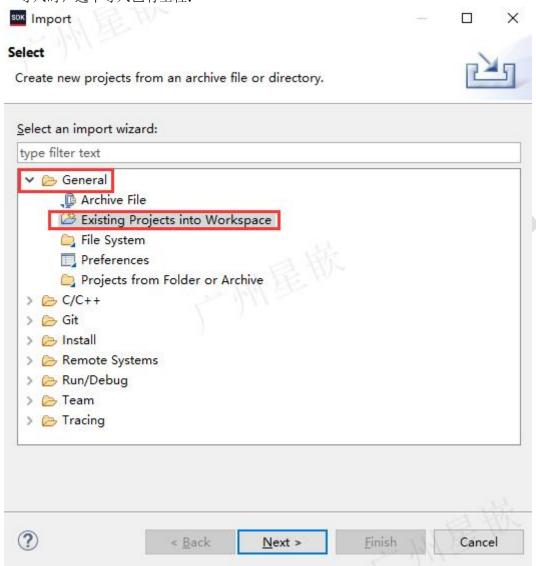

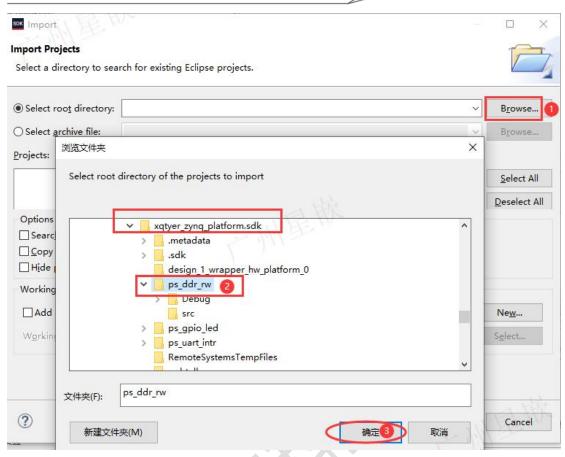

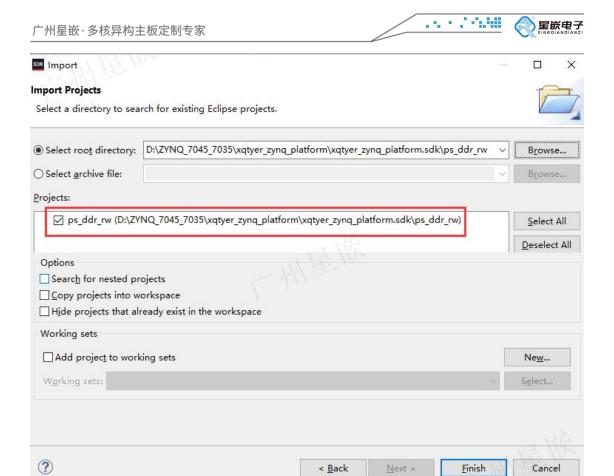

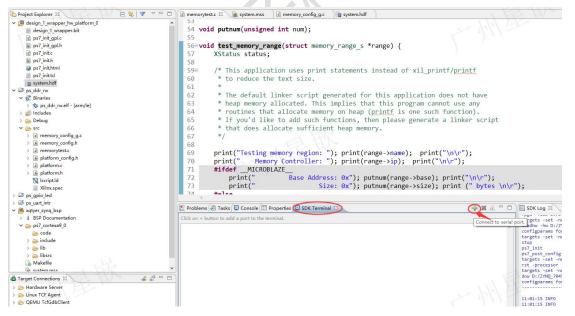

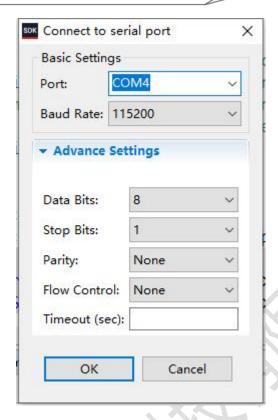

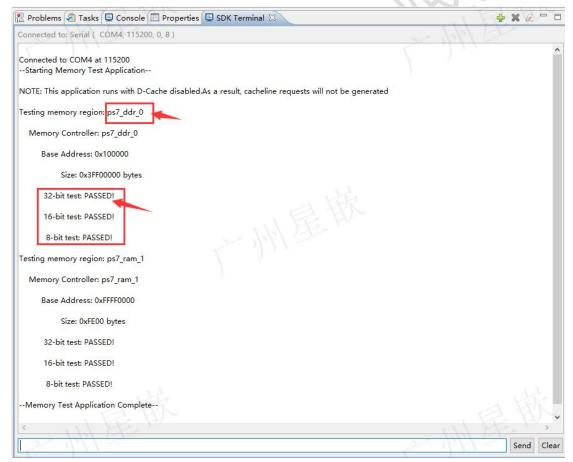

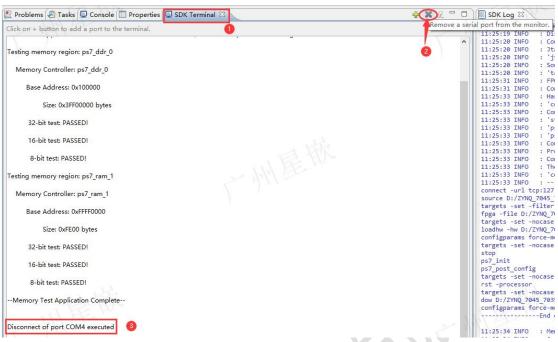

|   |     | 6.3.3    | 例程使用                | 146 |

# 1目的

本手册主要介绍说明 XQTyer 评估板实验平台各个例程的功能、使用步骤以及各个例程的运行效果。同时,也对例程所使用的软件版本、软件工具存放路径以及软件安装参考手册存放位置进行了必要说明。

# 2 软件版本说明

| 开 发  | 基于软件版本                                | 软件安装工具存放路径                                    | 软件安    |

|------|---------------------------------------|-----------------------------------------------|--------|

| 对象   |                                       |                                               | 装参考    |

|      |                                       | $\Delta 117$                                  | 手册     |

| ZYN  | Vivado 2018.3 Tools\ZYNQ\VIVADO2018.3 |                                               | 文 档    |

| Q PL |                                       | (注:提供的是 Vivado 网络安装器,需要联                      | \ZYNQ  |

|      |                                       | 网安装)                                          | 开发工    |

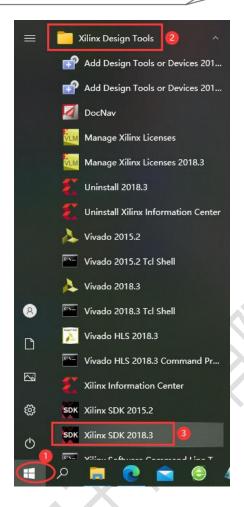

| ZYN  | Xilinx SDK 2018.3                     | 说明:安装 Vivado 工具时,附带一起进行安                      | 具安装    |

| Q PS |                                       | 装                                             | 说      |

|      |                                       |                                               | 明.docx |

|      | CCS 7.4                               | Tools\DSP\CCS7.4.0.00015_win32.zip            | 文档     |

|      |                                       | 1 1/2                                         | \CCS7. |

|      |                                       |                                               | 4 软件   |

|      |                                       |                                               | 安装说    |

|      |                                       |                                               | 明.docx |

| DSP  | 编译器 TI C6000 CGT                      | Tools\DSP\CCS 组 件 安 装 包                       | 文 档    |

| DSI  | 8.3.12                                | \ti_cgt_c6000_8.3.12_windows-x64_installer.ex | \CCS 编 |

|      |                                       | e                                             | 译器和    |

|      | bios_mcsdk_02_01_02_0                 | Tools\DSP\CCS 组 件 安 装 包                       | 依赖组    |

|      | 6                                     | \BIOSMCSDK-C66X                               | 件安装    |

|      |                                       |                                               | 说      |

|      |                                       |                                               | 明.docx |

— Xines

# 3 ZYNQ 与 DSP 之间通信例程

## 3.1ZYNQ与 DSP 之间 SRIO 通信

#### 3.1.1 例程位置

ZYNQ 例程保存在资料盘中的 Demo\ZYNQ\PL\srio\_gen2\_0\_ex 文件夹下。 DSP 例程保存在资料盘中的 Demo\DSP\XQ\_SRIO\_x4LANE\_5Gbps 文件夹下。

### 3.1.2功能简介

实现 DSP 与 ZYNQ 之间 SRIO 接口传输功能。

DSP 与 ZYNQ 之间 SRIO 通道宽度为 4,每个 SRIO 通道速率 5Gbps。DSP SRIO 参考时钟频率为 250MHz,ZYNQ SRIO 参考时钟频率为 125MHz。

DSP 与 ZYNQ 之间 SRIO 接口相关信号连接示意图如下图所示:

DSP 作为 Initiator 发起 NWrite 数据写事务,将数据写入 ZYNQ PL 端的 RAM 空间(最大 2KB);接着,DSP 发起 NRead 数据读事务,从 ZYNQ PL 端的 RAM 空间读取数据; DSP 完成数据写、读事务后,对读写数据进行比对,以检测 SRIO 传输是否有数据错误。

## 3.1.3 例程使用

特别提示: 例程使用,请参考下面章节顺序执行。确保 ZYNQ PL 程序要先运行,然后才能运行 DSP 程序。

### 3.1.3.1 加载运行 ZYNQ 程序

#### 3.1.3.1.1 打开 Vivado 工程

双击桌面 Vivado 图标,打开 Vivado 工具:

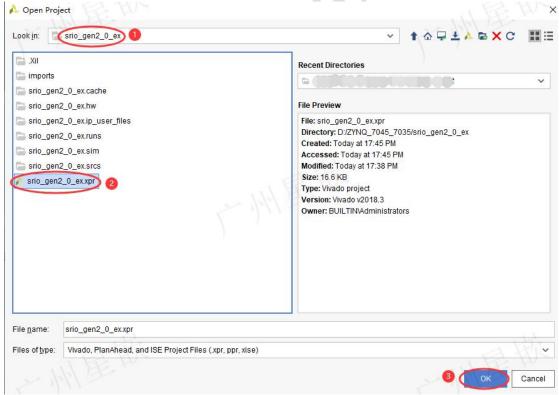

点击 Open Project, 打开工程 (注意:确保例程路径为非中文路径):

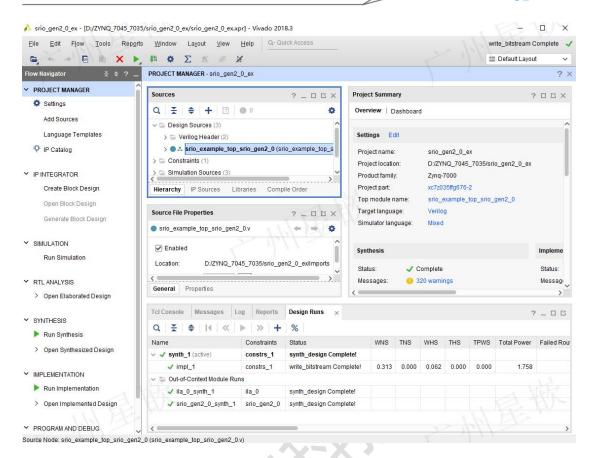

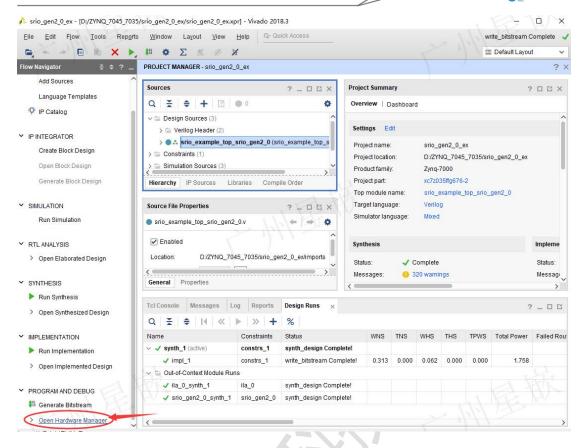

Vivado 工程打开后界面如下图所示:

### 3.1.3.1.2 下载 ZYNQ PL 程序

点击 Open Hardware Manager:

打开 Hardware Manager 的界面如下图所示:

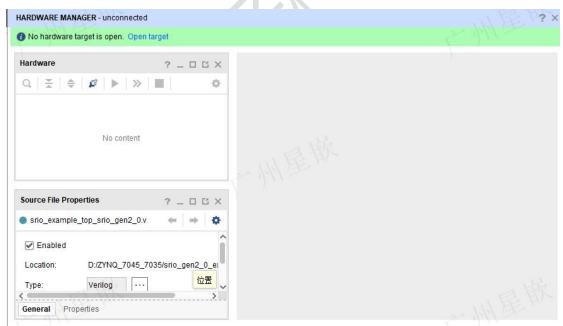

此后,确保 FPGA JTAG 仿真器已连至接板卡和电脑,并且板卡处于上电状态。

点击 Hardare Manager 界面上的 Open target,并在弹出的菜单中单击 Auto Connect:

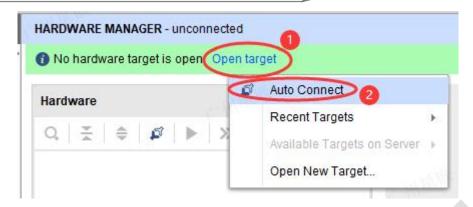

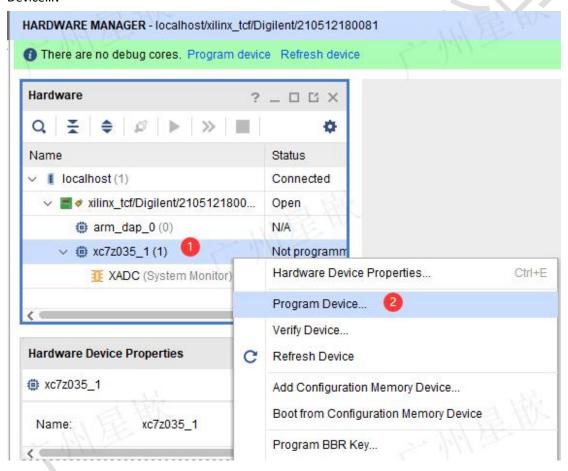

仿真器连接成功后,在找到的 xc7z035\_1 器件上右击,并在弹出的菜单中点击 Program Device...:

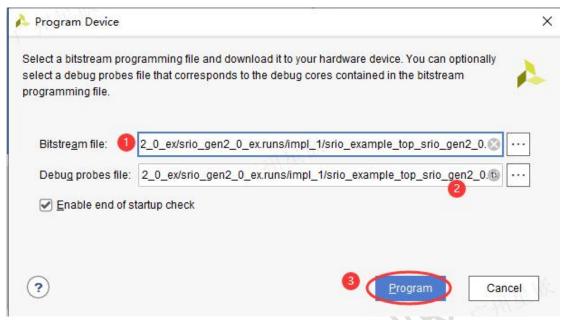

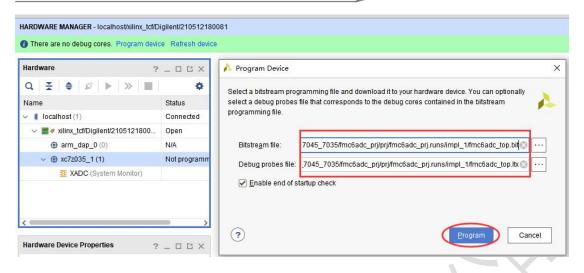

一般来说,Vivado下载工具会自动找到本工程下的程序 bit 流下载文件和调试文件,如果没有自动找到,则需要用户通过旁边的浏览按钮去自行选取。确保程序下载文件没问题后,点击 Program 下载程序:

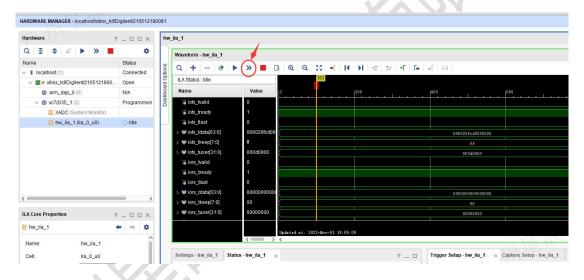

程序下载完成后,点击界面上的">>"按钮,可实时抓取查看 ZYNQ PL 端信号运行波形:

## 3.1.3.2 加载运行 DSP 程序

### 3.1.3.2.1 CCS 导入例程

双击桌面 CCS 快捷图标, 打开 CCS 软件:

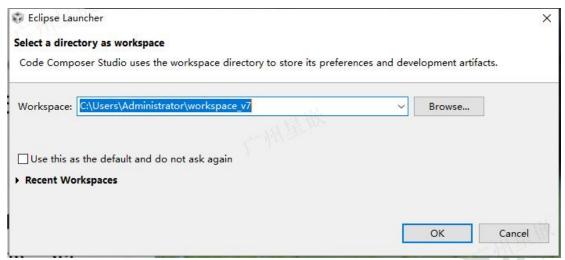

CCS 设置工作空间时,选择默认即可:

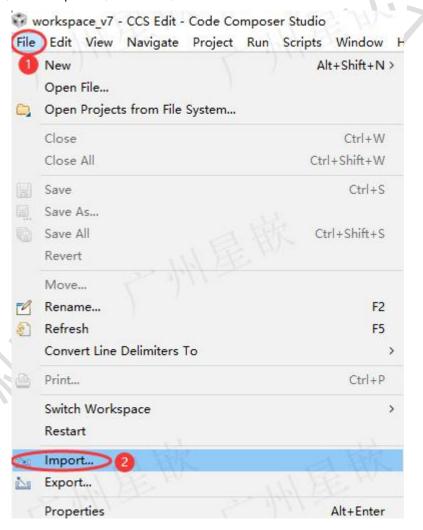

通过菜单 File->Import...导入 CCS 工程:

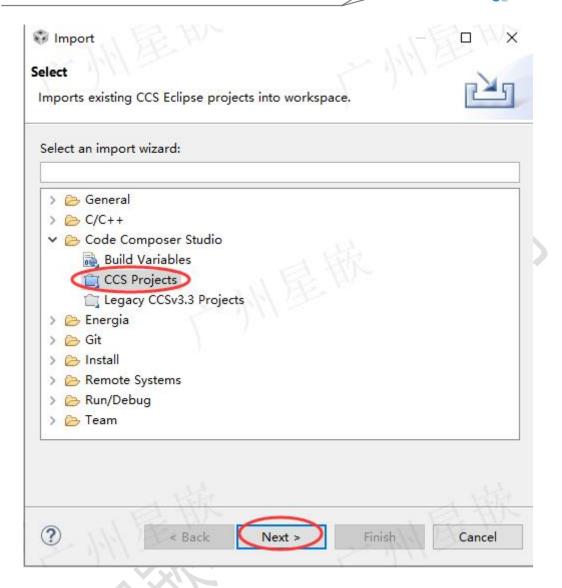

导入项目选择 CCS Projects:

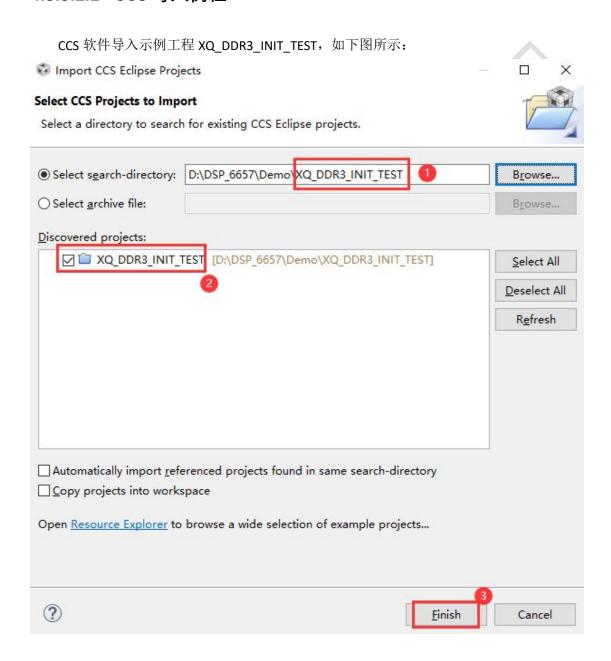

点击 Browse...,浏览找到例程所在位置(<mark>注意:确保例程路径为非中文路径</mark>),选中例程所在目录,并点击"确定":

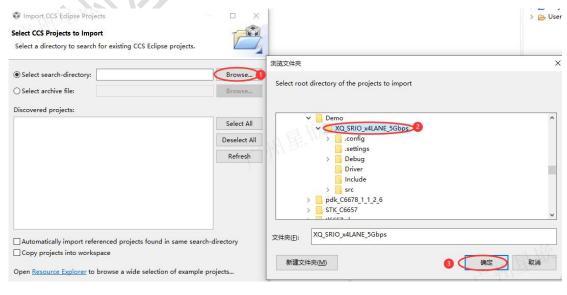

CCS 软件将识别到的例程显示在 Discovered projects 一栏,最后点击 Finish:

Frojects Import CCS Eclipse Projects

#### Select CCS Projects to Import

Select a directory to search for existing CCS Eclipse projects.

| <ul><li>Select search-directory:</li></ul> | D:\DSP_6657\Demo\XQ_SRIO_x4LANE_                 | B <u>r</u> owse  |

|--------------------------------------------|--------------------------------------------------|------------------|

| Select <u>a</u> rchive file:               |                                                  | Browse           |

| iscovered projects:                        |                                                  |                  |

| ☑ 🖆 XQ_SRIO_x4LAN                          | E_5Gbps D:\DSP_6657\Demo\XQ_SRIO                 | Select All       |

|                                            | 14.                                              | Deselect All     |

|                                            | 一目扩                                              | R <u>e</u> fresh |

| <                                          | 3                                                |                  |

| ,                                          | 3                                                |                  |

|                                            |                                                  |                  |

| Automatically import <u>r</u> efe          | erenced projects found in same search-di<br>pace | rectory          |

| Automatically import <u>r</u> efe          |                                                  | -                |

| Automatically import <u>r</u> efe          | pace                                             | -                |

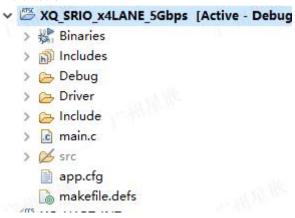

例程导入后界面如下图所示:

#### 3.1.3.2.2 下载 CCS 程序

#### 3.1.3.2.2.1 目标配置文件设置

特别提示:目标配置文件设置这一步骤可以只进行一次,后面例程可以反复使用,不用重复创建或设置。

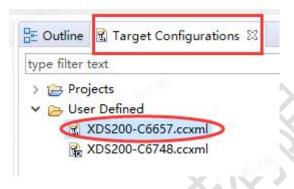

在右边的 Target Configuration 窗口,双击打开之前创建好的目标配置文件,如下图的 XDS200-C6657.ccxml:

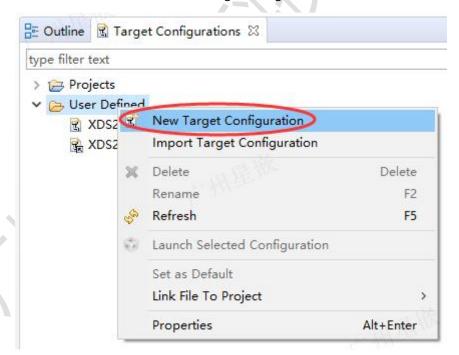

如果还没有目标配置文件,则在 Target Configuration 窗口的空白处或 User Defined 文件夹处右击,并在弹出的菜单中点击"New Target Configuration"新建目标配置文件:

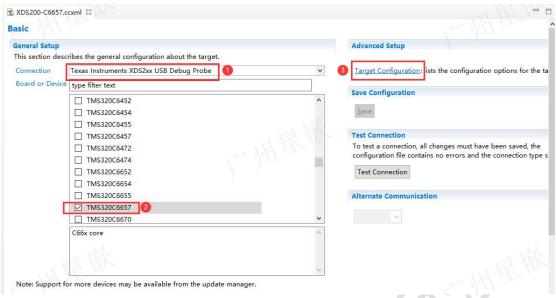

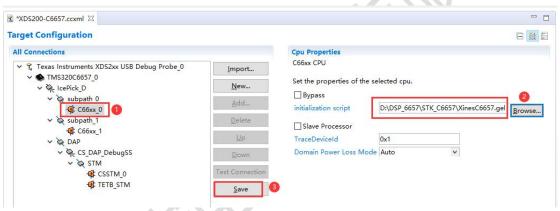

在打开的目标配置文件中,需要配置仿真器类型、器件型号,我们实验用的仿真器为 XQ-XDS200U,选中仿真器类型 XDS2xx USB Debug Probe 即可,器件型号勾选上 TMS320C6657,如下图所示,然后点击高级设置项 Target Configuration,准备 Gel 文件设置:

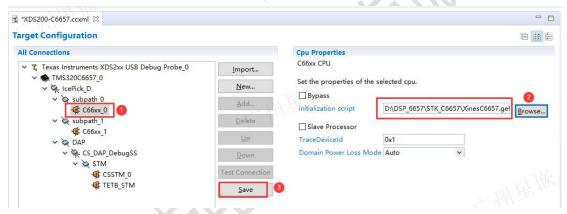

在高级项设置窗口中,点击 C66xx\_0 核心,然后在右侧的初始化脚本栏中,点击 Browse,找到我们提供的 Gel 文件,即 XinesC6657.gel。设置完 Gel 文件后,点击 Save:

#### 3.1.3.2.2.2 启动目标配置文件

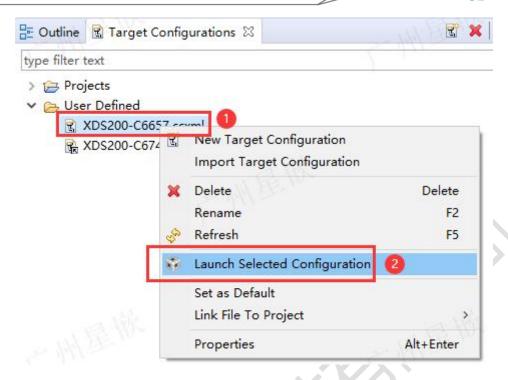

在已经创建并设置好的目标配置文件处右击,并在弹出的菜单中点击 Launch Selected Configuration,打开调试窗口:

#### 3.1.3.2.2.3 仿真器连接目标器件

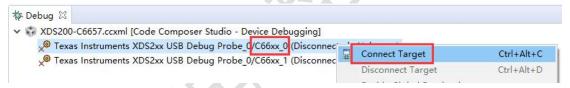

调试窗口打开后,右键单击 C66xx\_0 核心 0, 并在弹出的菜单中点击 Connect Target:

#### 3.1.3.2.2.4 加载 DSP 程序

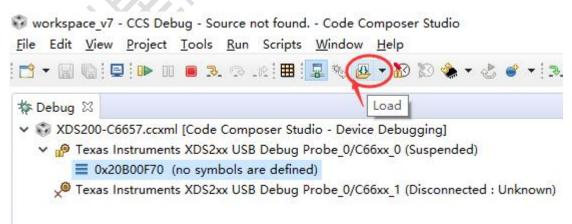

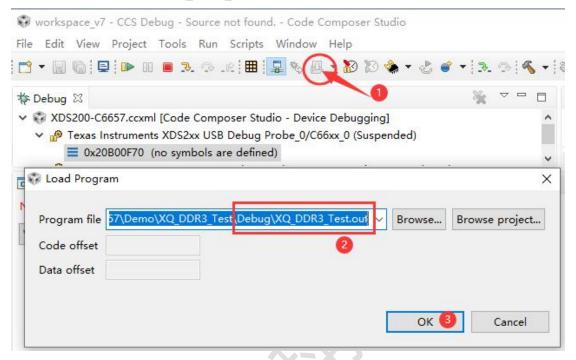

点击 Load 图标,加载 DSP 程序:

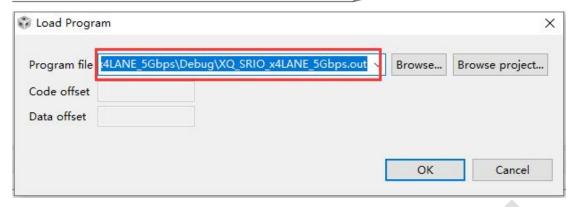

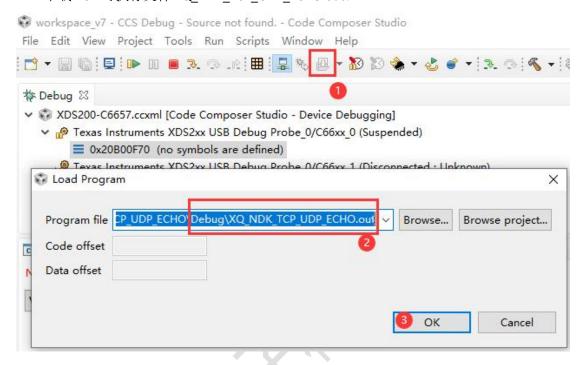

点击 Browse...或 Browse project...,找到 DSP 程序的可执行文件(以.out 为后缀),然后点击 OK,如下图所示:

#### 3.1.3.2.2.5 DSP 程序运行

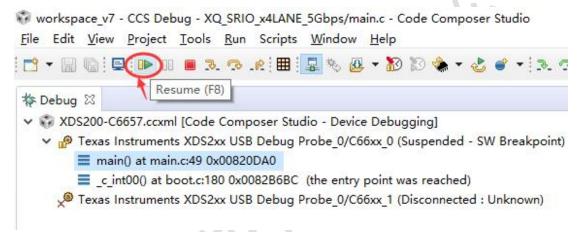

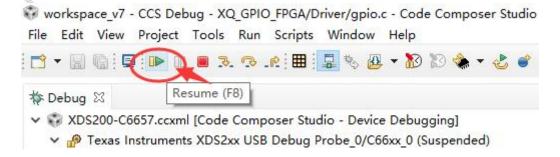

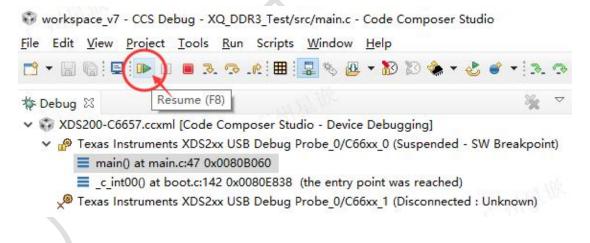

点击 Resume 运行图标,运行 DSP 程序,如下图所示:

### 3.1.3.3 运行结果说明

### 3.1.3.3.1 DSP 程序运行结果

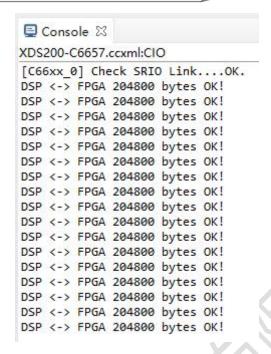

CCS 软件的 Console 控制台窗口打印 SRIO 调试信息。

DSP 通过 SRIO 接口先发起 NWrite 写事务,数据长度为 2048 字节;接着 DSP 发起 NRead 事务,数据长度为 2048 字节,然后比对读写事务对应的数据。

如果 SRIO 传输异常,存在数据错误,则程序里面错误计数器累加,并输出打印当前错误个数。每当完成 100 次 NWrite 和 NRead SRIO 读写事务,则输出打印一次"DSP <-> FPGA 204800 bytes OK!"字样,如下图所示:

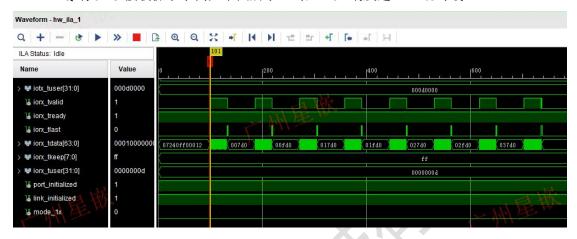

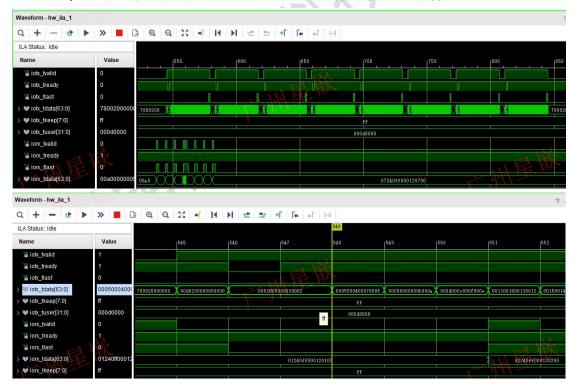

#### 3.1.3.3.2 ZYNQ PL 程序运行结果

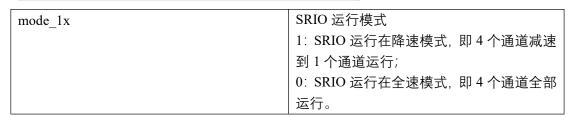

ZYNQ PL 端提供的 ILA 调试窗口,可以实时抓取采集 SRIO 本地总线信号时序波形。SRIO 本地总线信号说明如下(详细定义请参考数据手册 Xilinx 文档 pg007 srio gen2.pdf):

| SRIO 本地发送总线信号    |                         |  |  |

|------------------|-------------------------|--|--|

| iotx_tvalid      | 发送数据有效标志位               |  |  |

| iotx_tready      | 发送准备好标志位                |  |  |

| iotx_tlast       | 最后一个发送数据标志位             |  |  |

| iotx_tdata       | 发送数据                    |  |  |

| iotx_tkeep       | 发送数据字节控制位               |  |  |

| iotx_tuser       | 发送控制数据,主要内容是源 ID 和目的 ID |  |  |

| SRIO 本地接收总线信号    |                         |  |  |

| iorx_tvalid      | 接收数据有效标志位               |  |  |

| iorx_tready      | 接收准备好标志位                |  |  |

| iorx_tlast       | 最后一个接收数据标志位             |  |  |

| iorx_tdata       | 接收数据                    |  |  |

| iorx_tkeep       | 接收数据字节控制位               |  |  |

| iorx_tuser       | 接收控制数据,主要内容是源 ID 和目的 ID |  |  |

| 状态信号             |                         |  |  |

| port_initialized | SRIO 端口初始化完成标志位         |  |  |

|                  | 1: SRIO 端口初始化完成;        |  |  |

|                  | 0: SRIO 端口初始化未完成。       |  |  |

| link_initialized | SRIO 链路初始化完成标志位         |  |  |

|                  | 1: SRIO 链路初始化完成;        |  |  |

|                  | 0: SRIO 链路初始化未完成。       |  |  |

—— Xines -

ZYNQ端 SRIO 接收抓取示例如下图所示(对应 DSP端发起 NWrite 事务):

ZYNQ SRIO 发送抓取示例如下图所示(对应 DSP 端发起 NRead 事务):

#### 3.1.3.4 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接:

—— Xines

workspace\_v7 - CCS Debug - XQ\_SRIO\_x4LANE\_5Gbps/main.c - Code Composer Studio

File Edit View Project Tools Run Scripts Window Help

Terminate (Ctrl+F2)

▼ Debug

▼ XDS200-C6657.ccxml [Code Composer Studio - Device Debugging]

▼ Texas Instruments XDS2xx USB Debug Probe\_0/C66xx\_0 (Running)

▼ Texas Instruments XDS2xx USB Debug Probe\_0/C66xx\_1 (Disconnected : Unknown)

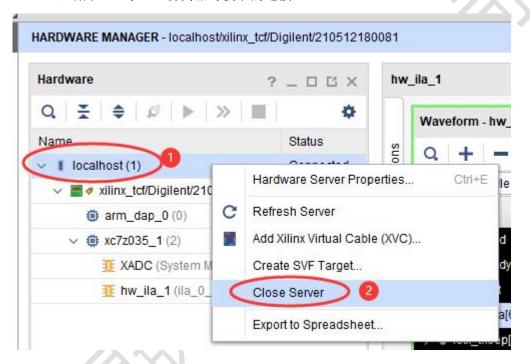

Vivado 调试界面 Hardware Manager 窗口,右键单击 localhost(1),在弹出的菜单中点击 Close Server,断开 ZYNQ JTAG 仿真器与板卡的连接:

最后,关闭板卡电源,实验结束。

# 3.2ZYNQ 与 DSP 之间 EMIF16 通信

### 3.2.1 例程位置

ZYNQ 例程保存在资料盘中的 Demo\ZYNQ\PL\FPGA\_DSP\_EMIF 文件夹下。 DSP 例程保存在资料盘中的 Demo\DSP\XQ\_EMIF16 文件夹下。

## 3.2.2功能简介

实现 DSP 与 ZYNQ PL 端之间 EMIF16 接口传输功能。

DSP 首先通过 EMIF16 接口往 ZYNQ PL 端发送 4096 字节数据,然后再读回来,并检测数据是否有错,数据发送、读回以及错误情况实时打印。

ZYNQ PL 端开辟了一块 RAM 空间,用于存放 DSP 通过 EMIF16 接口写入的数据,同时用作 DSP 通过 EMIF16 接口读数据时的数据源。

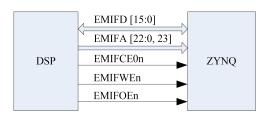

DSP 与 ZYNQ PL 端之间 EMIF16 接口连接示意图如下图所示:

EMIF16 接口信号定义说明如下表格所示:

| 信号名                 | 功能描述                     |  |  |

|---------------------|--------------------------|--|--|

| EMIFD [15:0]        | 双向数据总线。                  |  |  |

|                     | DSP 读数据时,对 DSP 而言是输入接口;  |  |  |

|                     | DSP 写数据时,对 DSP 而言是输出接口。  |  |  |

| EMIFA [23:0]        | 地址总线, 注意实际使用时, 23bit 作为最 |  |  |

| 低位。ZYNQ PL 端例程只使用了其 |                          |  |  |

|                     | 12bits 作为地址总线作为示例。       |  |  |

|                     | DSP 端: 为输出接口;            |  |  |

|                     | ZYNQ PL 端: 为输入接口。        |  |  |

| EMIFCE0n            | 片选信号,低电平有效。              |  |  |

|                     | DSP 端: 为输出接口;            |  |  |

|                     | ZYNQ PL 端: 为输入接口。        |  |  |

| EMIFWEn             | 写使能信号, 低电平有效。            |  |  |

|                     | DSP 端: 为输出接口;            |  |  |

| ZYNQ PL 端: 为输入接口。   |                          |  |  |

| EMIFOEn             | 输出使能信号,即 DSP 读使能,低电平有    |  |  |

| . (///, X*          | 效。                       |  |  |

|                     | DSP 端: 为输出接口;            |  |  |

| 1921.               | ZYNQ PL 端:为输入接口。         |  |  |

### 3.2.3 例程使用

### 3.2.3.1 加载运行 ZYNQ 程序

### 3.2.3.1.1 打开 Vivado 工程

打开 Vivado 示例工程:

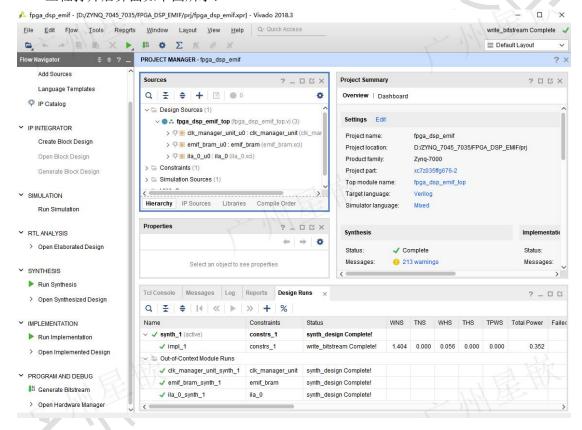

#### 工程打开后界面如下图所示:

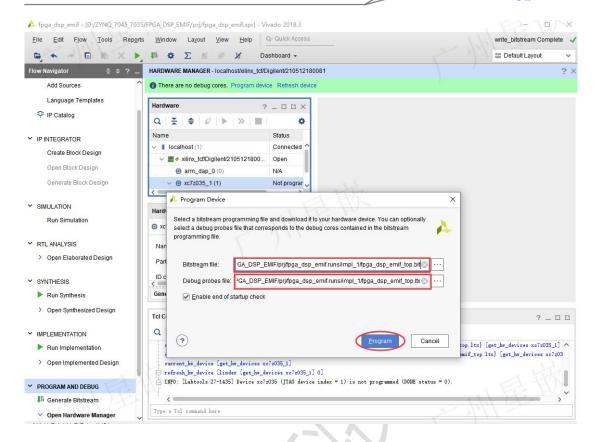

## 3.2.3.1.2 下载 ZYNQ PL 程序

下载 bit 流文件 fpga\_dsp\_emif\_top.bit,并且配套 fpga\_dsp\_emif\_top.ltx 调试文件,如下图下载界面所示:

## 3.2.3.2 加载运行 DSP 程序

#### 3.2.3.2.1 CCS 导入例程

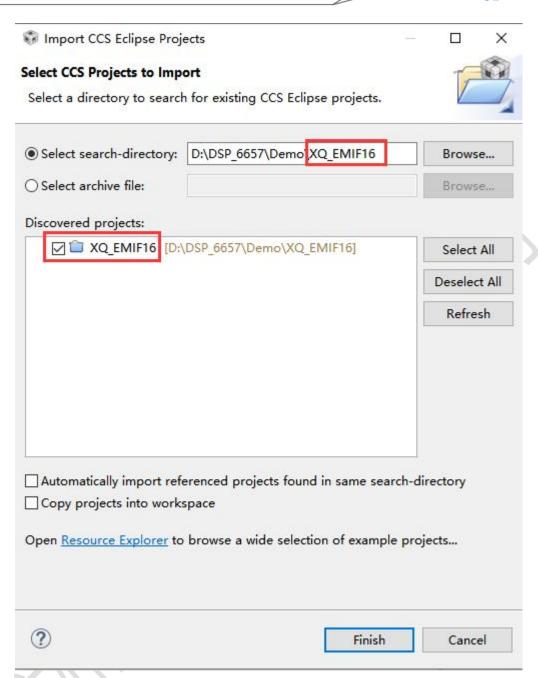

CCS 软件导入 EMIF16 示例工程 XQ EMIF16,如下图所示:

CCS 示例工程导入后界面如下图所示:

#### 3.2.3.2.2 下载运行 CCS 程序

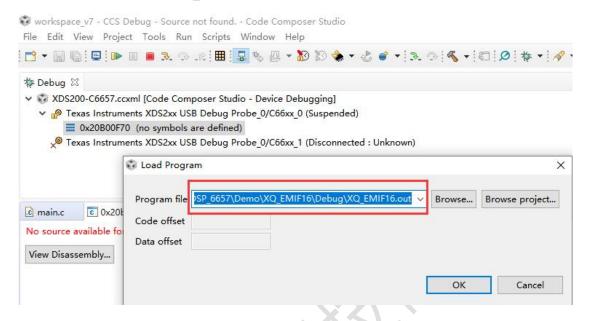

下载 DSP 可执行文件 XQ EMIF16.out:

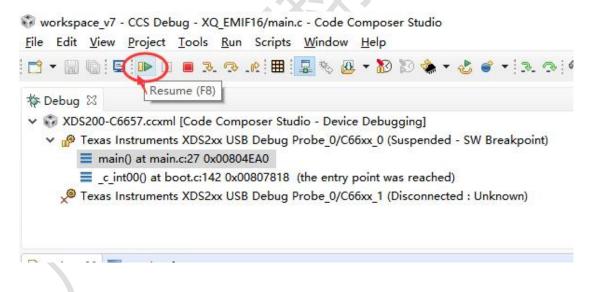

点击 Resume 运行 DSP 程序:

### 3.2.3.3 运行结果说明

### 3.2.3.3.1 DSP 程序运行结果

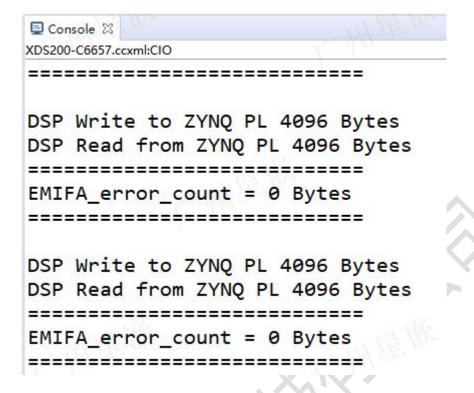

DSP 首先通过 EMIF16 接口往 ZYNQ PL 端发送 4096 字节数据,然后再读回来,并检测数据是否有错,数据发送、读回以及错误情况实时打印,如下图所示:

#### 3.2.3.3.2 ZYNQ PL 程序运行结果

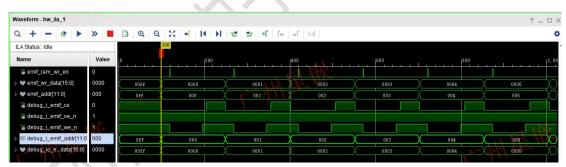

ZYNQ PL 端提供的 ILA 调试窗口,可以实时抓取采集 EMIF16 总线信号时序波形。 DSP 通过 EMIF16 总线接口发送数据(即写 ZYNQ PL 端 RAM)示例如下图所示:

DSP 通过 EMIF16 总线接口读回数据(即读 ZYNQ PL端 RAM)示例如下图所示:

#### 3.2.3.4 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。

Vivado 调试界面 Hardware Manager 窗口,右键单击 localhost(1),在弹出的菜单中点击 Close Server,断开 ZYNQ JTAG 仿真器与板卡的连接。

最后,关闭板卡电源,实验结束。

## 3.3ZYNQ与 DSP 之间 uPP 通信

### 3.3.1 例程位置

ZYNQ 例程保存在资料盘中的 Demo\ZYNQ\PL\FPGA\_DSP\_uPP 文件夹下。 DSP 例程保存在资料盘中的 Demo\DSP\XQ uPP 文件夹下。

### 3.3.2功能简介

实现 DSP 与 ZYNQ PL 端之间 uPP 接口传输功能。

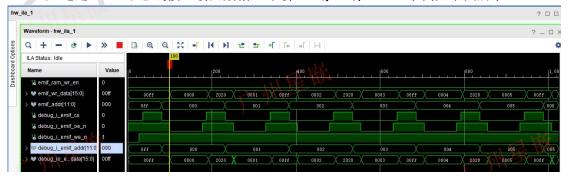

DSP 通过 uPP B 通道往 ZYNQ PL 端发送 204800 字节数据,ZYNQ PL 端收到 uPP B 通道数据后直接交给 uPP A 通道送回至 DSP。DSP 程序比对 uPP A 通道接收到的数据和 uPP B 通道发送出去的数据,检测数据是否有错,uPP A/B 两个通道的数据收发以及错误情况实时打印。

DSP 与 ZYNQ PL 端之间 uPP A/B 两个通道接口的连接示意图如下图所示:

### 3.3.3 例程使用

#### 3.3.3.1 加载运行 ZYNQ 程序

#### 3.3.3.1.1 打开 Vivado 工程

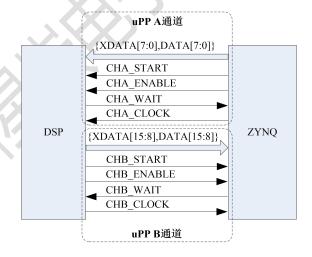

#### 工程打开后界面如下图所示:

#### 3.3.3.1.2 下载 ZYNQ PL 程序

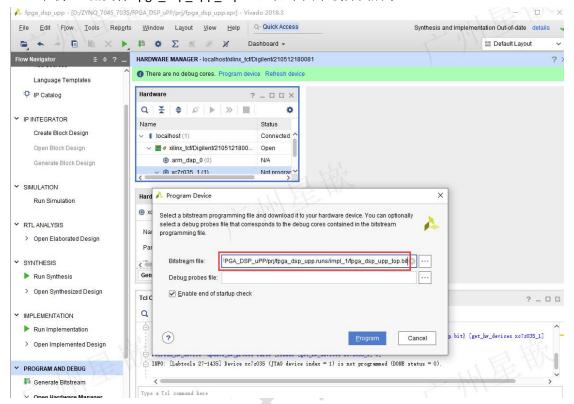

下载 bit 流文件 fpga\_dsp\_upp\_top.bit, 如下图下载界面所示:

### 3.3.3.2 加载运行 DSP 程序

#### 3.3.3.2.1 CCS 导入例程

CCS 软件导入 uPP 示例工程 XQ\_uPP, 如下图所示:

#### Select CCS Projects to Import

Select a directory to search for existing CCS Eclipse projects.

| Select search-directory: D:\DSP_6657\Demo\XQ_uPP                                                                                                                                   | B <u>r</u> owse  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| ○ Select <u>a</u> rchive file:                                                                                                                                                     | B <u>r</u> owse  |

| Discovered projects:                                                                                                                                                               |                  |

| ✓ 🗀 XQ_uPP [D:\DSP_6657\Demo\XQ_uPP]                                                                                                                                               | Select All       |

|                                                                                                                                                                                    | Deselect All     |

|                                                                                                                                                                                    | R <u>e</u> fresh |

| ☐ Automatically import <u>r</u> eferenced projects found in same searc ☐ <u>C</u> opy projects into workspace  Open <u>Resource Explorer</u> to browse a wide selection of example |                  |

| 四城,                                                                                                                                                                                | 山椒               |

| ? <u>Finish</u>                                                                                                                                                                    | Cancel           |

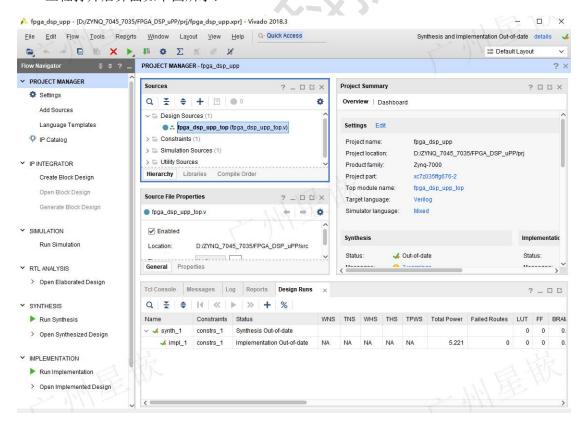

ccs 示例工程导入后界面如下图所示:

#### 3.3.3.2.2 下载运行 CCS 程序

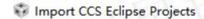

下载 DSP 可执行文件 XQ uPP.out:

### 3.3.3.3 运行结果说明

□ ---:-- ♡ □ 0..20L00570

### 3.3.3.3.1 DSP 程序运行结果

DSP 每完成一次 uPP 收、发传输后(uPP B 通道发送、uPP A 通道接收),程序对 uPP A/B 两个通道的收发数据进行比对,如果传输数据正常,则打印完成且无错误信息,否则打印此

次 uPP 传输存在错误的提示信息,如下图所示为正确传输打印信息:

© Console ⋈ XDS200-C6657.ccxml:CIO

uPP Transmission finished with 204800 Bytes data been sent and received! Verifying the results...

PASSED: uPP transmission completed with no errors!

-----

=== uPP Transmission Test : Start...

-----

Initializing uPP buffers... Starting uPP transfers...

uPP Transmission finished with 204800 Bytes data been sent and received!

Verifying the results...

PASSED: uPP transmission completed with no errors!

#### 3.3.3.4 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。

Vivado 调试界面 Hardware Manager 窗口,右键单击 localhost(1),在弹出的菜单中点击 Close Server,断开 ZYNQ JTAG 仿真器与板卡的连接。

最后,关闭板卡电源,实验结束。

### 3.4ZYNQ与 DSP 之间 GPIO 通信

### 3.4.1 例程位置

ZYNQ 例程保存在资料盘中的 Demo\ZYNQ\PL\FPGA\_DSP\_GPIO 文件夹下。 DSP 例程保存在资料盘中的 Demo\DSP\XQ\_GPIO\_FPGA 文件夹下。

### 3.4.2 功能简介

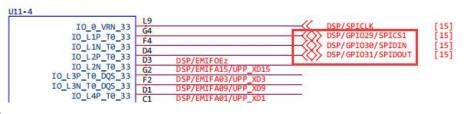

实现 DSP 与 ZYNQ PL 端之间 GPIO 接口传输功能。 DSP 与 ZYNQ PL 端之间有 3 根 GPIO 信号相连,如下原理图标注所示:

# ZYNQ PL CONNECTED TO DSP

### BANK33

DSP 示例通信程序将 GPIO29、GPIO30 两个 GPIO 设置为输出(对 ZYNQ 而言就是输入),GPIO31 设置为输入(对 ZYNQ 而言就是输出)。DSP 在 GPIO29、GPIO30 两个 GPIO 上产生方波信号,ZYNQ 可通过 ILA 软逻辑分析仪抓取波形查看;ZYNQ 通过 VIO 虚拟 IO 往 GPIO31 上输出高、低电平,DSP 示例程序里面检测 GPIO31 下降沿中断,一旦检测到 GPIO31 管脚下降沿中断信号,则打印测试信息。

## 3.4.3 例程使用

#### 3.4.3.1 加载运行 ZYNQ 程序

#### 3.4.3.1.1 打开 Vivado 工程

打开 Vivado 示例工程:

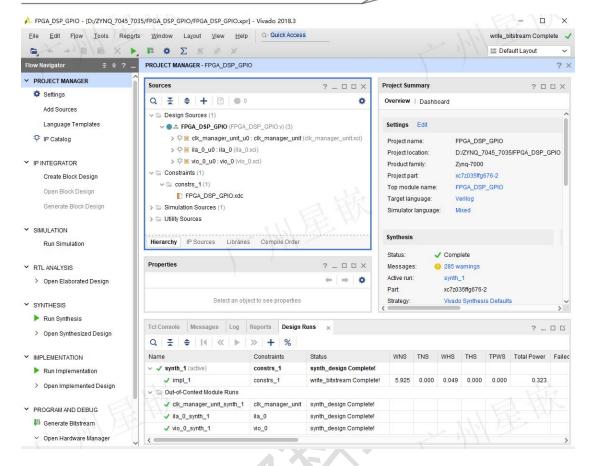

工程打开后界面如下图所示:

#### 3.4.3.1.2 下载 ZYNQ PL 程序

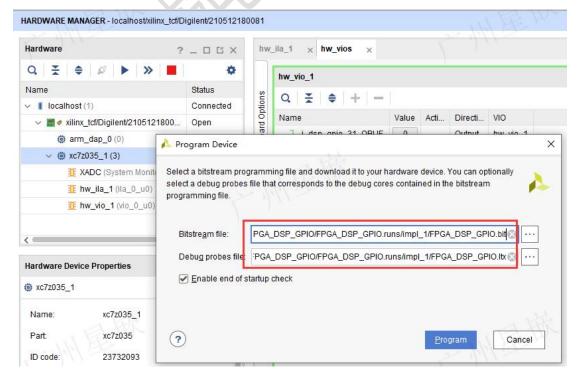

下载 bit 流文件 FPGA\_DSP\_GPIO.bit,如下图下载界面所示:

#### 3.4.3.2 加载运行 DSP 程序

### 3.4.3.2.1 CCS 导入例程

CCS 软件导入示例工程 XQ GPIO FPGA,如下图所示: Import CCS Eclipse Projects Select CCS Projects to Import Select a directory to search for existing CCS Eclipse projects. D:\DSP 6657\Demo\XQ GPIO FPGA Select search-directory: Browse... O Select archive file: Browse... Discovered projects: XQ\_GPIO\_FPGA [D:\DSP\_6657\Demo\XQ\_GPIO\_FPGA] Select All Deselect All Refresh Automatically import referenced projects found in same search-directory Copy projects into workspace Open Resource Explorer to browse a wide selection of example projects... Finish Cancel

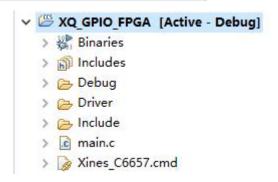

CCS 示例工程导入后界面如下图所示:

#### 3.4.3.2.2 下载运行 CCS 程序

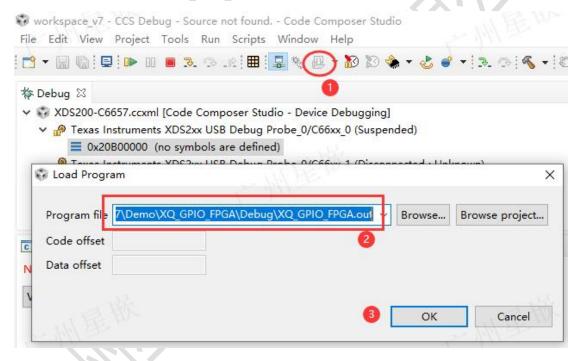

下载 DSP 可执行文件 XQ\_GPIO\_FPGA.out:

点击 Resume 运行 DSP 程序:

#### 3.4.3.3 运行结果说明

#### 3.4.3.3.1 DSP 程序运行结果

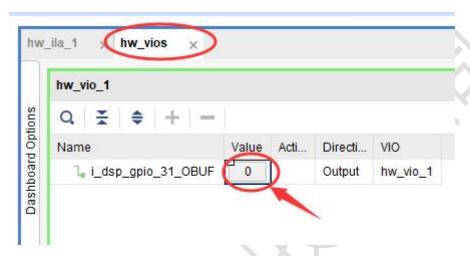

点击 ZYNQ PL 调试界面上 hw\_vios 窗口中 Value 下面的数字 0 或 1, 从而在 GPIO31 上产 生高低电平信号:

每当 GPIO31 上产生高低电平下降沿信号,DSP 程序进入中断服务函数,打印如下图所示的信息:

```

E Console

EXDS200-C6657.ccxml:CIO

[C66xx_0] ZYNQ PL GPIO falling edge detected!

ZYNQ PL GPIO falling edge detected!

```

# 3.4.3.3.2 ZYNQ 程序运行结果

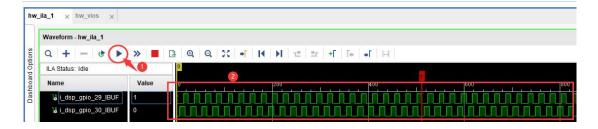

点击 hw\_ila\_1 窗口上三角符号的采集触发按钮,如下图①处标识的按钮,可查看到 DSP 通过 GPIO29、GPIO30 两个 GPIO 管脚发过来的方波信号:

#### 3.4.3.4 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。

Vivado 调试界面 Hardware Manager 窗口,右键单击 localhost(1),在弹出的菜单中点击 Close Server,断开 ZYNQ JTAG 仿真器与板卡的连接。

最后,关闭板卡电源,实验结束。

# 4 DSP 单独例程

# 4.1DSP 以太网通信

# 4.1.1 例程位置

DSP 例程保存在资料盘中的 Demo\DSP\XQ\_NDK\_TCP\_UDP\_ECHO 文件夹下。

# 4.1.2功能简介

实现 DSP 千兆以太网通信测试功能,实现 TCP、UDP 数据回显功能。

main.c 文件中的 NetworkOpen 函数里面创建了两个守护进程,端口号 7 对应任务 dtask\_udp\_echo,响应 TCP 数据接收,并将 TCP 数据回传;端口号 8 对应任务 dtask\_tcp\_echo,响应 UDP 数据接收,并将 UDP 数据回传:

```

€ main.c 🖾

322 static HANDLE hTcpEcho=0;

323//

324// NetworkOpen

325//

326// This function is called after the configuration has booted

327//

328 static void NetworkOpen()

329 {

// Create our local udp echo server

330

hUdpEcho = DaemonNew( SOCK_DGRAM, 0, (7), dtask_udp_echo,

OS_TASKPRINORM, OS_TASKSTKNORM, 0, 1 );

332

333

334

// Create our local tcp echo server

hTcpEcho = DaemonNew( SOCK_STREAMNC, 0, 8, dtask_tcp_echo,

335

OS_TASKPRINORM, OS_TASKSTKNORM, 0, 1 );

336

337}

```

# 4.1.3 例程使用

#### 4.1.3.1 网线连接

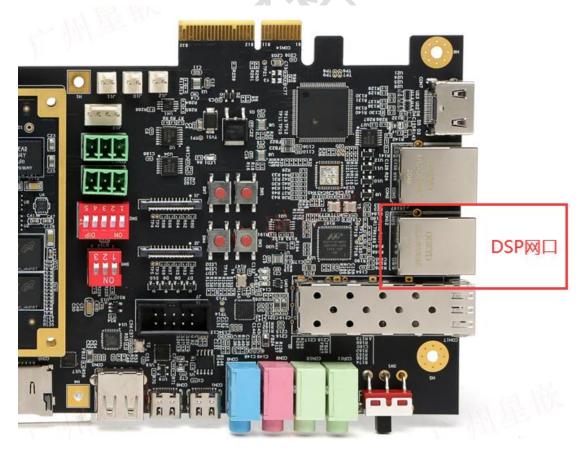

用网线连接板卡上 DSP 网口至交换机,要求和测试电脑在同一个网段:

— Xines ·

## 4.1.3.2 加载运行 DSP 程序

#### 4.1.3.2.1 CCS 导入例程

CCS 软件导入示例工程 XQ\_NDK\_TCP\_UDP\_ECHO, 如下图所示: Maria Import CCS Eclipse Projects Select CCS Projects to Import Select a directory to search for existing CCS Eclipse projects. Select search-directory: D:\DSP\_6657\Demo\_XQ\_NDK\_TCP\_UDP\_ECHO Browse... O Select archive file: Browse.. Discovered projects: ☑ XQ\_NDK\_TCP\_UDP\_ECHO [D:\DSP\_6657\Demo\XQ\_NDK\_TCP\_UDP\_ECHO] Select All Deselect All Refresh Automatically import referenced projects found in same search-directory Copy projects into workspace Open Resource Explorer to browse a wide selection of example projects... (?) Finish Cancel CCS 示例工程导入后界面如下图所示: ✓ ☼ XQ NDK TCP UDP ECHO [Active - Debug] > & Binaries > M Includes > 🗁 Debug > c main.c > c platform osal.c > c tcpEcho.c > c udpEcho.c app.cfg

#### 4.1.3.2.2 下载运行 CCS 程序

下载 DSP 可执行文件 XQ\_NDK\_TCP\_UDP\_ECHO.out:

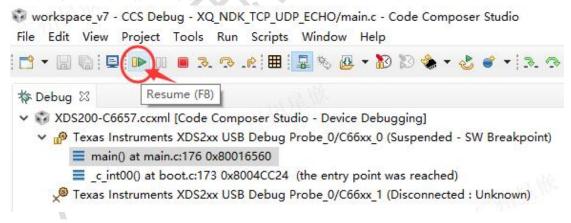

点击 Resume 运行 DSP 程序:

### 4.1.3.3 运行结果说明

# 4.1.3.3.1 DSP 程序运行结果

DSP 程序运行后, CCS 控制台打印如下图所示的信息:

```

■ Console 🏻

XDS200-C6657.ccxml:CIO

[C66xx 0]

Xines TCP/IP Stack 'TCP/UDP Echo' Application

emac_init: core 0, port 0, total number of channels/MAC addresses: 1/1

MAC addresses configured for channel 0:

00-35-FF-AF-BF-90

SGMII reset successful.....

SGMII config successful......

emac_open core 0 port 0 successfully

Registration of the EMAC Successful, waiting for link up ..

Service Status: DHCPC

: Enabled :

Service Status: DHCPC

: Enabled : Running : 000

Network Added: If-1:192.168.1.102

Service Status: DHCPC : Enabled : Running : 017

```

上图打印信息显示, DSP 网络链接成功, DSP 网络 MAC 地址为 00-35-FF-AF-BF-90, 分配 到的 IP 地址为 192.168.1.102。

#### 4.1.3.3.2 Ping 测试

打开测试电脑命令行运行窗口,并输入 ping 192.168.1.102 命令,然后回车,测试电脑 ping DSP 网络的效果:

```

Microsoft Windows [版本 10.0.19044.2130]

(c) Microsoft Corporation。保留所有权利。

C:\Users\Administrator>ping 192.168.1.102

正在 Ping 192.168.1.102 具有 32 字节的数据:

来自 192.168.1.102 的回复:字节=32 时间<1ms TTL=255

192.168.1.102 的回复:字节=32 时间=1ms TTL=255

192.168.1.102 的 Ping 统计信息:数据包:已发送=4,已接收=4,丢失=0(0% 丢失),往返行程的估计时间(以毫秒为单位):最短=0ms,最长=1ms,平均=0ms

C:\Users\Administrator>_

```

上图显示, 电脑能正常 ping 通 DSP 网络。

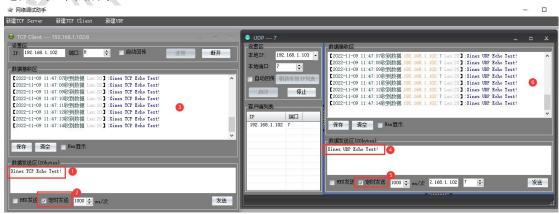

#### 4.1.3.3.3 网络调试助手测试

使用网络调试助手进行 TCP、UDP 通信测试。

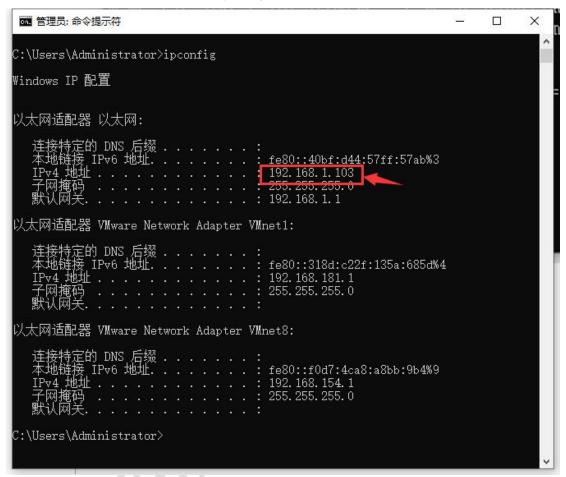

首先,在电脑命令行窗口使用 ipconfig 查看电脑的 IP 地址:

双击打开网络调试助手工具:

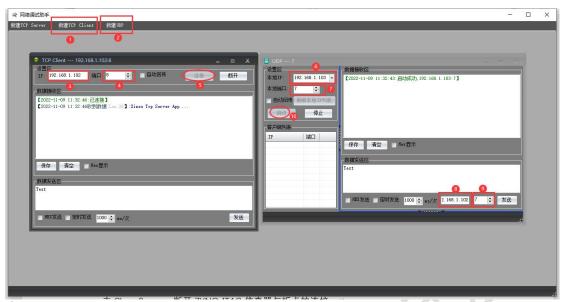

点击"新建 TCP Client"、"新建 UDP",然后按照下面①~⑩顺序进行参数设置:

- ① :新建 TCP Client,新建 TCP 客户端窗口;

- ② : 新建 UDP, 新建 UDP 客户端窗口;

- ③ :设置 TCP 主机 IP 地址,即 DSP 网络 IP 地址,通过 CCS 控制台窗口打印信息那里获取;

- ④ : 设置 TCP 主机 TCP 端口号,即 DSP 网络 TCP 端口号,DSP 程序里面固定设置为 8, 因此这里需填写 8;

- ⑤: 设置好 TCP 参数后,点击"连接",连接 TCP 主机。如果长时间没有 TCP 通信,那么 TCP 客户端会自动断开与 TCP 主机的连接,那么需要用户再次点击"连接"按钮以便继续 TCP 通信;

- ⑥ : 设置电脑 IP 地址,通过在电脑命令行窗口输入 ipconfig 命令获取;

- ⑦ : 设置电脑 UDP 端口号,随意设置,只要窗口不弹出错误就行;

- ⑧ : 设置 DSP 网络 IP 地址, 通过 CCS 控制台窗口打印信息那里获取;

- ⑨: 设置 DSP 网络 UDP 端口号, DSP 程序里面固定设置为 7, 因此这里需填写 7;

- ① : 设置好 UDP 参数后, 点击"启动"。

TCP、UDP 测试参数设置好后,下面开始 TCP、UDP 数据收发测试。在 TCP、UDP 测试窗口的数据发送区输入电脑网络发送数据,然后勾选上"定时发送"。如果 DSP 程序正常运行的话,那么会在数据接收区接收到 DSP 回显信息,即 DSP 将电脑发给它的网络数据原本返回,如下图所示:

## 4.1.3.4 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。 关闭网络调试助手。 最后,关闭板卡电源,实验结束。

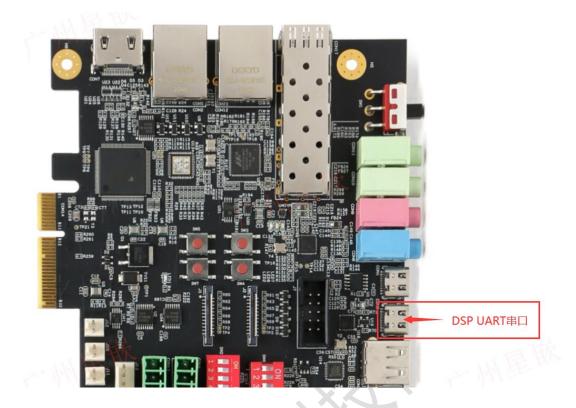

# 4.2DSP UARTO 串口通信

# 4.2.1 例程位置

DSP 例程保存在资料盘中的 Demo\DSP\XQ\_UART\_INT 文件夹下

# 4.2.2功能简介

实现 DSP 串口通信测试功能。

硬件设计上,使用的是 UARTO 串口。程序设计基于 UART 串口中断方式,实现串口数据回显功能。

# 4.2.3 例程使用

# 4.2.3.1 串口线缆连接

用 USB Type-C 线缆连接板卡上 DSP 串口至测试电脑:

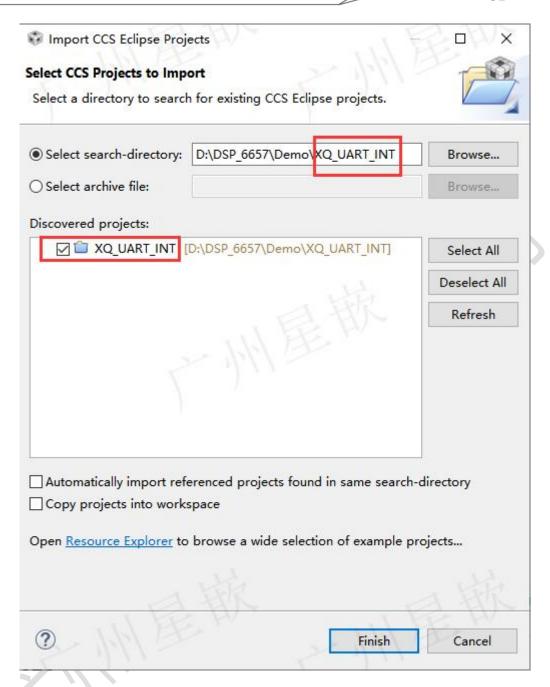

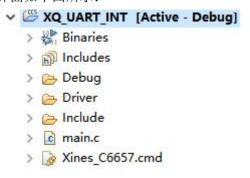

# 4.2.3.2 加载运行 DSP 程序

# 4.2.3.2.1 CCS 导入例程

CCS 软件导入示例工程 XQ\_UART\_INT,如下图所示:

— Xines

ccs 示例工程导入后界面如下图所示:

#### 4.2.3.2.2 下载运行 CCS 程序

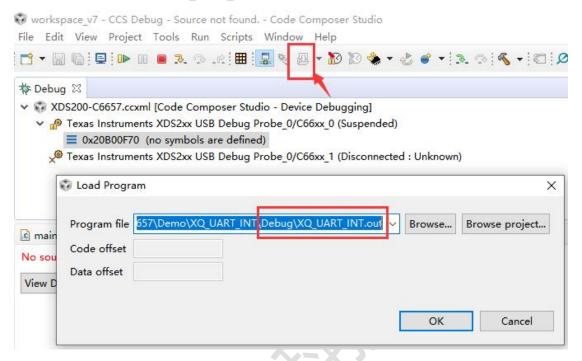

下载 DSP 可执行文件 XQ\_UART\_INT.out:

点击 Resume 运行 DSP 程序:

# 4.2.3.3 运行结果说明

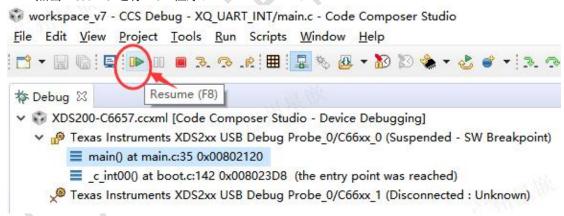

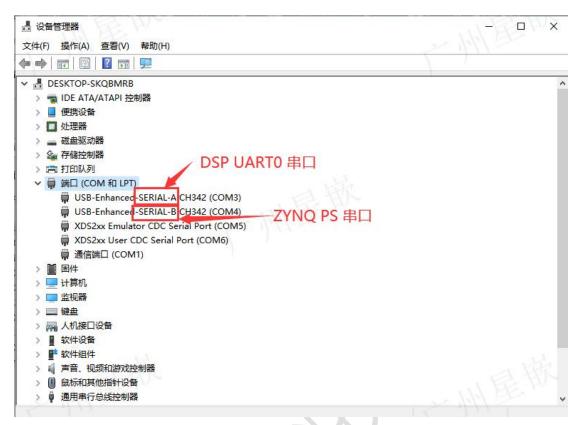

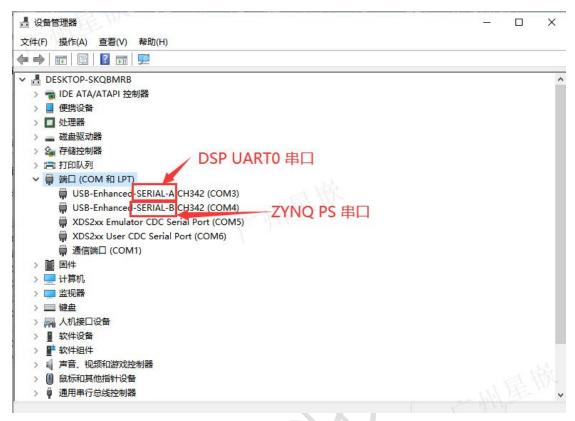

板卡上电,并通过设备管理器查看串口号。带 SERIAL-A 字样的为 DSP 端串口,带 SERIAL-B 字样的为 ZYNQ PS 串口,记住后面的 COM 编号,这里 DSP 串口编号为 COM3:

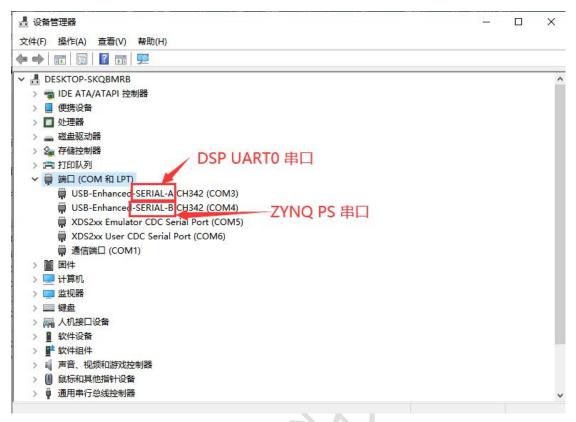

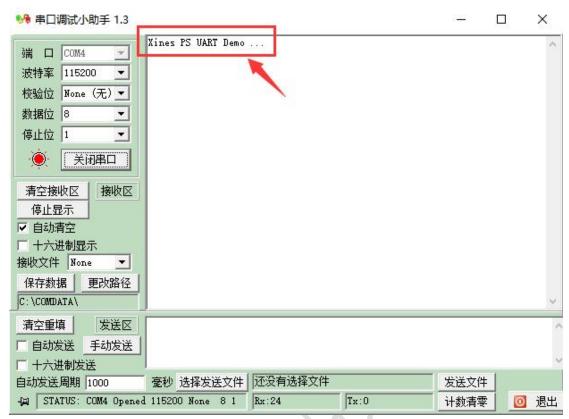

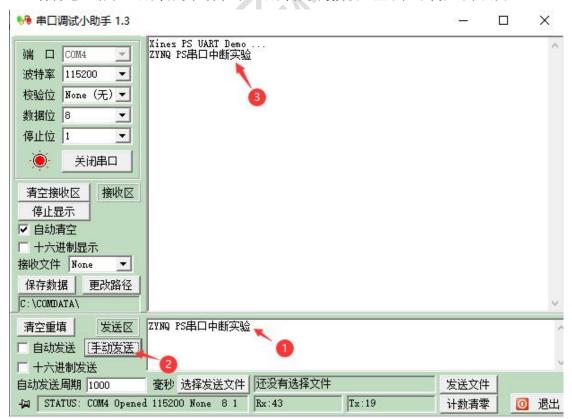

在 DSP 程序运行之前,打开串口调试助手,并设置串口参数,具体设置如下图①区域标识所示:

设置完串口参数后,在②位置点击"打开串口"。接着,在③位置输入串口发送数据,并勾选上④位置处的"自动发送",然后可以在⑤位置查看串口接收数据。串口调试助手将

串口数据发给 DSP, DSP 将接收到的串口数据原本返回给串口调试助手。

#### 4.2.3.4 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。 关闭串口调试助手。 最后,关闭板卡电源,实验结束。

## 4.3DSP GPIO LED 示例

# 4.3.1 例程位置

DSP 例程保存在资料盘中的 Demo\DSP\XQ GPIO LED 文件夹下。

# 4.3.2功能简介

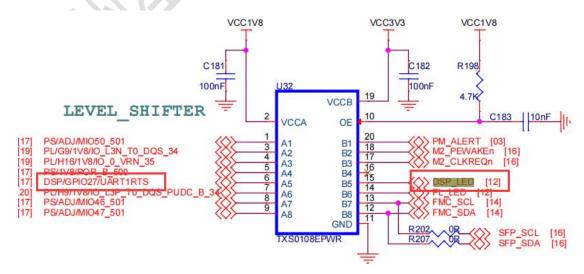

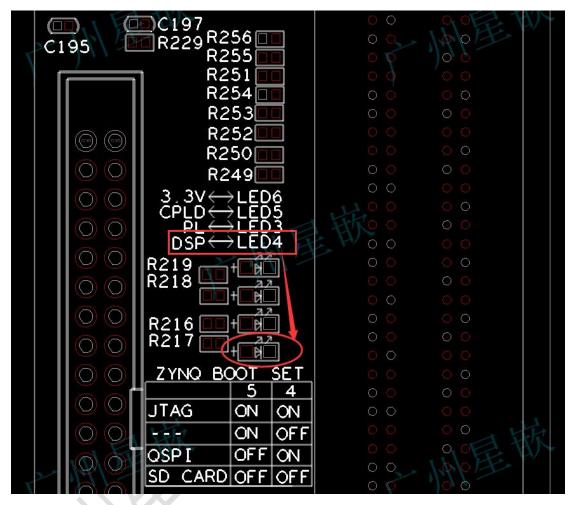

DSP 通过 GPIO 控制 LED 灯的亮、灭。具体控制的是底板上的 LED4 灯,原理图设计如下所示:

LED4 灯的控制信号 DSP\_LED 通过一颗电平转换芯片连接到 DSP 的 GPIO27 上,原理图部分如下图所示:

所以, DSP 程序设计时, 通过控制 GPIO27 来实现对底板上 LED4 灯的亮、灭操作。

# 4.3.3 例程使用

# 4.3.3.1 加载运行 DSP 程序

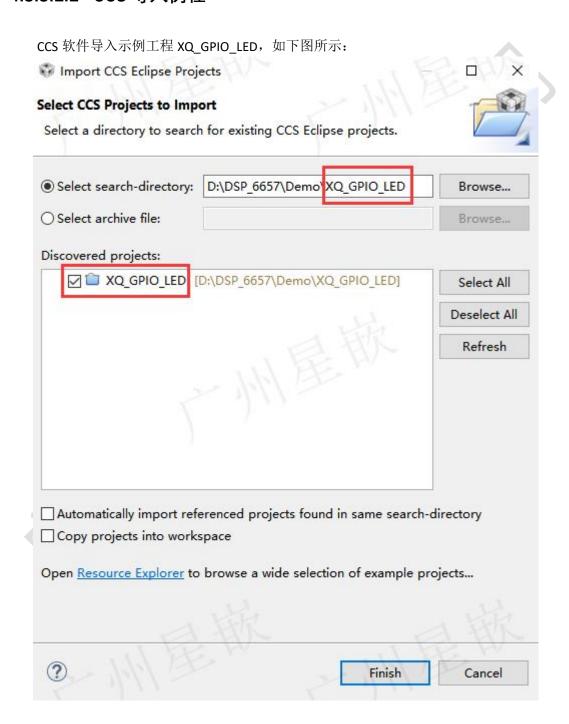

### 4.3.3.1.1 CCS 导入例程

CCS 示例工程导入后界面如下图所示:

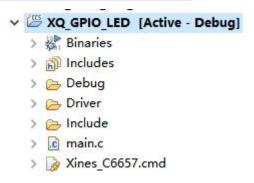

### 4.3.3.1.2 下载运行 CCS 程序

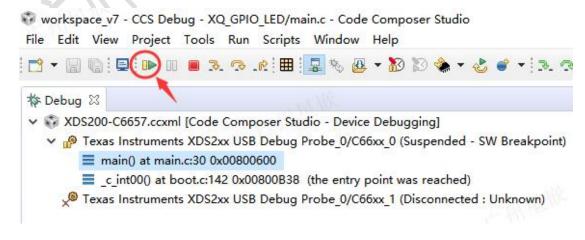

点击 Resume 运行 DSP 程序:

### 4.3.3.2 运行结果说明

DSP 程序运行起来后,如果程序正常运行的话,则可看到底板 LED4 灯会一亮一灭,快速闪烁。

LED4 灯在底板上的具体位置如下面两张图所示:

#### 4.3.3.3 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。 最后,关闭板卡电源,实验结束。

### 4.4DSP DDR3 内存读写测试

## 4.4.1 例程位置

DSP 例程保存在资料盘中的 Demo\DSP\XQ DDR3 Test 文件夹下。

# 4.4.2功能简介

DSP 外挂 2 颗 DDR3 颗粒,总容量 1Gbytes,总位宽 32bits。

本实验通过两种方式测试 DDR3 的读写,分别是: EDMA 方式和 DSP 核心直接读写方式,两种方式的 DDR3 读写测试如下图程序代码段标注位置所示:

```

/* main函数 */

void main()

int i;

// TSC初始化,用于时间测量

TSC_init();

// EDMA初始化

EDMA_init();

/*make DDR cacheable and prefetchable*/

for(i= 0; i< (DDREndAddress-DDRStartAddress)/16/1024/1024; i++)</pre>

gpCGEM_regs->MAR[(DDRStartAddress/16/1024/1024)+i]=1

(1<<CSL_CGEM_MARO_PFX_SHIFT);

// 设置缓存

CACHE_setL1PSize(CACHE_L1_32KCACHE);

CACHE_setL1DSize(CACHE_L1_32KCACHE);

CACHE_setL2Size(CACHE_OKCACHE);

tscl= TSCL;

tsch= TSCH;

printf("DDR3 Memory Test Start at %11d cycle\n", _itoll(tsch, tscl));

// 以EDMA方式对DDR3内存进行读写测试

KeyStone_memory_EDMA_test(DDRStartAddress, DDREndAddress, 1, "DDR3");

// DSP核心直接对DDR3内存进行读写测试

KeyStone_memory_test(DDRStartAddress, DDRStartAddress+512*1024, 1, "DDR3")

tscl= TSCL;

tsch= TSCH;

printf("DDR3 Memory test complete at %11d cycle\n", _itoll(tsch, tscl));

```

EDMA 方式测试时,对整个 DDR3 地址空间(1GB)进行读写测试, EDMA 测试 DDR3 地

址空间设置代码如下代码段所示:

.// DDR3测试起始地址和结束地址,地址空间1GB

!unsigned int DDRStartAddress = 0x80000000; !unsigned int DDREndAddress= 0xC0000000;

DSP 核心直接方式读写 DDR3 测试时,只测试其中的 512KB 空间:

```

73 // DSP核心直接对DDR3内存进行读写测试

74 KeyStone_memory_test(DDRStartAddress, DDRStartAddress+512*1024, 1, "DDR3");

```

# 4.4.3 例程使用

4.4.3.1 加载运行 DSP 程序

## 4.4.3.1.1 CCS 导入例程

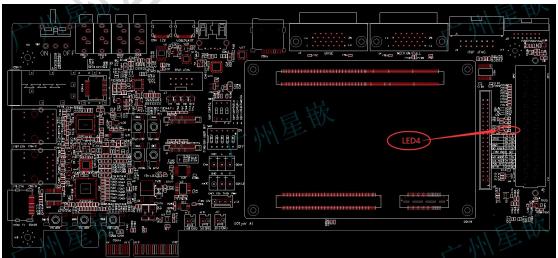

CCS 软件导入示例工程 XQ\_DDR3\_Test,如下图所示:

ccs 示例工程导入后界面如下图所示:

#### 4.4.3.1.2 下载运行 CCS 程序

下载 DSP 可执行文件 XQ\_DDR3\_Test.out:

点击 Resume 运行 DSP 程序:

#### 4.4.3.2 运行结果说明

首先以 EDMA 方式读写 DDR3 内存,往 DDR3 写测试数据,并读出对比。如果读写数据正确,则打印 Passed 字样,否则打印 Failed 字样,EDMA 方式测试通过后的打印信息如下图所示:

```

Console 🛭

[C66xx 0] DDR3 Memory Test Start at 113524 cycle

DDR3 memory test with EDMA at 123591 cycle

Passed Memory Fill Test from 0x80000000 to 0xc0000000 with pattern 0x 0 with EDMA CC0 TC0 Passed Memory Fill Test from 0x80000000 to 0xc0000000 with pattern 0xffffffffffffff with EDMA CC0 TC1

Passed Memory Fill Test from 0x80000000 to 0xc0000000 with pattern 0xaaaaaaaaaaaaaa with EDMA CC0 TC2

Passed Memory Fill Test from 0x80000000 to 0xc0000000 with pattern 0x555555555555555 with EDMA CC0 TC3

Passed Memory Address Test from 0x80000000 to 0xc0000000 with EDMA CC0 TC0

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

100000001

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xfffffffeffffffe

200000000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xffffffffffffffd

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

400000004

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xfff

ffbffffffb

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

800000008

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xfffff

1000000010

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xf

feffffffef

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xffffffffffffffff

Memory Bit Walking with EDMA CCO TC1 at 0x80000000 with pattern 0x

4000000040

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xfffff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

800000080

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xf

f7fffffff7f

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

10000000100

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

20000000200

Memory Bit Walking with EDMA CCO TC1 at 0x80000000 with pattern 0x 4000000400

40000000400

☐ Console ⊠

XDS200-C6657.ccxml:CIO

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

49999999499

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

80000000800

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xfffff7ffffffffffff

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

200000002000

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xffffdffffffffffffff

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

400000004000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

800000008000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

Memory Bit Walking with EDMA CCO TC3 at 0x80000000 with pattern 0x

2000000020000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

4000000040000

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xfffbfffffbffff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

20000000000000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 10000000100000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

20000000200000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 40000000400000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

80000000800000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 100000001000000

XDS200-C6657.ccxml:CIO

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 100000001000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x 200000002000000

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xfdffffffffffffff

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 40000004000000

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xfbffffffffffffffff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x 800000008000000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x2000000020000000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x4000000040000000

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xbffffffffffffffff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x8000000080000000

Passed Memory Bit Walking from 0x80000000 to 0xc0000000 with DMA

Failed Times:

```

接着,以 DSP 核心直接方式读写 DDR3 内存,往 DDR3 写测试数据,并读出对比。如果读写数据正确,则打印 Passed 字样,否则打印 Failed 字样,DSP 核心直接方式测试通过后的

#### 打印信息如下图所示:

#### 4.4.3.3 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。最后,关闭板卡电源,实验结束。

# 4.5DSP DDR3 初始化以及内存读写测试

# 4.5.1 例程位置

DSP 例程保存在资料盘中的 Demo\DSP\XQ DDR3 INIT TEST 文件夹下。

# 4.5.2功能简介

DSP 外挂 2 颗 DDR3 颗粒,总容量 1Gbytes,总位宽 32bits。

本实验不需要使用 Gel 文件去对 PLL 和 DDR3 外设进行初始化配置,而是在用户代码中实现对 PLL 和 DDR3 外设的初始化配置工作。初始化完成后,通过两种方式测试 DDR3 内存的读写,分别是: EDMA 方式和 DSP 核心直接读写方式。

主函数代码如下图所示:

```

main.c 🖾

49 int main(void)

50 {

51

int i;

52

// TSC初始化,用于时间测量

53

54

TSC_init();

55

56

// DSP core speed: 100*10/1=1000MHz

57

58

// XQTyer C6657 with 100MHz input for DDR

59

KeyStone_DDR_init(100, 64, 6, NULL);

60

- DDR3控制器外设初始化

61

// EDMA初始化

62

63

EDMA_init();

64

65

/*make DDR cacheable and prefetchable*/

66

for(i= 0; i< (DDREndAddress-DDRStartAddress)/16/1024/1024; i++)</pre>

67

gpCGEM_regs->MAR[(DDRStartAddress/16/1024/1024)+i]=1|

68

(1<<CSL_CGEM_MARO_PFX_SHIFT);

69

70

// 设置缓存

CACHE_setL1PSize(CACHE_L1_32KCACHE);

71

CACHE_setL1DSize(CACHE_L1_32KCACHE);

72

73

CACHE_setL2Size(CACHE_OKCACHE);

74

75

tscl= TSCL;

tsch= TSCH;

76

printf("DDR3 Memory Test Start at %lld cycle\n", _itoll(tsch, tscl));

77

78

DDR3内存读写测试

// 以EDMA方式对DDR3内存进行读写测试

79

KeyStone_memory_EDMA_test(DDRStartAddress, DDREndAddress, 1, "DDR3");

80

81

82

// DSP核心直接对DDR3内存进行读写测试

83

KeyStone_memory_test(DDRStartAddress, DDRStartAddress+512*1024, 1, "DDR3");

84

85

tscl= TSCL;

```

EDMA 方式测试时,对整个 DDR3 地址空间(1GB)进行读写测试,EDMA 测试 DDR3 地址空间设置代码如下代码段所示:

.// DDR3测试起始地址和结束地址,地址空间1GB

```

!unsigned int DDRStartAddress = 0x80000000;

!unsigned int DDREndAddress= 0xC0000000;

```

DSP 核心直接方式读写 DDR3 测试时,只测试其中的 512KB 空间:

```

73 // DSP核心直接对DDR3内存进行读写测试

74 KeyStone_memory_test(DDRStartAddress, DDRStartAddress+512*1024, 1, "DDR3");

```

# 4.5.3 例程使用

## 4.5.3.1 加载运行 DSP 程序

### 4.5.3.1.1 CCS 导入例程

CCS 示例工程导入后界面如下图所示:

#### 4.5.3.1.2 下载运行 CCS 程序

特别说明:本实验可以使用 Gel 文件,也可以不使用 Gel 文件。Gel 文件的设置在.ccxml目标配置文件中进行,如下图②位置所示的.ccxml目标配置文件中 Gel 文件设置,可以为空,也可以指定 Gel 文件位置:

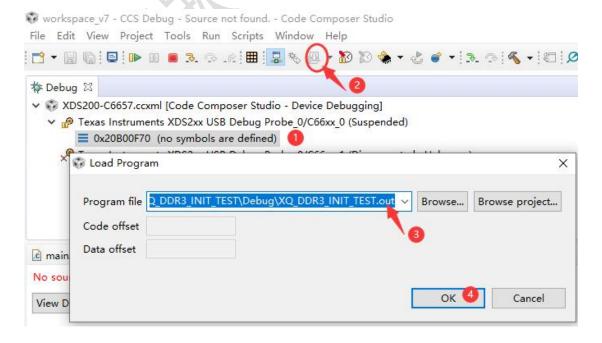

下载 DSP 可执行文件 XQ\_DDR3\_INIT\_TEST.out:

点击 Resume 运行 DSP 程序:

#### 4.5.3.2 运行结果说明

首先以 EDMA 方式读写 DDR3 内存,往 DDR3 写测试数据,并读出对比。如果读写数据正确,则打印 Passed 字样,否则打印 Failed 字样,EDMA 方式测试通过后的打印信息如下图所示:

```

XDS200-C6657.ccxml:CIC

[C66xx_0] Initialize DDR speed = 100.00MHzx64/6 = 1066.667MTS

DDR3 Memory Test Start at 11724702 cycle

DDR3 memory test with EDMA at 11734709 cycle

Passed Memory Fill Test from 0x80000000 to 0xc0000000 with pattern 0x

0 with EDMA CC0 TC0

Passed Memory Fill Test from 0x80000000 to 0xc0000000 with pattern 0xfffffffffffffff with EDMA CC0 TC1

Passed Memory Fill Test from 0x80000000 to 0xc0000000 with pattern 0xaaaaaaaaaaaaaa with EDMA CC0 TC2

Passed Memory Fill Test from 0x80000000 to 0xc0000000 with pattern 0x555555555555555 with EDMA CC0 TC3

Passed Memory Address Test from 0x80000000 to 0xc0000000 with EDMA CC0 TC0

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

100000001

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xfff

ffefffffffe

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

200000002

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xfff

ffffdffffffd

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

400000004

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xfff

ffffbffffffb

Memory Bit Walking with EDMA CCO TC3 at 0x80000000 with pattern 0x

80000008

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xf

ff7ffffff7

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

EDMA CC0 TC2 at 0x80000000 with pattern 0xf

Memory Bit Walking with

efffffffef

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

20000000000

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xf

fdfffffffdf

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

4000000040

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xf

fbffffffbf

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

8000000080

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xf

10000000100

EDMA CC0 TC1 at 0x80000000 with pattern 0x

Memory Bit Walking with

feffffffeff

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xfff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

200000000200

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xfff

ffdfffffffdff

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

40000000400

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xf

fbfffffffbff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

8000000800

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0x1

f7ffffffffffff

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x

100000001000

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xf

fefffffffefff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x

200000002000

```

```

□ Console ⊠

XDS200-C6657.ccxml:CIO

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x 2000000020000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 4000000040000

Memory Bit Walking with EDMA CCO TC3 at 0x80000000 with pattern 0x 8000000080000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 10000000100000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x 20000000200000

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 40000000400000

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xffbffffffbfffff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x 80000000800000

Memory Bit Walking with EDMA CCO TCO at 0x80000000 with pattern 0xff7ffffffffffffff

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 100000001000000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x 2000000020000000

Memory Bit Walking with EDMA CCO TCO at 0x80000000 with pattern 0xfdfffffffffffff

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x 400000004000000

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x 800000008000000

Memory Bit Walking with EDMA CCO TC1 at 0x80000000 with pattern 0x1000000010000000

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xefffffffffffffff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x2000000020000000

Memory Bit Walking with EDMA CC0 TC0 at 0x80000000 with pattern 0xdffffffffffffffff

Memory Bit Walking with EDMA CC0 TC1 at 0x80000000 with pattern 0x4000000040000000

Memory Bit Walking with EDMA CC0 TC2 at 0x80000000 with pattern 0xbfffffffbffffffff

Memory Bit Walking with EDMA CC0 TC3 at 0x80000000 with pattern 0x80000000800000000

Passed Memory Bit Walking from 0x80000000 to 0xc0000000 with DMA

Passed Times:

Failed Times:

```

接着,以 DSP 核心直接方式读写 DDR3 内存,往 DDR3 写测试数据,并读出对比。如果读写数据正确,则打印 Passed 字样,否则打印 Failed 字样,DSP 核心直接方式测试通过后的打印信息如下图所示:

```

DDR3 memory test at 470786837771 cycle

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0x

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0xaaaaaaaaaaaaaa

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0x555555555555555555

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0x31ccccccccccccc

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0x3333333300363630

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0x

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0x 81bbc900000000

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0xff00ff00ff00f

Passed Memory Fill Test from 0x80000000 to 0x80080000 with pattern 0x 80f3a000000001

Passed Memory Address Test from 0x80000000 to 0x80080000

Passed Memory Bit Walking from 0x80000000 to 0x80080000

Passed Times:

Failed Times:

2

DDR3 Memory test complete at 471225759895 cycle

```

### 4.5.3.3 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。最后,关闭板卡电源,实验结束。

## 4.6DSP IPC 核间通信之 NOTIFY

## 4.6.1 例程位置

DSP 例程保存在资料盘中的 Demo\DSP\XQ IPC NOTIFY 文件夹下。

# 4.6.2功能简介

IPC 组件可用于处理器多核之间的核间通信,通信内容可包含消息传递、数据流以及链表等,IPC 组件的运行是建立在 SYS/BIOS 基础之上的。

根据难易程度, IPC 有如下几种使用场景:

- 1) IPC 最简化使用场景: 该场景下, 处理器核心之间只运行通知机制, 即 Notify 通知。 Notify 通知可携带 32bits 的用户数据。Notify 通知事件可用于多个处理器核心之间 的简单同步。

- 2) 数据传输使用场景:相比于IPC 最简化使用场景,该场景增加了处理器核心之间链表元素传递功能。数据传输场景下,可通过共享内存或门来辅助实现处理器核心之间的同步。

- 3) 动态链表分配使用场景: 该场景下, 可从 heap 中动态添加或删减链表元素。

- 4) MessageQ 消息传递使用场景: 使用 MessageQ 模块在处理器核心之间传递消息。

本节实验内容使用 Notify 模块实现两个 DSP 核心之间的简单通知和 32bits 数据传递功能。

Notify 通知需要用到两个模块: Notify module 和 MultiProc module,其中 Notify module 提供 API 供用户调用,Notify module 需要使用 MultiProc module 中配置的属性,MultiProc module 可静态配置或动态配置:

本实验两个 DSP 核心使用同一个程序镜像,通过核心号区分哪些代码运行在核心 0,哪些代码运行在核心 1。首先,需要调用 lpc\_start()函数,与其他核心进行同步;然后注册 Notify 通知事件,Notify 事件注册时需要关联核心号(即本核心需要响应哪个核心发过来的 Notify 事件)、中断线、事件 ID 以及 Notify 事件回调函数等参数,具体实现如下 main 函数里面的代码段所示:

```

Int main(Int argc, Char* argv[])

Int status;

UInt numProcs = MultiProc_getNumProcessors();

Determine which processors Notify will communicate with based on the

local MultiProc id. Also, create a processor-specific Task.

srcProc = ((MultiProc_self() - 1 + numProcs) % numProcs);

dstProc = ((MultiProc_self() + 1) % numProcs);

System_printf("main: MultiProc id = %d\n", MultiProc_self());

System_printf("main: MultiProc name = %s\n",

MultiProc_getName(MultiProc_self()));

Ipc start() calls Ipc attach() to synchronize all remote processors

because 'Ipc.procSync' is set to 'Ipc.ProcSync ALL' in *.cfg

status = Ipc_start(); 🕕 与远程处理器核心进行同步

if (status < 0) {

System_abort("Ipc_start failed\n");

本核心需要响应的远程处理器核心编号

Register call back with Notify. It will be called when the processor

with id = srcProc sends event number EVENTID to this processor.

Notify中断信号线编号

Notify事件ID号

*/ ② 注册Notify事件

status = Notify_registerEvent(srcProc, INTERRUPT_LINE, EVENTID,

(Notify_FnNotifyCbck)cbFxn, NULL);

if (status < 0) {

System_abort("Notify_registerEvent failed\n");

}

BIOS_start();

```

Notify 中断信号线、Notify 事件 ID 号、远程处理器核心编号三者共同决定 Notify 事件的响应。如果远程处理器核心发给本地处理器核心的 Notify 事件中的 Notify 中断信号线、Notify 事件 ID 号、远程处理器核心编号均与本地注册的 Notify 事件参数匹配,那么本地核心处理器就会响应远程发过来的 Notify 事件,调用 Notify 事件回调函数执行。

本实验的 Notify 事件回调函数代码实现如下:

Notify 事件到来后,如果远程处理器核心编号、Notify 中断信号线、Notify 事件 ID 号三个参数与本地注册的 Notify 事件参数匹配(对应回调函数中 procld、lineld、eventId 三个形参),那么 Notify 事件回调函数开始执行,记录远程处理器核心编号和 32bits 的附带数据,然后 post 信号量 semHandle。

程序里面静态创建了一个任务 tsk0,对应的任务函数为 tsk0\_func, tsk0\_func 中核心 0 代码实现部分如下图所示:

```

Void tsk0_func(UArg arg0, UArg arg1)

{

Int i = 1;

Int status;

if (MultiProc_self() == 0) {

// 核心@运行程序

while (i < NUMLOOPS) {

/* Send an event to the next processor */

// ipc notify发送至ID号为dspProc的处理器, ipc notify附带发送的payload数据为i

status = Notify_sendEvent(dstProc, INTERRUPT_LINE, EVENTID, i,

/* Continue until remote side is up */

if (status < 0) {</pre>

continue;

System_printf("Sent ipc notify to %s with payload = %d\n",

MultiProc_getName(dstProc), i);

/* Wait to be released by the cbFxn posting the semaphore */

// 等待核心1 post 信号量

Semaphore_pend(semHandle, BIOS_WAIT_FOREVER);

System_printf("Received ipc notify from %s with payload = %d\n",

MultiProc_getName(recvProcId), recvPayload);

/* increment for next iteration */

}

else { // 核心1运行程序

```

核心 0 调用 Notify\_sendEvent 函数,往核心 1 发送 Notify 事件,附带 32bits 数据,数据内容为 i,即循环次数。然后,核心 0 等待核心 1 发布信号量 semHandle,一旦等到核心 1 发布信号量 semHandle,则进入下一次循环,如此循环执行,直到指定循环次数结束。

tsk0\_func 中核心 1 代码实现部分如下图所示:

```

else { // 核心1运行程序

while (i < NUMLOOPS) {

/* wait forever on a semaphore, semaphore is posted in callback */

// 等待核心@ post 信号量

Semaphore_pend(semHandle, BIOS_WAIT_FOREVER);

System_printf("Received ipc notify from %s with payload = %d\n",

MultiProc_getName(recvProcId), recvPayload);

/* Send an event to the next processor */

// ipc notify发送至ID号为dspProc的处理器, ipc notify附带发送的payload数据为i+100

status = Notify_sendEvent(dstProc, INTERRUPT_LINE, EVENTID, i+100,

TRUE);

if (status < 0) {

System_abort("sendEvent failed\n");

}

System_printf("Sent ipc notify to %s with payload = %d\n",

MultiProc_getName(dstProc), i+100);

/* increment for next iteration */

i++;

}

}

System_printf("Test completed\n");

BIOS_exit(0);

} <

```

首先,核心 1 等待核心 0 发布信号量 semHandle,一旦等到核心 0 发布信号量 semHandle,核心 1 调用 Notify\_sendEvent 函数,往核心 0 发送 Notify 事件,附带 32bits 数据,数据内容为 i+100,即循环次数+100。然后,进入下一次循环,如此循环执行,直到指定循环次数结束。

# 4.6.3 例程使用

# 4.6.3.1 加载运行 DSP 程序

# 4.6.3.1.1 CCS 导入例程

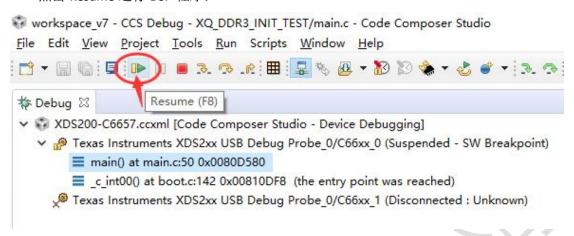

CCS 软件导入示例工程 XQ IPC NOTIFY, 如下图所示:

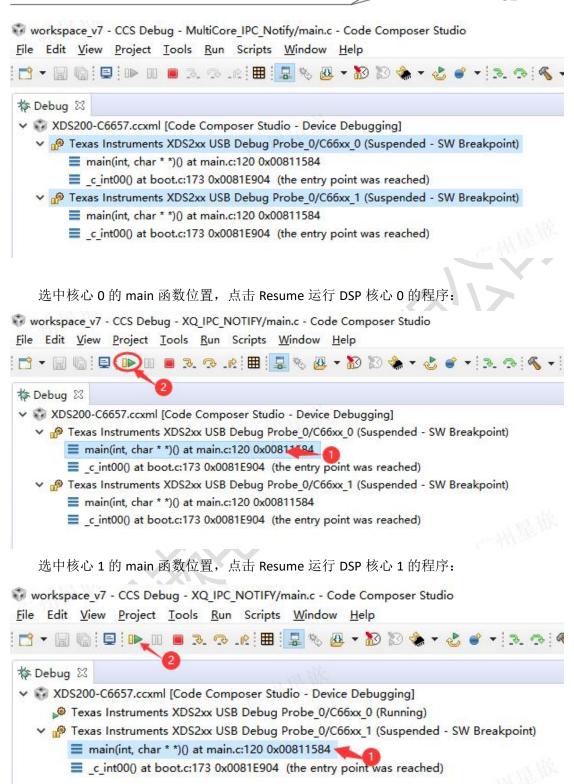

#### 4.6.3.1.2 下载运行 CCS 程序

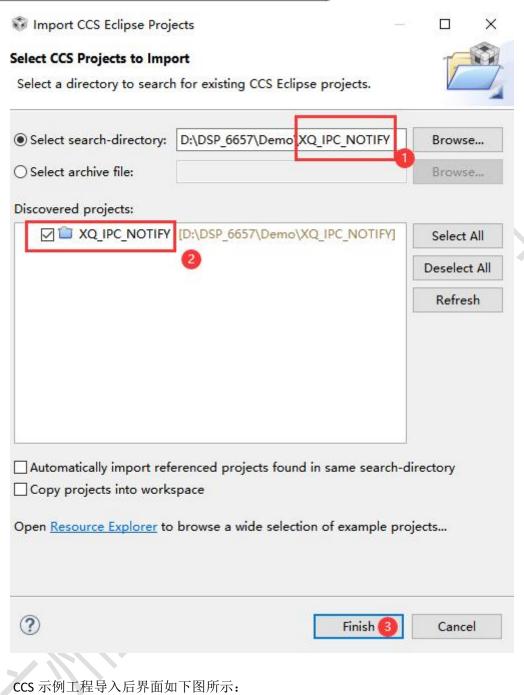

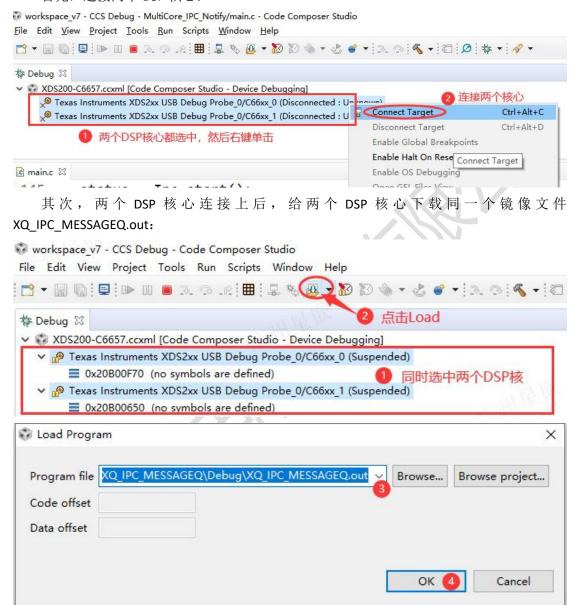

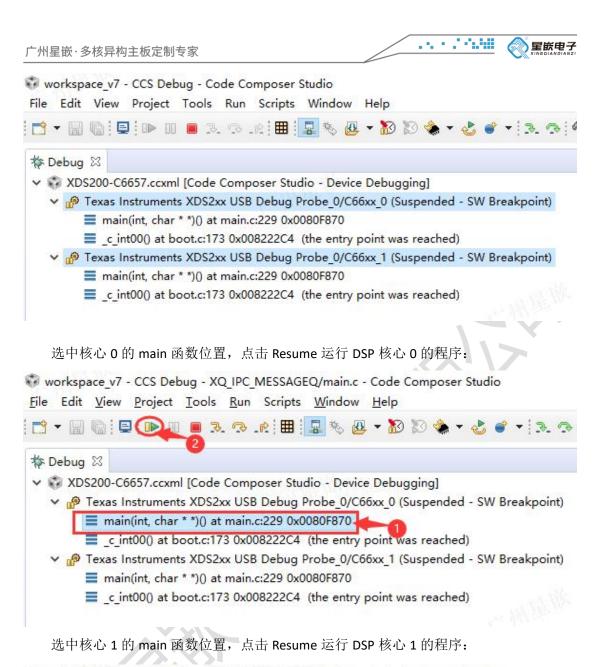

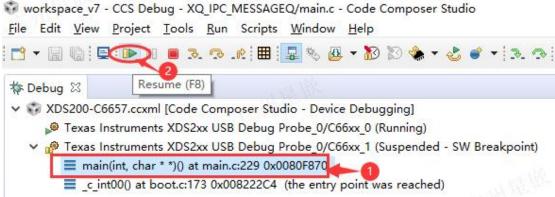

此实验需要连接 DSP 的两个核心,并给这两个 DSP 核心下载同一个镜像文件。 首先,连接两个 DSP 核心:

两个 DSP 核心均下载完 DSP 可执行镜像文件 XQ\_IPC\_NOTIFY.out 后的界面如下图所示:

# 4.6.3.2 运行结果说明

CCS Console 窗口打印程序运行结果。下面,首先对部分打印信息进行解读,然后附带给出程序运行产生的所有打印信息。

#### 部分打印信息解读:

核心 0 给核心 1 发送 Notify 通知事件,通知事件附带用户数据 1, Console 打印信息如下示例所示:

#### [C66xx\_0] Sent ipc notify to CORE1 with payload = 1

核心 1 收到核心 0 发过来的 Notify 通知事件后,将收到的附带数据以及谁发过来的这些信息也打印出来,如下示例所示:

[C66xx\_1] main: MultiProc id = 1

main: MultiProc name = CORE1

Received ipc notify from CORE0 with payload = 1

Sent ipc notify to CORE0 with payload = 101

核心 1 给核心 0 发送 Notify 通知事件,通知事件附带用户数据 101, Console 打印信息如下示例所示:

[C66xx\_1] main: MultiProc id = 1

main: MultiProc name = CORE1

Received ipc notify from CORE0 with payload = 1

Sent ipc notify to CORE0 with payload = 101

[C66xx\_0] Sent ipc notify to CORE1 with payload = 1

核心 0 收到核心 1 发过来的 Notify 通知事件后,将收到的附带数据以及谁发过来的这些信息也打印出来,如下示例所示:

[C66xx\_0] Sent ipc notify to CORE1 with payload = 1

Received ipc notify from CORE1 with payload = 101

Sent ipc notify to CORE1 with payload = 2

#### 程序运行产生的所有打印信息:

IPC 核间 Notify 程序运行结果的全部打印信息如下图所示:

■ Console 器

```

XDS200-C6657.ccxml:CIO

```

```

[C66xx_0] main: MultiProc id = 0

main: MultiProc name = CORE0

[C66xx 1] main: MultiProc id = 1

main: MultiProc name = CORE1

Received ipc notify from CORE0 with payload = 1

Sent ipc notify to COREO with payload = 101

[C66xx_0] Sent ipc notify to CORE1 with payload = 1

Received ipc notify from CORE1 with payload = 101

Sent ipc notify to CORE1 with payload = 2

[C66xx_1] Received ipc notify from COREO with payload = 2

Sent ipc notify to COREO with payload = 102

[C66xx_0] Received ipc notify from CORE1 with payload = 102

Sent ipc notify to CORE1 with payload = 3

[C66xx_1] Received ipc notify from COREO with payload = 3

Sent ipc notify to COREO with payload = 103

[C66xx_0] Received ipc notify from CORE1 with payload = 103

Sent ipc notify to CORE1 with payload = 4

[C66xx_1] Received ipc notify from COREO with payload = 4

Sent ipc notify to COREO with payload = 104

[C66xx_0] Received ipc notify from CORE1 with payload = 104

Sent ipc notify to CORE1 with payload = 5

[C66xx_1] Received ipc notify from COREO with payload = 5

Sent ipc notify to COREO with payload = 105

[C66xx_0] Received ipc notify from CORE1 with payload = 105

Sent ipc notify to CORE1 with payload = 6

[C66xx_1] Received ipc notify from COREO with payload = 6

Sent ipc notify to COREO with payload = 106

[C66xx_0] Received ipc notify from CORE1 with payload = 106

Sent ipc notify to CORE1 with payload = 7

[C66xx_1] Received ipc notify from COREO with payload = 7

Sent ipc notify to COREO with payload = 107

[C66xx_0] Received ipc notify from CORE1 with payload = 107

Sent ipc notify to CORE1 with payload = 8

[C66xx 1] Received ipc notify from CORE0 with payload = 8

Sent ipc notify to COREO with payload = 108

[C66xx 0] Received ipc notify from CORE1 with payload = 108

Sent ipc notify to CORE1 with payload = 9

[C66xx_1] Received ipc notify from CORE0 with payload = 9

Sent ipc notify to COREO with payload = 109

Test completed

[C66xx_0] Received ipc notify from CORE1 with payload = 109

Test completed

```

#### 4.6.3.3 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。最后,关闭板卡电源,实验结束。

# 4.7DSP IPC 核间通信之 MessageQ

## 4.7.1 例程位置

DSP 例程保存在资料盘中的 Demo\DSP\XQ\_IPC\_MESSAGEQ 文件夹下。

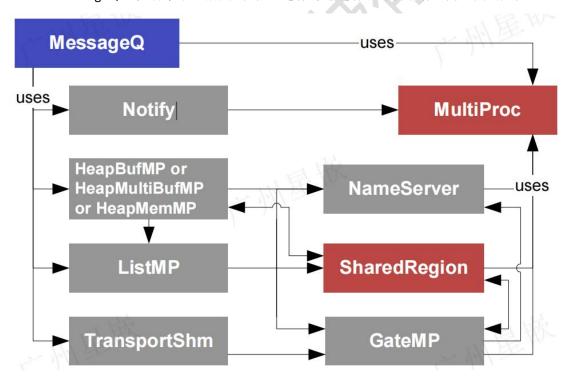

## 4.7.2功能简介

本实验使用 IPC MessageQ 模块实现 DSP 核心之间的相互通信。 IPC MessageQ 通信场景下,所用到的 IPC 模块以及模块之间调用关系如下图所示:

用户应用程序只需配置 MultiProc 和 SharedRegion 模块,然后调用 MessageQ 模块提供的 API 函数即可。像上图所示的灰色模块不需用户去手动配置,而是由 lpc\_start() API 函数自动配置。

本实验 SharedRegion 模块配置使用静态方式配置,即在.cfg 配置文件中进行 SharedRegion 模块配置。SharedRegion 模块配置共享内存区域查找表项,以便各处理器利用此查找表项对共享内存区域进行访问。配置内容包括:查找表序号、共享内存区域基地址 (base)/大小(len)、负责共享内存区域管理的处理器核心号(ownerProcld)、该共享内存区域是否有效(isValid)以及该共享内存区域名称(name),具体实现如下图所示:

```

@ main.c

app.cfg &

63/* BIOS/XDC modules */

64 var BIOS

= xdc.useModule('ti.sysbios.BIOS');

65 BIOS.heapSize

= 0x8000;

66 var Task

= xdc.useModule('ti.sysbios.knl.Task');

67

68 var tsk0 = Task.create('&tsk0 func');

69 tsk0.instance.name = "tsk0";

71/* Synchronize all processors (this will be done in Ipc_start) */

72 Ipc.procSync = Ipc.ProcSync_ALL;

74/* Shared Memory base address and length */

75 var SHAREDMEM

= 0x0C000000;

76 var SHAREDMEMSIZE

= 0 \times 00100000;

77

78/*

79 * Need to define the shared region. The IPC modules use this

80 * to make portable pointers. All processors need to add this

81 * call with their base address of the shared memory region.

82 * If the processor cannot access the memory, do not add it.

84 var SharedRegion = xdc.useModule('ti.sdo.ipc.SharedRegion');

85 SharedRegion.setEntryMeta(0,

86

{ base: SHAREDMEM,

87

len:

SHAREDMEMSIZE,

88

ownerProcId: 0,

89

isValid: true,

name: "DDR3 RAM",

90

91

});

```

MessageQ 实验示例程序 main 函数里面只调用了 lpc\_start()函数,实现各处理器之间的同步:

```

Int main(Int argc, Char* argv[])

{

Int status;

nextProcId = (MultiProc_self() + 1) % MultiProc_getNumProcessors();

/* Generate queue names based on own proc ID and total number of procs */

System_sprintf(localQueueName, "%s", MultiProc_getName(MultiProc_self()));

System_sprintf(nextQueueName, "%s", MultiProc_getName(nextProcId));

Ipc_start() calls Ipc_attach() to synchronize all remote processors

* because 'Ipc.procSync' is set to 'Ipc.ProcSync_ALL' in *.cfg

status = Ipc_start();

if (status < 0) {

System_abort("Ipc_start failed\n");

}

BIOS start();

return (0);

}

其余 IPC 任务操作放在了一个任务函数里面实现:

```

— Xines —

```

Allocates a message and ping-pongs the message around the processors.

* A local message queue is created and a remote message queue is opened.

Messages are sent to the remote message queue and retrieved from the

local MessageQ.

Void tsk0_func(UArg arg0, UArg arg1)

pMessageQ_UserMsg msg;

MessageQ_Handle messageQ;

MessageQ_QueueId remoteQueueId;

status;

UInt16

msgId = 0;

HeapBufMP_Handle

heapHandle;

HeapBufMP_Params

heapBufParams;

if (MultiProc_self() == 0) { /* 核心 运行代码*/

Create the heap that will be used to allocate messages.

HeapBufMP_Params_init(&heapBufParams);

heapBufParams.regionId

heapBufParams.name

= HEAP_NAME;

= 1;

heapBufParams.numBlocks

= sizeof(MessageQ_MsgHeader);

heapBufParams.blockSize

heapHandle = HeapBufMP_create(&heapBufParams);

if (heapHandle == NULL) {

System_abort("HeapBufMP_create failed\n" );

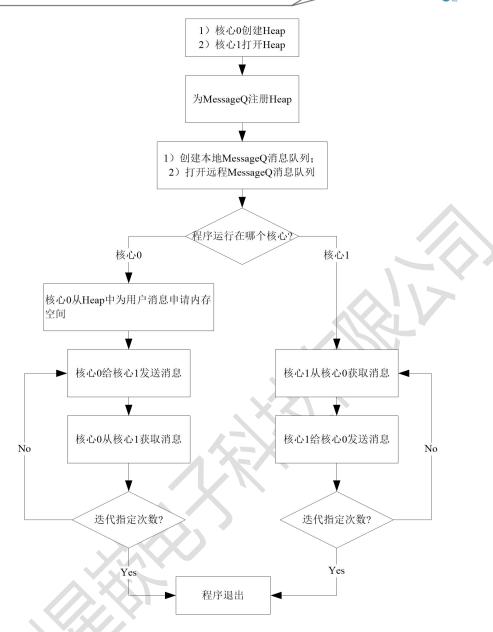

tsk0_func 任务函数实现的程序流程图如下图所示:

```

– Xines

# 4.7.3 例程使用

# 4.7.3.1 加载运行 DSP 程序

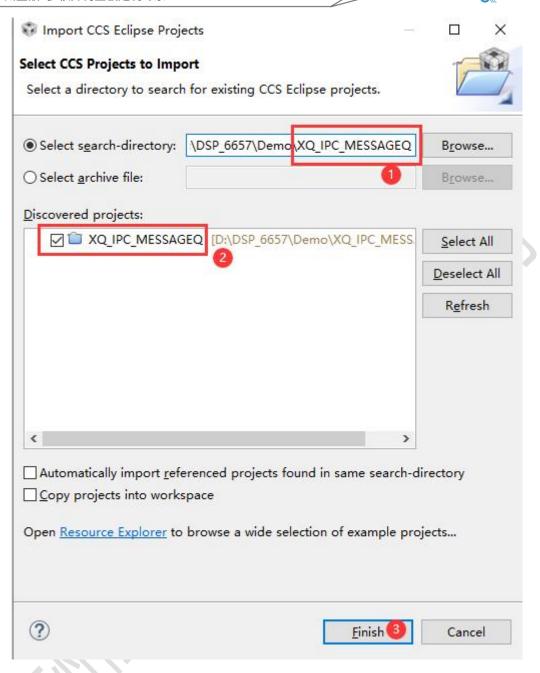

## 4.7.3.1.1 CCS 导入例程

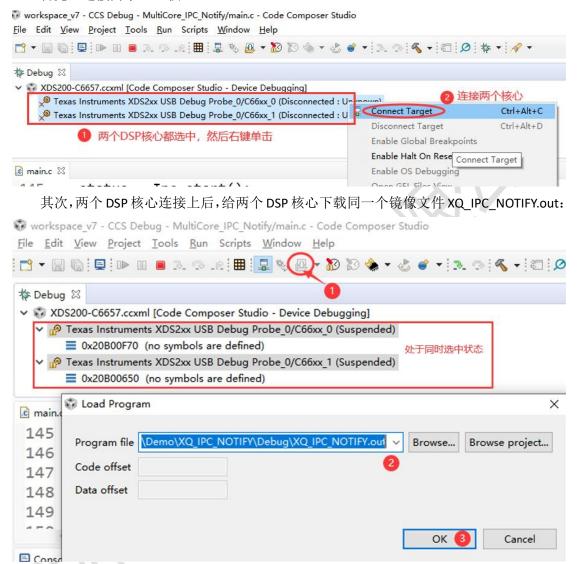

CCS 软件导入示例工程 XQ\_IPC\_MESSAGEQ,如下图所示:

ccs 示例工程导入后界面如下图所示:

#### 4.7.3.1.2 下载运行 CCS 程序

此实验需要连接 DSP 的两个核心,并给这两个 DSP 核心下载同一个镜像文件。 首先,连接两个 DSP 核心:

两个 DSP 核心均下载完 DSP 可执行镜像文件 XQ\_IPC\_MESSAGEQ.out 后的界面如下图所示:

## 4.7.3.2 运行结果说明

CCS Console 窗口打印程序运行结果。下面,首先对部分打印信息进行解读,然后附带

给出程序运行产生的所有打印信息。

#### 部分打印信息解读:

核心 0 从核心 1 那获得消息, 消息 ID 为 1, 消息数据为 201; 核心 0 给核心 1 发送消息, 消息 ID 为 2, 消息数据为 102, Console 打印信息如下示例所示:

[C66xx\_0] Received a message from CORE1: Message ID = 1, Message data = 201

Sent a message to CORE1: Message ID = 2, Message data = 102

核心 1 从核心 0 那获得消息,消息 ID 为 2,消息数据为 102;核心 1 给核心 0 发送消息,消息 ID 为 2,消息数据为 202, Console 打印信息如下示例所示:

[C66xx\_1] Received a message from COREO: Message ID = 2, Message data = 102

Sent a message to COREO: Message ID = 2, Message data = 202

#### 程序运行产生的所有打印信息:

IPC 核间 MessageQ 程序运行结果的全部打印信息如下图所示:

```

XDS200-C6657.ccxml:CIO

[C66xx_1] Start the main loop

[C66xx 0] Start the main loop

Sent a message to CORE1: Message ID = 1, Message data = 101

[C66xx_1] Received a message from COREO: Message ID = 1, Message data = 101

Sent a message to COREO: Message ID = 1, Message data = 201

[C66xx_0] Received a message from CORE1: Message ID = 1, Message data = 201

Sent a message to CORE1: Message ID = 2, Message data = 102

[C66xx_1] Received a message from CORE0: Message ID = 2, Message data = 102

Sent a message to COREO: Message ID = 2, Message data = 202

[C66xx 0] Received a message from CORE1: Message ID = 2, Message data = 202

Sent a message to CORE1: Message ID = 3, Message data = 103

[C66xx_1] Received a message from COREO: Message ID = 3, Message data = 103

Sent a message to COREO: Message ID = 3, Message data = 203

[C66xx_0] Received a message from CORE1: Message ID = 3, Message data = 203

Sent a message to CORE1: Message ID = 4, Message data = 104

[C66xx_1] Received a message from CORE0: Message ID = 4, Message data = 104

Sent a message to COREO: Message ID = 4, Message data = 204

[C66xx_0] Received a message from CORE1: Message ID = 4, Message data = 204

Sent a message to CORE1: Message ID = 5, Message data = 105

[C66xx_1] Received a message from COREO: Message ID = 5, Message data = 105

Sent a message to COREO: Message ID = 5, Message data = 205

[C66xx_0] Received a message from CORE1: Message ID = 5, Message data = 205

Sent a message to CORE1: Message ID = 6, Message data = 106

[C66xx_1] Received a message from CORE0: Message ID = 6, Message data = 106

Sent a message to COREO: Message ID = 6, Message data = 206

[C66xx_0] Received a message from CORE1: Message ID = 6, Message data = 206

Sent a message to CORE1: Message ID = 7, Message data = 107

[C66xx_1] Received a message from CORE0: Message ID = 7, Message data = 107

Sent a message to COREO: Message ID = 7, Message data = 207

[C66xx_0] Received a message from CORE1: Message ID = 7, Message data = 207

Sent a message to CORE1: Message ID = 8, Message data = 108

[C66xx_1] Received a message from CORE0: Message ID = 8, Message data = 108

Sent a message to COREO: Message ID = 8, Message data = 208

[C66xx_0] Received a message from CORE1: Message ID = 8, Message data = 208

Sent a message to CORE1: Message ID = 9, Message data = 109

```

[C66xx\_1] Received a message from CORE0: Message ID = 9, Message data = 109 Sent a message to CORE0: Message ID = 9, Message data = 209 [C66xx\_0] Received a message from CORE1: Message ID = 9, Message data = 209 Sent a message to CORE1: Message ID = 10, Message data = 110 [C66xx\_1] Received a message from CORE0: Message ID = 10, Message data = 110 Sent a message to CORE0: Message ID = 10, Message data = 210 The test is complete [C66xx\_0] Received a message from CORE1: Message ID = 10, Message data = 210 The test is complete

#### 4.7.3.3 退出实验

CCS 软件窗口上,点击 Terminate 断开 DSP 仿真器与板卡的连接。 最后,关闭板卡电源,实验结束。

# 5 ZYNQ PL 单独例程

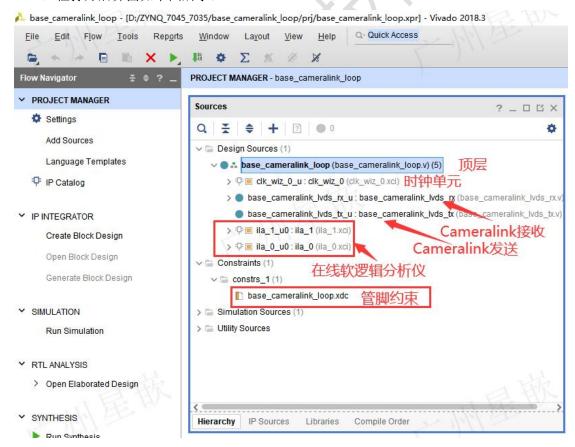

## 5.1ZYNQPL Cameralink 回环例程

## 5.1.1 例程位置

ZYNQ 例程保存在资料盘中的 Demo\ZYNQ\PL\base\_cameralink\_loop\prj 文件夹下。

## 5.1.2功能简介

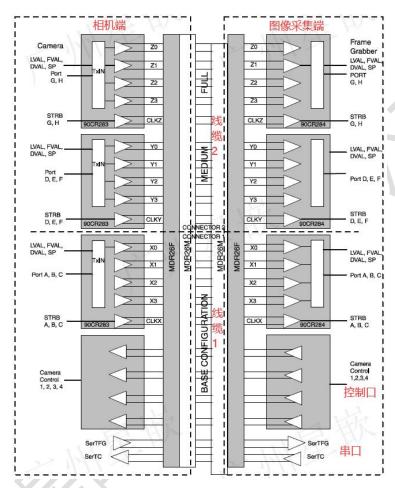

Cameralink 回环例程将 J3、J4 当作两个独立的 Base Cameralink 接口使用,一个接收,另一个发送。

Cameralink 接收端,利用 Xilinx ISERDESE2 原语进行串/并转换,将 LVDS 串行数据转换成 28bit 的 cameralink 并行数据。解串后的并行数据通过 ila 进行在线分析和查看,并实时检测并行数据是否有误码。

Cameralink 发送端,利用 Xilinx OSERDESE2 原语进行并/串转换,将本地 28bit cameralink 并行数据串行化为 LVDS 数据发送出去。

## 5.1.3 Cameralink 接口时序说明

### 5.1.3.1 Cameralink 三种配置模式

Base 模式: 只需一根 Cameralink 线缆; 4 对差分数据、1 对差分时钟;

Medium 模式: 需要两根 Cameralink 线缆; 8 对差分数据、2 对差分时钟;

Full 模式: 需要两根 Cameralink 线缆; 12 对差分数据、3 对差分时钟。

各种模式下,统一都包含一组控制口和一组串口。控制口有 4 根信号,用于图像采集端对相机的 IO 控制; 串口用于图像采集端对相机参数的配置。

## 5.1.3.2 单路差分数据与时钟之间时序关系

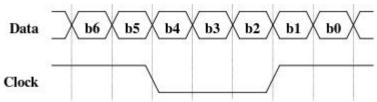

单路 Cameralink 差分数据与随路的差分像素时钟之间的时序关系如下图所示:

一个时钟周期内传输 7bits 串行数据,首先传输串行数据的最高位,最后传输串行数据的最低位。7bits 数据起始于像素时钟高电平的中间位置,即数据的最高位在 Clock 高电平的中间时刻开始传输。

Clock 高电平时间比 Clock 低电平时间多一个 bit 位。

## 5.1.3.3 通道传输数据与图像数据映射关系

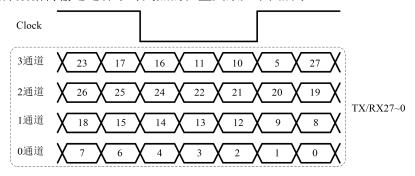

1 路差分数据通道上,一个 Clock 像素时钟周期传输 7bits 串行数据,那么 4 路差分数据通道总共就是 4\*7bits=28bits,我们称这 28bits 数据为并行数据,为了方便描述,这 28bits 数据记为 TX/RX27~0。Cameralink Base 模式下,这 28bits 数据与图像行/场同步/数据有效标记、图像数据的映射关系如下图所示:

| TX/RX24 | (A. 14)   | LVAL   |       |

|---------|-----------|--------|-------|

| 1       | L PROLET  |        |       |

| TX/RX25 | 1         | FVAL   |       |

| TX/RX26 |           | DVAL   |       |

| TX/RX23 |           | Spare  |       |

| TX/RX0  |           | PortA0 |       |

| TX/RX1  |           | PortA1 |       |

| TX/RX2  |           | PortA2 |       |

| TX/RX3  |           | PortA3 |       |

| TX/RX4  | 28bits    | PortA4 |       |

| TX/RX6  | 并行数据      | PortA5 |       |

| TX/RX27 |           | PortA6 |       |

| TX/RX5  |           | PortA7 |       |

| TX/RX7  |           | PortB0 |       |

| TX/RX8  | 1115      | PortB1 |       |

| TX/RX9  | > 1/1/1/2 | PortB2 |       |

| TX/RX12 | /         | PortB3 |       |

| TX/RX13 |           | PortB4 |       |

| TX/RX14 |           | PortB5 |       |

| TX/RX10 |           | PortB6 |       |

| TX/RX11 |           | PortB7 |       |

| TX/RX15 |           | PortC0 |       |

| TX/RX18 |           | PortC1 |       |

| TX/RX19 |           | PortC2 |       |

| TX/RX20 |           | PortC3 |       |

| TX/RX21 |           | PortC4 | 10.7% |

| TX/RX22 |           | PortC5 | HR    |

| TX/RX16 |           | PortC6 | : 14/ |

| TX/RX17 | >         | PortC7 |       |

TX/RX24 映射为行同步标记 LVAL, TX/RX25 映射为场同步标记 FVAL, TX/RX26 映射为图像数据有效标记 DVAL, TX/RX23 未使用,其余位对应图像数据。

## 5.1.3.4 28 位并行数据与 4 路差分数据传输通道之间的映射关系

上述 28 位并行数据是如何通过 4 路差分数据传输通道进行传输的呢? 28 位并行数据映射到 4 路差分数据传输通道各个时刻点的位置关系如下图所示:

– Xines ·

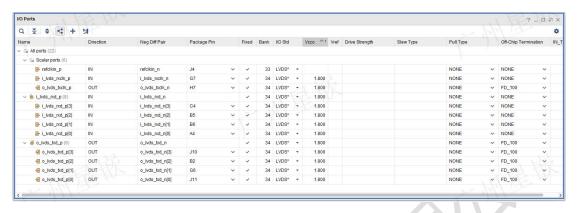

# 5.1.4管脚约束

ZYNQ PL 工程管脚约束如下图所示:

# 5.1.5 例程使用

## 5.1.5.1 连接 Cameralink 线缆

使用 Cameralink 线缆将 J3、J4 两个接口连接在一起:

## 5.1.5.2 加载运行 ZYNQ 程序

#### 5.1.5.2.1 打开 Vivado 工程

打开 Vivado 示例工程:

#### 工程打开后界面如下图所示:

### 5.1.5.2.2 下载 ZYNQ PL 程序

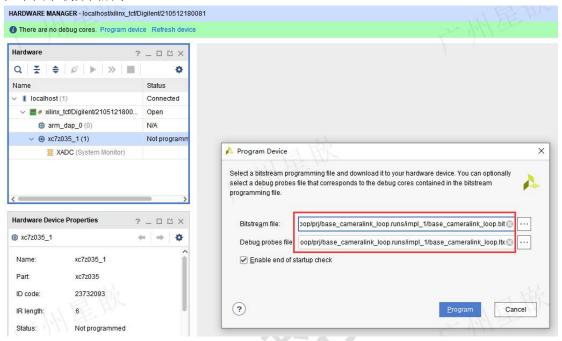

下载 bit 流文件 base\_cameralink\_loop.bit,并且配套 base\_cameralink\_loop.ltx 调试文件,如下图下载界面所示:

## 5.1.5.3 运行结果说明

ZYNQ PL 端提供的 ILA 调试窗口,可以实时抓取采集 Cameralink 并行信号以及错误检测信号的时序波形。

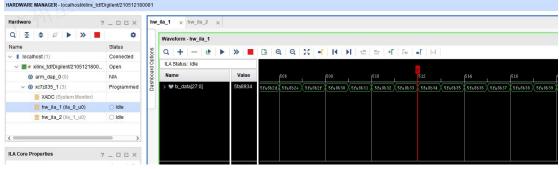

hw\_ila\_1 调试界面抓取 Cameralink 并行发送数据,是一个 28bits 的累加数:

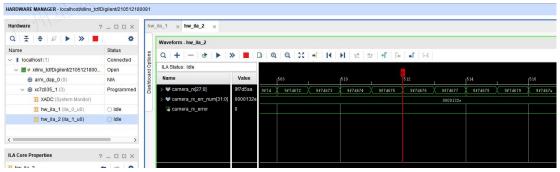

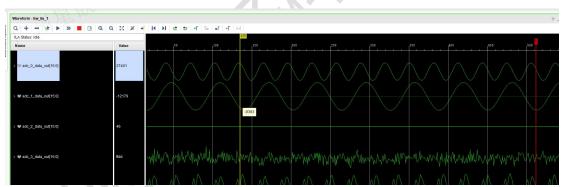

hw\_ila\_2 调试界面抓取 Cameralink 并行接收数据、接收误码统计以及接收误码实时标识信号,如下图所示:

cameralink\_rx\_err\_num 显示有数值,则说明 Cameralink 接收过程中存在误码。可能在 开始通信初始化期间存在误码现象,导致 cameralink\_rx\_err\_num 误码统计累加。待程序下 载完毕后,如果 Cameralink 通信正常的话,cameralink\_rx\_err\_num 误码统计应该不会再累 加。如果 cameralink\_rx\_err\_num 误码统计继续不断累加,则通过触发 camera\_rx\_error 信号 可以捕捉到误码具体发生时刻。

### 5.1.5.4 退出实验

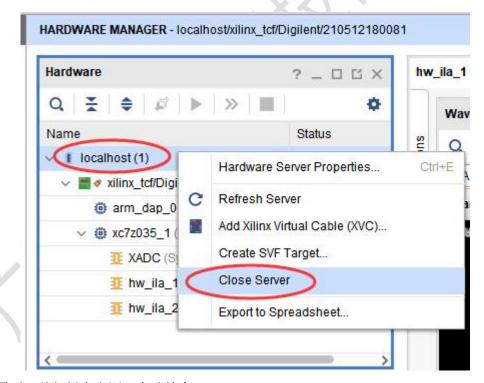

Vivado 调试界面 Hardware Manager 窗口,右键单击 localhost(1),在弹出的菜单中点击 Close Server,断开 ZYNQ JTAG 仿真器与板卡的连接:

最后,关闭板卡电源,实验结束。

# 5.2ZYNQPL SFP 光口通信例程

## 5.2.1 例程位置

ZYNQ 例程保存在资料盘中的 Demo\ZYNQ\PL\aurora\_8b10b\_0\_ex 文件夹下。

## 5.2.2功能简介

使用 Aurora 8B/10B IP 核生成后带的例子工程,稍作修改。

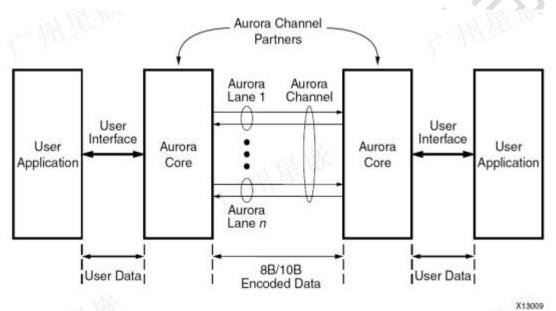

Figure 1-1: Aurora 8B/10B Channel Overview

#### 图 Aurora 8B/10B 例子工程

FRAME GEN: 本地并行数据发送模块

功能:本地产生 GTX 并行发送数据

接口说明:

// User Interface

output [0:15] TX\_D; //发送数据

output TX REM; //最后一个 16bits 数据的高低字节有效标识, 0表示,

表示 TX\_D[0:7]有效; 1表示 TX\_D[0:15]有效。

output TX\_SOF\_N; //发送开始标识,低电平有效 output TX\_EOF\_N; //发送结束标识,低电平有效

output TX SRC RDY N; //发送数据源端准备好标志,低有效

input TX DST RDY N; //发送数据目的端准备好标, 为 0 时才允许发送数

据

// System Interface

input USER\_CLK;//用户时钟,由 Aurora IP 核提供,数据发送模块用此时

钟作为同步时钟

input RESET;//复位,高有效

input CHANNEL\_UP;//GTX 通道初始化完成标志,为1时表示完成

数据发送模块只有在 RESET=0、CHANNEL\_UP=1 和 TX\_DST\_RDY\_N=0 时,才允许发送数据。

#### FRAME\_CHECK: 本地并行数据接收检测模块

功能:本地接收 GTX 并行数据,并检测数据是否存在误码

接口说明:

// User Interface

input [0:15] RX D; //接收数据

output RX\_REM; //最后一个 16bits 数据的高低字节有效标识,0 表示,

表示 RX D[0:7]有效; 1表示 RX D[0:15]有效。

output RX\_SOF\_N; //接收开始标识,低电平有效 output RX\_EOF\_N; //接收结束标识,低电平有效 input RX SRC RDY N; //接收数据有效,低电平有效

// System Interface

input USER\_CLK; //用户时钟,由 Aurora IP 核提供,数据发送模块用此时

钟作为同步时钟

input RESET; //复位,高有效

input CHANNEL\_UP; //GTX 通道初始化完成标志,为 1 时表示完成

output [0:7] ERR\_COUNT; //接收数据错误个数

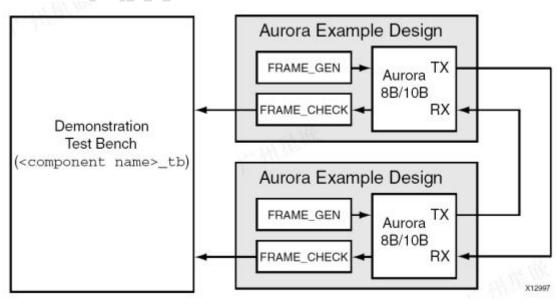

Aurora 8B10B IP 核参数设置如下图所示:

Aurora 8B10B IP 核显示最高只支持 6.6Gbps,这里我们将线速率设置为 5Gbps,参考时钟设置为 100MHz。

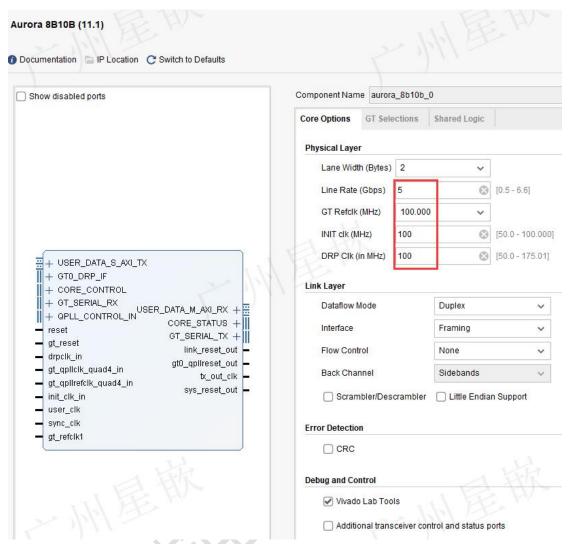

# 5.2.3管脚约束

ZYNQ PL 工程管脚约束如下图所示:

# 5.2.4 例程使用

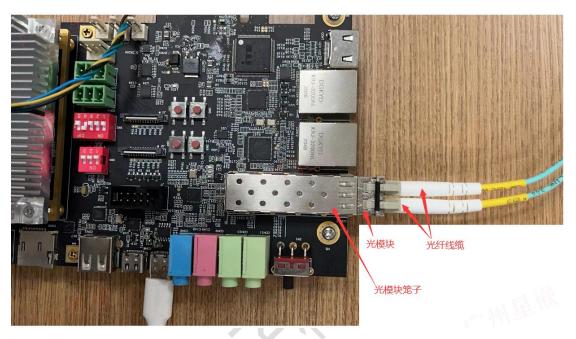

## 5.2.4.1 连接光纤模块

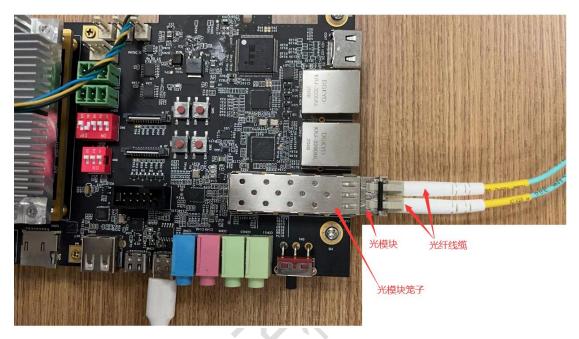

将光模块插入光模块笼子,并使用光纤线缆将光模块的收、发端口自环对接:

# 5.2.4.2 加载运行 ZYNQ 程序

# 5.2.4.2.1 打开 Vivado 工程

打开 Vivado 示例工程:

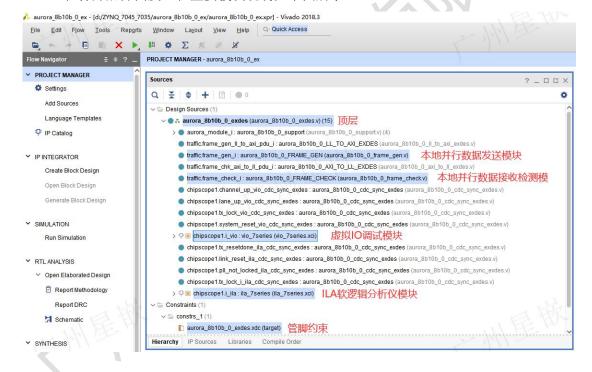

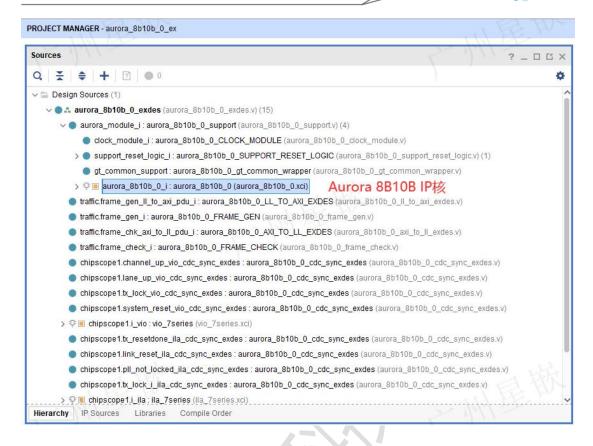

工程打开后界面及工程主要模块说明如下图所示:

## 5.2.4.2.2 下载 ZYNQ PL 程序

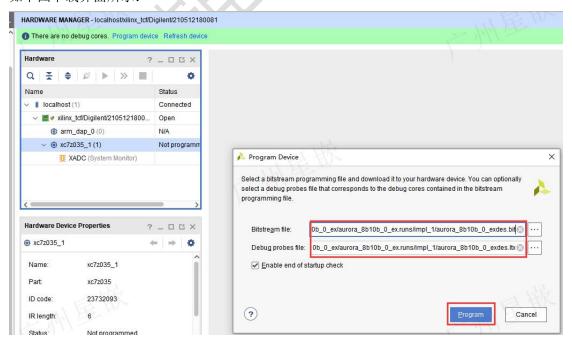

下载 bit 流文件 aurora\_8b10b\_0\_exdes.bit, 并且配套 aurora\_8b10b\_0\_exdes.ltx 调试文件, 如下图下载界面所示:

#### 5.2.4.3 运行结果说明

ZYNQ PL 端提供的 ILA 调试窗口,可以实时抓取采集 GTX 收发本地并行信号以及错误检测信号的时序波形。

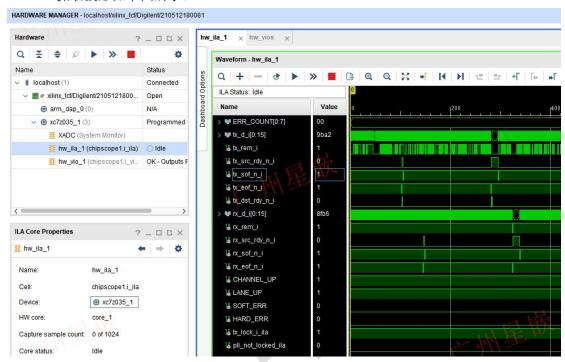

ILA 抓取波形如下图所示:

#### ILA 抓取信号说明如下:

ERR\_COUNT[0:7]: 接收数据错误个数,接收模块分析接收数据是否正确;

tx\_d\_i[0:15]: 发送数据;

$tx_{rem_i}$ : 最后一个发送数据的高低字节有效标识,0表示,表示 $tx_d_i$ [0:7]有效,1表示  $tx_d_i$ [0:15]有效;

tx\_src\_rdy\_n\_i: 发送数据源端准备好标志,结合tx\_dst\_rdy\_n\_i使用,都为0时表示可以发送数据,

tx\_sof\_n\_i: 发送开始标识, 低电平有效;

tx\_eof\_n\_i: 发送结束标识, 低电平有效;

tx\_dst\_rdy\_n\_i: 发送数据目的端准备好标志;

rx d i[0:15]: 接收数据

$rx_rem_i$ : 最后一个接收数据的高低字节有效标识,0表示,表示 $rx_d_i$ [0:7]有效,1表示 $rx_d_i$ [0:15]有效;

rx\_src\_rdy\_n\_i: 接收数据源端准备好标志;

rx\_sof\_n\_i: 接收开始标识,低电平有效;

rx eof n i: 接收结束标识, 低电平有效;

CHANNEL\_UP: 为1表示GTX通道完成正常初始化;

LANE\_UP: 指示GTX每个lane是否正常初始化成功,这里只有1个Lane;

SOFT ERR、HARD ERR: 软、硬件错误指示,正常情况应该为0

tx\_lock\_i\_ila: GTX时钟锁定指示,正常情况应该为1

pll\_not\_locked\_ila: GTX时钟失锁指示,正常情况应该为0

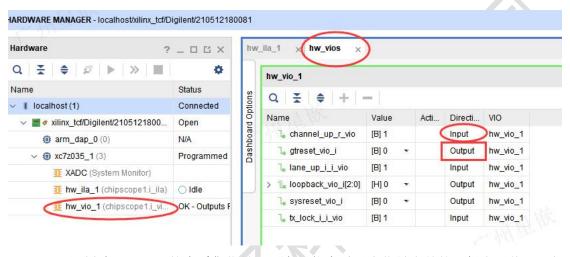

VIO 虚拟 IO 界面如下图所示:

VIO 界面上标识 Input 的为采集信号,用户只能查看对应信号当前的逻辑电平值,1表示高电平,0表示低电平; VIO 界面上标识 Output 的为用户控制信号,用于控制用户逻辑的,用户可以在 Value 一栏输入 0/1 电平值,从而达到控制用户逻辑的目的。VIO 界面主要用于复位用户逻辑,以及查看通道是否链接成功,VIO 界面可以不用操作。

### 5.2.4.4 退出实验

Vivado 调试界面 Hardware Manager 窗口,右键单击 localhost(1),在弹出的菜单中点击 Close Server,断开 ZYNQ JTAG 仿真器与板卡的连接:

#### HARDWARE MANAGER - localhost/xilinx\_tcf/Digilent/210512180081 Hardware hw\_ila\_1 ? \_ D L X Waveform Name Status (I localhost (1) Connected Hardware Server Properties... Ctrl+E @ arm\_dap\_0 (0) C Refresh Server xc7z035\_1 (3) Add Xilinx Virtual Cable (XVC)... 3 XADC (Syster Create SVF Target... hw\_ila\_1 (chi Close Server I hw\_vio\_1 (ch Export to Spreadsheet...

最后,关闭板卡电源,实验结束。

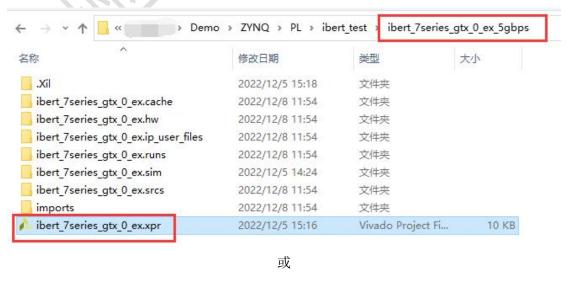

## 5.3ZYNQPL SFP 光口 IBERT 链路误码测试

## 5.3.1 例程位置

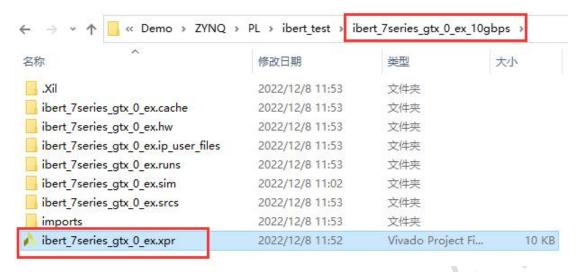

ZYNQ IBERT 链路误码测试例程有两个,分别用于光口运行在 5Gbps 和 10Gbps 两种线路 速率情形下的误码统计和眼图测试,IBERT 测试例程保存在资料盘中的位置如下:

(1) 5Gbps IBERT 例程存放位置:

Demo\ZYNQ\PL\ibert\_test\ibert\_7series\_gtx\_0\_ex\_5gbps 文件夹下;

(2) 10Gbps IBERT 例程存放位置:

Demo\ZYNQ\PL\ibert\_test\ibert\_7series\_gtx\_0\_ex\_10gbps 文件夹下。

# 5.3.2功能简介

LogiCORE IBERT IP 核是 Xilinx 提供的集成式误码率测试 IP 核,该 IP 核产生测试样式,由发送端发出测试样式,经接收端接收测试样式并进行误码检测、分析,以检测 Xilinx 器件内部高速串行收发器的收发性能。由 IBERT IP 生成的测试工程会提供一个图形化测试界面,方便用户直观控制和检测高速串行收发器的参数指标。

## 5.3.3 例程使用

### 5.3.3.1 连接光纤模块

将光模块插入光模块笼子,并使用光纤线缆将光模块的收、发端口自环对接:

## 5.3.3.2 加载运行 ZYNQ 程序

## 5.3.3.2.1 打开 Vivado 工程

打开 Vivado 示例工程,打开 5Gbps IBERT 例程或 10Gbps IBERT 例程:

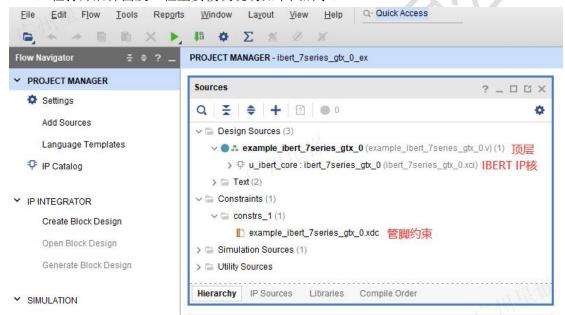

工程打开后界面及工程主要模块说明如下图所示:

## 5.3.3.2.2 下载 ZYNQ PL 程序

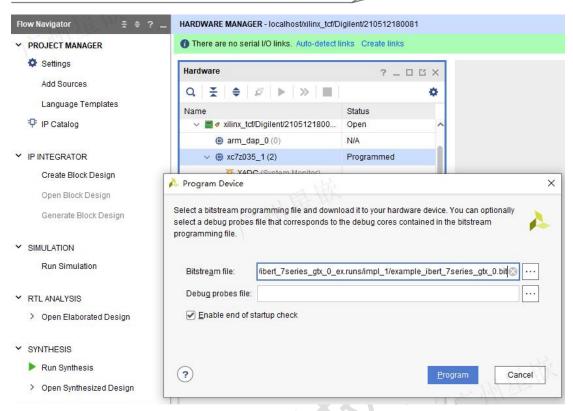

下载 bit 流文件 example ibert 7series gtx 0.bit, 如下图下载界面所示:

## 5.3.3.3 运行结果说明

## 5.3.3.3.1 查看链路状态

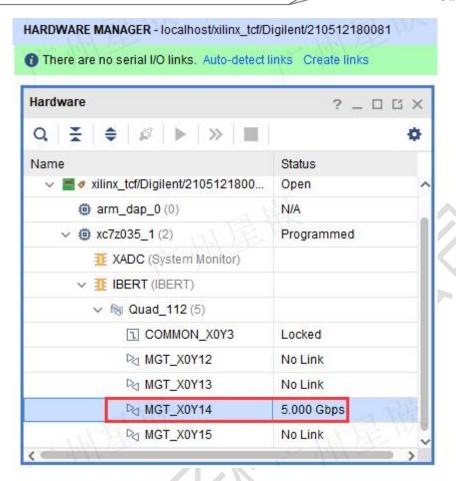

## 5.3.3.3.1.1 5Gbps 速率测试时

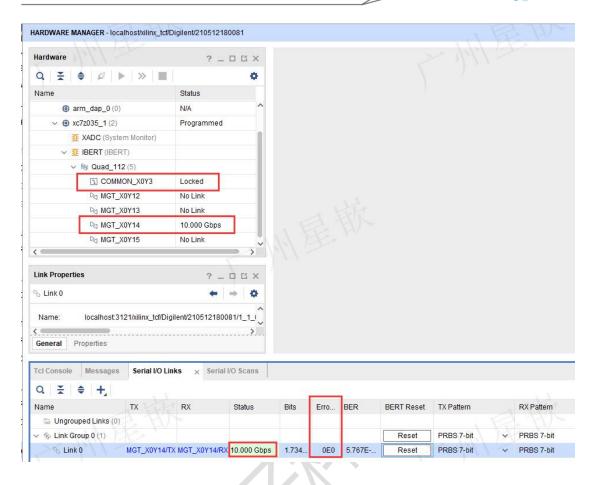

可查看到 MGT\_X0Y14 链路锁定在了 5Gbps 线路速率,通信链路已经建立起来:

#### 5.3.3.3.1.2 10Gbps 速率测试时

10Gbps 速率测试时,需要用户根据板卡实际情况调节链路参数。在调试窗口的下方,有一个 Serial I/O Links 窗口,打开此窗口去完成链路参数调节任务。

用户调节 Tx Pre-Cursor、 Tx Post-Cursor、Tx Diff Swing 这三个链路参数,参数调节完毕后,首先点击 TX Reset,然后点击 RX Reset,最后再查看 Status 和 Errors 状态,直到 Status 显示出预期的线路运行速率,比如 10Gbps,且 Errors=0E0,即误码,则表示链路目前运行正常:

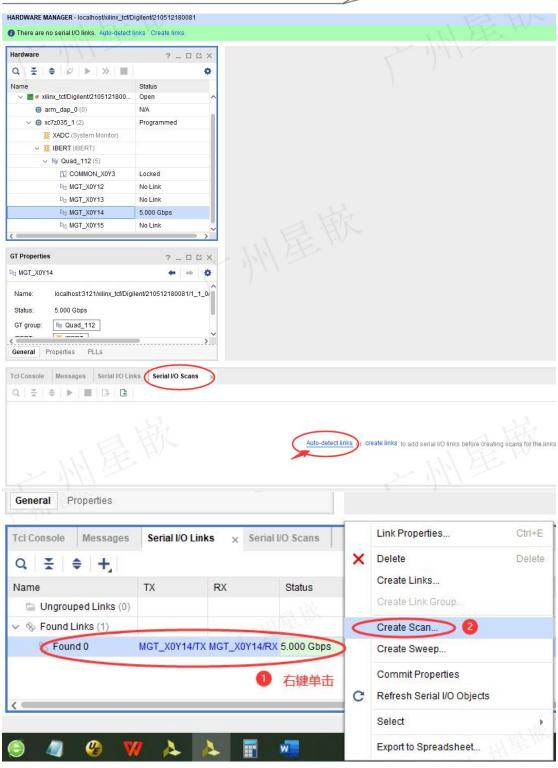

## 5.3.3.3.2 查看眼图

在 Serial I/O Scans 窗口,点击创建链路,然后再针对链路创建眼图扫描:

— Xines ·

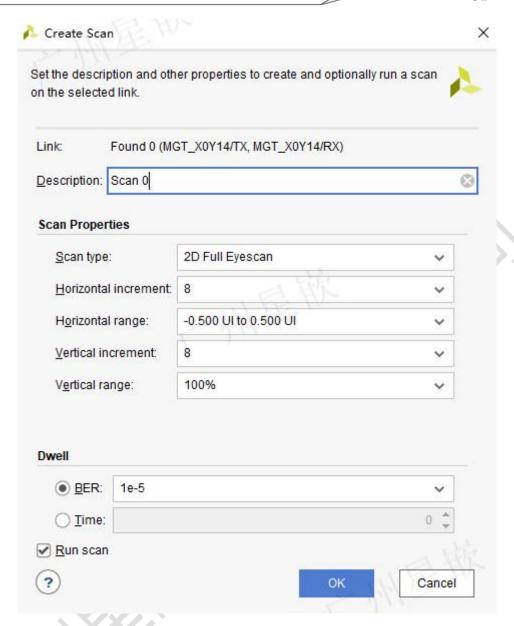

设置眼图扫描参数:

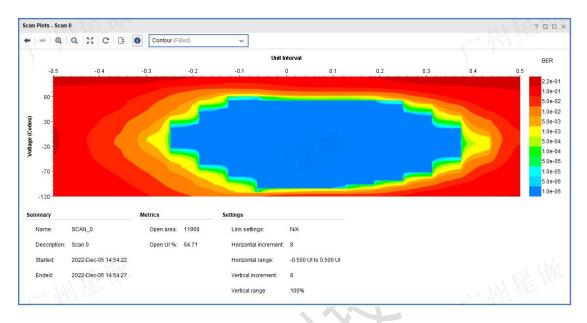

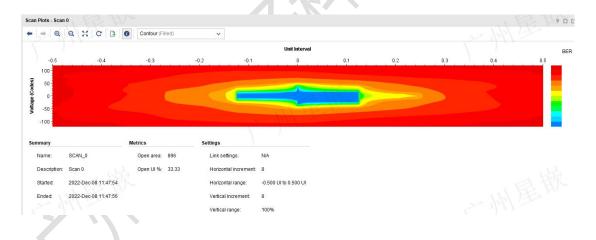

#### 5.3.3.3.2.1 眼图测试结果

### 5.3.3.3.2.1.15Gbps 速率测试时

### 5.3.3.3.2.1.210Gbps 速率测试时

## 5.3.3.4 退出实验

Vivado 调试界面 Hardware Manager 窗口,右键单击 localhost(1),在弹出的菜单中点击 Close Server,断开 ZYNQ JTAG 仿真器与板卡的连接。

最后,关闭板卡电源,实验结束。

# 5.4ZYNQPL M.2 接口验证例程

# 5.4.1 例程位置

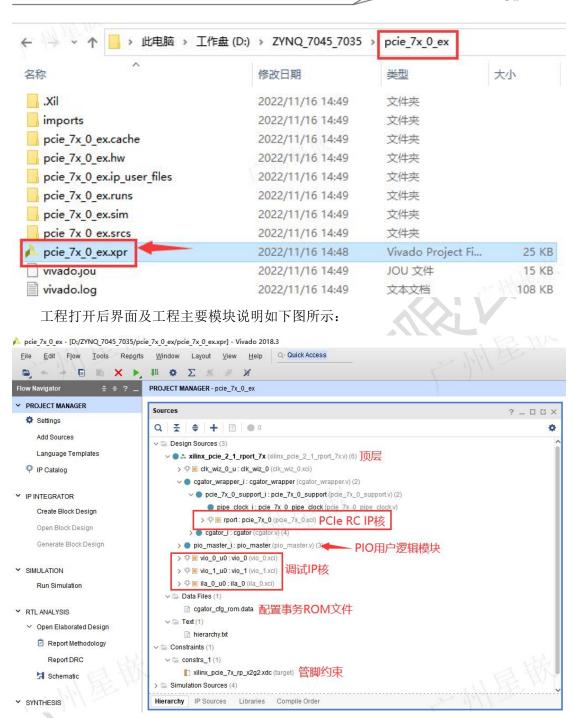

ZYNQ 例程保存在资料盘中的 Demo\ZYNQ\PL\pcie\_7x\_0\_ex 文件夹下。

## 5.4.2功能简介

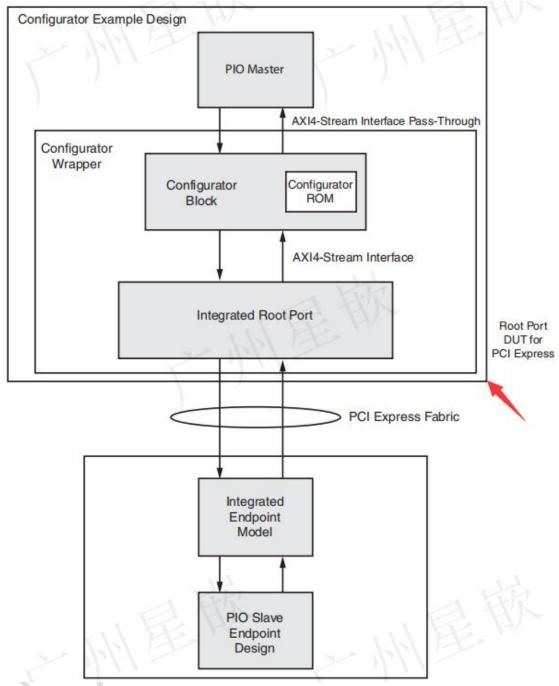

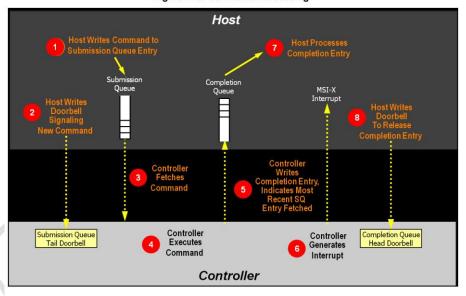

使用 7 Series Integrated Block for PCI Express IP 核 PCIe RC(PCIe 根复合体)例子工程,即 PCIe 配置示例工程,该示例工程执行 PCIe RC 端配置事务,枚举和配置 PCIe EP 端的配置空间,同时也可产生用户数据包交互。

PCIe 配置示例工程数据流和实现框图如下图所示,PCIe 配置示例工程实现的是图中Configurator Example Design 部分,PIO Master 为用户数据包产生逻辑,可由用户自行修改,以便产生所需的 PCIe TLP 事务包:

图 PCIe RC 配置示例工程数据流和框图

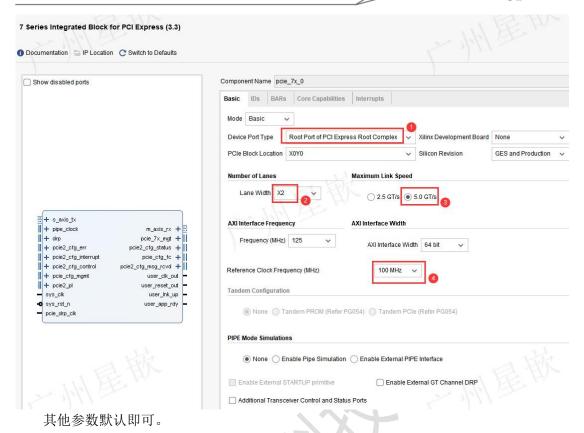

7 Series Integrated Block for PCI Express IP 核参数设置如下图所示:

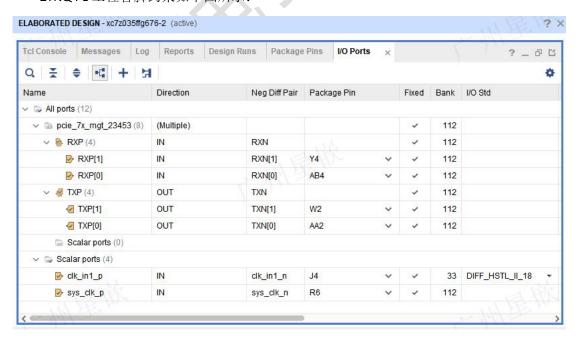

## 5.4.3管脚约束

ZYNQ PL 工程管脚约束如下图所示:

# 5.4.4 例程使用

# 5.4.4.1 插入 NVMe 硬盘

将一块 NVMe 硬盘插入底板背面的 M.2 接口插槽上,并拧上螺丝固定硬盘:

# 5.4.4.2 加载运行 ZYNQ 程序

# 5.4.4.2.1 打开 Vivado 工程

打开 Vivado 示例工程:

### 5.4.4.2.2 下载 ZYNQ PL 程序

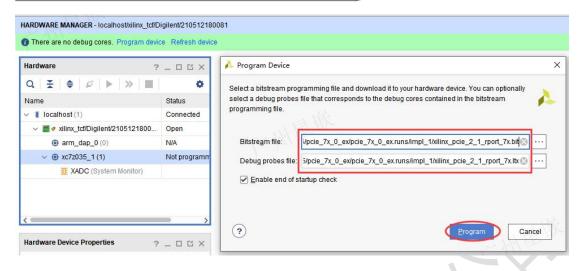

下载 bit 流文件 xilinx\_pcie\_2\_1\_rport\_7x.bit,并且配套 xilinx\_pcie\_2\_1\_rport\_7x.ltx 调试文件,如下图下载界面所示:

### 5.4.4.3 运行结果说明

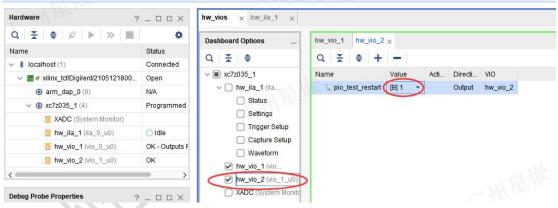

ZYNQ PL 端提供的 ILA 和 VIO 调试窗口, ILA 可以实时抓取采集 PIO 用户逻辑信号的时序 波形, VIO 可以控制 PIO 事务的重启。

hw\_vio\_2 里面的 pio\_test\_restart 控制信号用来控制 PIO 事务重启操作,先设置为 0 值,再设置为 1 值,可以启动一次 PIO 事务:

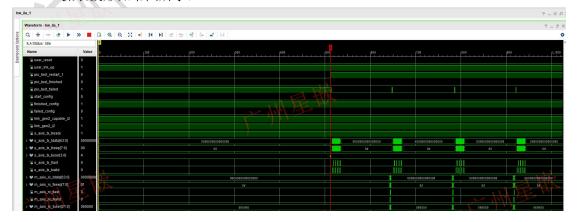

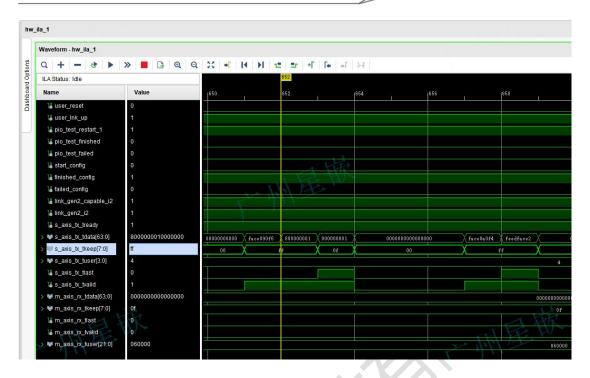

ILA 抓取波形如下图所示:

### ILA 抓取的关键信号说明如下:

user reset: 事务层用户复位信号,正常为0;

user\_lnk\_up: 事务层Link up信号,正常为1;

pio\_test\_restart\_1: PIO事务测试启动信号,0到1启动一次PIO事务测试,主要是读写PCle EP端的用户BAR存储空间,如果挂载NVMe硬盘测试的话,PIO事务测试将无意义,因为NVMe硬盘上可能并未开辟对应用户BAR存储空间;

pio\_test\_finished: PIO事务测试成功完成标识,正常为1,只有对应的PCle EP端开辟了对应的用户BAR存储空间才有意义;

pio\_test\_failed: PIO事务测试失败标识,正常为0,只有对应的PCle EP端开辟了对应的用户BAR存储空间才有意义;

start\_config: PCle配置启动信号,1表示启动PCle配置事务过程,0表示结束配置或不在配置阶段:

finished\_config: PCle配置成功完成标识,正常为1;

failed config: PCIe配置失败标识,正常为0;

link\_gen2\_capable\_i2: 速率支持指示,1表示支持PCle Gen2协议速率,即5Gbps,0表示不支持PCle Gen2协议速率;

link\_gen2\_i2: 当前PCle链路速率,0表示当前PCle链路速率为2.5 Gb/s,1表示当前PCle链路速率为5.0 Gb/s;

s\_axis\_tx\_xxx: TLP事务用户发送数据和控制接口;

m\_axis\_rx\_xxx: TLP事务用户接收数据和控制接口。

### 5.4.4.4 退出实验

Vivado 调试界面 Hardware Manager 窗口,右键单击 localhost(1),在弹出的菜单中点击 Close Server,断开 ZYNQ JTAG 仿真器与板卡的连接。

最后,关闭板卡电源,实验结束。

# 5.5ZYNQPL M.2 接口之 NVMe Host IP 例程说明

# 5.5.1 例程声明

此例程涉及到收费 IP 核,因此只对例程进行介绍性说明,如需要详细例程和对应 IP 核资料,请联系市场洽谈。

# 5.5.2设计目的

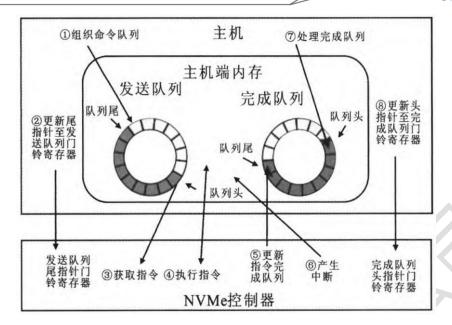

使用 FPGA 实现标准 NVMe 1.3 协议的 Host 端,即纯逻辑实现 NVMe Host IP。

用户可以根据自身需求,定制 NVMe Host FPGA IP,还可以在此基础上定制 FPGA 纯逻辑来实现文件系统 ExFAT。

NVMe Host FPGA IP 核使用 VHDL 硬件描述语言的纯逻辑方式来实现,NVMe 物理层使用 Xilinx 7 系列 PCle 核,无需 CPU 参与。目前已在广州星嵌电子 ZYNQ+DSP 平台上实现并经充分测试验证: PCle 2.0 x2 Lane 平台,连续读速率: 685 MB/s,连续写速率: 531 MB/s,日后升级可能还有提升空间。后续广州星嵌电子会提供 PCle 2.0 x4/x8 Lane 平台,以获取更高的硬盘读写带宽。

### 5.5.3 NVMe Host FPGA IP 核简介

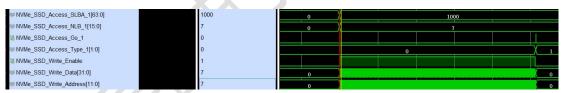

NVMe Host FPGA IP 访问接口简单,用户可将此 IP 当作双端口 RAM 来使用,只是相对普通双端口 RAM 而言多增加了一些读、写命令握手接口信号而已。当然,用户还可将 IP 定制为自身所需要的接口形式。

NVMe Host FPGA IP 对外接口图如下:

| NVMe_                               | _Host_Com    | ponent                         |  |  |  |

|-------------------------------------|--------------|--------------------------------|--|--|--|

| NVMe_Host_Reset_N                   | <b>a</b>     |                                |  |  |  |

| NVMe_SSD_Access_Go                  |              |                                |  |  |  |

| NVMe_SSD_Access_NLB[15:0]           | 1000<br>1000 | Index_NVMe_SSD_Read_Data[11:0] |  |  |  |

| NVMe_SSD_Access_SLBA[63:0]          |              | NVMe_Host_Ready                |  |  |  |

| NVMe_SSD_Access_Type[1:0]           |              | NVMe_Host_User_CLK             |  |  |  |

| NVMe_SSD_Read_Clock                 |              | NVMe_SSD_Access_Area           |  |  |  |

| NVMe_SSD_Read_Configure_Start[11:0] |              | NVMe_SSD_Access_Done           |  |  |  |

| NVMe_SSD_Read_Configure_Stop[11:0]  |              | NVMe_SSD_Access_Status[5:0]    |  |  |  |

| NVMe_SSD_Read_Go                    |              | NVMe_SSD_Read_Area             |  |  |  |

| NVMe_SSD_Write_Address[11:0]        |              | NVMe_SSD_Read_Data[31:0]       |  |  |  |

| NVMe_SSD_Write_Clock                |              | NVMe_SSD_Read_Data_Valid       |  |  |  |

| NVMe_SSD_Write_Data[31:0]           | 4.00         | NVMe_SSD_Read_Done             |  |  |  |

| NVMe_SSD_Write_Enable               |              | PCIE_TXN[3:0]                  |  |  |  |

| PCIE_RXN[3:0]                       |              | PCIE_TXP[3:0]                  |  |  |  |

| PCIE_RXP[3:0]                       |              | sl_oport0[0:16]                |  |  |  |

| PCIe_CLK                            |              | sl_oport0_1[0:16]              |  |  |  |

### 名词和概念解释:

SLBA(Starting LBA): 逻辑块基地址,数据在 SSD 固态硬盘上的起始地址。

NLB (Number of Logical Blocks):逻辑块数量,指定数据传输大小,需要指出的是这是一个 0 基数值,即以 0 为初始值,所以最终传的是(NLB+1)个逻辑块。

NVMe Host FPGA IP 支持最大队列数 64 对,最大队列深度 16383,用户可以根据需要进行定制。NVMe Host FPGA IP 核源码实现了参数化,可根据用户功能及性能(比如队列数与队列深度)对 IP 参数进行修改设置。

NVMe Host FPGA IP 使用的 FPGA 软件开发平台为 Vivado 2018.3,用户可以定制为自身所需的 FPGA 软件开发平台上。

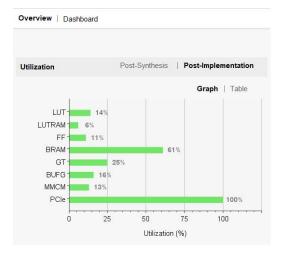

# 5.5.4资源消耗

广州星嵌电子 ZYNQ+DSP 平台上使用 ZYNQ 7035 PL 端作为 FPGA 开发平台,ZYNQ 芯片型号为 XC7Z035FFG676-2。NVMe Host FPGA IP 在 XC7Z035FFG676-2 芯片上的资源消耗报表如下:

(注: 此为第一版 IP 资源消耗图表,还有优化空间)

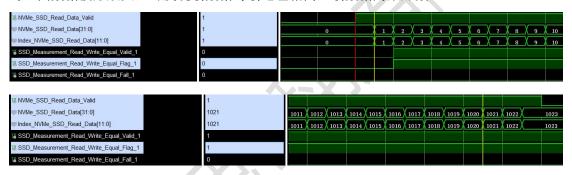

## 5.5.5 NVMe Host FPGA IP 测试截图和说明

借助 NVMe Host FPGA IP,往 NVMe SSD 固态硬盘上写入测试数据(例程使用的是累加数),然后读出,并在 FPGA 上使用逻辑进行比对,并给出比对结果,以验证 NVMe 硬盘读写数据是否一致。

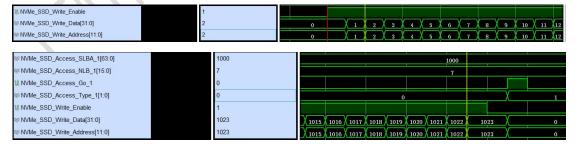

## 5.5.5.1 单次写 8 个扇区

注: NLB = 7, 即逻辑块数量 8。

数据波形放大查看,可以看到写数据与写地址相同,写数据为累加数:

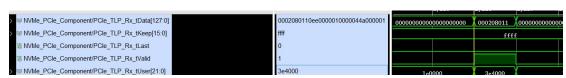

单次写 8 个扇区对应的 PCIe 底层时序波形如下图所示:

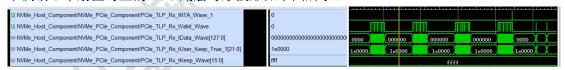

I§ NVMe\_Host\_Component/NVMe\_PCIe\_Component/PCIe\_TLP\_Tx\_tReady

I§ NVMe\_Host\_Component/NVMe\_PCIe\_Component/PCIe\_TLP\_Tx\_tLast

I§ NVMe\_Host\_Component/NVMe\_PCIe\_Component/PCIe\_TLP\_Tx\_tValid

I§ NVMe\_Host\_Component/NVMe\_PCIe\_Component/PCIe\_TLP\_Tx\_tData[127:0]

NVMe\_Host\_Component/NVMe\_PCle\_Component/PCle\_TLP\_Tx\_tKeep[15:0]

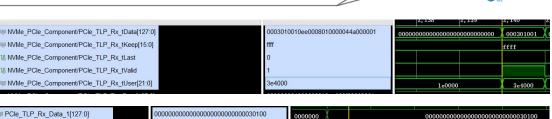

### 5.5.5.2 单次读 8 个扇区

### 对上面数据波形放大,可发现读数据与读地址相同,读数据为累加数:

### 单次读 8 个扇区对应的 PCIe 底层时序波形如下图所示:

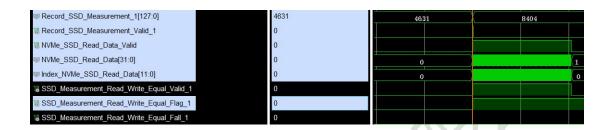

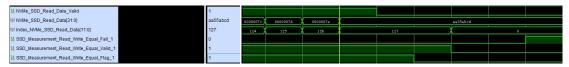

## 5.5.5.3 扇区读写比对测试

比对结果如下图高亮信号所示:

Equal\_Fail: SSD 硬盘读写数据不一致标识, 1 表示读写数据不一致; Equal\_Valid: 读写数据比对结果有效标识, 1 表示读写对比结果有效;

Equal Flag: SSD 硬盘读写数据一致标识, 1表示读写数据一致。

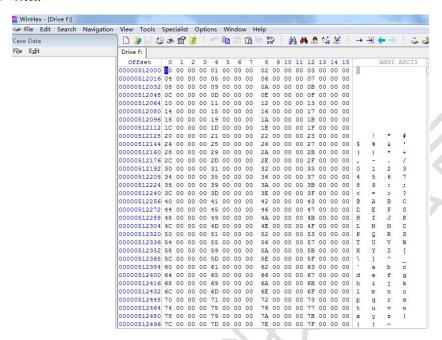

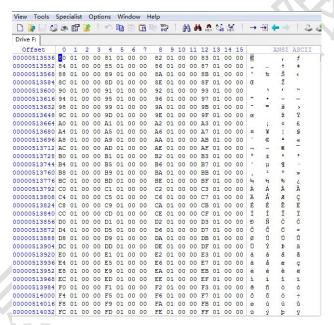

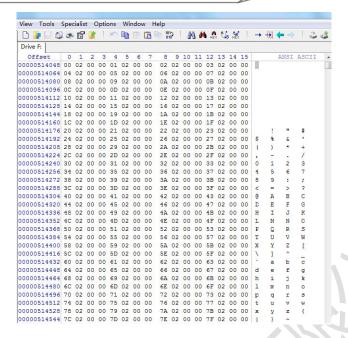

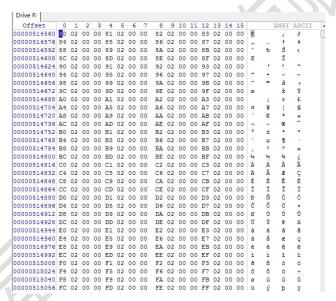

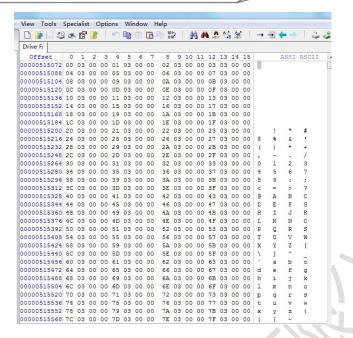

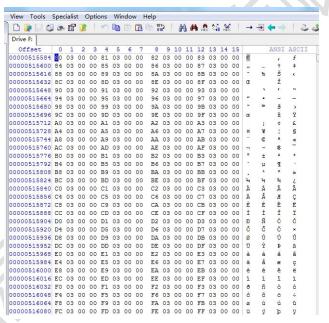

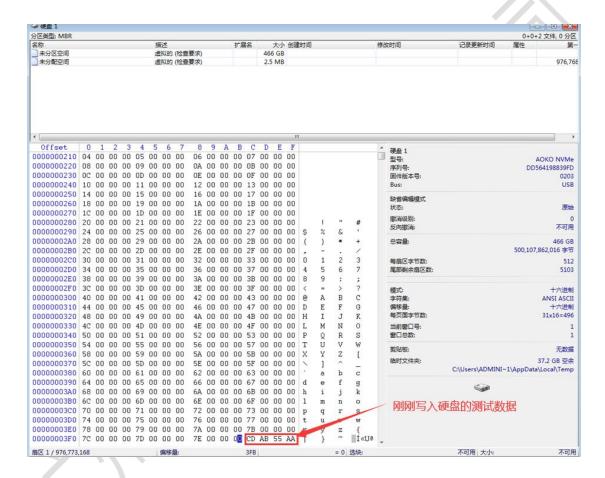

NVMe SSD 硬盘读写测试完后,从测试平台上取下 NVMe SSD 固态硬盘,并将 SSD 硬盘连接至 PC 电脑,使用 WinHex 软件工具分析 NVMe SSD 固态硬盘的写入数据。

### 扇区1写入数据:

### 扇区 2 写入数据:

扇区 3 写入数据:

#### 扇区 4 写入数据:

扇区5写入数据:

### 扇区 6 写入数据:

扇区7写入数据:

扇区 8 写入数据:

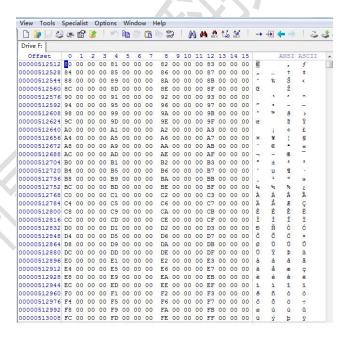

# 5.5.5.4 指定扇区某位置写入指定值

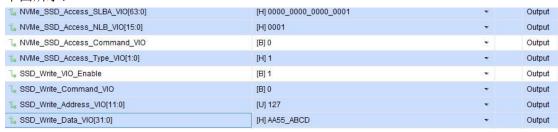

指定往 SSD 硬盘的第 1 扇区偏移地址 127 中写入数据 0xAA55\_ABCD, FPGA VIO 设置如下图所示:

- Xines

指定从 SSD 硬盘的第 1 扇区偏移地址 127 中读出数据,读数据为 0xAA55\_ABCD,与写入数据一致,读时序和读写比对结果如下图所示:

从测试平台上取下 NVMe SSD 固态硬盘,并将硬盘连接至 PC 电脑,使用 WinHex 软件工具分析刚刚写入硬盘的测试数据,如下图所示,也可发现确实已经将 0xAA55\_ABCD 用户数据写入了硬盘:

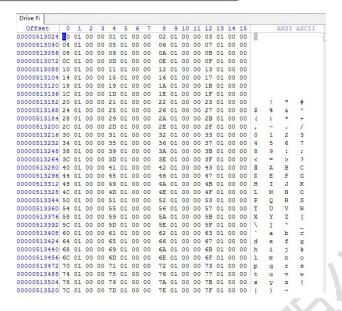

### 5.5.5.5 NVMe 协议相关寄存器读取

NVMe 协议码: 0x010802,对应的 PCIe 底层读时序波形如下图所示:

**NVMe** 协议版本 **1.3**: **0x00010300**, 对应的 **PCIe** 底层读时序波形如下图所示:

星嵌电子

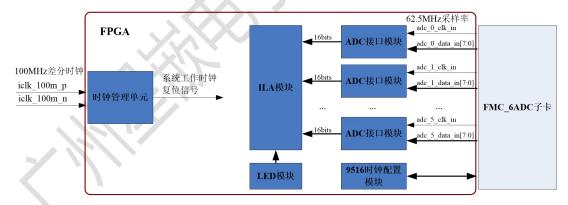

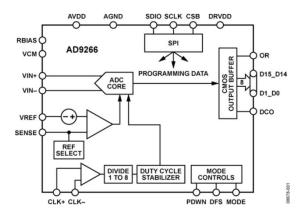

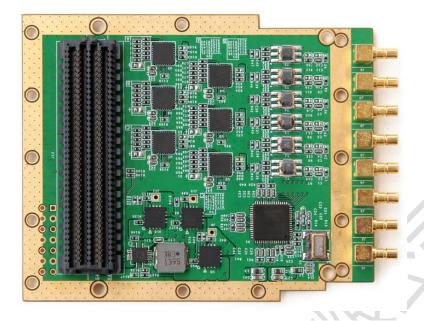

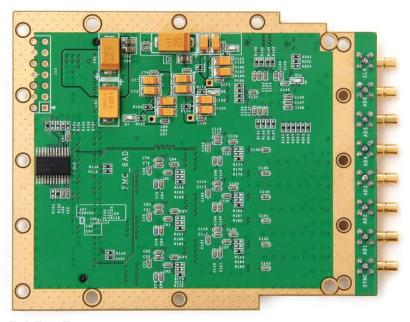

# 5.6ZYNQPL FMC 之 6 路 ADC 采集例程

此例程需要配合 6 路 ADC FMC 子卡使用。

## 5.6.1 例程位置

B PCle\_TLP\_Rx\_Data\_Valid\_1

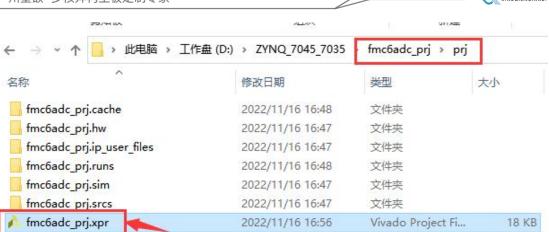

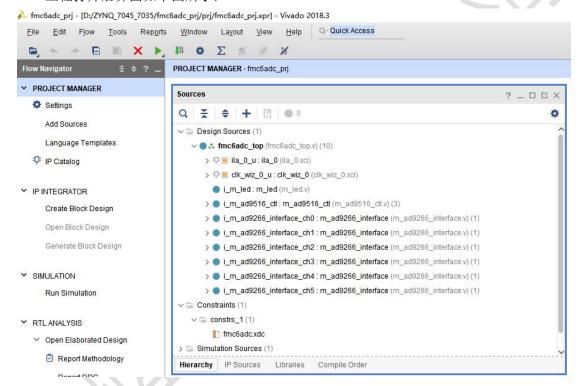

ZYNQ 例程保存在资料盘中的 Demo\ZYNQ\PL\fmc6adc prj\prj 文件夹下。

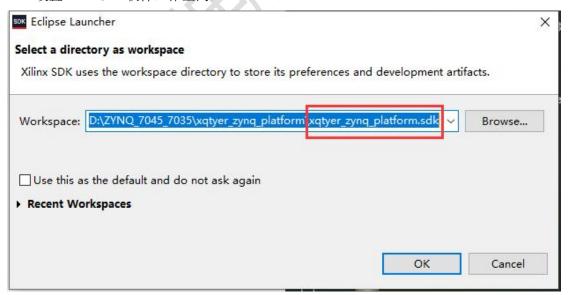

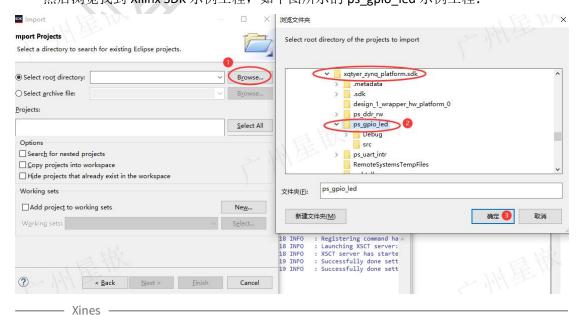

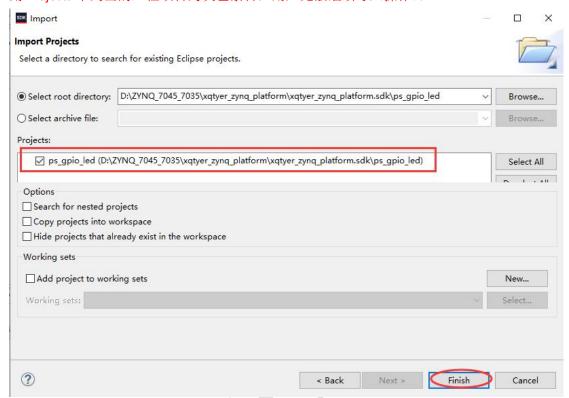

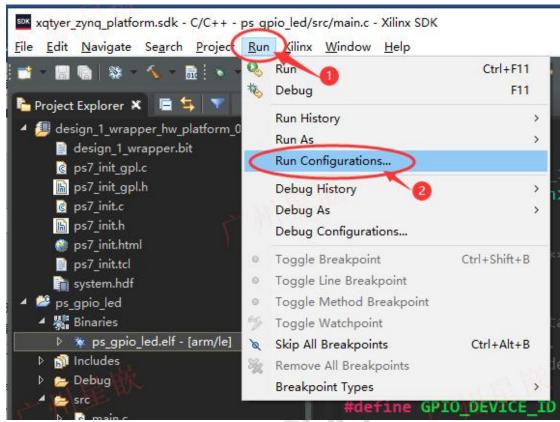

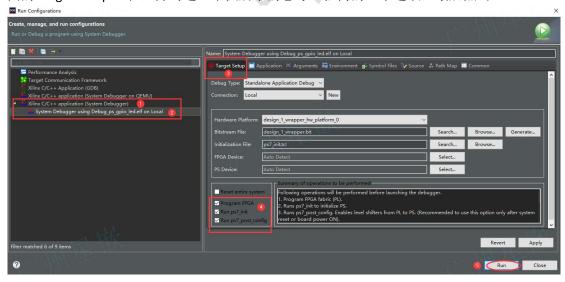

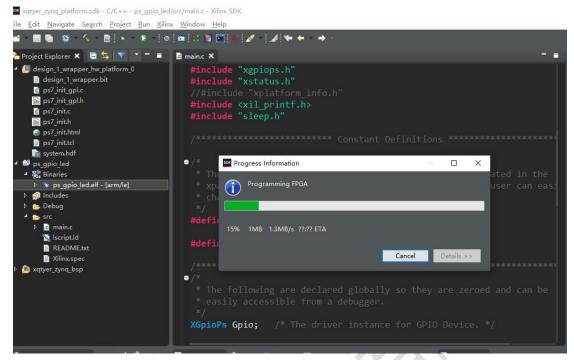

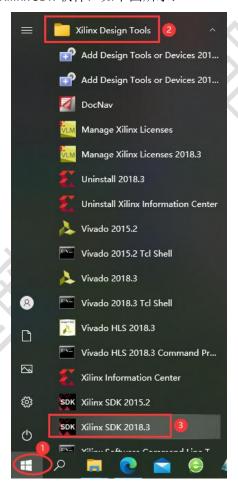

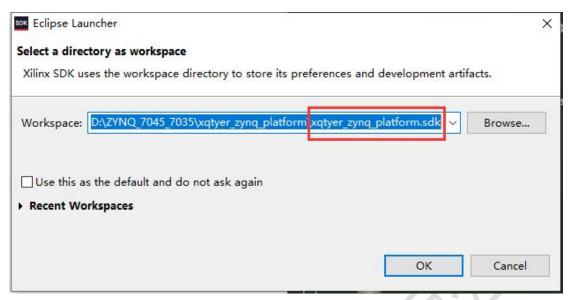

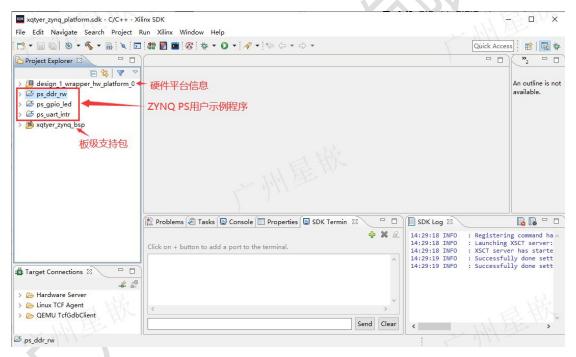

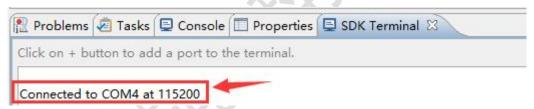

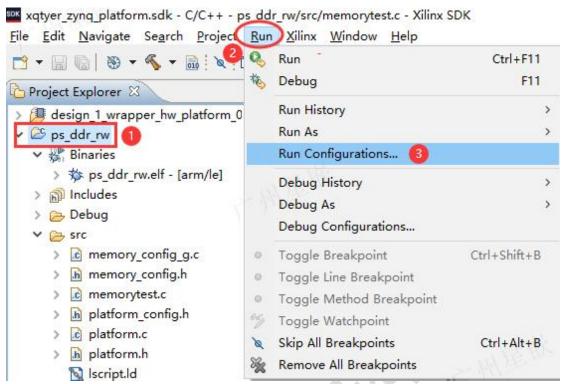

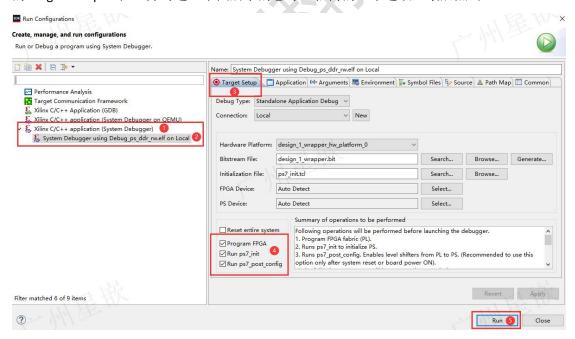

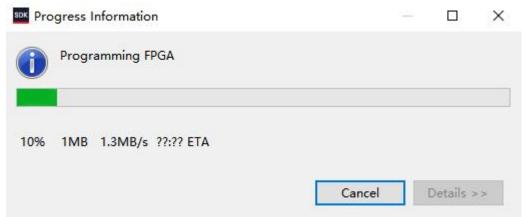

## 5.6.2功能简介