#### **Freescale Semiconductor**

Data Sheet: Advance Information

Document Number: MCF52259 Rev. 0, 12/2008

## MCF52259

# MCF52259 ColdFire Microcontroller

The MCF52259 is a member of the ColdFire<sup>®</sup> family of reduced instruction set computing (RISC) microprocessors.

This document provides an overview of the 32-bit MCF52259 microcontroller, focusing on its highly integrated and diverse feature set.

This 32-bit device is based on the Version 2 ColdFire core operating at a frequency up to 80 MHz, offering high performance and low power consumption. On-chip memories connected tightly to the processor core include up to 512 Kbytes of flash memory and 64 Kbytes of static random access memory (SRAM). On-chip modules include:

- V2 ColdFire core delivering 76 MIPS (Dhrystone 2.1) at 80 MHz running from internal flash memory with Enhanced Multiply Accumulate (MAC) Unit and hardware divider

- Cryptography Acceleration Unit (CAU)

- Fast Ethernet controller (FEC)

- Mini-FlexBus external bus interface available on 144 pin packages

- Universal Serial Bus On-The-Go (USBOTG)

- · USB Transceiver

- FlexCAN controller area network (CAN) module

- Three universal asynchronous/synchronous receiver/transmitters (UARTs)

- Two inter-integrated circuit (I2C<sup>TM</sup>) bus interface modules

- Queued serial peripheral interface (QSPI) module

- Eight-channel 12-bit fast analog-to-digital converter (ADC) with simultaneous sampling

- Four-channel direct memory access (DMA) controller

- Four 32-bit input capture/output compare timers with DMA support (DTIM)

- Four-channel general-purpose timer (GPT) capable of input capture/output compare, pulse width modulation (PWM), and pulse accumulation

- Eight-channel/Four-channel, 8-bit/16-bit pulse width modulation timer

- Two 16-bit periodic interrupt timers (PITs)

- Real-time clock (RTC) module with 32 kHz crystal

- Programmable software watchdog timer

- Secondary watchdog timer with independent clock

- Interrupt controller capable of handling 57 sources

- Clock module with 8 MHz on-chip relaxation oscillator and integrated phase-locked loop (PLL)

- Test access/debug port (JTAG, BDM)

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

## **Table of Contents**

| 1 | Fami  | ly Configurations                                |   | 2.10 | Fast Ethernet Timing Specifications                 | . 26 |

|---|-------|--------------------------------------------------|---|------|-----------------------------------------------------|------|

|   | 1.1   | Block Diagram4                                   |   | 2.11 | General Purpose I/O Timing                          | . 28 |

|   | 1.2   | Features                                         |   | 2.12 | Reset Timing                                        | . 29 |

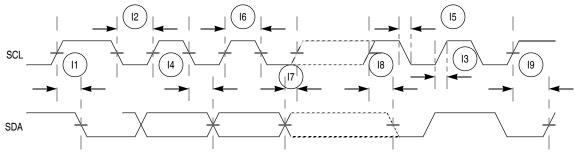

| 2 | Elect | trical Characteristics                           |   | 2.13 | I <sup>2</sup> C Input/Output Timing Specifications | . 30 |

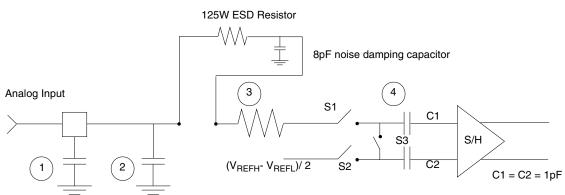

|   | 2.1   | Maximum Ratings                                  |   | 2.14 | Analog-to-Digital Converter (ADC) Parameters        | . 31 |

|   | 2.2   | Current Consumption                              |   | 2.15 | Equivalent Circuit for ADC Inputs                   | . 32 |

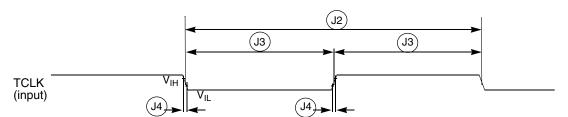

|   | 2.3   | Thermal Characteristics                          |   | 2.16 | DMA Timers Timing Specifications                    | . 33 |

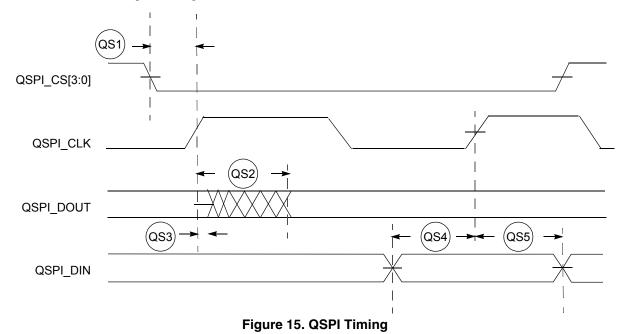

|   | 2.4   | Flash Memory Characteristics                     |   | 2.17 | QSPI Electrical Specifications                      | . 33 |

|   | 2.5   | ESD Protection                                   |   | 2.18 | JTAG and Boundary Scan Timing                       | . 34 |

|   | 2.6   | DC Electrical Specifications                     |   | 2.19 | Debug AC Timing Specifications                      | . 36 |

|   | 2.7   | Clock Source Electrical Specifications           | 3 | Mech | nanical Outline Drawings                            | . 37 |

|   | 2.8   | USB Operation                                    |   | 3.1  | 100-pin LQFP Package                                | . 38 |

|   | 2.9   | Mini-FlexBus External Interface Specifications26 | 4 |      | sion History                                        |      |

**Table 1. MCF52259 Family Configurations**

| Module                                                                                                          | 52252      | 52254                  | 52255                        | 52256      | 52258                 | 52259                        |

|-----------------------------------------------------------------------------------------------------------------|------------|------------------------|------------------------------|------------|-----------------------|------------------------------|

| Version 2 ColdFire Core with eMAC (Enhanced multiply-accumulate unit) and CAU (Cryptographic acceleration unit) | •          | •                      | •                            | •          | •                     | •                            |

| System Clock                                                                                                    | up to 66 c | or 80 MHz <sup>1</sup> | up to<br>80 MHz <sup>1</sup> | up to 66 o | r 80 MHz <sup>1</sup> | up to<br>80 MHz <sup>1</sup> |

| Performance (Dhrystone 2.1 MIPS)                                                                                |            |                        | up to 6                      | 3 or 76    |                       |                              |

| Flash                                                                                                           | 256 KB     | 512 KB                 | 512 KB                       | 256 KB     | 512 KB                | 512 KB                       |

| Static RAM (SRAM)                                                                                               | 32 KB      | 64 KB                  | 64 KB                        | 32 / 64 KB | 64 KB                 | 64 KB                        |

| Two Interrupt Controllers (INTC)                                                                                | •          | •                      | •                            | •          | •                     | •                            |

| Fast Analog-to-Digital Converter (ADC)                                                                          | •          | •                      | •                            | •          | •                     | •                            |

| USB On-The-Go (USB OTG)                                                                                         | •          | •                      | •                            | •          | •                     | •                            |

| Mini-FlexBus external bus interface                                                                             | _          | _                      | _                            | •          | •                     | •                            |

| Fast Ethernet Controller (FEC)                                                                                  | •          | •                      | •                            | •          | •                     | •                            |

| Random Number Generator and<br>Cryptographic Acceleration Unit (CAU)                                            | _          | _                      | •                            | _          | _                     | •                            |

| FlexCAN 2.0B Module                                                                                             | Varies     | Varies                 | •                            | Varies     | Varies                | •                            |

| Four-channel Direct-Memory Access (DMA)                                                                         | •          | •                      | •                            | •          | •                     | •                            |

| Software Watchdog Timer (WDT)                                                                                   | •          | •                      | •                            | •          | •                     | •                            |

| Secondary Watchdog Timer                                                                                        | •          | •                      | •                            | •          | •                     | •                            |

| Two-channel Periodic Interrupt Timer (PIT)                                                                      | 2          | 2                      | 2                            | 2          | 2                     | 2                            |

| Four-Channel General Purpose Timer (GPT)                                                                        | •          | •                      | •                            | •          | •                     | •                            |

| 32-bit DMA Timers                                                                                               | 4          | 4                      | 4                            | 4          | 4                     | 4                            |

| QSPI                                                                                                            | •          | •                      | •                            | •          | •                     | •                            |

| UART(s)                                                                                                         | 3          | 3                      | 3                            | 3          | 3                     | 3                            |

| I <sup>2</sup> C                                                                                                | 2          | 2                      | 2                            | 2          | 2                     | 2                            |

| Eight/Four-channel 8/16-bit PWM Timer                                                                           | •          | •                      | •                            | •          | •                     | •                            |

| General Purpose I/O Module (GPIO)                                                                               | •          | •                      | •                            | •          | •                     | •                            |

| Chip Configuration and Reset Controller Module                                                                  | •          | •                      | •                            | •          | •                     | •                            |

| Background Debug Mode (BDM)                                                                                     | •          | •                      | •                            | •          | •                     | •                            |

| JTAG - IEEE 1149.1 Test Access Port                                                                             | •          | •                      | •                            | •          | •                     | •                            |

| Package                                                                                                         |            | 100 LQFP               |                              | 144 LQ     | FP or 144 M           | APBGA                        |

<sup>&</sup>lt;sup>1</sup> 66 MHz = 63 MIPS; 80 MHz = 76 MIPS

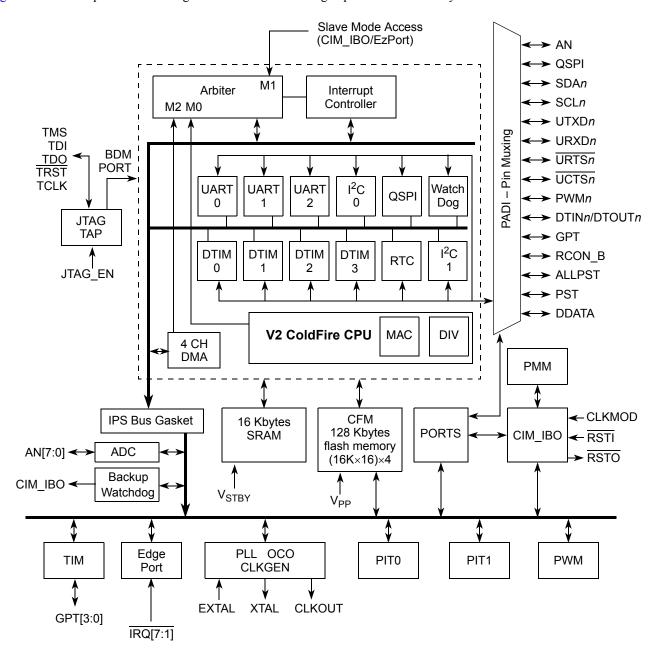

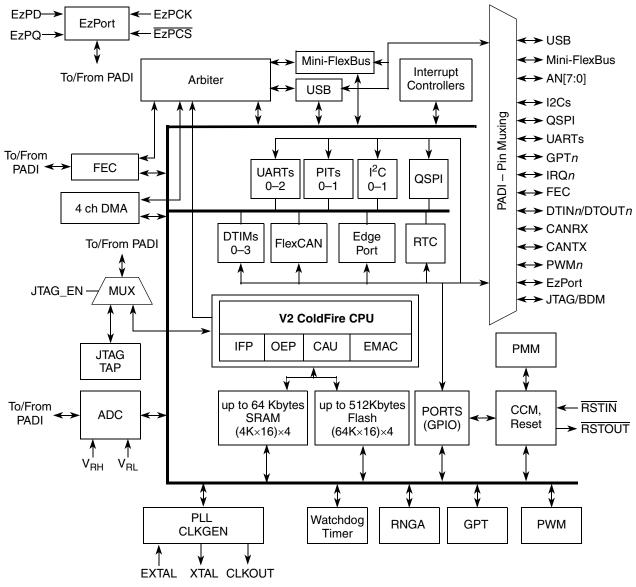

## 1.1 Block Diagram

Figure 1 shows a top-level block diagram of the device. Package options for this family are described later in this document.

Figure 1. Block Diagram

#### 1.2 Features

This document contains information on a new product under development. Freescale reserves the right to change or discontinue this product without notice. Specifications and information herein are subject to change without notice.

#### 1.2.1 Feature Overview

The MCF52259 family includes the following features:

- Version 2 ColdFire variable-length RISC processor core

- Static operation

- 32-bit address and data paths on-chip

- Up to 80 MHz processor core frequency

- 40 MHz or 33 MHz off-platform bus frequency

- Sixteen general-purpose, 32-bit data and address registers

- Implements ColdFire ISA\_A with extensions to support the user stack pointer register and four new instructions for improved bit processing (ISA\_A+)

- Enhanced Multiply-Accumulate (EMAC) unit with four 32-bit accumulators to support  $16 \times 16 \rightarrow 32$  or  $32 \times 32 \rightarrow 32$  operations

- Cryptographic Acceleration Unit (CAU)

- Tightly-coupled coprocessor to accelerate software-based encryption and message digest functions

- Support for DES, 3DES, AES, MD5, and SHA-1 algorithms

- System debug support

- Real-time trace for determining dynamic execution path

- Background debug mode (BDM) for in-circuit debugging (DEBUG\_B+)

- Real-time debug support, with six hardware breakpoints (4 PC, 1 address and 1 data) configurable into a 1- or 2-level trigger

- On-chip memories

- Up to 64-Kbyte dual-ported SRAM on CPU internal bus, supporting core, DMA, and USB access with standby power supply support for the first 16 Kbytes

- Up to 512 Kbytes of interleaved flash memory supporting 2-1-1-1 accesses

- Power management

- Fully static operation with processor sleep and whole chip stop modes

- Rapid response to interrupts from the low-power sleep mode (wake-up feature)

- Clock enable/disable for each peripheral when not used (except backup watchdog timer)

- Software controlled disable of external clock output for low-power consumption

- FlexCAN 2.0B module

- Based on and includes all existing features of the Freescale TouCAN module

- Full implementation of the CAN protocol specification version 2.0B

- Standard data and remote frames (up to 109 bits long)

- Extended data and remote frames (up to 127 bits long)

- Zero to eight bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Flexible message buffers (MBs), totalling up to 16 message buffers of 0–8 byte data length each, configurable as Rx or Tx, all supporting standard and extended messages

- Unused MB space can be used as general purpose RAM space

- Listen-only mode capability

- Content-related addressing

- No read/write semaphores

- Three programmable mask registers: global for MBs 0–13, special for MB14, and special for MB15

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Universal Serial Bus On-The-Go (USB OTG) dual-mode host and device controller

- Full-speed / low-speed host controller

- USB 1.1 and 2.0 compliant full-speed / low speed device controller

- 16 bidirectional end points

- DMA or FIFO data stream interfaces

- Low power consumption

- OTG protocol logic

- Fast Ethernet controller (FEC)

- 10/100 BaseT/TX capability, half duplex or full duplex

- On-chip transmit and receive FIFOs

- Built-in dedicated DMA controller

- Memory-based flexible descriptor rings

- Mini-FlexBus

- External bus interface available on 144 pin packages

- Supports glueless interface with 8-bit ROM/flash/SRAM/simple slave peripherals. Can address up to 2 Mbytes of addresses

- 2 chip selects (FB\_CS[1:0])

- Non-multiplexed mode: 8-bit dedicated data bus, 20-bit address bus

- Multiplexed mode: 16-bit data and 20-bit address bus

- FB CLK output to support synchronous memories

- Programmable base address, size, and wait states to support slow peripherals

- Operates at up to 40 MHz (bus clock) in 1:2 mode or up to 80 MHz (core clock) in 1:1 mode

- Three universal asynchronous/synchronous receiver transmitters (UARTs)

- 16-bit divider for clock generation

- Interrupt control logic with maskable interrupts

- DMA support

- Data formats can be 5, 6, 7 or 8 bits with even, odd, or no parity

- Up to two stop bits in 1/16 increments

- Error-detection capabilities

- Modem support includes request-to-send (RTS) and clear-to-send (CTS) lines for two UARTs

- Transmit and receive FIFO buffers

- Two I<sup>2</sup>C modules

- Interchip bus interface for EEPROMs, LCD controllers, A/D converters, and keypads

- Fully compatible with industry-standard I<sup>2</sup>C bus

- Master and slave modes support multiple masters

- Automatic interrupt generation with programmable level

- Queued serial peripheral interface (QSPI)

- Full-duplex, three-wire synchronous transfers

- Up to three chip selects available

- Master mode operation only

- Programmable bit rates up to half the CPU clock frequency

- Up to 16 pre-programmed transfers

- Fast analog-to-digital converter (ADC)

- Eight analog input channels

- 12-bit resolution

- Minimum 1.125 μs conversion time

- Simultaneous sampling of two channels for motor control applications

- Single-scan or continuous operation

- Optional interrupts on conversion complete, zero crossing (sign change), or under/over low/high limit

- Unused analog channels can be used as digital I/O

MCF52259 ColdFire Microcontroller, Rev. 0

- Four 32-bit timers with DMA support

- 12.5 ns resolution at 80 MHz

- Programmable sources for clock input, including an external clock option

- Programmable prescaler

- Input capture capability with programmable trigger edge on input pin

- Output compare with programmable mode for the output pin

- Free run and restart modes

- Maskable interrupts on input capture or output compare

- DMA trigger capability on input capture or output compare

- · Four-channel general purpose timer

- 16-bit architecture

- Programmable prescaler

- Output pulse-widths variable from microseconds to seconds

- Single 16-bit input pulse accumulator

- Toggle-on-overflow feature for pulse-width modulator (PWM) generation

- One dual-mode pulse accumulation channel

- Pulse-width modulation timer

- Support for PCM mode (resulting in superior signal quality compared to conventional PWM)

- Operates as eight channels with 8-bit resolution or four channels with 16-bit resolution

- Programmable period and duty cycle

- Programmable enable/disable for each channel

- Software selectable polarity for each channel

- Period and duty cycle are double buffered. Change takes effect when the end of the current period is reached (PWM counter reaches zero) or when the channel is disabled.

- Programmable center or left aligned outputs on individual channels

- Four clock sources (A, B, SA, and SB) provide for a wide range of frequencies

- Emergency shutdown

- Two periodic interrupt timers (PITs)

- 16-bit counter

- Selectable as free running or count down

- Real-Time Clock (RTC)

- Maintains system time-of-day clock

- Provides stopwatch and alarm interrupt functions

- Software watchdog timer

- 32-bit counter

- Low-power mode support

- Backup watchdog timer (BWT)

- Independent timer that can be used to help software recover from runaway code

- 16-bit counter

- Low-power mode support

- Clock generation features

- Twelve to 48 MHz crystal, 8 MHz on-chip trimmed relaxation oscillator, or external oscillator reference options

- Two to 10 MHz reference frequency for normal PLL mode with a pre-divider programmable from 1 to 8

- System can be clocked from PLL or directly from crystal oscillator or relaxation oscillator

- Low power modes supported

- $2^n$  (n  $\leq 0 \leq 15$ ) low-power divider for extremely low frequency operation

- Interrupt controller

- Uniquely programmable vectors for all interrupt sources

- Fully programmable level and priority for all peripheral interrupt sources

- Seven external interrupt signals with fixed level and priority

- Unique vector number for each interrupt source

- Ability to mask any individual interrupt source or all interrupt sources (global mask-all)

- Support for hardware and software interrupt acknowledge (IACK) cycles

- Combinatorial path to provide wake-up from low-power modes

- DMA controller

- Four fully programmable channels

- Dual-address transfer support with 8-, 16-, and 32-bit data capability, along with support for 16-byte (4×32-bit) burst transfers

- Source/destination address pointers that can increment or remain constant

- 24-bit byte transfer counter per channel

- Auto-alignment transfers supported for efficient block movement

- Bursting and cycle-steal support

- Software-programmable DMA requests for the UARTs (3) and 32-bit timers (4)

- Channel linking support

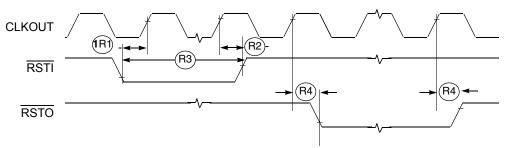

- Reset

- Separate reset in and reset out signals

- Seven sources of reset:

- Power-on reset (POR)

- External

- Software

- Watchdog

- Loss of clock / loss of lock

- Low-voltage detection (LVD)

- JTAG

- Status flag indication of source of last reset

- Chip configuration module (CCM)

- System configuration during reset

- Selects one of six clock modes

- Configures output pad drive strength

- Unique part identification number and part revision number

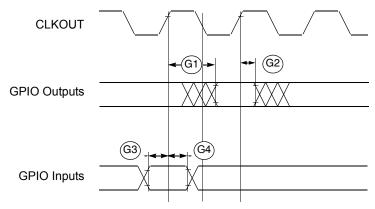

- General purpose I/O interface

- Up to 56 bits of general purpose I/O on 100-pin package

- Up to 96 bits of general purpose I/O on 144-pin package

- Bit manipulation supported via set/clear functions

- Programmable drive strengths

- Unused peripheral pins may be used as extra GPIO

- JTAG support for system level board testing

#### 1.2.2 V2 Core Overview

The version 2 ColdFire processor core is comprised of two separate pipelines decoupled by an instruction buffer. The two-stage instruction fetch pipeline (IFP) is responsible for instruction-address generation and instruction fetch. The instruction buffer is a first-in-first-out (FIFO) buffer that holds prefetched instructions awaiting execution in the operand execution pipeline (OEP). The OEP includes two pipeline stages. The first stage decodes instructions and selects operands (DSOC); the second stage (AGEX) performs instruction execution and calculates operand effective addresses, if needed.

The V2 core implements the ColdFire instruction set architecture revision A+ with support for a separate user stack pointer register and four new instructions to assist in bit processing. Additionally, the core includes the enhanced multiply-accumulate (EMAC) unit for improved signal processing capabilities. The EMAC implements a three-stage arithmetic pipeline, optimized for 32x32 bit operations, with support for four 48-bit accumulators. Supported operands include 16- and 32-bit signed and unsigned integers, signed fractional operands, and a complete set of instructions to process these data types. The EMAC provides support for execution of DSP operations within the context of a single processor at a minimal hardware cost.

## 1.2.3 Integrated Debug Module

The ColdFire processor core debug interface is provided to support system debugging with low-cost debug and emulator development tools. Through a standard debug interface, access to debug information and real-time tracing capability is provided on 144-lead packages. This allows the processor and system to be debugged at full speed without the need for costly in-circuit emulators.

The on-chip breakpoint resources include a total of nine programmable 32-bit registers: an address and an address mask register, a data and a data mask register, four PC registers, and one PC mask register. These registers can be accessed through the dedicated debug serial communication channel or from the processor's supervisor mode programming model. The breakpoint registers can be configured to generate triggers by combining the address, data, and PC conditions in a variety of single- or dual-level definitions. The trigger event can be programmed to generate a processor halt or initiate a debug interrupt exception. This device implements revision B+ of the ColdFire Debug Architecture.

The processor's interrupt servicing options during emulator mode allow real-time critical interrupt service routines to be serviced while processing a debug interrupt event. This ensures the system continues to operate even during debugging.

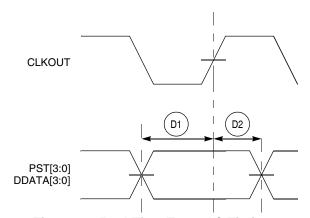

To support program trace, the V2 debug module provides processor status (PST[3:0]) and debug data (DDATA[3:0]) ports. These buses and the PSTCLK output provide execution status, captured operand data, and branch target addresses defining processor activity at the CPU's clock rate. The device includes a new debug signal, ALLPST. This signal is the logical AND of the processor status (PST[3:0]) signals and is useful for detecting when the processor is in a halted state (PST[3:0] = 1111).

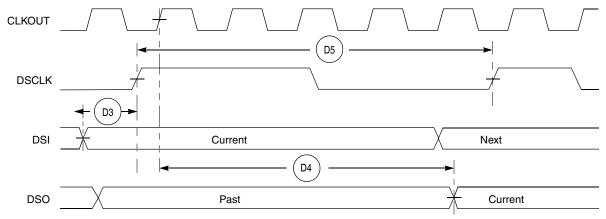

The full debug/trace interface is available only on the 144-pin packages. However, every product features the dedicated debug serial communication channel (DSI, DSO, DSCLK) and the ALLPST signal.

#### 1.2.4 JTAG

The processor supports circuit board test strategies based on the Test Technology Committee of IEEE and the Joint Test Action Group (JTAG). The test logic includes a test access port (TAP) consisting of a 16-state controller, an instruction register, and three test registers (a 1-bit bypass register, a boundary-scan register, and a 32-bit ID register). The boundary scan register links the device's pins into one shift register. Test logic, implemented using static logic design, is independent of the device system logic.

The device implementation can:

- Perform boundary-scan operations to test circuit board electrical continuity

- Sample system pins during operation and transparently shift out the result in the boundary scan register

- Bypass the device for a given circuit board test by effectively reducing the boundary-scan register to a single bit

- Disable the output drive to pins during circuit-board testing

- Drive output pins to stable levels

## 1.2.5 On-Chip Memories

#### 1.2.5.1 SRAM

The dual-ported SRAM module provides a general-purpose 64-Kbyte memory block that the ColdFire core can access in a single cycle. The location of the memory block can be set to any 64-Kbyte boundary within the 4-Gbyte address space. This memory is ideal for storing critical code or data structures and for use as the system stack. Because the SRAM module is physically connected to the processor's high-speed local bus, it can quickly service core-initiated accesses or memory-referencing commands from the debug module.

The SRAM module is also accessible by the DMA, FEC, and USB. The dual-ported nature of the SRAM makes it ideal for implementing applications with double-buffer schemes, where the processor and a DMA device operate in alternate regions of the SRAM to maximize system performance.

#### 1.2.5.2 Flash Memory

The ColdFire flash module (CFM) is a non-volatile memory (NVM) module that connects to the processor's high-speed local bus. The CFM is constructed with four banks of 64-Kbyte×16-bit flash memory arrays to generate 512 Kbytes of 32-bit flash memory. These electrically erasable and programmable arrays serve as non-volatile program and data memory. The flash memory is ideal for program and data storage for single-chip applications, allowing for field reprogramming without requiring an external high voltage source. The CFM interfaces to the ColdFire core through an optimized read-only memory controller that supports interleaved accesses from the 2-cycle flash memory arrays. A backdoor mapping of the flash memory is used for all program, erase, and verify operations, as well as providing a read datapath for the DMA. Flash memory may also be programmed via the EzPort, which is a serial flash memory programming interface that allows the flash memory to be read, erased and programmed by an external controller in a format compatible with most SPI bus flash memory chips.

## 1.2.6 Cryptographic Acceleration Unit

The MCF52235 device incorporates two hardware accelerators for cryptographic functions. First, the CAU is a coprocessor tightly-coupled to the V2 ColdFire core that implements a set of specialized operations to increase the throughput of software-based encryption and message digest functions, specifically the DES, 3DES, AES, MD5 and SHA-1 algorithms. Second, a random number generator provides FIPS-140 compliant 32-bit values to security processing routines. Both modules supply critical acceleration to software-based cryptographic algorithms at a minimal hardware cost.

## 1.2.7 Power Management

The device incorporates several low-power modes of operation entered under program control and exited by several external trigger events. An integrated power-on reset (POR) circuit monitors the input supply and forces an MCU reset as the supply voltage rises. The low voltage detector (LVD) monitors the supply voltage and is configurable to force a reset or interrupt condition if it falls below the LVD trip point. The RAM standby switch provides power to RAM when the supply voltage to the chip falls below the standby battery voltage.

#### 1.2.8 FlexCAN

The FlexCAN module is a communication controller implementing version 2.0 of the CAN protocol parts A and B. The CAN protocol can be used as an industrial control serial data bus, meeting the specific requirements of reliable operation in a harsh EMI environment with high bandwidth. This instantiation of FlexCAN has 16 message buffers.

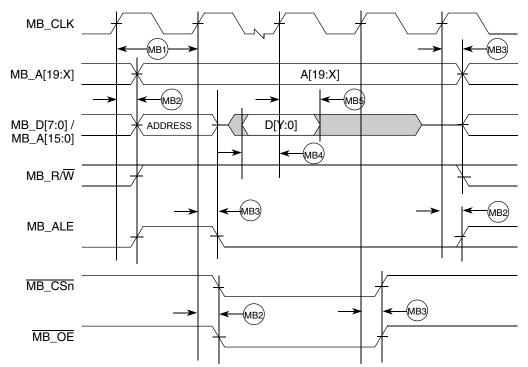

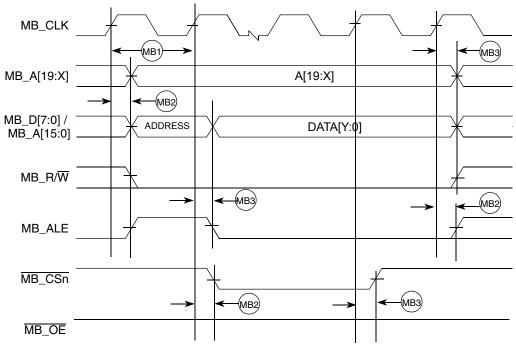

#### 1.2.9 Mini-FlexBus

A multi-function external bus interface called the Mini-FlexBus is provided on the device with basic functionality of interfacing to slave-only devices with a maximum slave bus frequency up to 40 MHz in 1:2 mode and 80 MHz in 1:1 mode. It can be directly connected to the following asynchronous or synchronous devices with little or no additional circuitry:

- External ROMs

- Flash memories

- Gate-array logic

- Other simple target (slave) devices

The Mini-FlexBus is a subset of the FlexBus module found on higher-end ColdFire microprocessors. The Mini-FlexBus minimizes package pin-outs while maintaining a high level of configurability and functionality.

#### 1.2.10 USB On-The-Go Controller

The device includes a Universal Serial Bus On-The-Go (USB OTG) dual-mode controller. USB is a popular standard for connecting peripherals and portable consumer electronic devices such as digital cameras and handheld computers to host PCs. The OTG supplement to the USB specification extends USB to peer-to-peer application, enabling devices to connect directly to each other without the need for a PC. The dual-mode controller on the device can act as a USB OTG host and as a USB device. It also supports full-speed and low-speed modes.

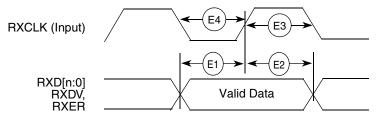

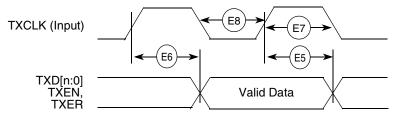

## 1.2.11 Fast Ethernet Controller (FEC)

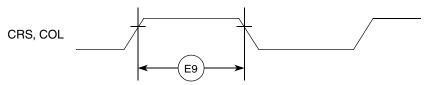

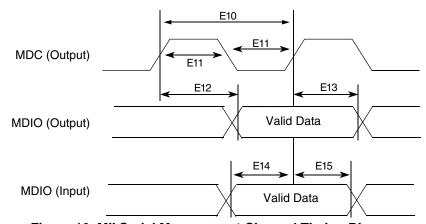

The Ethernet media access controller (MAC) supports 10 and 100 Mbps Ethernet/IEEE 802.3 networks. An external transceiver interface and transceiver function are required to complete the interface to the media. The FEC supports three different standard MAC-PHY (physical) interfaces for connection to an external Ethernet transceiver. The FECs supports the 10/100 Mbps MII, and the 10 Mbps-only 7-wire interface.

#### 1.2.12 **UARTs**

The device has three full-duplex UARTs that function independently. The three UARTs can be clocked by the system bus clock, eliminating the need for an external clock source. On smaller packages, the third UART is multiplexed with other digital I/O functions.

## 1.2.13 I<sup>2</sup>C Bus

The processor includes two I<sup>2</sup>C modules. The I<sup>2</sup>C bus is an industry-standard, two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange and minimizes the interconnection between devices. This bus is suitable for applications requiring occasional communications over a short distance between many devices.

#### 1.2.14 QSPI

The queued serial peripheral interface (QSPI) provides a synchronous serial peripheral interface with queued transfer capability. It allows up to 16 transfers to be queued at once, minimizing the need for CPU intervention between transfers.

#### 1.2.15 Fast ADC

The fast ADC consists of an eight-channel input select multiplexer and two independent sample and hold (S/H) circuits feeding separate 12-bit ADCs. The two separate converters store their results in accessible buffers for further processing. Signals on the SYNCA and SYNCB pins initiate an ADC conversion.

MCF52259 ColdFire Microcontroller, Rev. 0

The ADC can be configured to perform a single scan and halt, a scan when triggered, or a programmed scan sequence repeatedly until manually stopped.

The ADC can be configured for sequential or simultaneous conversion. When configured for sequential conversions, up to eight channels can be sampled and stored in any order specified by the channel list register. Both ADCs may be required during a scan, depending on the inputs to be sampled.

During a simultaneous conversion, both S/H circuits are used to capture two different channels at the same time. This configuration requires that a single channel may not be sampled by both S/H circuits simultaneously.

Optional interrupts can be generated at the end of the scan sequence if a channel is out of range (measures below the low threshold limit or above the high threshold limit set in the limit registers) or at several different zero crossing conditions.

#### 1.2.16 DMA Timers (DTIM0-DTIM3)

There are four independent, DMA transfer capable 32-bit timers (DTIM0, DTIM1, DTIM2, and DTIM3) on the device. Each module incorporates a 32-bit timer with a separate register set for configuration and control. The timers can be configured to operate from the system clock or from an external clock source using one of the DTINn signals. If the system clock is selected, it can be divided by 16 or 1. The input clock is further divided by a user-programmable 8-bit prescaler that clocks the actual timer counter register (TCRn). Each of these timers can be configured for input capture or reference (output) compare mode. Timer events may optionally cause interrupt requests or DMA transfers.

## 1.2.17 General Purpose Timer (GPT)

The general purpose timer (GPT) is a four-channel timer module consisting of a 16-bit programmable counter driven by a seven-stage programmable prescaler. Each of the four channels can be configured for input capture or output compare. Additionally, channel three, can be configured as a pulse accumulator.

A timer overflow function allows software to extend the timing capability of the system beyond the 16-bit range of the counter. The input capture and output compare functions allow simultaneous input waveform measurements and output waveform generation. The input capture function can capture the time of a selected transition edge. The output compare function can generate output waveforms and timer software delays. The 16-bit pulse accumulator can operate as a simple event counter or a gated time accumulator.

## 1.2.18 Periodic Interrupt Timers (PIT0 and PIT1)

The two periodic interrupt timers (PIT0 and PIT1) are 16-bit timers that provide interrupts at regular intervals with minimal processor intervention. Each timer can count down from the value written in its PIT modulus register or it can be a free-running down-counter.

## 1.2.19 Real-Time Clock (RTC)

The Real-Time Clock (RTC) module maintains the system (time-of-day) clock and provides stopwatch, alarm, and interrupt functions. It includes full clock features: seconds, minutes, hours, days and supports a host of time-of-day interrupt functions along with an alarm interrupt.

## 1.2.20 Pulse-Width Modulation (PWM) Timers

The device has an 8-channel, 8-bit PWM timer. Each channel has a programmable period and duty cycle as well as a dedicated counter. Each of the modulators can create independent continuous waveforms with software-selectable duty rates from 0% to 100%. The timer supports PCM mode, which results in superior signal quality when compared to that of a conventional PWM. The PWM outputs have programmable polarity, and can be programmed as left aligned outputs or center aligned outputs. For

higher period and duty cycle resolution, each pair of adjacent channels ([7:6], [5:4], [3:2], and [1:0]) can be concatenated to form a single 16-bit channel. The module can, therefore, be configured to support 8/0, 6/1, 4/2, 2/3, or 0/4 8-/16-bit channels.

## 1.2.21 Software Watchdog Timer

The watchdog timer is a 32-bit timer that facilitates recovery from runaway code. The watchdog counter is a free-running down-counter that generates a reset on underflow. To prevent a reset, software must periodically restart the countdown.

## 1.2.22 Backup Watchdog Timer

The backup watchdog timer is an independent 16-bit timer that, like the software watchdog timer, facilitates recovery from runaway code. This timer is a free-running down-counter that generates a reset on underflow. To prevent a reset, software must periodically restart the countdown. The backup watchdog timer can be clocked by either the relaxation oscillator or the system clock.

## 1.2.23 Phase-Locked Loop (PLL)

The clock module contains a crystal oscillator, 8 MHz on-chip relaxation oscillator (OCO), phase-locked loop (PLL), reduced frequency divider (RFD), low-power divider status/control registers, and control logic. To improve noise immunity, the PLL, crystal oscillator, and relaxation oscillator have their own power supply inputs: VDDPLL and VSSPLL. All other circuits are powered by the normal supply pins, VDD and VSS.

## 1.2.24 Interrupt Controllers (INTCn)

The device has two interrupt controllers that supports up to 128 interrupt sources. There are 56 programmable sources, 49 of which are assigned to unique peripheral interrupt requests. The remaining seven sources are unassigned and may be used for software interrupt requests.

#### 1.2.25 DMA Controller

The direct memory access (DMA) controller provides an efficient way to move blocks of data with minimal processor intervention. It has four channels that allow byte, word, longword, or 16-byte burst line transfers. These transfers are triggered by software explicitly setting a DCRn[START] bit or by the occurrence of certain UART or DMA timer events.

#### 1.2.26 Reset

The reset controller determines the source of reset, asserts the appropriate reset signals to the system, and keeps track of what caused the last reset. There are seven sources of reset:

- External reset input

- Power-on reset (POR)

- Watchdog timer

- Phase locked-loop (PLL) loss of lock / loss of clock

- Software

- Low-voltage detector (LVD)

- JTAG

Control of the LVD and its associated reset and interrupt are managed by the reset controller. Other registers provide status flags indicating the last source of reset and a control bit for software assertion of the  $\overline{RSTO}$  pin.

### 1.2.27 GPIO

Nearly all pins on the device have general purpose I/O capability and are grouped into 8-bit ports. Some ports do not use all eight bits. Each port has registers that configure, monitor, and control the port pin.

## 1.2.28 Part Numbers and Packaging

This product is RoHS-compliant. Refer to the product page at freescale.com or contact your sales office for up-to-date RoHS information.

**Table 2. Orderable Part Number Summary**

| Freescale Part<br>Number | Description              | Speed<br>(MHz) | Flash/SRAM<br>(Kbytes) | Package   | Temp range (°C) |

|--------------------------|--------------------------|----------------|------------------------|-----------|-----------------|

| MCF52221CAE66            | MCF52221 Microcontroller | 66             | 128/16                 | 64 LQFP   | -40 to +85      |

| MCF52221CVM66            | MCF52221 Microcontroller | 66             | 128/16                 | 81 MAPBGA | -40 to +85      |

| MCF52221CAF66            | MCF52221 Microcontroller | 66             | 128/16                 | 100 LQFP  | -40 to +85      |

| MCF52221CVM80            | MCF52221 Microcontroller | 80             | 128/16                 | 81 MAPBGA | -40 to +85      |

| MCF52221CAF80            | MCF52221 Microcontroller | 80             | 128/16                 | 100 LQFP  | -40 to +85      |

| MCF52223CVM66            | MCF52223 Microcontroller | 66             | 128/16                 | 81 MAPBGA | -40 to +85      |

| MCF52223CAF66            | MCF52223 Microcontroller | 66             | 128/16                 | 100 LQFP  | -40 to +85      |

| MCF52223CVM80            | MCF52223 Microcontroller | 80             | 128/16                 | 81 MAPBGA | -40 to +85      |

| MCF52223CAF80            | MCF52223 Microcontroller | 80             | 128/16                 | 100 LQFP  | -40 to +85      |

**Table 3. Orderable Part Number Summary**

| Freescale Part<br>Number | FlexCAN | Encryption | Speed<br>(MHz) | Flash<br>(Kbytes) | SRAM<br>(Kbytes) | Package    | Temp range (°C) |

|--------------------------|---------|------------|----------------|-------------------|------------------|------------|-----------------|

| MCF52252AF80             | _       | _          | 80             | 256               | 32               | 100 LQFP   | 0 to +70        |

| MCF52252CAF66            | •       | _          | 66             | 230               | 32               | 100 LQIT   | -40 to +85      |

| MCF52254AF80             | _       | _          | 80             | 512               | 64 100 LQFP      |            | 0 to +70        |

| MCF52254CAF66            | •       | _          | 66             | 312               | 04               | 100 LQFF   | -40 to +85      |

| MCF52255CAF80            | •       | •          | 80             | 512               | 64               | 100 LQFP   | -40 to +85      |

| MCF52256AG80             | _       | _          | 80             |                   | 32               | 144 LQFP   | 0 to +70        |

| MCF52256CAG66            | •       | _          | 66             | 256               | 64               | 144 LQII   | -40 to +85      |

| MCF52256CVN66            | •       | _          | 66             | 230               | 64               | 144 MAPBGA | -40 to +85      |

| MCF52256VN80             | _       | _          | 80             |                   | 32               | 144 MAFBOA | 0 to +70        |

**Table 3. Orderable Part Number Summary (continued)**

| Freescale Part<br>Number | FlexCAN | Encryption | Speed<br>(MHz) | Flash<br>(Kbytes) | SRAM<br>(Kbytes) | Package     | Temp range (°C) |

|--------------------------|---------|------------|----------------|-------------------|------------------|-------------|-----------------|

| MCF52258AG80             | _       | _          | 80             |                   |                  | 144 LQFP    | 0 to +70        |

| MCF52258CAG66            | •       | _          | 66             | 512               | 64               | 177 LQII    | -40 to +85      |

| MCF52258CVN66            | •       | _          | 66             | 312               | 04               | 144 MAPBGA  | -40 to +85      |

| MCF52258VN80             | _       | _          | 80             |                   |                  | 144 MAI DOA | 0 to +70        |

| MCF52259CAG80            | •       | •          | 80             | 512               | 64               | 144 LQFP    | -40 to +85      |

| MCF52259CVN80            | •       | •          | 00             | 512               | 5                | 144 MAPBGA  | -40 to +85      |

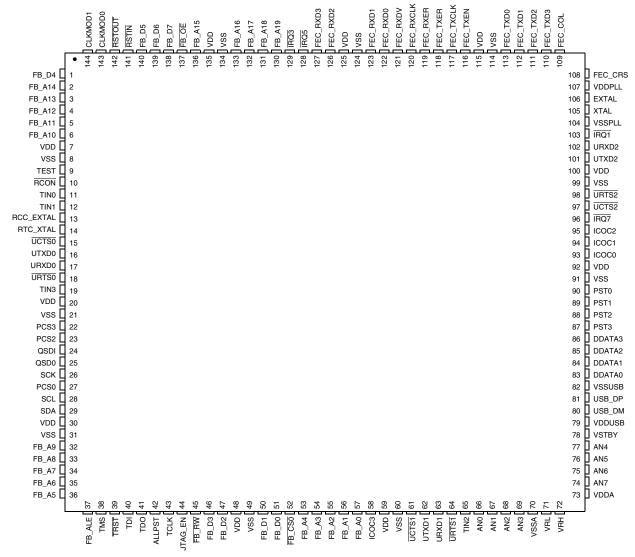

Figure 2 shows the pinout configuration for the 144 LQFP.

Figure 2. 144 LQFP Pin Assignment

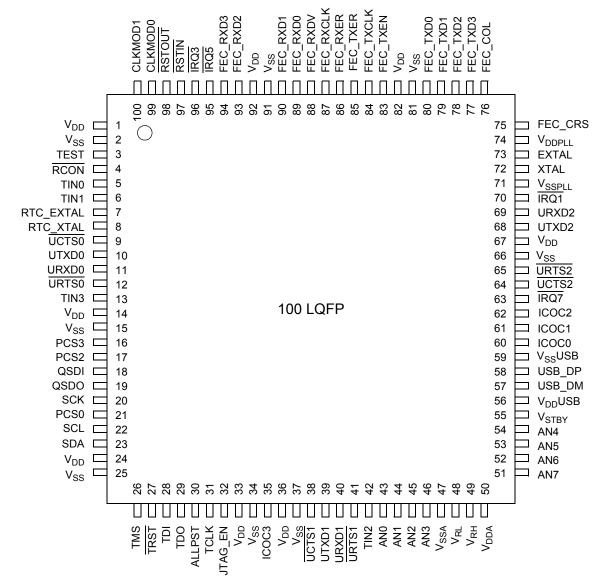

Figure 3 shows the pinout configuration for the 100 LQFP.

Figure 3. 100 LQFP Pin Assignments

MCF52259 ColdFire Microcontroller, Rev. 0

Figure 4 shows the pinout configuration for the 144 MAPBGA.

|   | 1             | 2           | 3      | 4       | 5       | 6      | 7            | 8             | 9             | 10           | 11           | 12      |   |

|---|---------------|-------------|--------|---------|---------|--------|--------------|---------------|---------------|--------------|--------------|---------|---|

| Α | VSS           | RSTOUT      | RSTIN  | FB_D6   | FB_D7   | ĪRQ3   | ĪRQ5         | FEC_<br>RXD0  | FEC_<br>RXER  | FEC_<br>TXEN | FEC_<br>TXD3 | VSS     | Α |

| В | TEST          | FB_A14      | FB_D4  | FB_D5   | FB_OE   | FB_A19 | FEC_<br>RXD1 | FEC_<br>RXCLK | FEC_<br>TXCLK | FEC_<br>TXD2 | FEC_COL      | FEC_CRS | В |

| С | TIN1          | FB_A12      | FB_A13 | FB_A15  | FB_A16  | FB_A18 | FEC_<br>RXD2 | FEC_<br>RXDV  | FEC_<br>TXD1  | URXD2        | VDDPLL       | EXTAL   | С |

| D | RTC_<br>EXTAL | TIN0        | FB_A11 | CLKMOD1 | CLKMOD0 | FB_A17 | FEC_<br>RXD3 | FEC_<br>TXER  | FEC_<br>TXD0  | UTXD2        | VSSPLL       | XTAL    | D |

| Е | RTC_<br>XTAL  | UCTS0       | FB_A10 | RCON    | VDD     | VDD    | VDD          | VDD           | ĪRQ1          | URTS2        | UCTS2        | ĪRQ7    | Е |

| F | UTXD0         | URXD0       | URTS0  | TIN3    | VDD     | VSS    | VSS          | VSS           | PST3          | DDATA0       | DDATA1       | ICOC0   | F |

| G | QSDO          | QSDI        | PCS2   | PCS3    | VDD     | VSS    | VSS          | VSS           | DDATA3        | PST2         | PST1         | PST0    | G |

| н | SCL           | SDA         | SCK    | PCS0    | VDD     | VDD    | VDD          | VSS           | VSSUSB        | DDATA2       | USB_DM       | USB_DP  | Н |

| J | FB_A6         | FB_A7       | FB_A9  | FB_A8   | FB_D0   | FB_A3  | VDD          | TIN2          | VDDUSB        | ICOC2        | ICOC1        | VSTBY   | J |

| К | TMS           | TRST        | FB_ALE | FB_A5   | FB_D2   | FB_A4  | UCTS1        | UTXD1         | AN3           | AN6          | AN4          | AN5     | K |

| L | TDI           | TDO         | ALLPST | FB_D3   | FB_D1   | FB_A1  | FB_A0        | URXD1         | AN2           | VRH          | VDDA         | AN7     | L |

| М | VSS           | JTAG_<br>EN | TCLK   | FB_RW   | FB_CS0  | FB_A2  | ICOC3        | URTS1         | AN0           | AN1          | VRL          | VSSA    | М |

|   | 1             | 2           | 3      | 4       | 5       | 6      | 7            | 8             | 9             | 10           | 11           | 12      |   |

Figure 4. Pinout Top View (144 MAPBGA)

Table 4 shows the pin functions by primary and alternate purpose, and illustrates which packages contain each pin.

### **Table 4. Pin Functions by Primary and Alternate Purpose**

| Pin<br>Group     | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP | Pin on 81<br>MAPBGA | Pin on 64<br>LQFP/QFN |

|------------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|--------------------|---------------------|-----------------------|

| ADC              | AN7                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 51                 | H9                  | 33                    |

|                  | AN6                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 52                 | G9                  | 34                    |

|                  | AN5                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 53                 | G8                  | 35                    |

|                  | AN4                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 54                 | F9                  | 36                    |

|                  | AN3                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 46                 | G7                  | 28                    |

|                  | AN2                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 45                 | G6                  | 27                    |

|                  | AN1                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 44                 | H6                  | 26                    |

|                  | AN0                 | _                     | _                    | GPIO                   | Low                                         | FAST                                | _                                   | 43                 | J6                  | 25                    |

|                  | SYNCA <sup>3</sup>  | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | _                  | _                   | _                     |

|                  | SYNCB <sup>3</sup>  | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | _                  | _                   | _                     |

|                  | VDDA                | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 50                 | H8                  | 32                    |

|                  | VSSA                | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 47                 | H7, J9              | 29                    |

|                  | VRH                 | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 49                 | J8                  | 31                    |

|                  | VRL                 | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 48                 | J7                  | 30                    |

| Clock            | EXTAL               | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 73                 | B9                  | 47                    |

| Generation       | XTAL                | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 72                 | C9                  | 46                    |

|                  | VDDPLL              | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 74                 | B8                  | 48                    |

|                  | VSSPLL              | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 71                 | C8                  | 45                    |

| Debug Data       | ALLPST              | _                     | _                    | _                      | High                                        | FAST                                | _                                   | 86                 | A6                  | 55                    |

|                  | DDATA[3:0]          | _                     | _                    | GPIO                   | High                                        | FAST                                | _                                   | 84,83,78,77        | _                   | _                     |

|                  | PST[3:0]            | _                     | _                    | GPIO                   | High                                        | FAST                                | _                                   | 70,69,66,65        | _                   | _                     |

| I <sup>2</sup> C | SCL                 |                       | UTXD2                | GPIO                   | PDSR[0]                                     | PSRR[0]                             | pull-up <sup>4</sup>                | 10                 | E1                  | 8                     |

|                  | SDA                 |                       | URXD2                | GPIO                   | PDSR[0]                                     | PSRR[0]                             | pull-up <sup>4</sup>                | 11                 | E2                  | 9                     |

Table 4. Pin Functions by Primary and Alternate Purpose (continued)

| Pin<br>Group           | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP | Pin on 81<br>MAPBGA | Pin on 64<br>LQFP/QFN |

|------------------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|--------------------|---------------------|-----------------------|

| Interrupts             | IRQ7                | _                     | _                    | GPIO                   | Low                                         | FAST                                |                                     | 95                 | C4                  | 58                    |

|                        | ĪRQ6                | _                     |                      | GPIO                   | Low                                         | FAST                                |                                     | 94                 | B4                  | _                     |

|                        | ĪRQ5                | _                     | _                    | GPIO                   | Low                                         | FAST                                |                                     | 91                 | A4                  | _                     |

|                        | ĪRQ4                | _                     | _                    | GPIO                   | Low                                         | FAST                                |                                     | 90                 | C5                  | 57                    |

|                        | ĪRQ3                | _                     |                      | GPIO                   | Low                                         | FAST                                |                                     | 89                 | A5                  | _                     |

|                        | ĪRQ2                | _                     | _                    | GPIO                   | Low                                         | FAST                                |                                     | 88                 | B5                  | _                     |

|                        | ĪRQ1                | SYNCA                 |                      | GPIO                   | High                                        | FAST                                | pull-up <sup>4</sup>                | 87                 | C6                  | 56                    |

| JTAG/BDM               | JTAG_EN             | _                     |                      | _                      | N/A                                         | N/A                                 | pull-down                           | 26                 | J2                  | 17                    |

|                        | TCLK/<br>PSTCLK     | CLKOUT                | _                    | _                      | High                                        | FAST                                | pull-up <sup>5</sup>                | 64                 | C7                  | 44                    |

|                        | TDI/DSI             | _                     |                      | _                      | N/A                                         | N/A                                 | pull-up <sup>5</sup>                | 79                 | B7                  | 50                    |

|                        | TDO/DSO             | _                     |                      | _                      | High                                        | FAST                                | _                                   | 80                 | A7                  | 51                    |

|                        | TMS<br>/BKPT        | _                     |                      | _                      | N/A                                         | N/A                                 | pull-up <sup>5</sup>                | 76                 | A8                  | 49                    |

|                        | TRST<br>/DSCLK      | _                     | _                    | _                      | N/A                                         | N/A                                 | pull-up <sup>5</sup>                | 85                 | В6                  | 54                    |

| Mode                   | CLKMOD0             | _                     | _                    | _                      | N/A                                         | N/A                                 | pull-down <sup>6</sup>              | 40                 | G5                  | 24                    |

| Selection <sup>6</sup> | CLKMOD1             | _                     |                      | _                      | N/A                                         | N/A                                 | pull-down <sup>6</sup>              | 39                 | H5                  | _                     |

|                        | RCON/<br>EZPCS      | _                     |                      | _                      | N/A                                         | N/A                                 | pull-up                             | 21                 | G3                  | 16                    |

MCF52259 ColdFire Microcontroller, Rev. 0

## Table 4. Pin Functions by Primary and Alternate Purpose (continued)

| Pin<br>Group       | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP | Pin on 81<br>MAPBGA | Pin on 64<br>LQFP/QFN |

|--------------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|--------------------|---------------------|-----------------------|

| QSPI               | QSPI_DIN/<br>EZPD   |                       | URXD1                | GPIO                   | PDSR[2]                                     | PSRR[2]                             | _                                   | 16                 | F3                  | 12                    |

|                    | QSPI_DOUT/<br>EZPQ  |                       | UTXD1                | GPIO                   | PDSR[1]                                     | PSRR[1]                             | _                                   | 17                 | G1                  | 13                    |

|                    | QSPI_CLK/<br>EZPCK  | SCL                   | URTS1                | GPIO                   | PDSR[3]                                     | PSRR[3]                             | pull-up <sup>7</sup>                | 18                 | G2                  | 14                    |

|                    | QSPI_CS3            | SYNCA                 |                      | GPIO                   | PDSR[7]                                     | PSRR[7]                             |                                     | 12                 | F1                  | _                     |

|                    | QSPI_CS2            |                       | _                    | GPIO                   | PDSR[6]                                     | PSRR[6]                             |                                     | 13                 | F2                  | _                     |

|                    | QSPI_CS1            | _                     | _                    | GPIO                   | PDSR[5]                                     | PSRR[5]                             | _                                   | 19                 | H2                  | _                     |

|                    | QSPI_CS0            | SDA                   | UCTS1                | GPIO                   | PDSR[4]                                     | PSRR[4]                             | pull-up <sup>7</sup>                | 20                 | H1                  | 15                    |

| Reset <sup>8</sup> | RSTI                | _                     | _                    | _                      | N/A                                         | N/A                                 | pull-up <sup>8</sup>                | 96                 | А3                  | 59                    |

|                    | RSTO                | _                     | _                    | _                      | high                                        | FAST                                | _                                   | 97                 | В3                  | 60                    |

| Test               | TEST                | _                     |                      | _                      | N/A                                         | N/A                                 | pull-down                           | 5                  | C2                  | 3                     |

| Timers, 16-bit     | GPT3                | _                     | PWM7                 | GPIO                   | PDSR[23]                                    | PSRR[23]                            | pull-up <sup>9</sup>                |                    |                     |                       |

|                    | GPT2                | _                     | PWM5                 | GPIO                   | PDSR[22]                                    | PSRR[22]                            | pull-up <sup>9</sup>                |                    |                     |                       |

|                    | GPT1                | _                     | PWM3                 | GPIO                   | PDSR[21]                                    | PSRR[21]                            | pull-up <sup>9</sup>                |                    |                     |                       |

|                    | GPT0                | _                     | PWM1                 | GPIO                   | PDSR[20]                                    | PSRR[20]                            | pull-up <sup>9</sup>                |                    |                     |                       |

| Timers, 32-bit     | DTIN3               | DTOUT3                | PWM6                 | GPIO                   | PDSR[19]                                    | PSRR[19]                            | _                                   | 32                 | H3                  | 19                    |

|                    | DTIN2               | DTOUT2                | PWM4                 | GPIO                   | PDSR[18]                                    | PSRR[18]                            | _                                   | 31                 | J3                  | 18                    |

|                    | DTIN1               | DTOUT1                | PWM2                 | GPIO                   | PDSR[17]                                    | PSRR[17]                            | _                                   | 37                 | G4                  | 23                    |

|                    | DTIN0               | DTOUT0                | PWM0                 | GPIO                   | PDSR[16]                                    | PSRR[16]                            | _                                   | 36                 | H4                  | 22                    |

| UART 0             | UCTS0               |                       | _                    | GPIO                   | PDSR[11]                                    | PSRR[11]                            | _                                   | 6                  | C1                  | 4                     |

|                    | URTS0               |                       | _                    | GPIO                   | PDSR[10]                                    | PSRR[10]                            | _                                   | 9                  | D3                  | 7                     |

|                    | URXD0               |                       | _                    | GPIO                   | PDSR[9]                                     | PSRR[9]                             | _                                   | 7                  | D1                  | 5                     |

|                    | UTXD0               |                       | _                    | GPIO                   | PDSR[8]                                     | PSRR[8]                             | _                                   | 8                  | D2                  | 6                     |

#### Table 4. Pin Functions by Primary and Alternate Purpose (continued)

| Pin<br>Group | Primary<br>Function | Secondary<br>Function | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength /<br>Control <sup>1</sup> | Slew Rate /<br>Control <sup>1</sup> | Pull-up /<br>Pull-down <sup>2</sup> | Pin on<br>100 LQFP                      | Pin on 81<br>MAPBGA      | Pin on 64<br>LQFP/QFN |

|--------------|---------------------|-----------------------|----------------------|------------------------|---------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------|--------------------------|-----------------------|

| UART 1       | UCTS1               | SYNCA                 | URXD2                | GPIO                   | PDSR[15]                                    | PSRR[15]                            | _                                   | 98                                      | C3                       | 61                    |

|              | URTS1               | SYNCB                 | UTXD2                | GPIO                   | PDSR[14]                                    | PSRR[14]                            | _                                   | 4                                       | B1                       | 2                     |

|              | URXD1               |                       | _                    | GPIO                   | PDSR[13]                                    | PSRR[13]                            | _                                   | 100                                     | B2                       | 63                    |

|              | UTXD1               |                       | _                    | GPIO                   | PDSR[12]                                    | PSRR[12]                            | _                                   | 99                                      | A2                       | 62                    |

| UART 2       | UCTS2               |                       | _                    | GPIO                   | PDSR[27]                                    | PSRR[27]                            | _                                   | 27                                      | _                        | _                     |

|              | URTS2               |                       | _                    | GPIO                   | PDSR[26]                                    | PSRR[26]                            | _                                   | 30                                      | _                        | _                     |

|              | URXD2               | _                     | _                    | GPIO                   | PDSR[25]                                    | PSRR[25]                            | _                                   | 28                                      | _                        | _                     |

|              | UTXD2               | _                     | _                    | GPIO                   | PDSR[24]                                    | PSRR[24]                            | _                                   | 29                                      | _                        | _                     |

| VSTBY        | VSTBY               | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 55                                      | F8                       | 37                    |

| VDD          | VDD                 | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 1,2,14,22,<br>23,34,41,<br>57,68,81,93  | D5,E3–E7,<br>F5          | 1,10,20,39,5<br>2     |

| VSS          | VSS                 | _                     | _                    | _                      | N/A                                         | N/A                                 | _                                   | 3,15,24,25,3<br>5,42,56,<br>67,75,82,92 | A1,A9,D4,D<br>6,F4,F6,J1 | 11,21,38,<br>53,64    |

<sup>1</sup> The PDSR and PSSR registers are described in the General Purpose I/O chapter. All programmable signals default to 2 mA drive and FAST slew rate in normal (single-chip) mode.

All signals have a pull-up in GPIO mode.

These signals are multiplexed on other pins.

For primary and GPIO functions only.

Only when JTAG mode is enabled.

CLKMOD0 and CLKMOD1 have internal pull-down resistors; however, the use of external resistors is very strongly recommended.

For secondary and GPIO functions only.

RSTI has an internal pull-up resistor; however, the use of an external resistor is very strongly recommended.

For GPIO function. Primary Function has pull-up control within the GPT module.

Table 5. Pin Functions by Primary and Alternate Purpose

| Pin Group  | Primary<br>Function | SecondaryF<br>unction | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength/<br>Control <sup>1</sup> | Wired OR<br>Control | Pull-up/<br>Pull-down <sup>2</sup> | Pin on<br>144 MAPBGA       | Pin on<br>144 LQFP  | Pin on<br>100 LQFP |

|------------|---------------------|-----------------------|----------------------|------------------------|--------------------------------------------|---------------------|------------------------------------|----------------------------|---------------------|--------------------|

| ADC        | AN[7:0]             | _                     | _                    | PAN[7:0]               | N/A                                        | _                   | _                                  | K9-K12; L9,<br>L12; M9-M10 | 74–77;<br>66–69     | 43–46;<br>51–54    |

|            | VDDA                | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | L11                        | 73                  | 50                 |

|            | VSSA                | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | M12                        | 70                  | 47                 |

|            | VRH                 | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | L10                        | 72                  | 49                 |

|            | VRL                 | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | M11                        | 71                  | 48                 |

| Clock      | EXTAL               | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | C12                        | 106                 | 73                 |

| Generation | XTAL                | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | D12                        | 105                 | 72                 |

|            | VDDPLL              | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | C11                        | 107                 | 74                 |

|            | VSSPLL              | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | D11                        | 104                 | 71                 |

| RTC        | RTC_EXTAL           | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | D1                         | 33                  | 7                  |

|            | RTC_XTAL            | _                     | _                    | _                      | N/A                                        | N/A                 | _                                  | E1                         | 34                  | 8                  |

| Debug      | ALLPST              | _                     | _                    | _                      | High                                       | _                   | _                                  | L3                         | 42                  | 30                 |

| Data       | DDATA[3:0]          | _                     | _                    | PDD[7:4]               | High                                       | _                   | _                                  | F10–F11; G9;<br>H10        | 83–86               | _                  |

|            | PST[3:0]            | _                     | _                    | PDD[3:0]               | High                                       | _                   | _                                  | F9; G10–G12                | 87–90               | _                  |

| FEC        | FEC_COL             | _                     | _                    | PTI0                   | Low                                        |                     |                                    | B11                        | 109                 | 76                 |