## F28M35x Concerto™ Microcontrollers

### 1 Features

- Master Subsystem — Arm® Cortex®-M3

- Up to 100 MHz

- Embedded memory

- Up to 512KB of flash (ECC)

- Up to 32KB of RAM (ECC or parity)

- Up to 64KB of shared RAM

- 2KB of IPC Message RAM

- Five Universal Asynchronous Receiver/Transmitters (UARTs)

- Four Synchronous Serial Interfaces (SSIs) and a Serial Peripheral Interface (SPI)

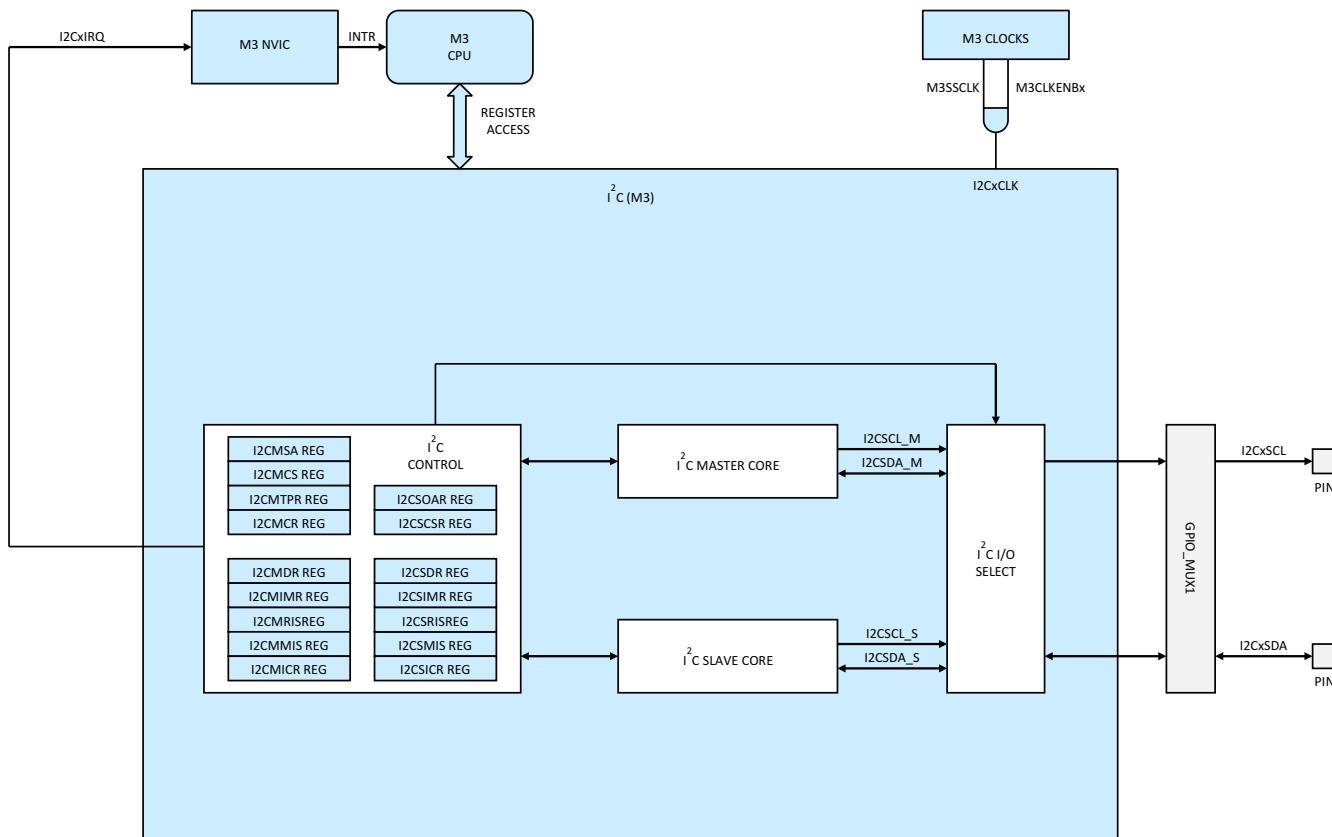

- Two Inter-integrated Circuits (I2Cs)

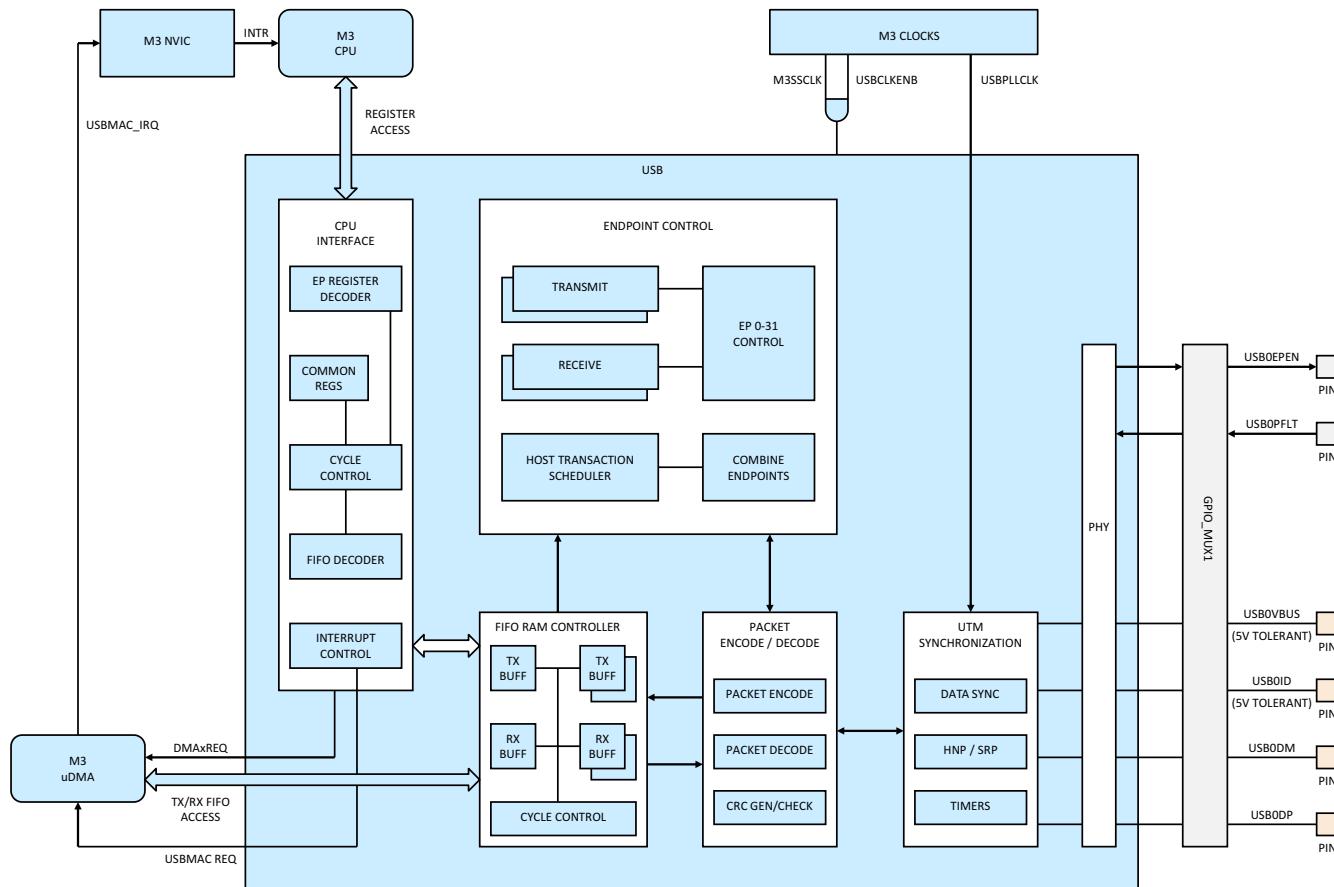

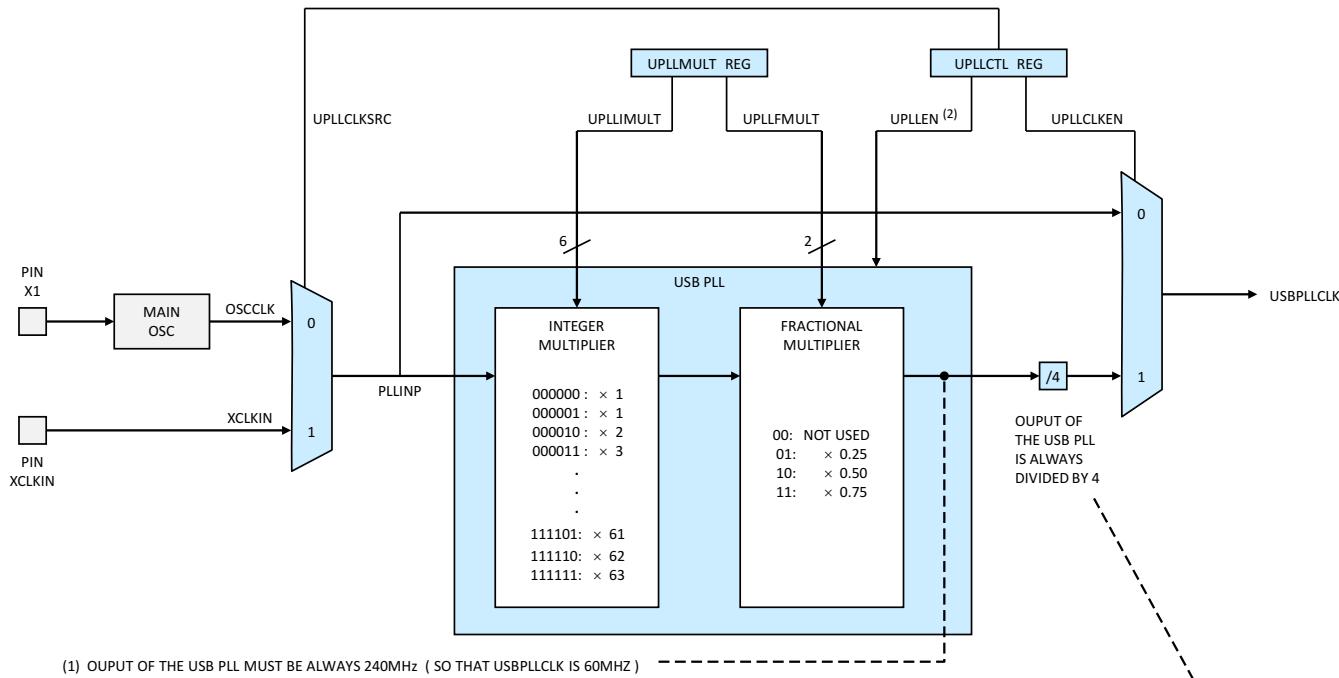

- Universal Serial Bus On-the-Go (USB-OTG) + PHY

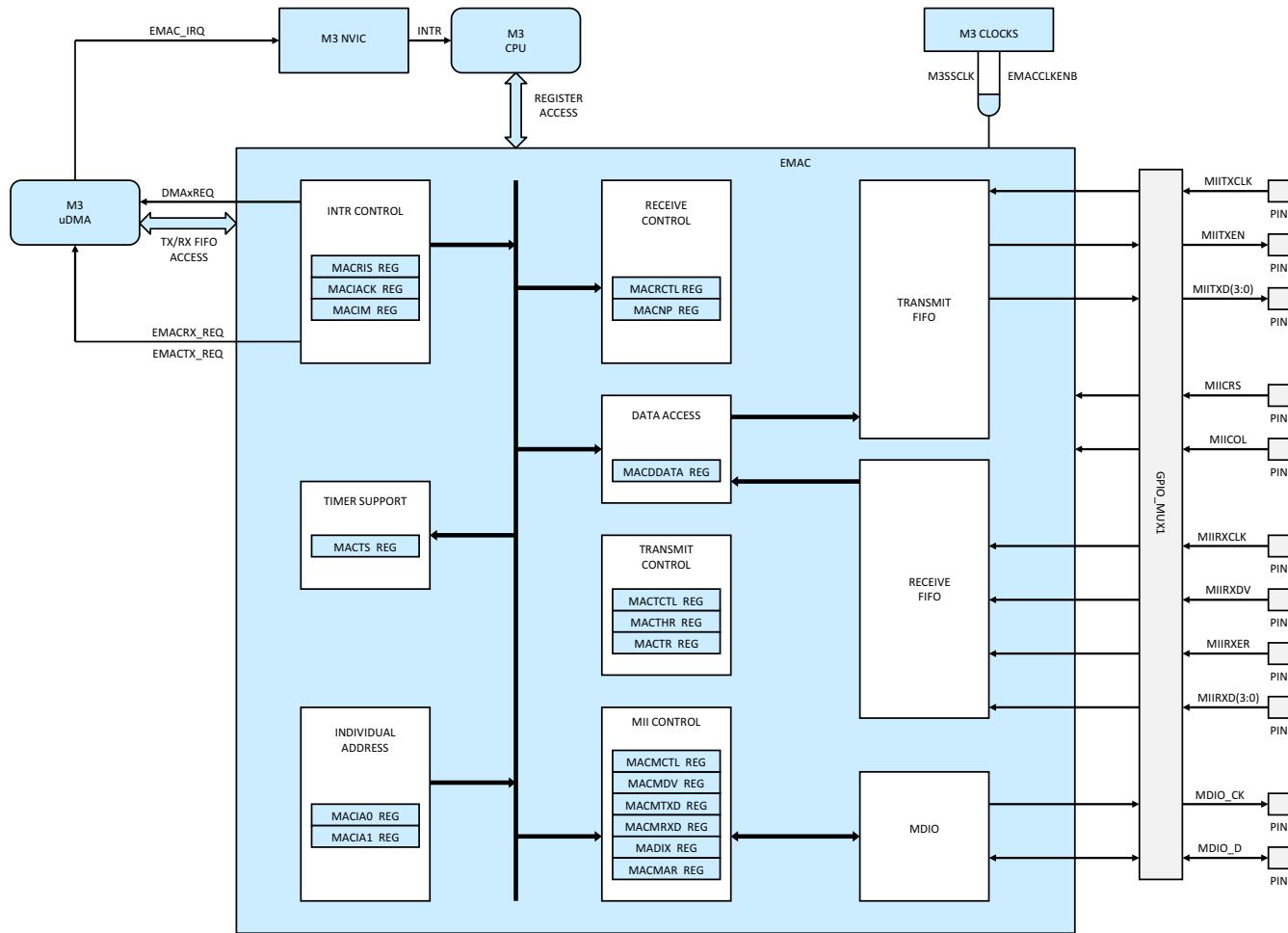

- 10/100 ENET 1588 MII

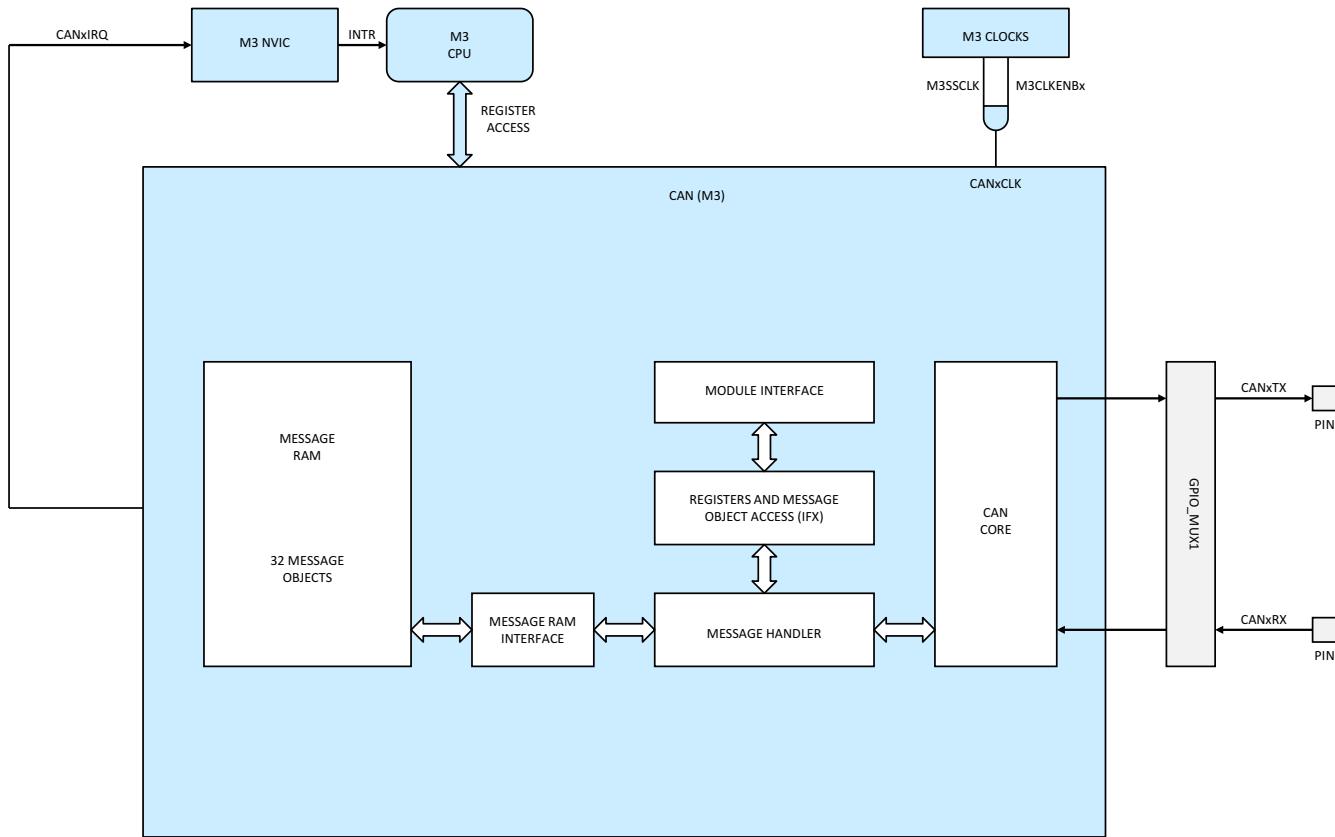

- Two Controller Area Network, D\_CAN, modules (pin-bootable)

- 32-channel Micro Direct Memory Access (μDMA)

- Dual security zones (128-bit password per zone)

- External Peripheral Interface (EPI)

- Micro Cyclic Redundancy Check (μCRC) module

- Four general-purpose timers

- Two watchdog timer modules

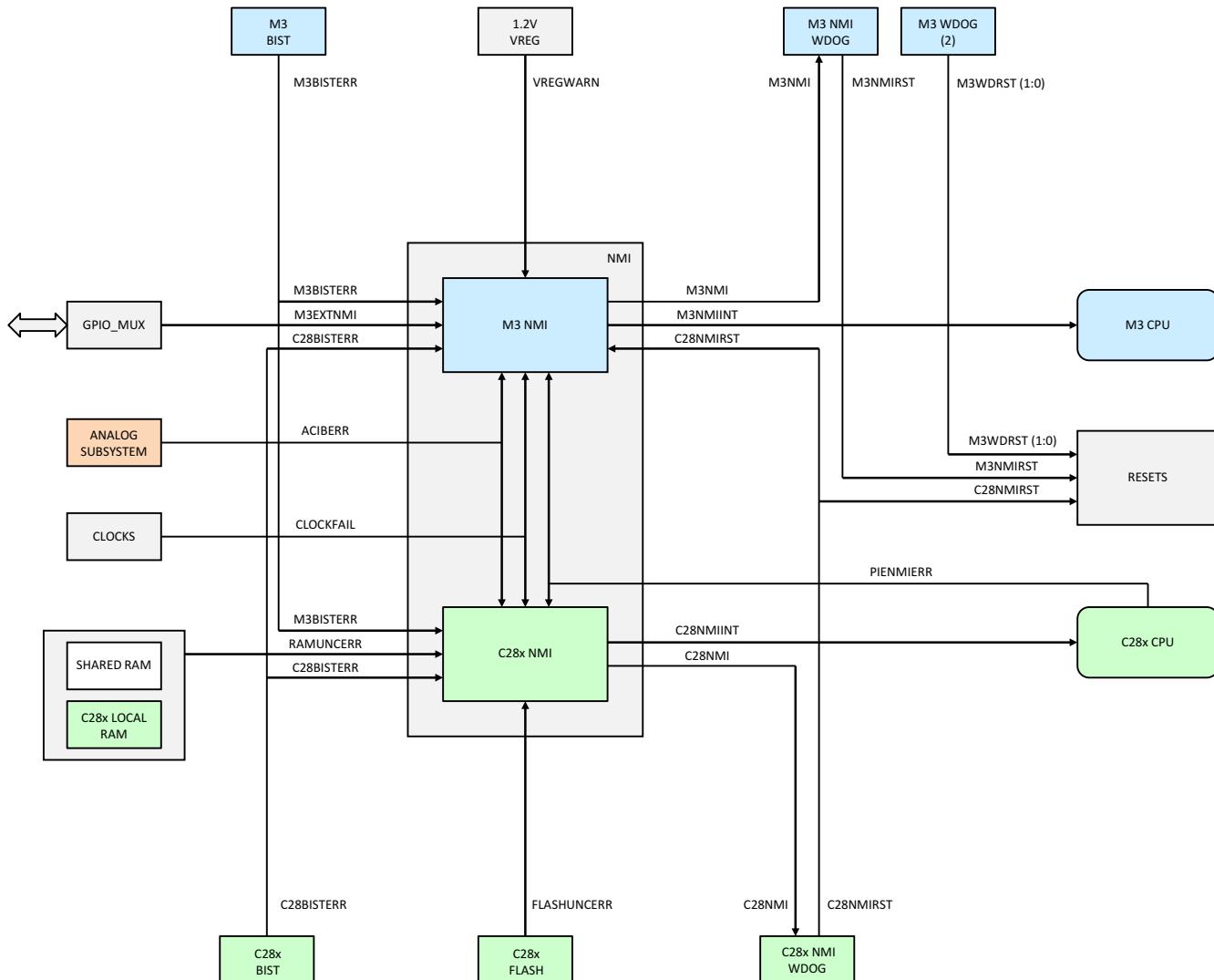

- Three external interrupts

- Endianness: little endian

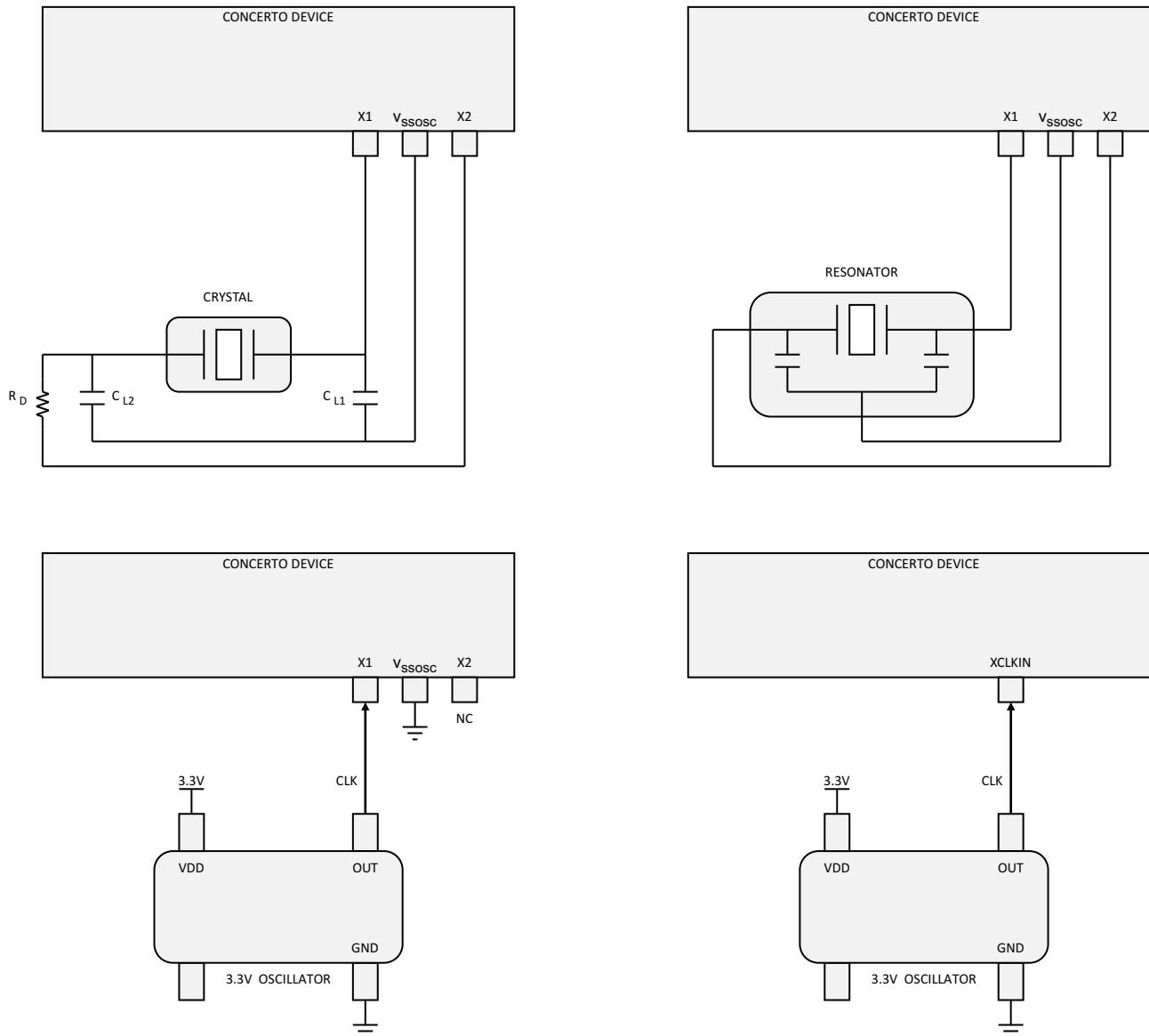

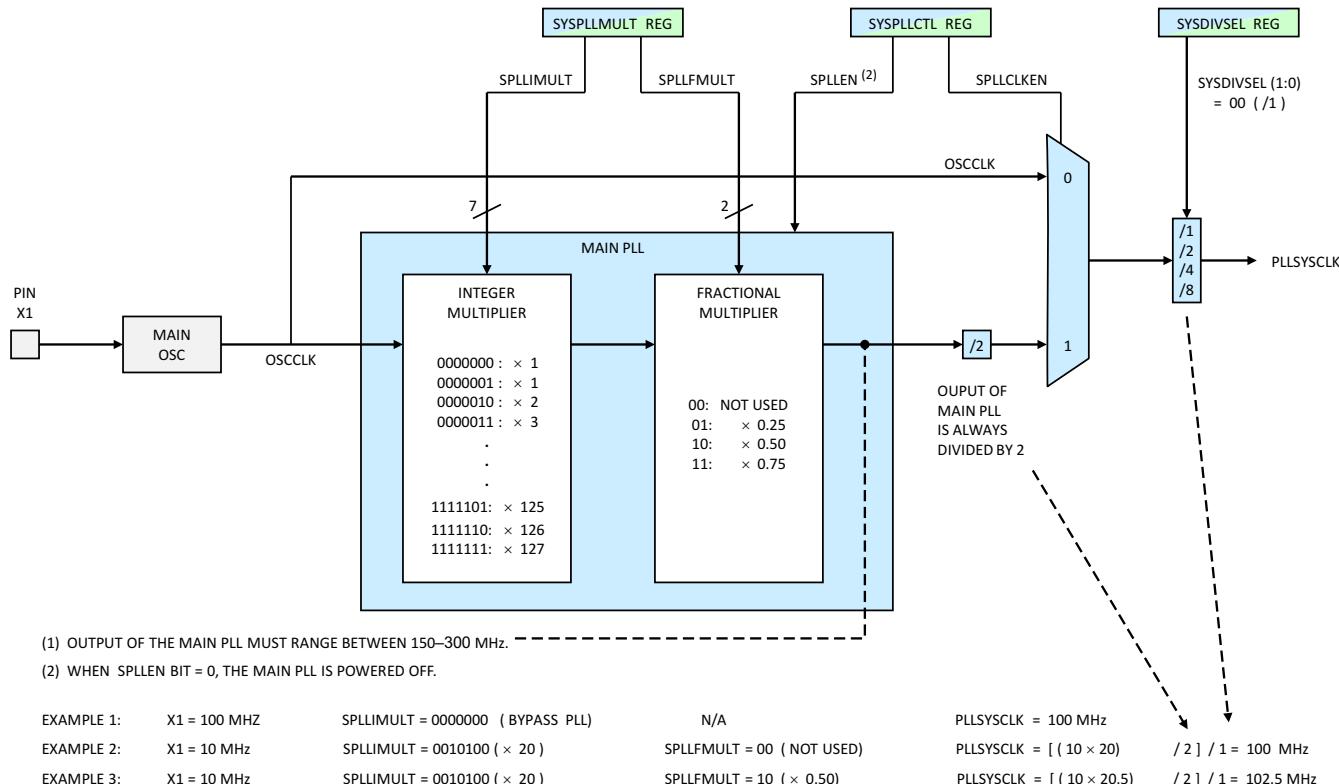

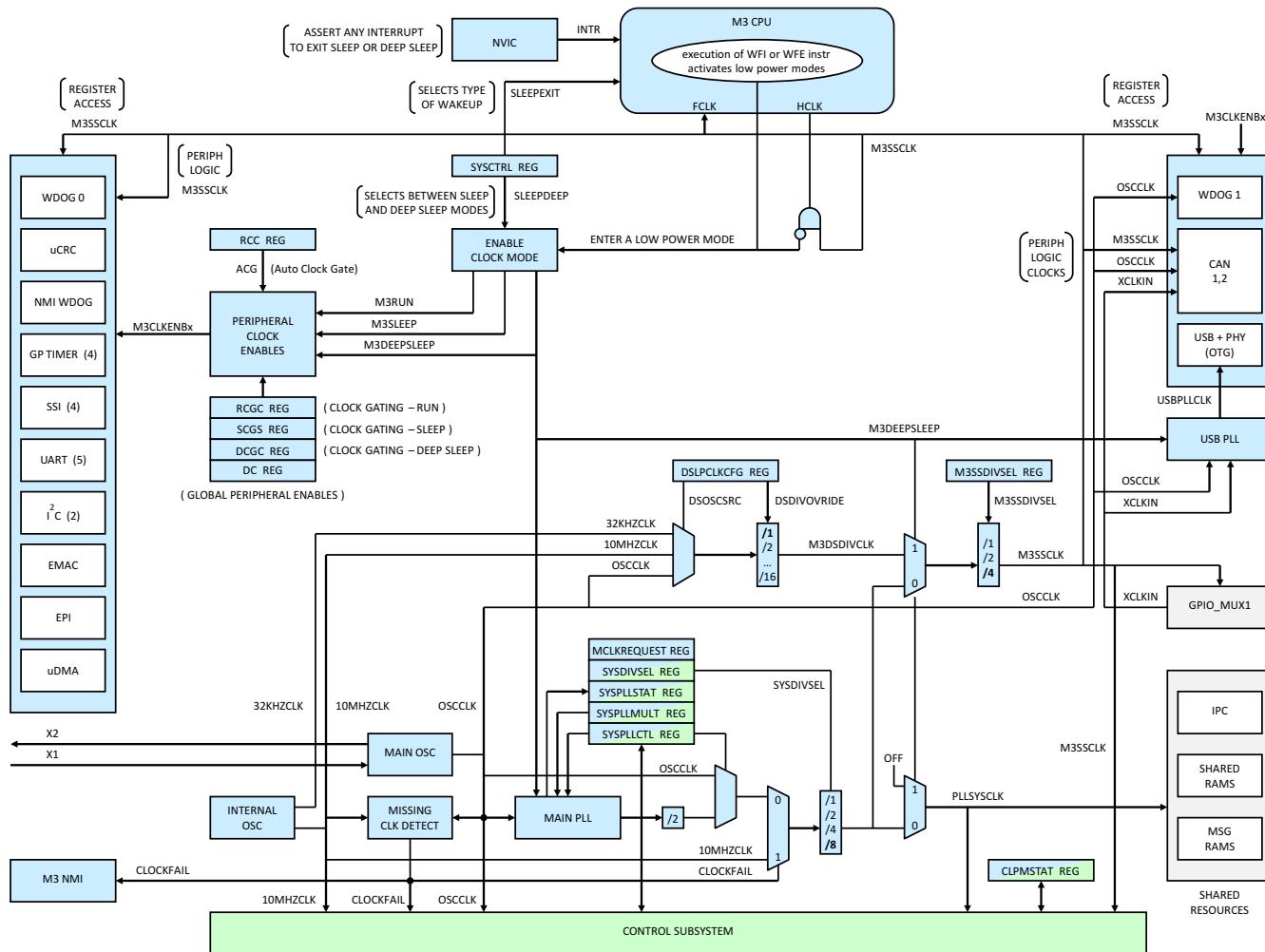

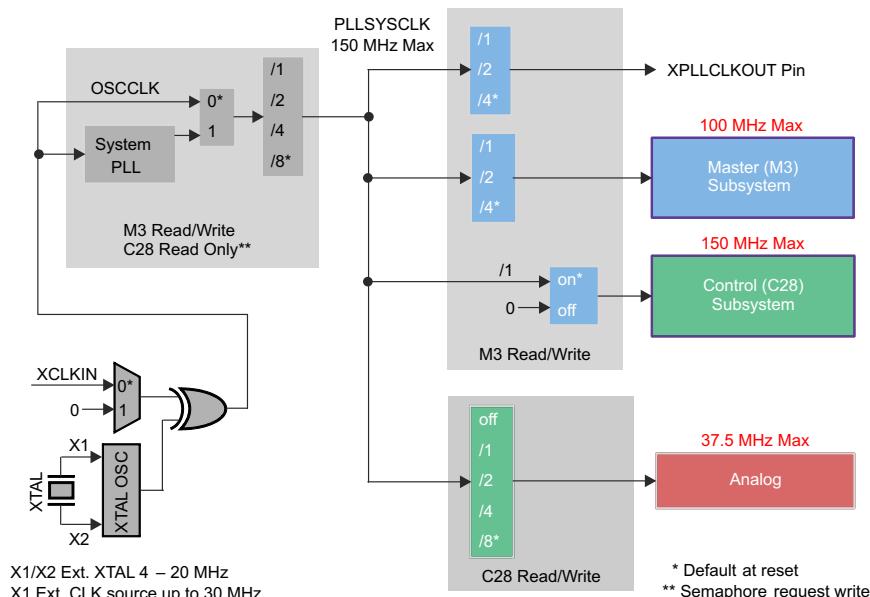

- Clocking

- On-chip crystal oscillator and external clock input

- Dynamic Phase-Locked Loop (PLL) ratio changes supported

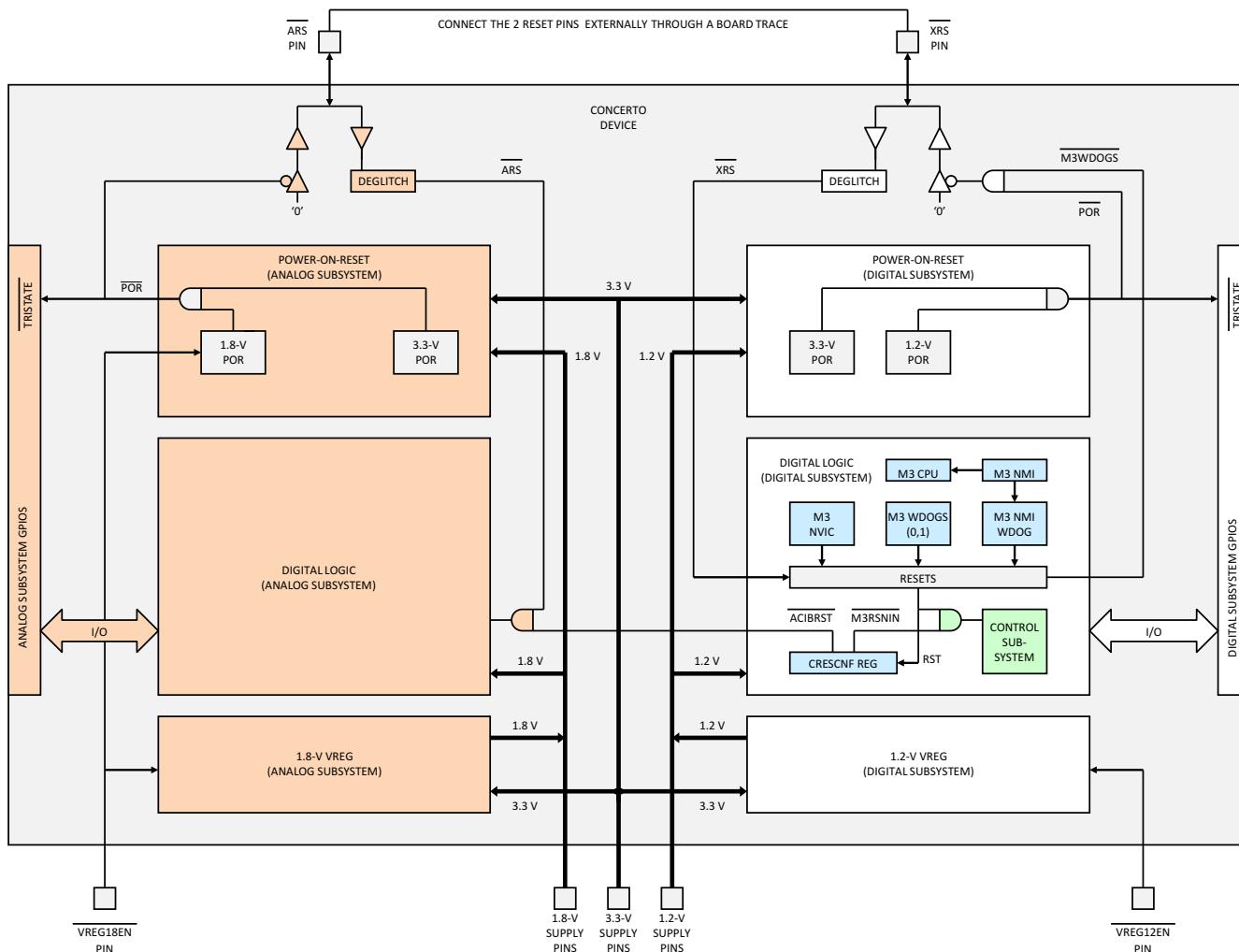

- 1.2-V digital, 1.8-V analog, 3.3-V I/O design

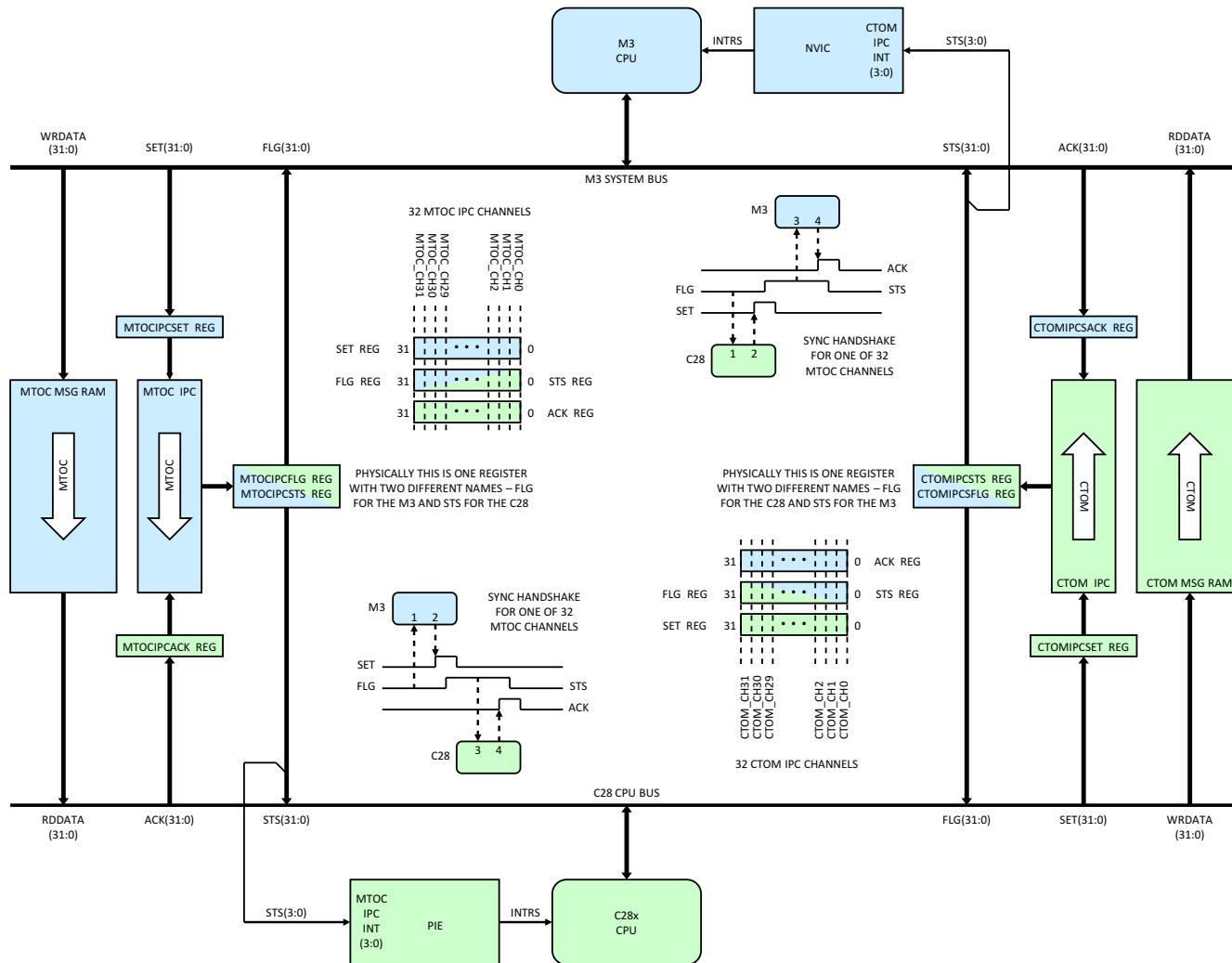

- Interprocessor Communications (IPC)

- 32 handshaking channels

- Four channels generate IPC interrupts

- Can be used to coordinate transfer of data through IPC Message RAMs

- Up to 74 individually programmable, multiplexed General-Purpose Input/Output (GPIO) pins

- Glitch-free I/Os

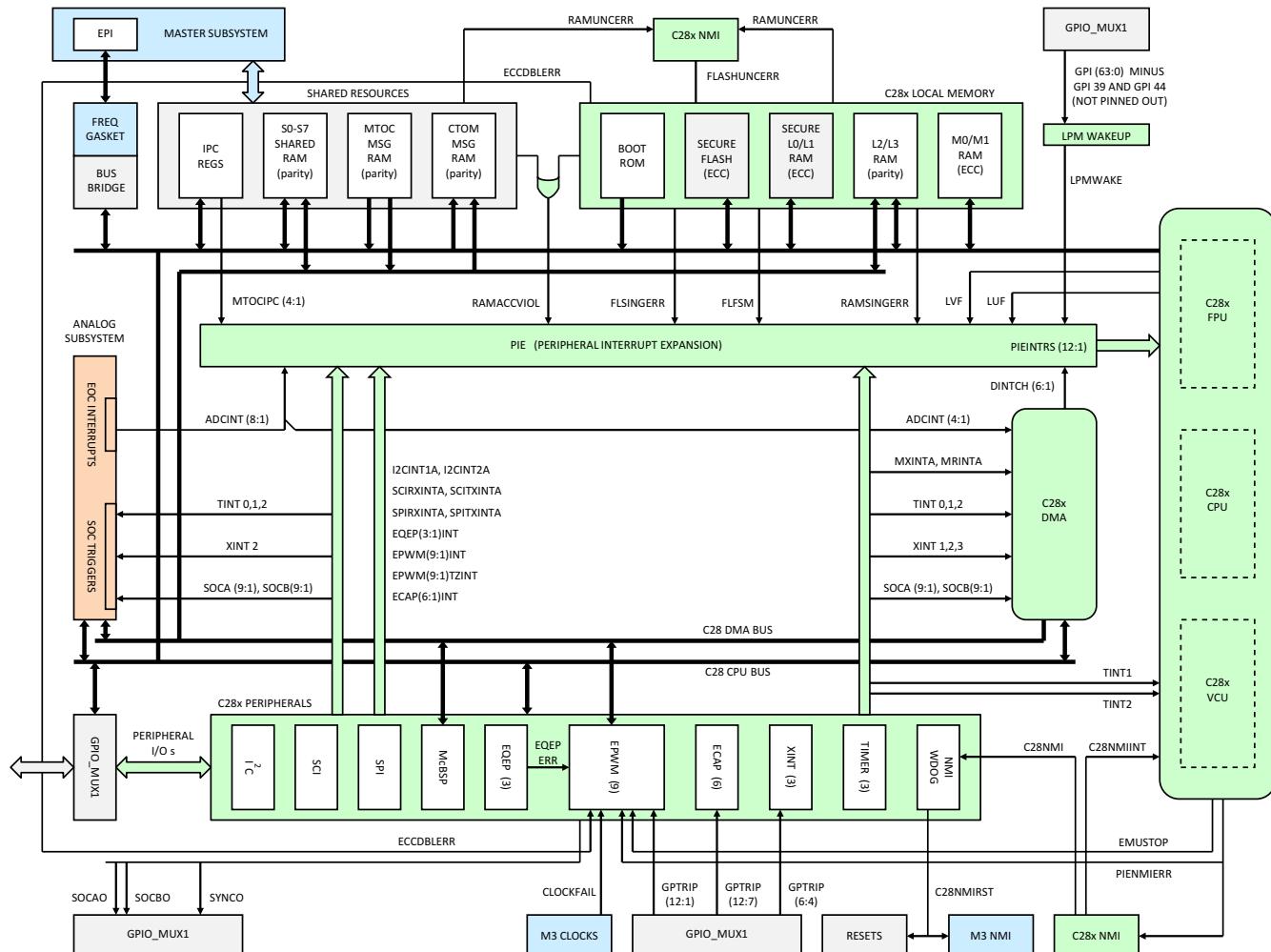

- Control Subsystem — TMS320C28x 32-bit CPU

- Up to 150 MHz

- C28x core hardware built-in self-test

- Embedded memory

- Up to 512KB of flash (ECC)

- Up to 36KB of RAM (ECC or parity)

- Up to 64KB of shared RAM

- 2KB of IPC Message RAM

- IEEE-754 single-precision Floating-Point Unit (FPU)

- Viterbi, Complex Math, CRC Unit (VCU)

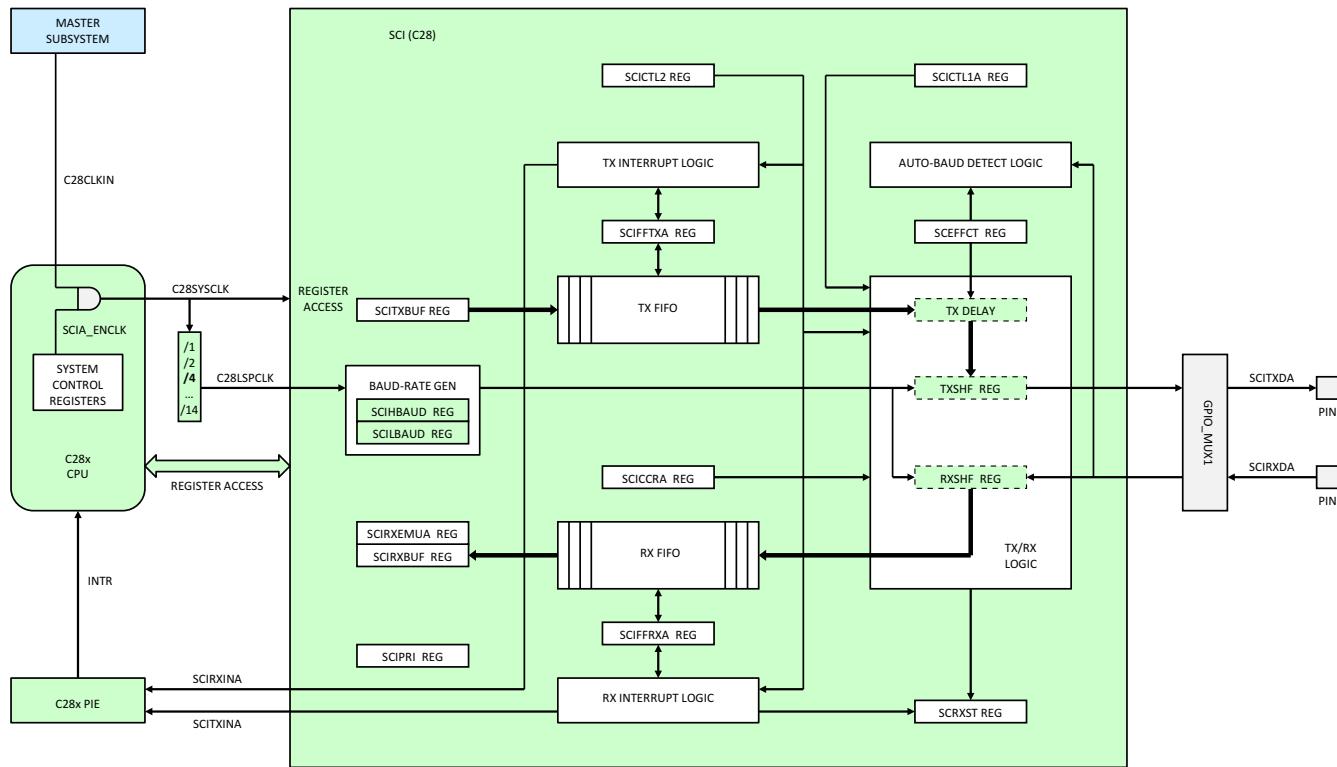

- Serial Communications Interface (SCI)

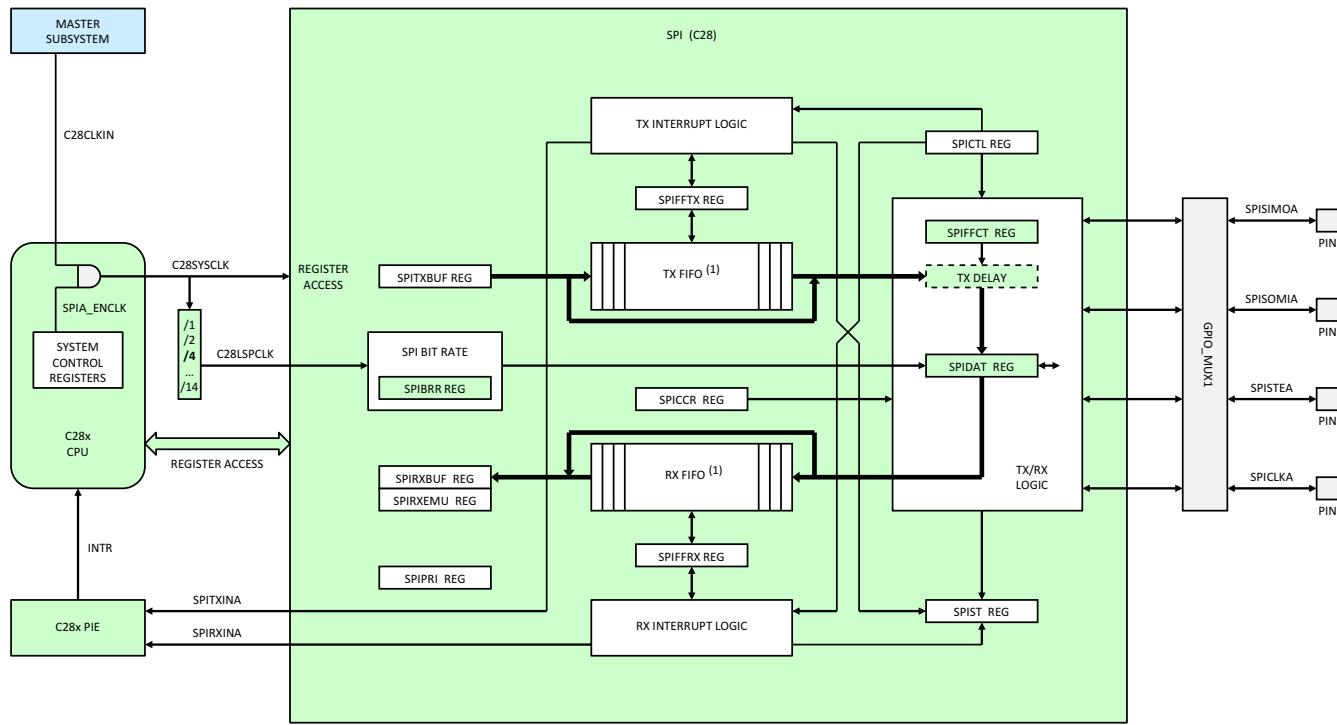

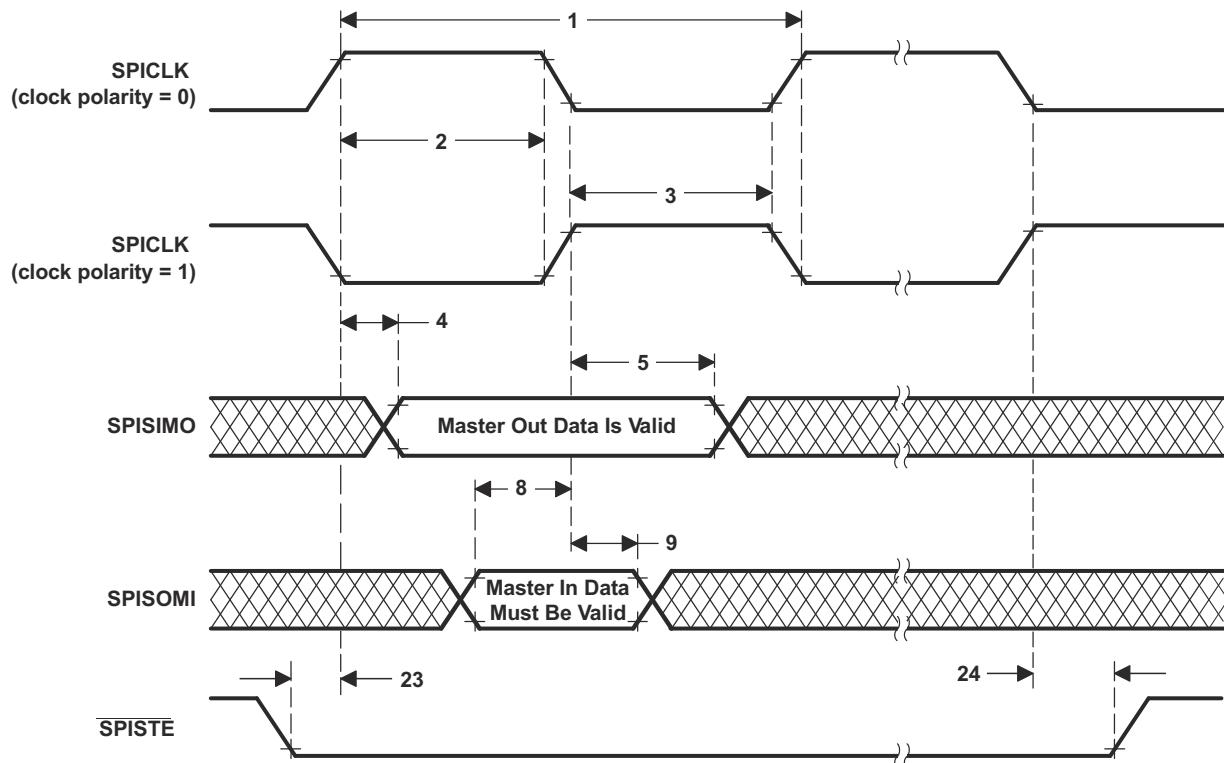

- SPI

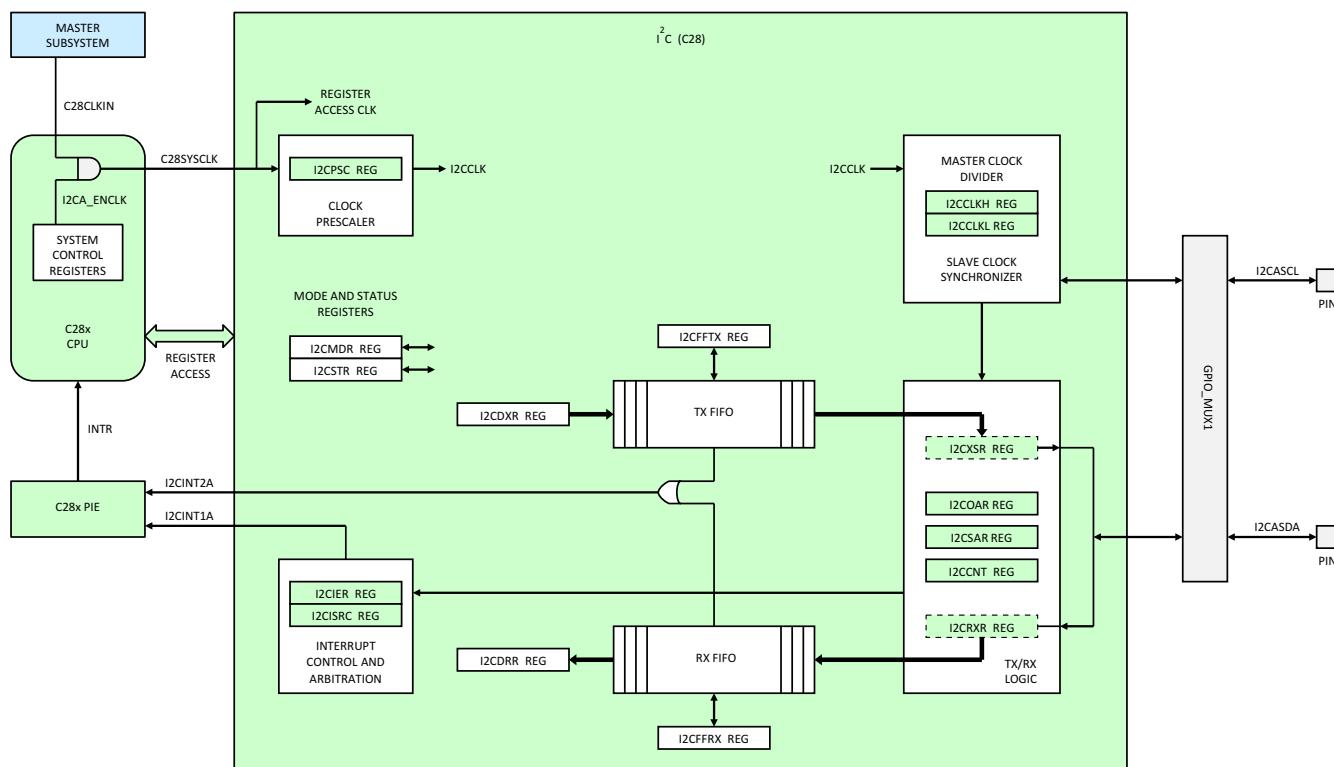

- I2C

- 6-channel Direct Memory Access (DMA)

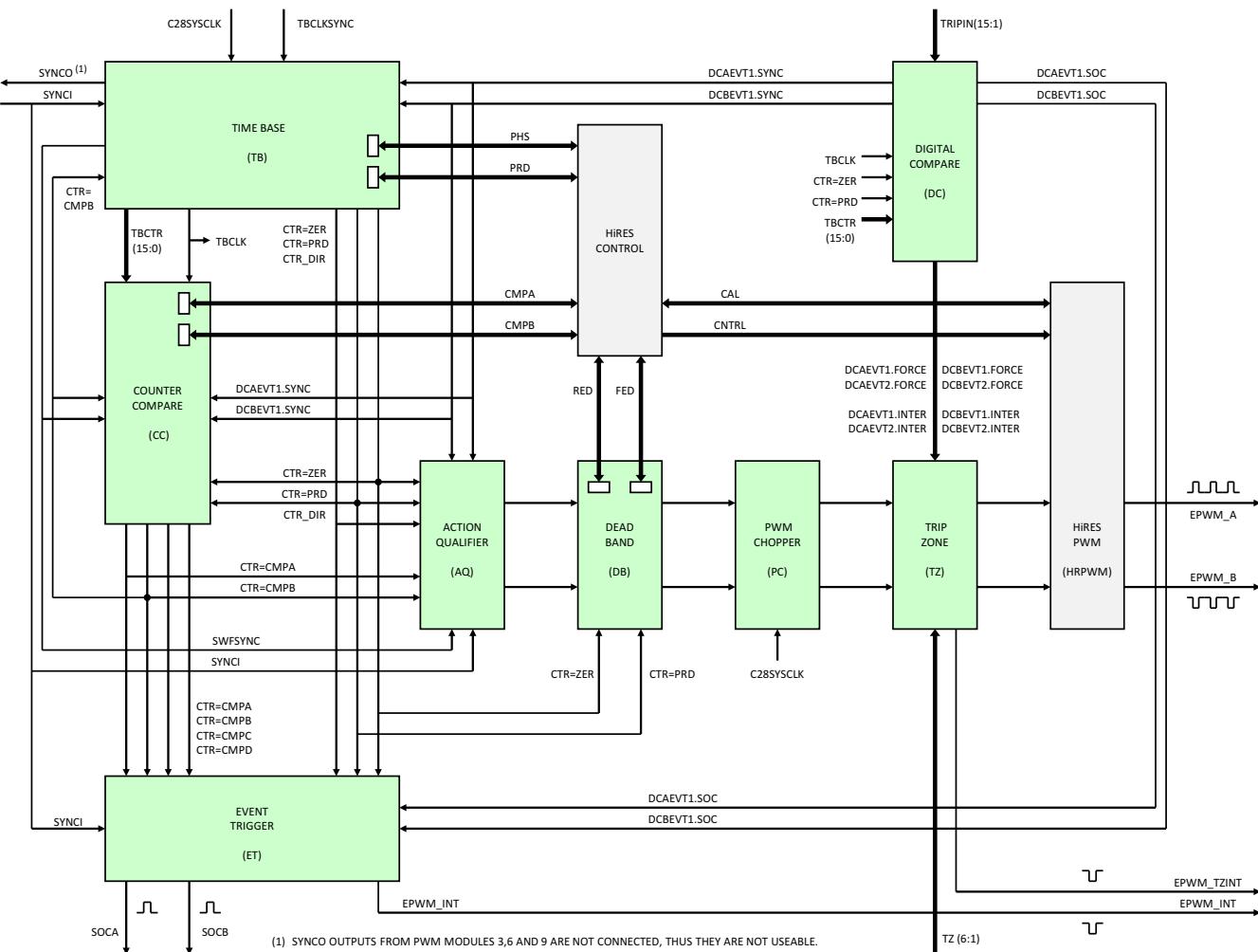

- Nine Enhanced Pulse Width Modulator (ePWM) modules

- 18 outputs (16 high-resolution)

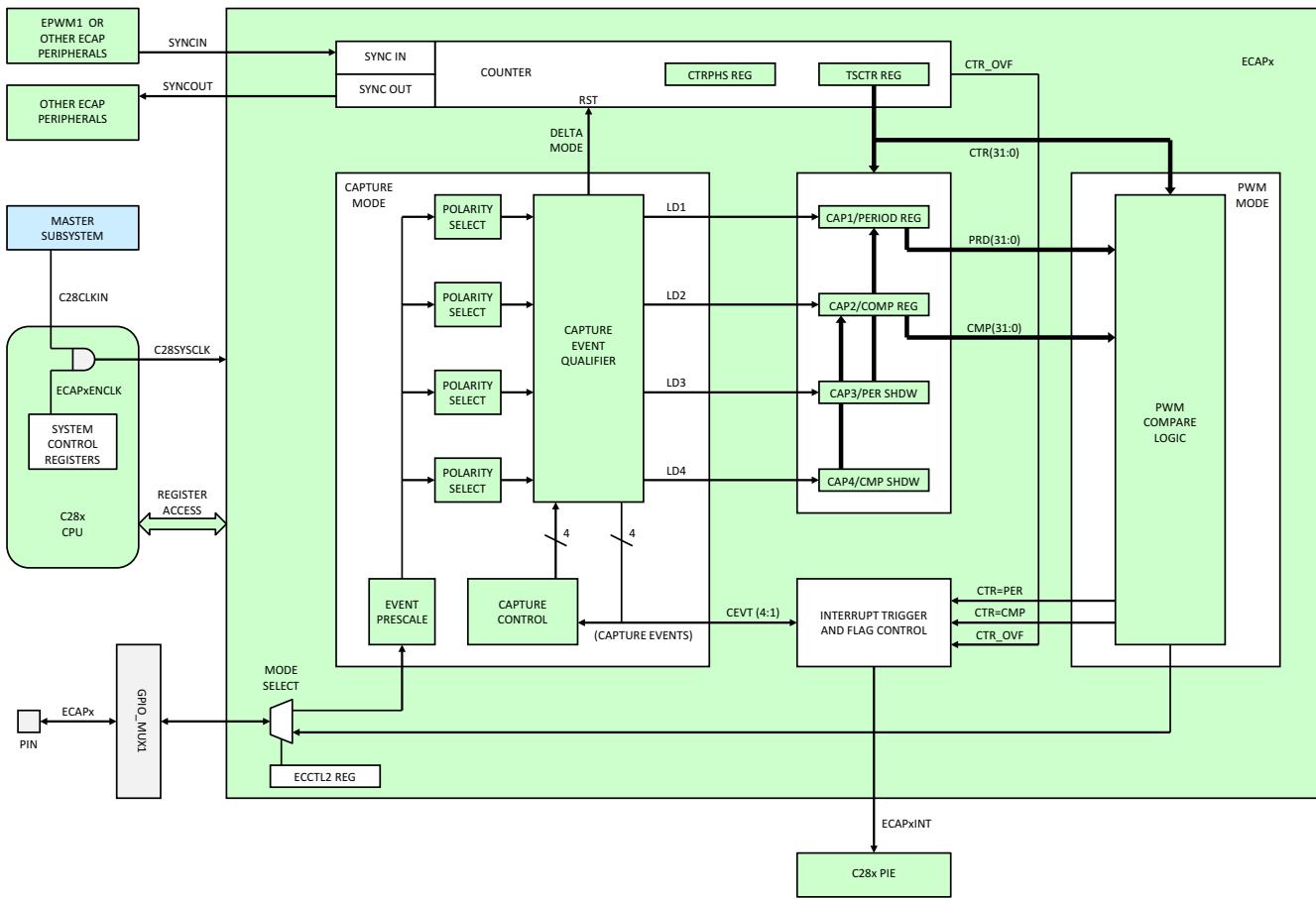

- Six 32-bit Enhanced Capture (eCAP) modules

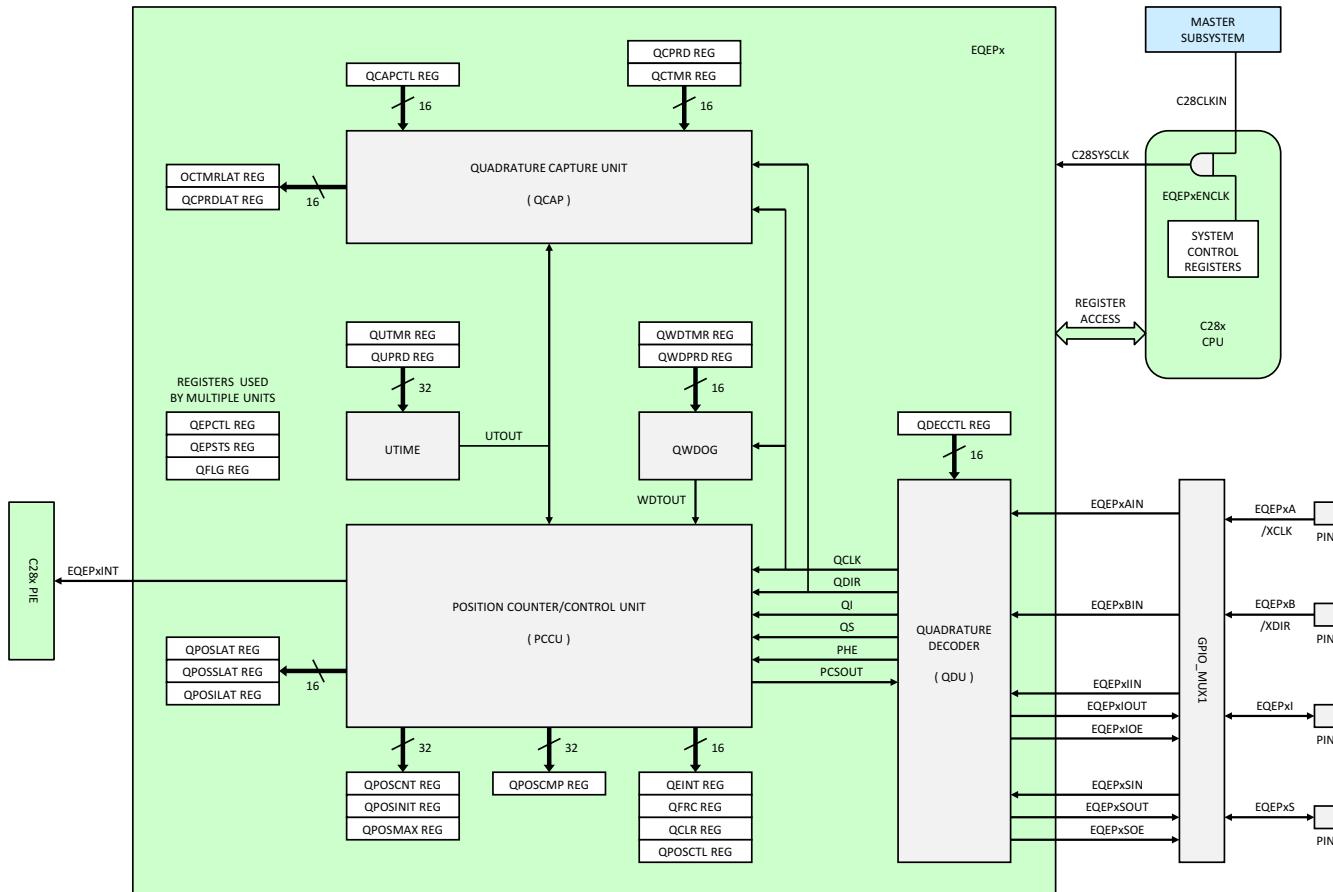

- Three 32-bit Enhanced Quadrature Encoder Pulse (eQEP) modules

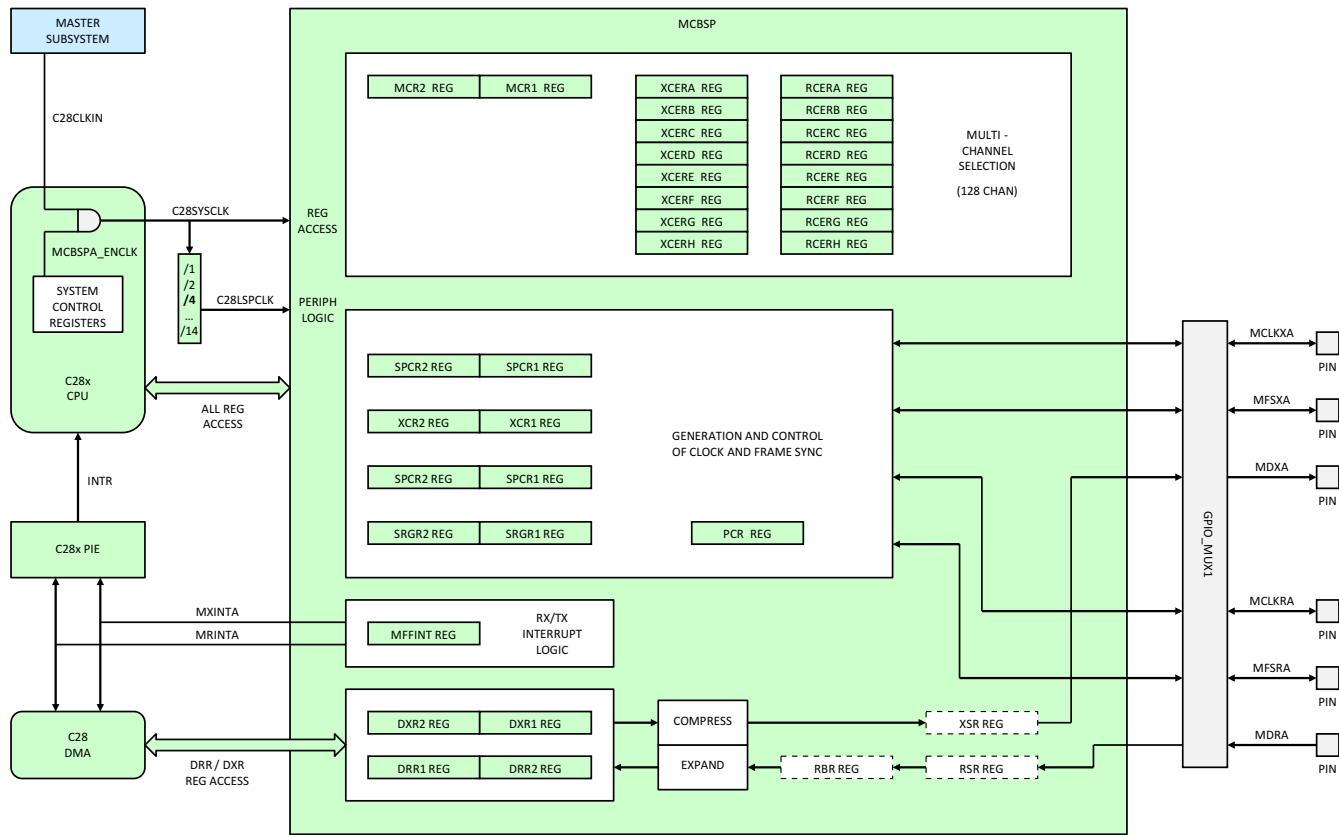

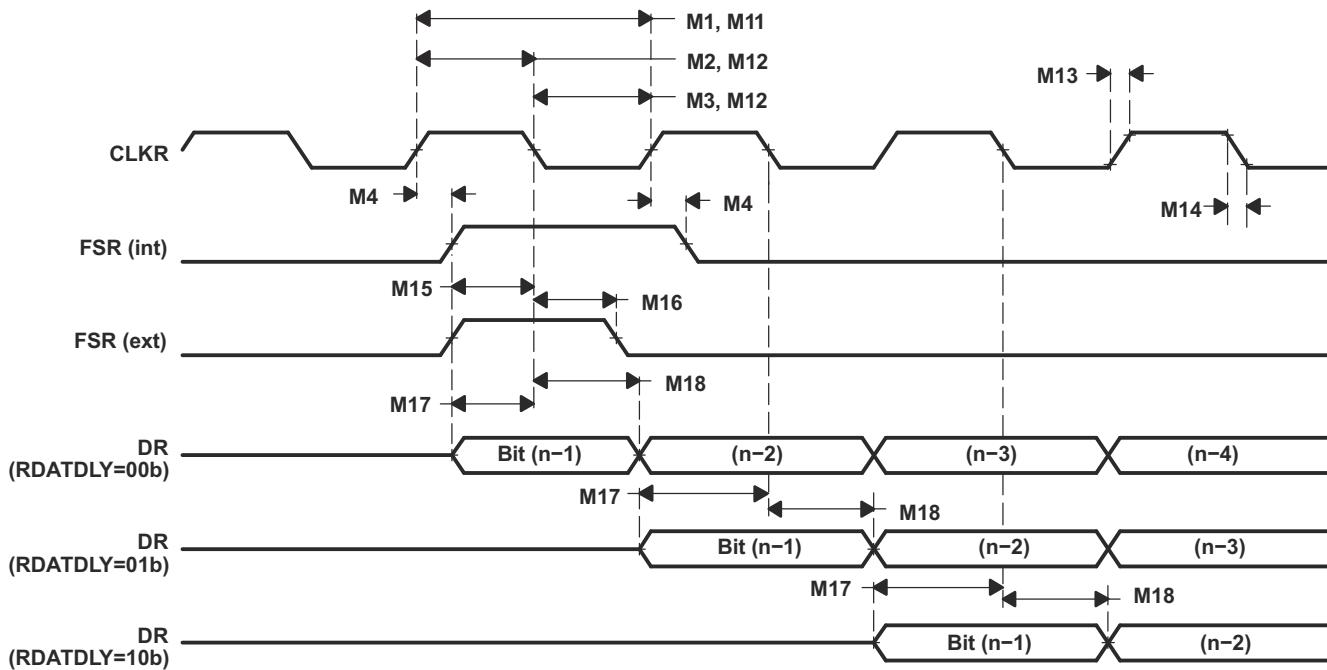

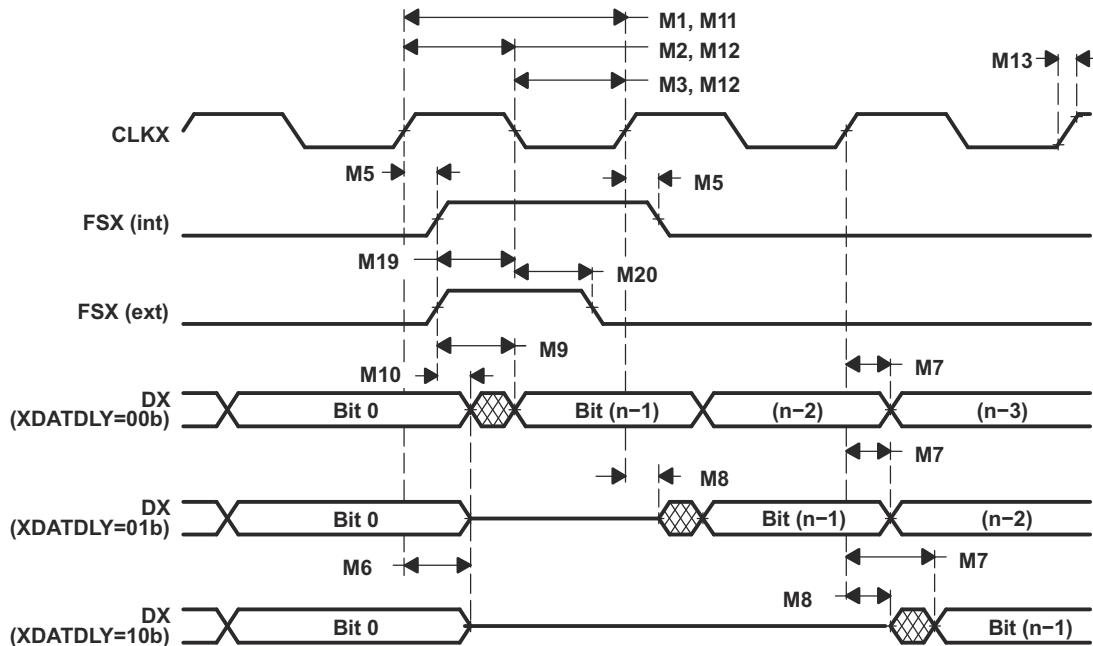

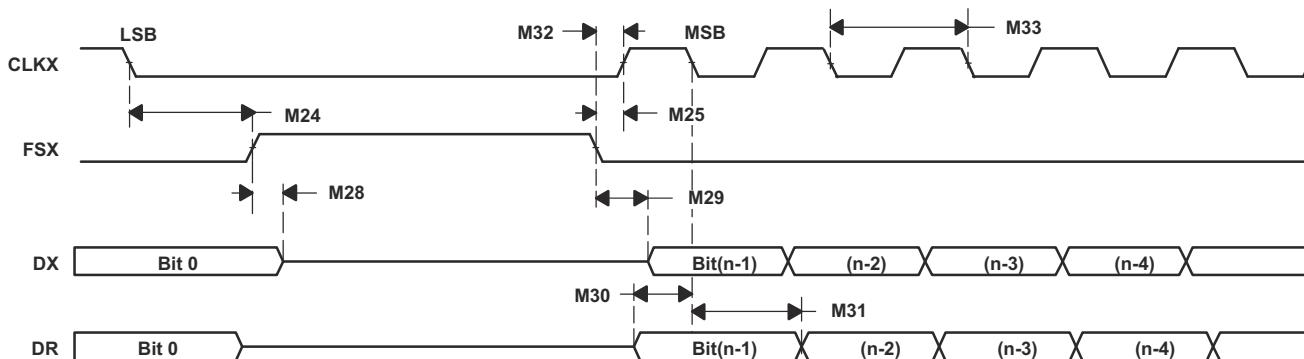

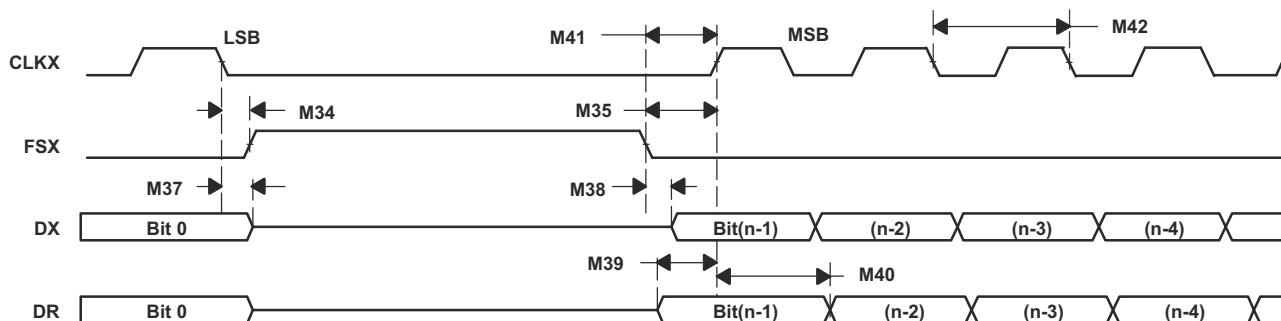

- Multichannel Buffered Serial Port ( McBSP)

- EPI

- One security zone (128-bit password)

- Three 32-bit timers

- Endianness: little endian

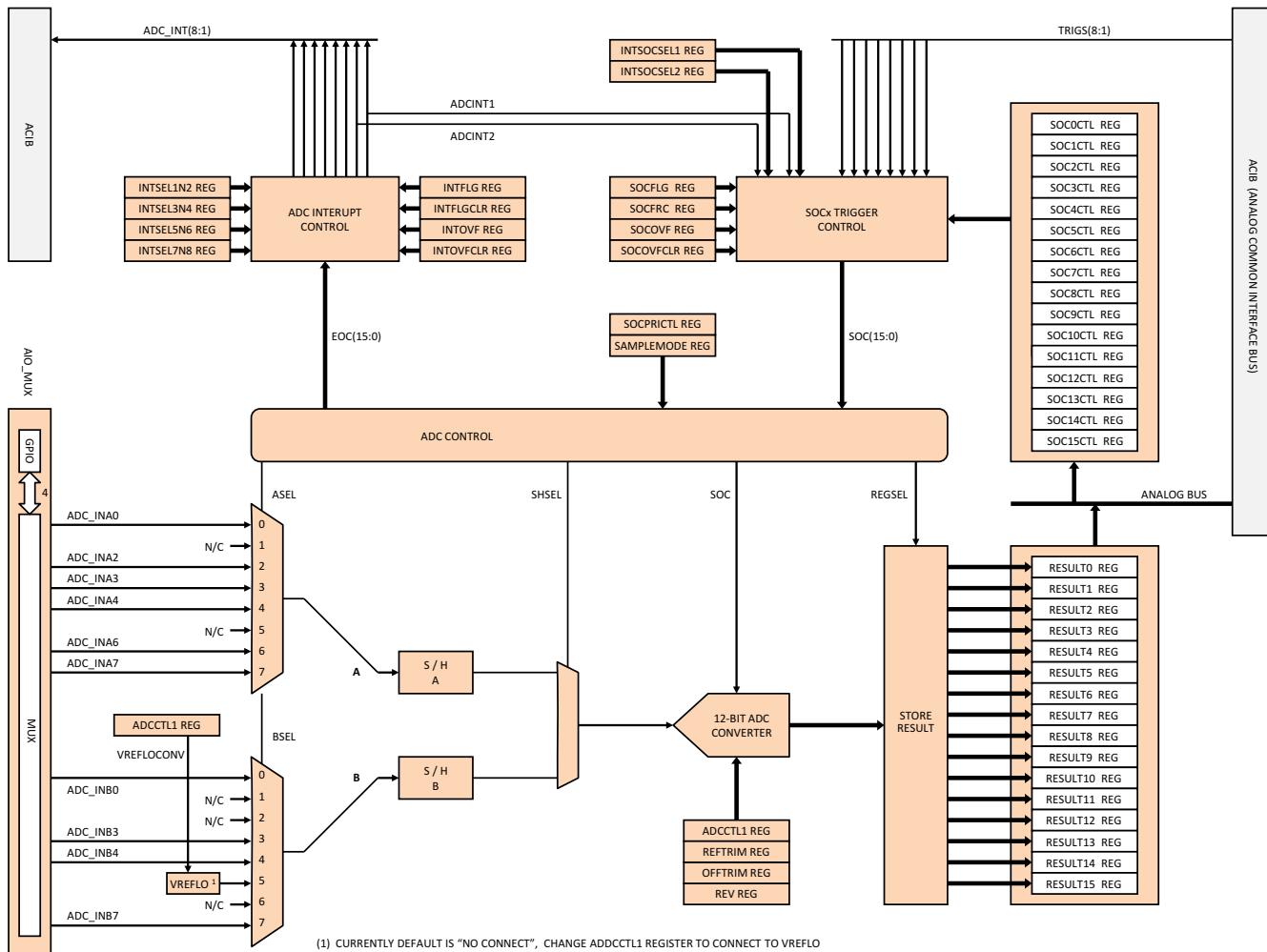

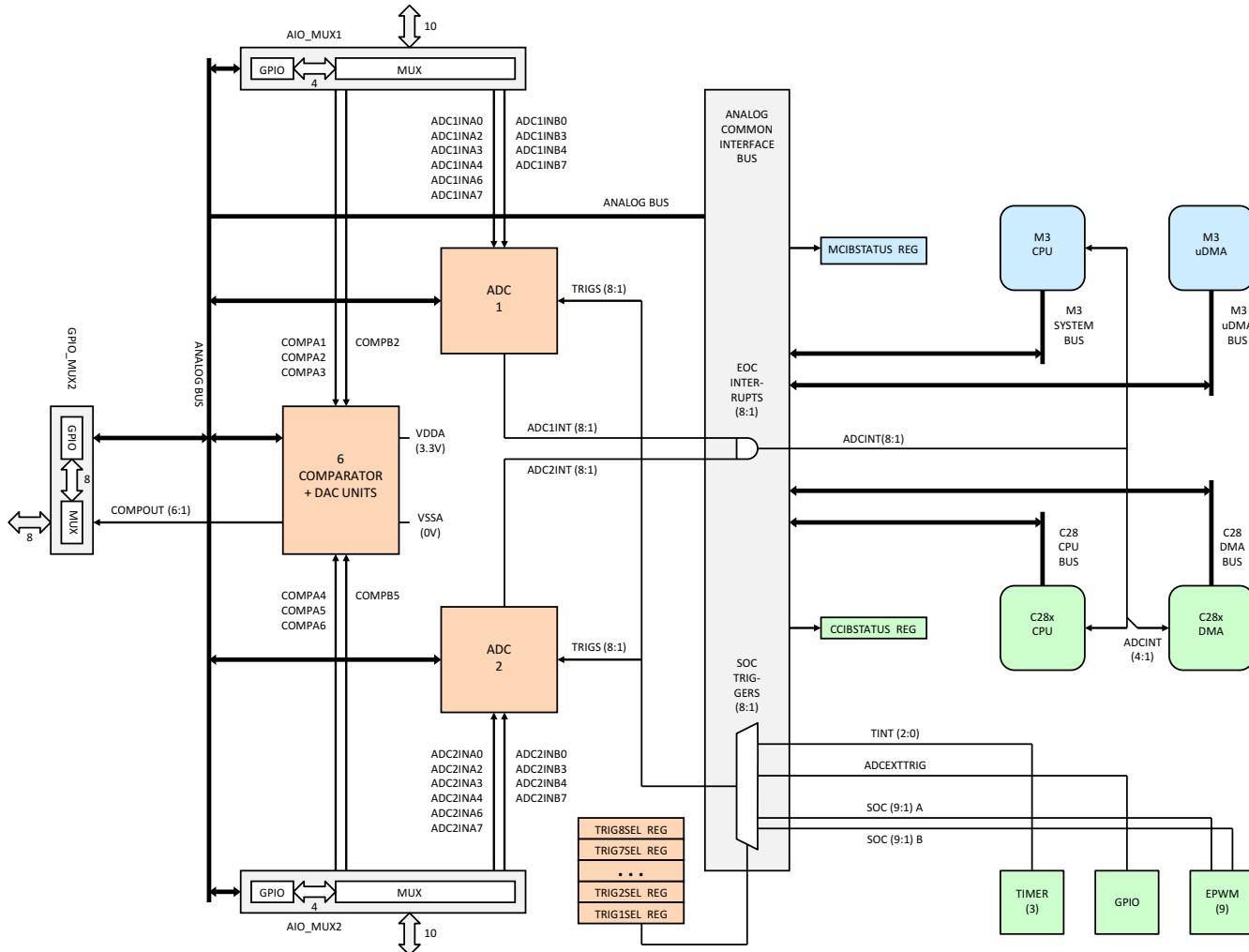

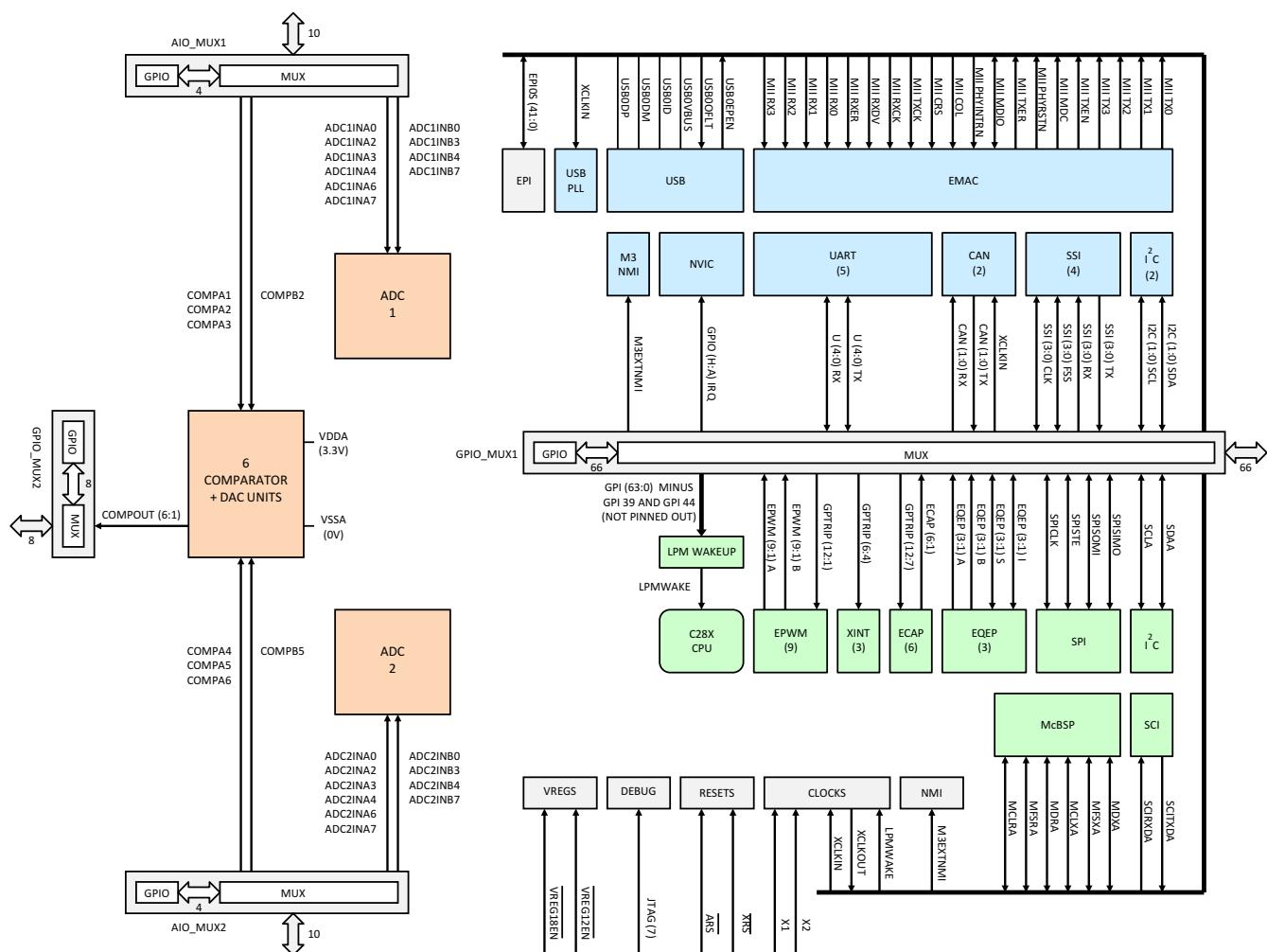

- Analog Subsystem

- Dual 12-bit Analog-to-Digital Converters (ADCs)

- Up to 2.88 MSPS

- Up to 20 channels

- Four Sample-and-Hold (S/H) circuits

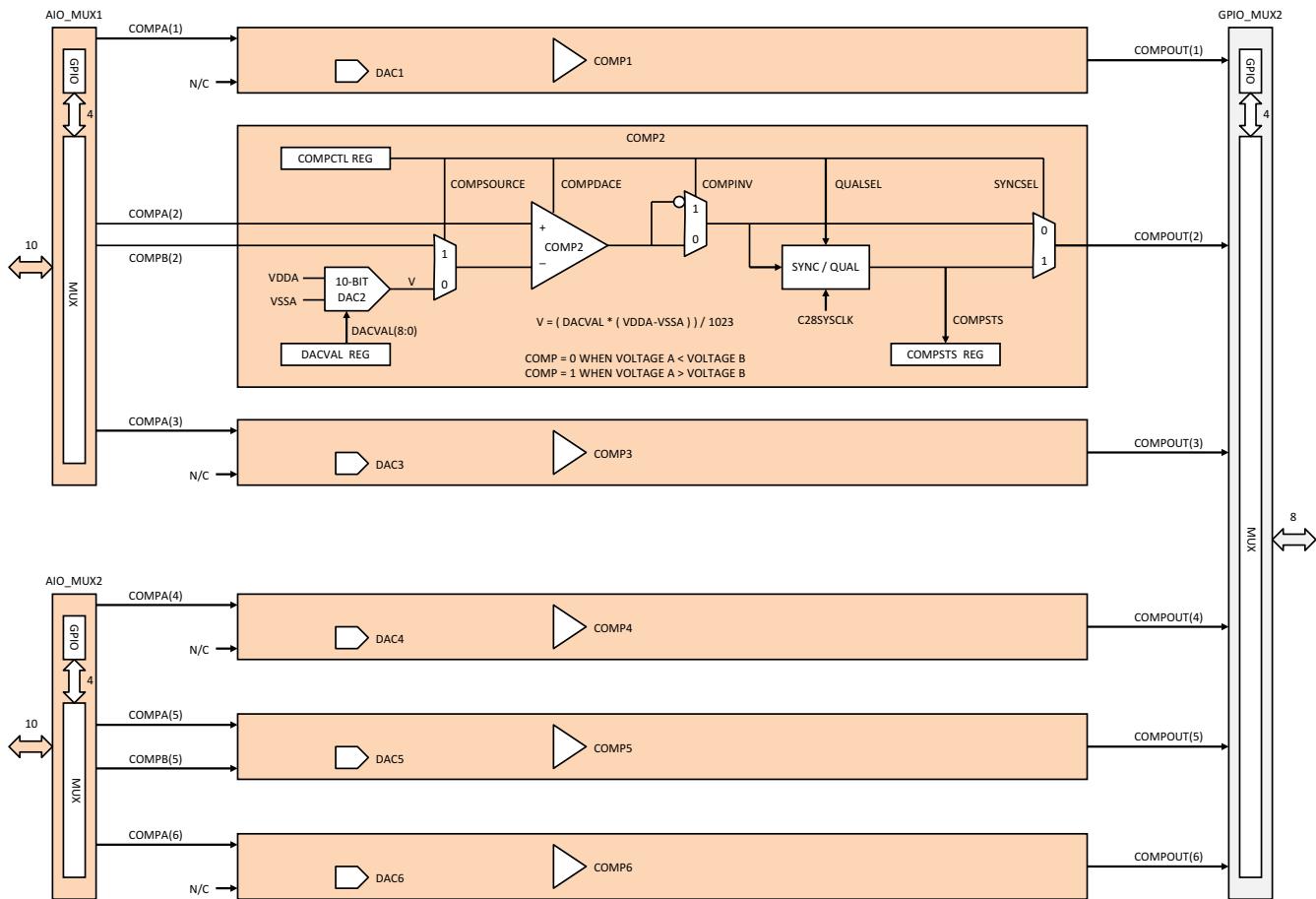

- Up to six comparators with 10-bit Digital-to-Analog Converter (DAC)

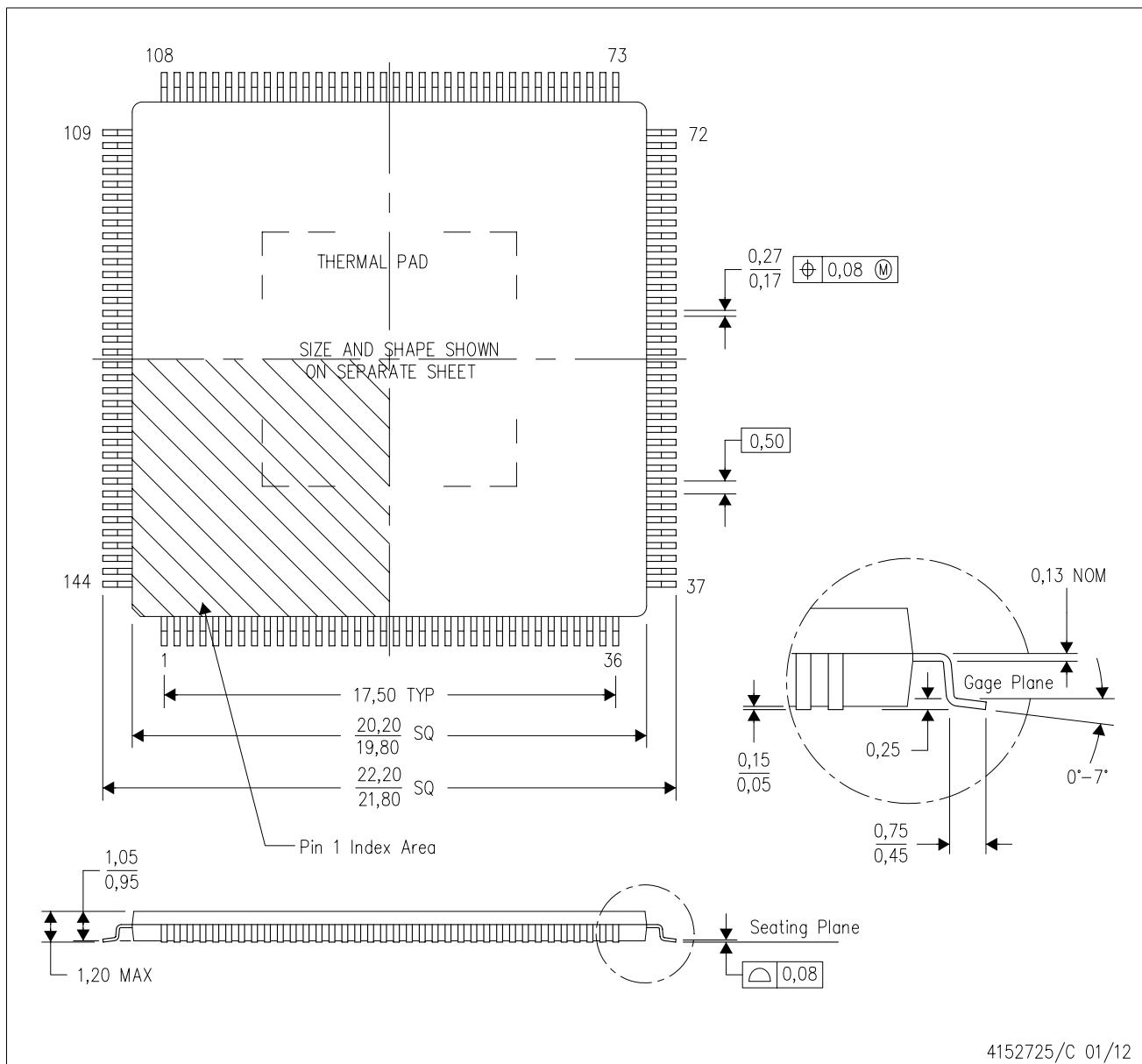

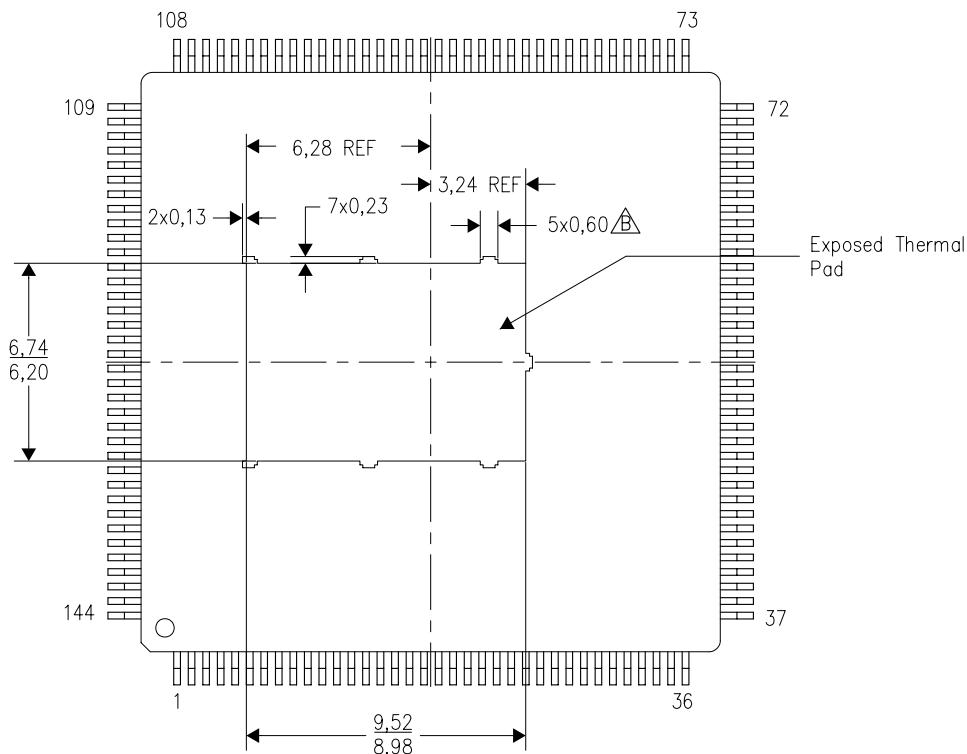

- Package

- 144-Pin RFP PowerPAD™ Thermally Enhanced Thin Quad Flatpack (HTQFP)

- Temperature options:

- T: -40°C to 105°C Junction

- S: -40°C to 125°C Junction

- Q: -40°C to 125°C Free-Air (AEC Q100 qualification for automotive applications)

### 2 Applications

- [Automated sorting equipment](#)

- [CNC control](#)

- [Central inverter](#)

- [String inverter](#)

- [AC drive control module](#)

- [Servo drive control module](#)

- [AC-input BLDC motor drive](#)

- [DC-input BLDC motor drive](#)

- [Industrial AC-DC](#)

- [Three phase UPS](#)

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

### 3 Description

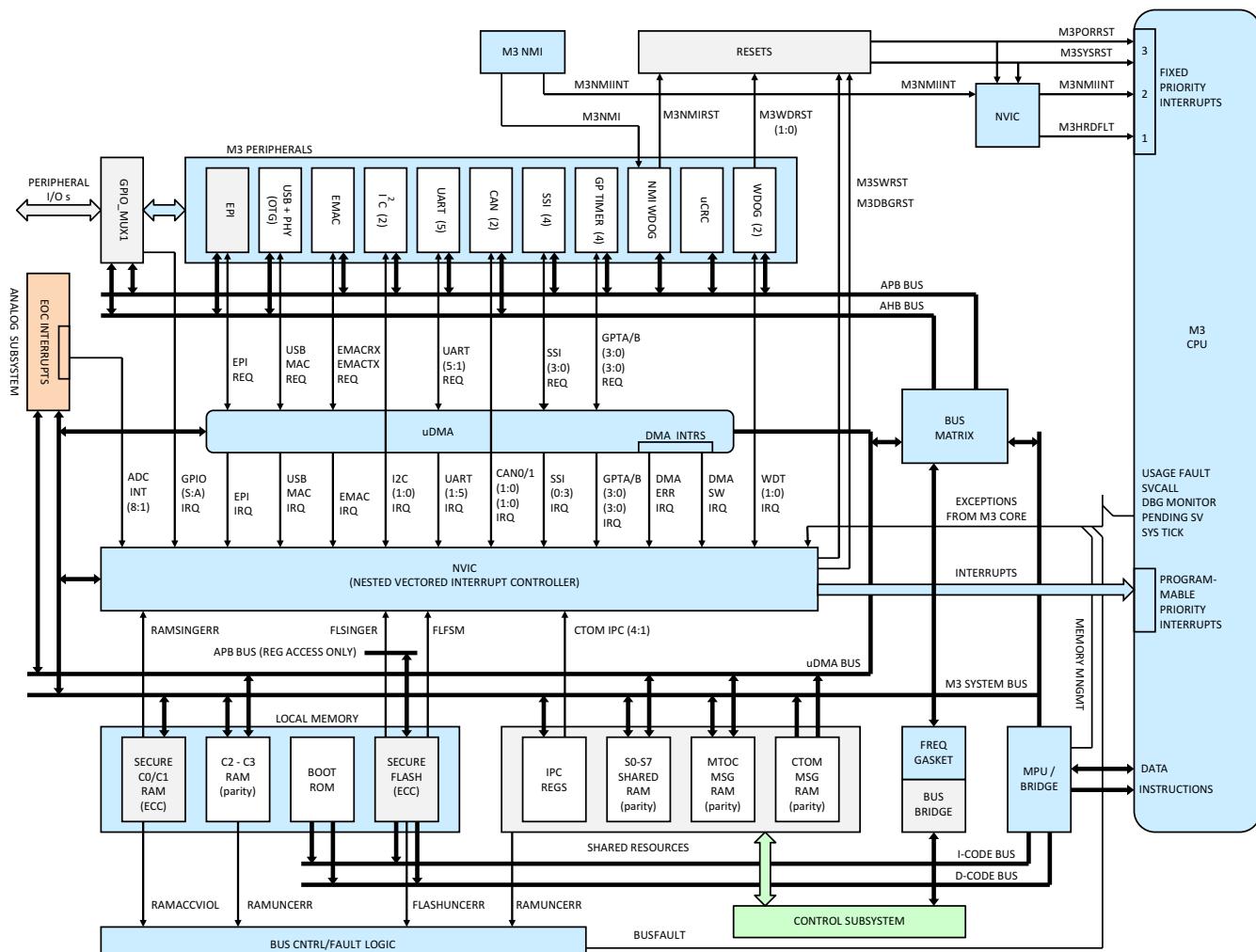

The Concerto family is a multicore system-on-chip microcontroller unit (MCU) with independent communication and real-time control subsystems. The F28M35x family of devices is the first series in the Concerto family.

The communications subsystem is based on the industry-standard 32-bit Arm Cortex-M3 CPU and features a wide variety of communication peripherals, including Ethernet 1588, USB OTG with PHY, Controller Area Network (CAN), UART, SSI, I2C, and an external interface.

The real-time control subsystem is based on TI's industry-leading proprietary 32-bit C28x floating-point CPU and features the most flexible and high-precision control peripherals, including ePWMs with fault protection, and encoders and captures—all as implemented by TI's TMS320C2000™ [Entry performance MCUs](#) and [Premium performance MCUs](#). In addition, the C28-CPU has been enhanced with the addition of the VCU instruction accelerator that implements efficient Viterbi, Complex Arithmetic, 16-bit FFTs, and CRC algorithms.

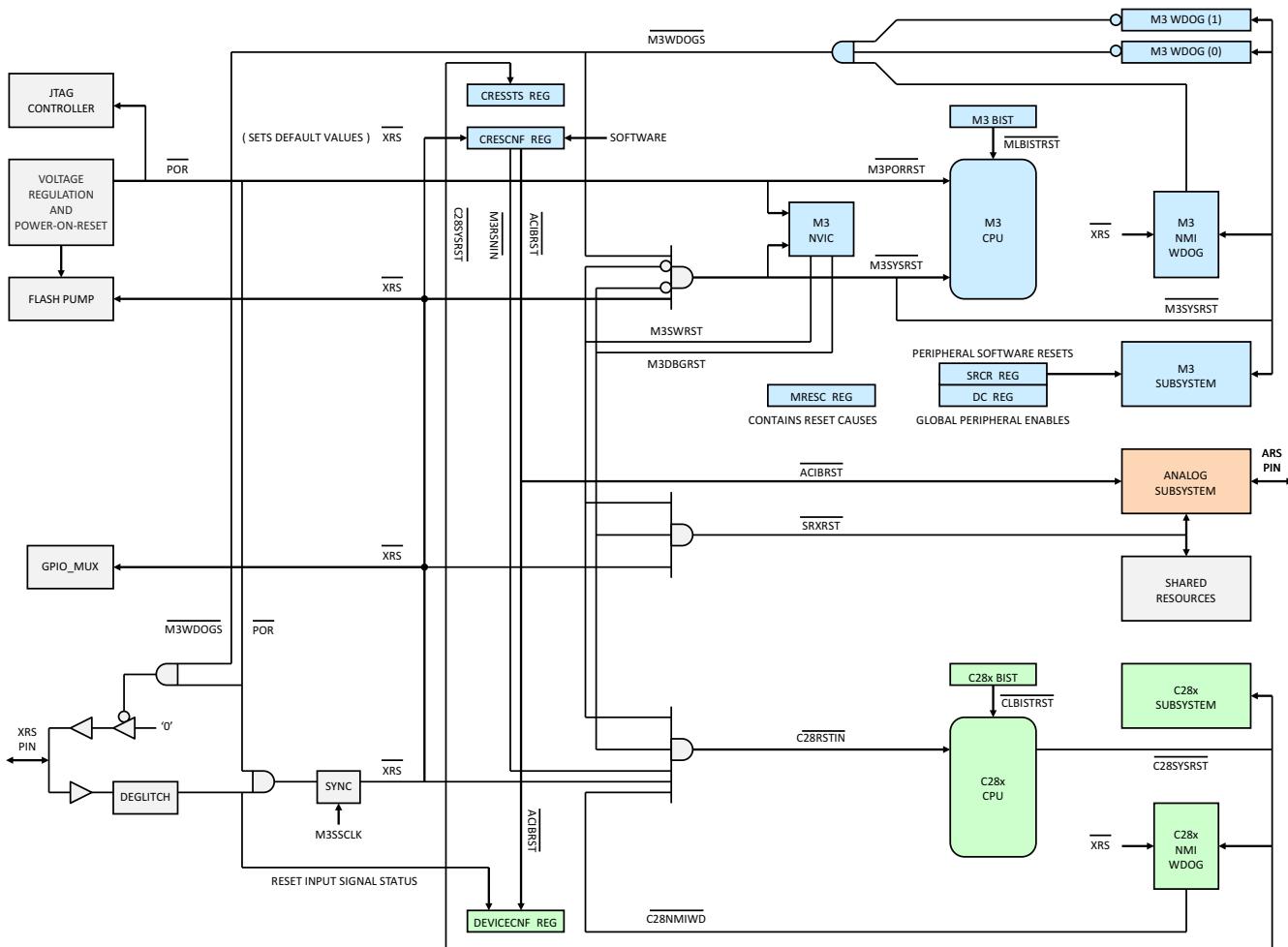

A high-speed analog subsystem and supplementary RAM memory is shared, along with on-chip voltage regulation and redundant clocking circuitry. Safety considerations also include Error Correction Code (ECC), parity, and code secure memory, as well as documentation to assist with system-level industrial safety certification.

#### Device Information

| PART NUMBER <sup>(1)</sup> | PACKAGE     | BODY SIZE         |

|----------------------------|-------------|-------------------|

| F28M35H52CRFP              | HTQFP (144) | 20.0 mm × 20.0 mm |

| F28M35H22CRFP              | HTQFP (144) | 20.0 mm × 20.0 mm |

| F28M35M52CRFP              | HTQFP (144) | 20.0 mm × 20.0 mm |

| F28M35E20BRFP              | HTQFP (144) | 20.0 mm × 20.0 mm |

(1) For more information on these devices, see [Mechanical, Packaging, and Orderable Information](#).

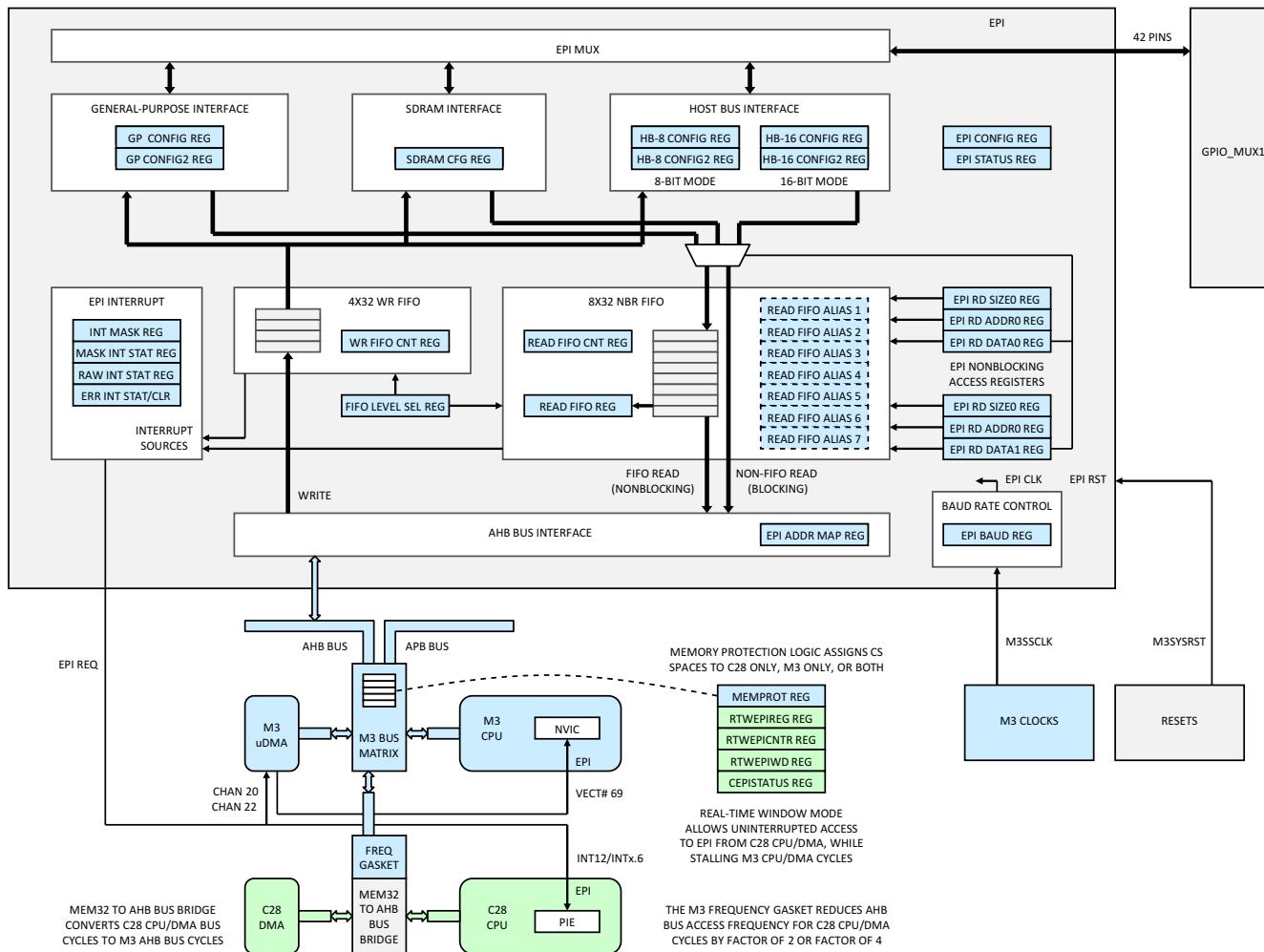

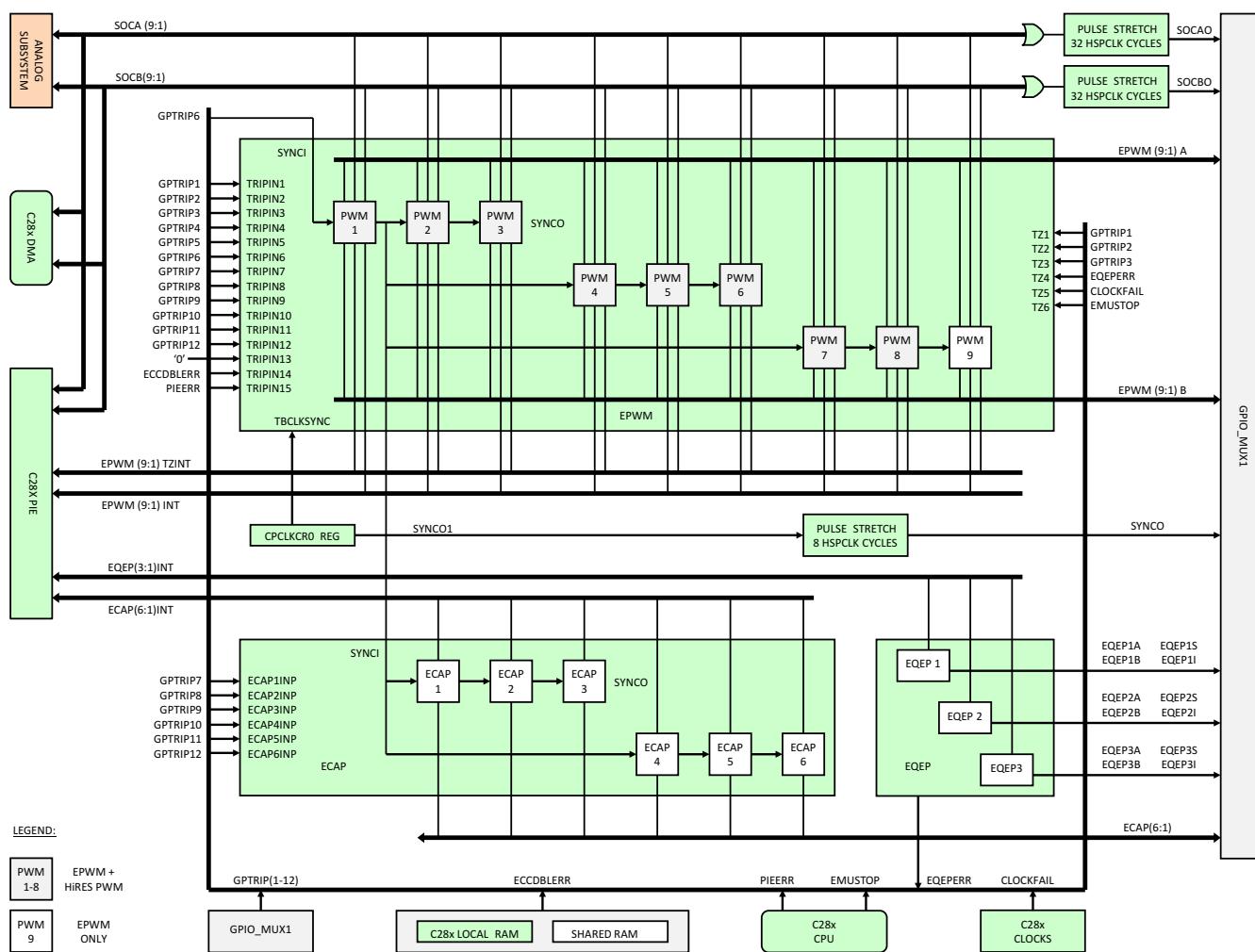

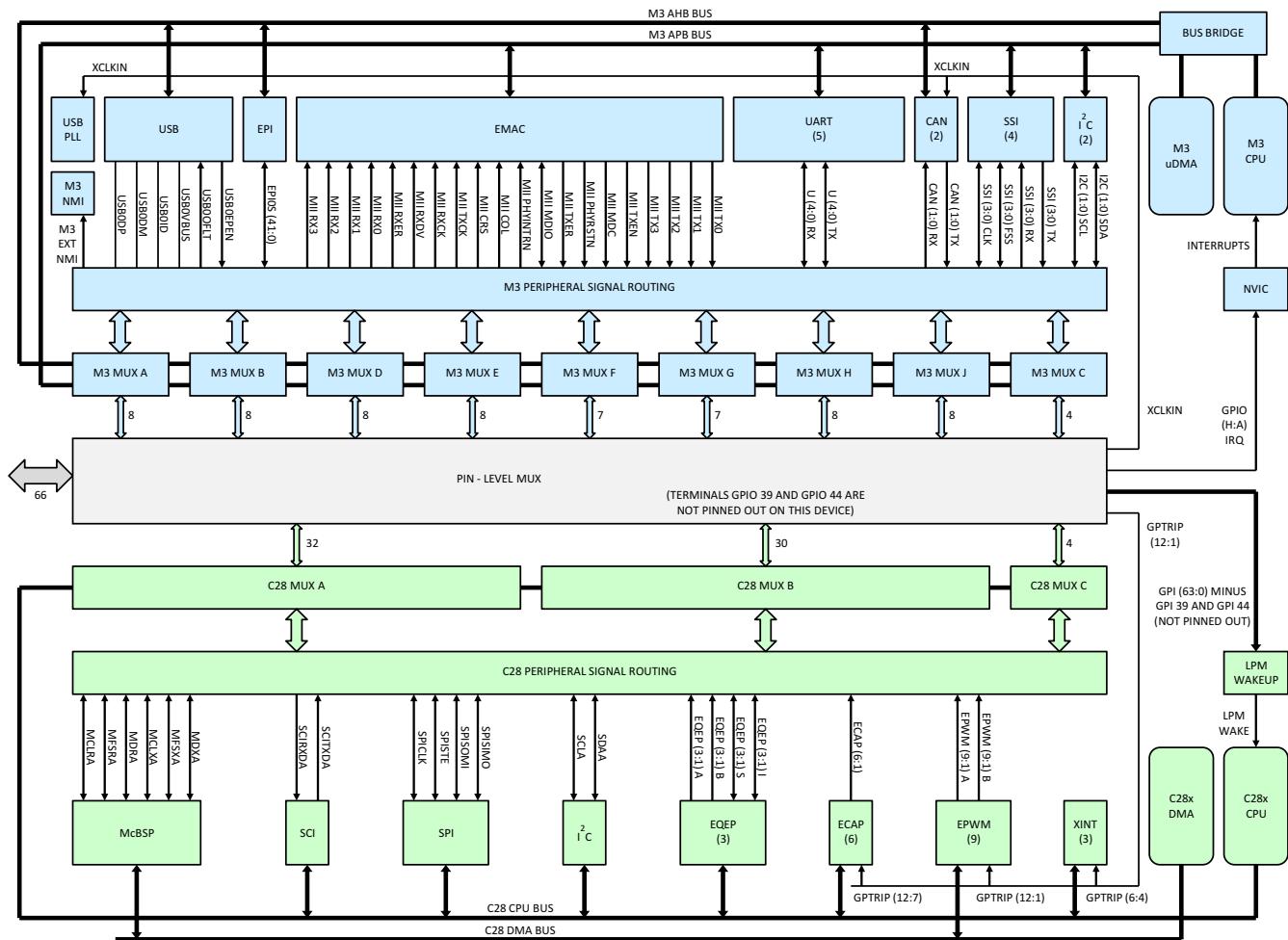

### 3.1 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

A. Some peripherals are not available on the F28M35Mx and F28M35Ex devices.

**Figure 3-1. Functional Block Diagram**

## Table of Contents

|                                                                      |            |                                                                       |            |

|----------------------------------------------------------------------|------------|-----------------------------------------------------------------------|------------|

| <b>1 Features</b> .....                                              | <b>1</b>   | 8.6 Master Subsystem NMIs.....                                        | <b>170</b> |

| <b>2 Applications</b> .....                                          | <b>1</b>   | 8.7 Control Subsystem NMIs.....                                       | <b>170</b> |

| <b>3 Description</b> .....                                           | <b>2</b>   | 8.8 Resets.....                                                       | <b>171</b> |

| 3.1 Functional Block Diagram.....                                    | 3          | 8.9 Internal Voltage Regulation and Power-On-Reset Functionality..... | <b>176</b> |

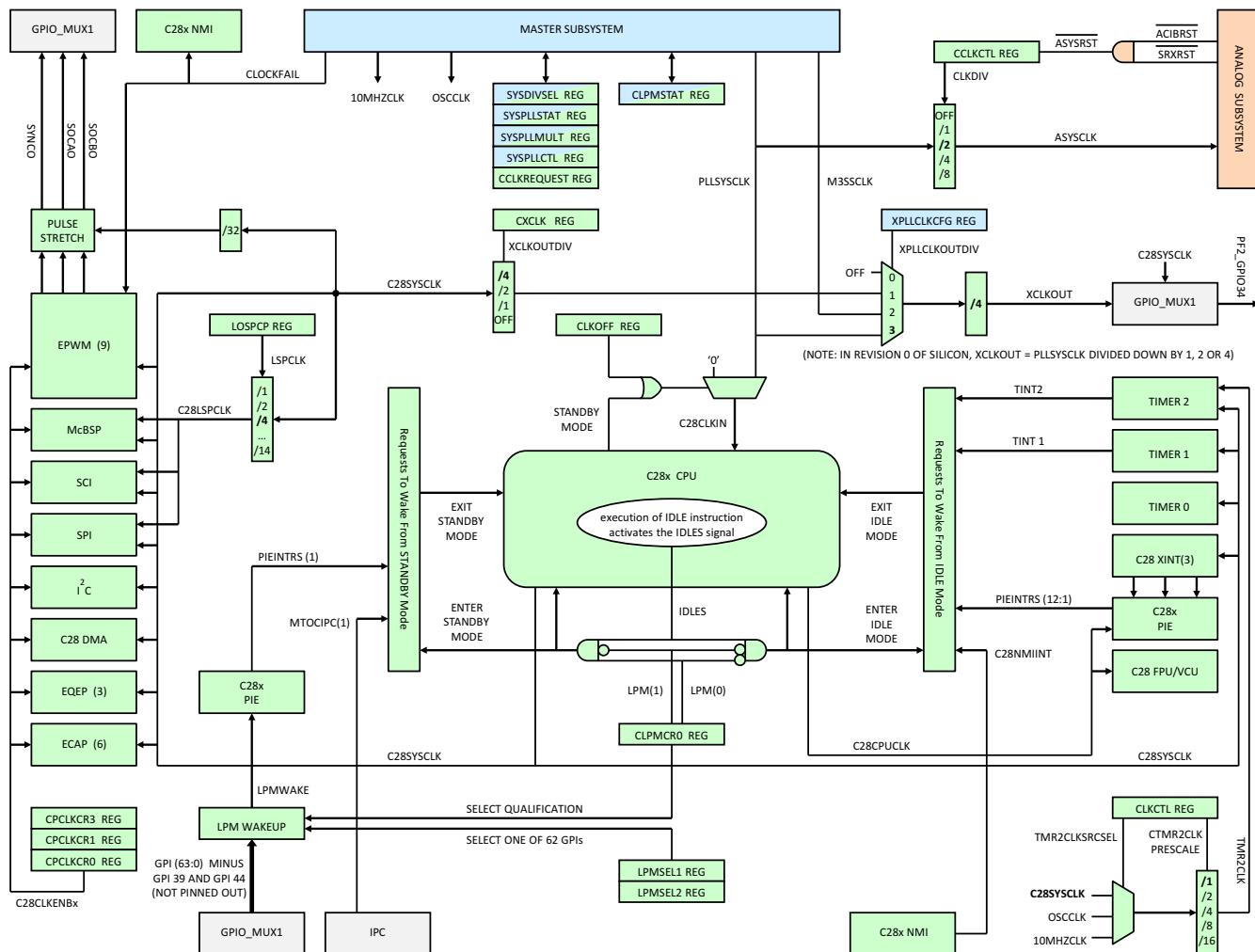

| <b>4 Revision History</b> .....                                      | <b>5</b>   | 8.10 Input Clocks and PLLs.....                                       | <b>179</b> |

| <b>5 Device Comparison</b> .....                                     | <b>6</b>   | 8.11 Master Subsystem Clocking.....                                   | <b>189</b> |

| 5.1 Related Products.....                                            | 8          | 8.12 Control Subsystem Clocking.....                                  | <b>193</b> |

| <b>6 Terminal Configuration and Functions</b> .....                  | <b>9</b>   | 8.13 Analog Subsystem Clocking.....                                   | <b>195</b> |

| 6.1 Pin Diagram.....                                                 | 9          | 8.14 Shared Resources Clocking.....                                   | <b>195</b> |

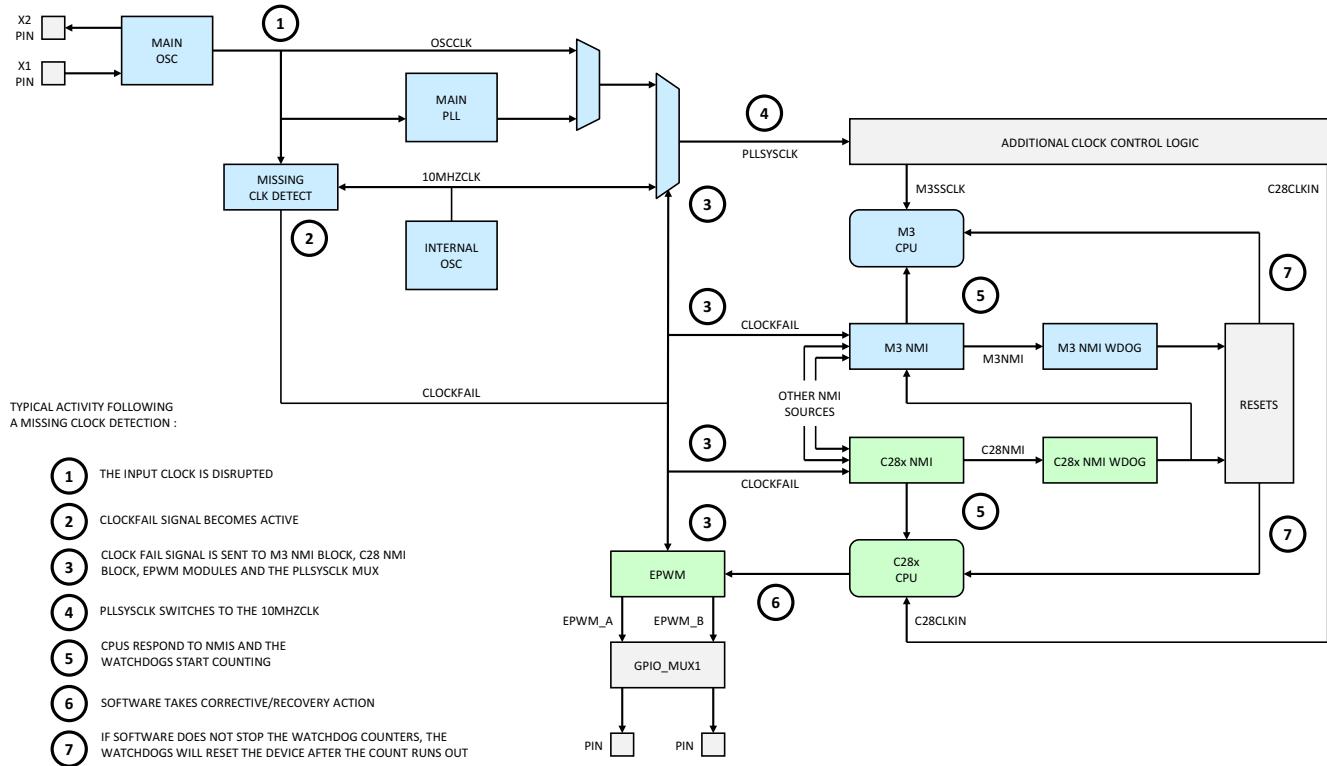

| 6.2 Signal Descriptions.....                                         | 11         | 8.15 Loss of Input Clock (NMI Watchdog Function).....                 | <b>195</b> |

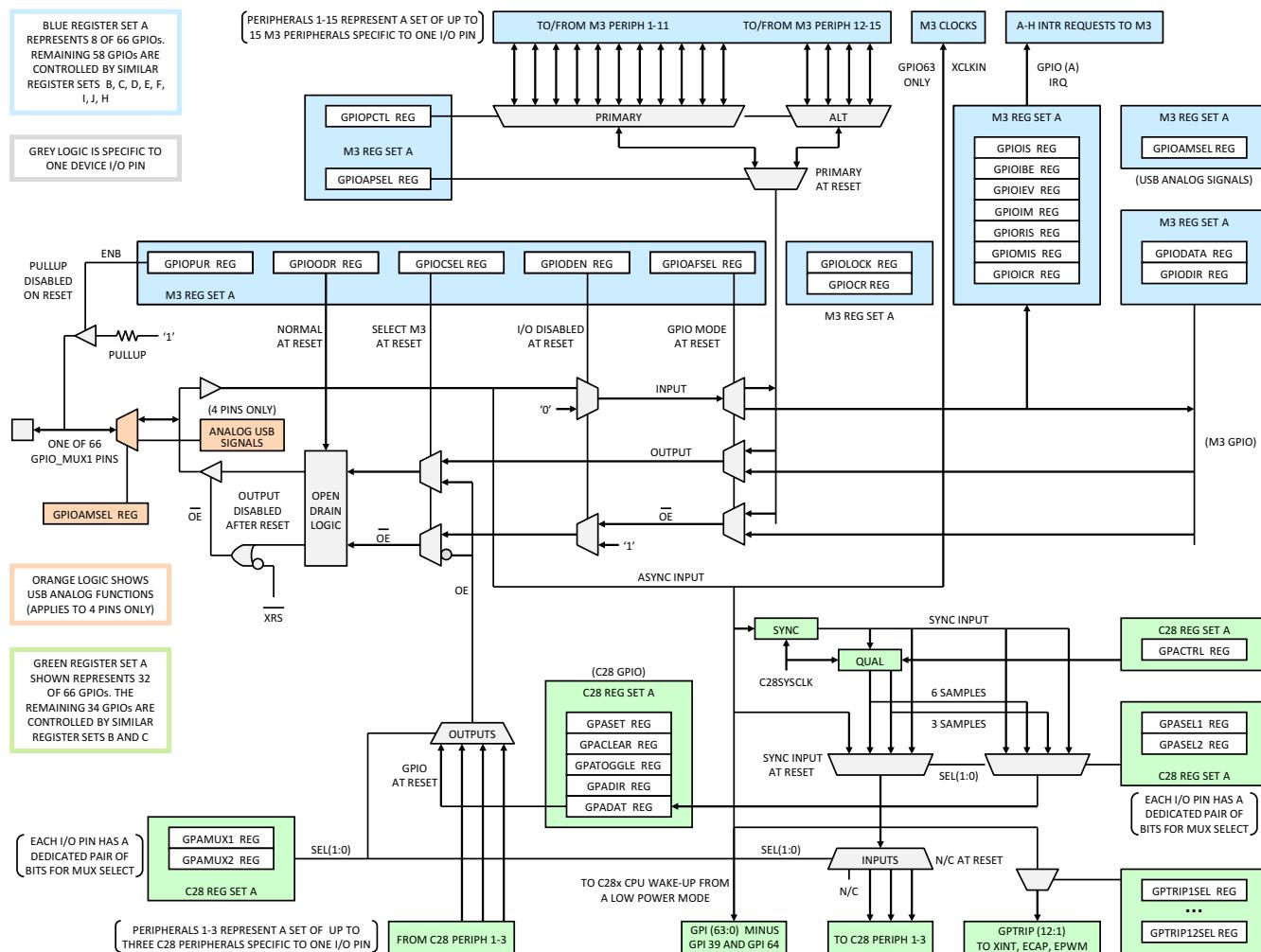

| <b>7 Specifications</b> .....                                        | <b>31</b>  | 8.16 GPIOs and Other Pins.....                                        | <b>196</b> |

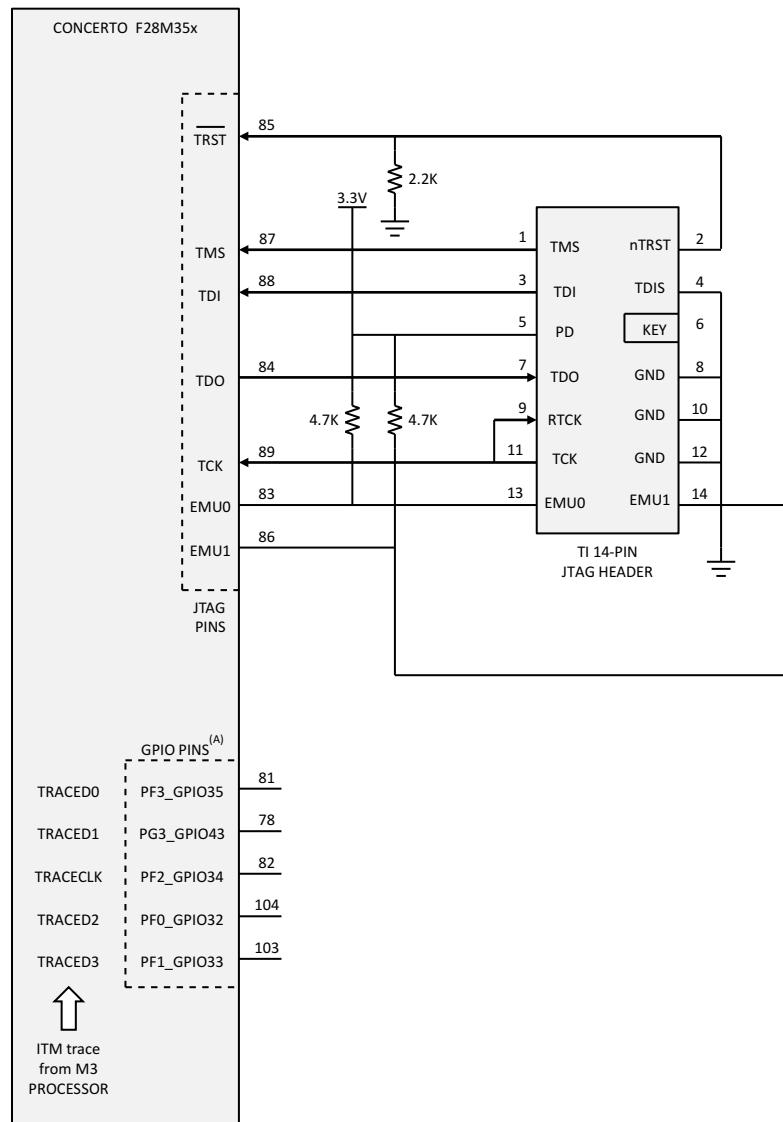

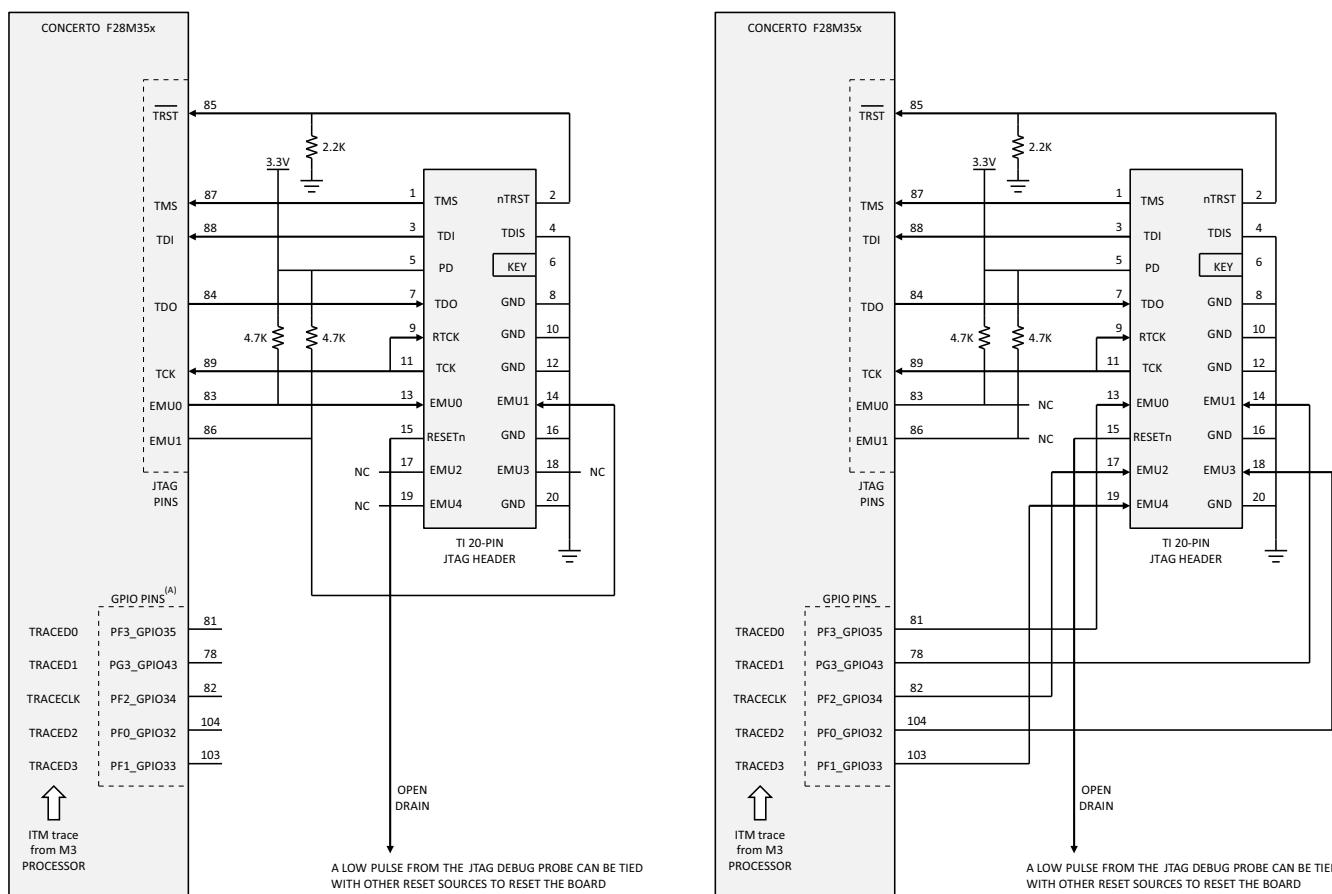

| 7.1 Absolute Maximum Ratings.....                                    | 31         | 8.17 Emulation/JTAG.....                                              | <b>211</b> |

| 7.2 ESD Ratings – Automotive.....                                    | 31         | 8.18 Code Security Module.....                                        | <b>213</b> |

| 7.3 ESD Ratings – Commercial.....                                    | 31         | 8.19 $\mu$ CRC Module.....                                            | <b>216</b> |

| 7.4 Recommended Operating Conditions.....                            | 32         | <b>9 Applications, Implementation, and Layout</b> .....               | <b>217</b> |

| 7.5 Power Consumption Summary.....                                   | 33         | 9.1 TI Reference Design.....                                          | <b>217</b> |

| 7.6 Electrical Characteristics.....                                  | 41         | <b>10 Device and Documentation Support</b> .....                      | <b>218</b> |

| 7.7 Thermal Resistance Characteristics for RFP PowerPAD Package..... | 42         | 10.1 Device and Development Support Tool Nomenclature.....            | <b>218</b> |

| 7.8 Thermal Design Considerations.....                               | 42         | 10.2 Tools and Software.....                                          | <b>219</b> |

| 7.9 Timing and Switching Characteristics.....                        | 43         | 10.3 Documentation Support.....                                       | <b>220</b> |

| 7.10 Analog and Shared Peripherals.....                              | 62         | 10.4 Trademarks.....                                                  | <b>221</b> |

| 7.11 Master Subsystem Peripherals.....                               | 97         | 10.5 Support Resources.....                                           | <b>221</b> |

| 7.12 Control Subsystem Peripherals.....                              | 114        | 10.6 Electrostatic Discharge Caution.....                             | <b>222</b> |

| <b>8 Detailed Description</b> .....                                  | <b>144</b> | 10.7 Glossary.....                                                    | <b>222</b> |

| 8.1 Memory Maps.....                                                 | 145        | <b>11 Mechanical, Packaging, and Orderable Information</b> .....      | <b>223</b> |

| 8.2 Identification.....                                              | 156        | 11.1 Packaging Information.....                                       | <b>223</b> |

| 8.3 Master Subsystem.....                                            | 157        |                                                                       |            |

| 8.4 Control Subsystem.....                                           | 163        |                                                                       |            |

| 8.5 Analog Subsystem.....                                            | 167        |                                                                       |            |

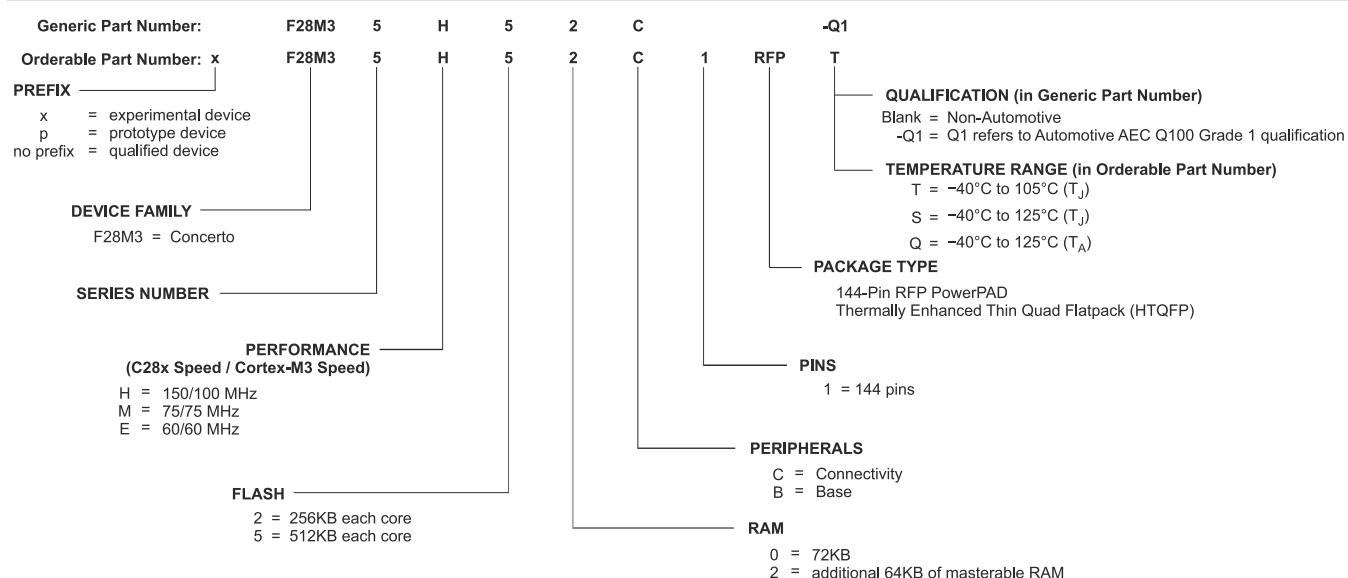

## 4 Revision History

**Changes from June 23, 2020 to February 1, 2021 (from Revision K (June 2020) to Revision L (February 2021))**

|                                                            | <b>Page</b> |

|------------------------------------------------------------|-------------|

| • Added Q1 Part Numbers.....                               | 0           |

| • <a href="#">Table 5-1</a> : Added Q1 Part Numbers.....   | 6           |

| • <a href="#">Figure 10-1</a> : Added GPN information..... | 218         |

## 5 Device Comparison

Table 5-1 lists the features of the F28M35x devices.

**Table 5-1. Device Comparison**

| FEATURE                                 | TYPE <sup>(1)</sup> | H52C<br>H52C-Q1 | H22C  | M52C                      | M22C  | E20B  |

|-----------------------------------------|---------------------|-----------------|-------|---------------------------|-------|-------|

| <b>Master Subsystem — Arm Cortex-M3</b> |                     |                 |       |                           |       |       |

| Speed (MHz) <sup>(2)</sup>              | —                   | 100             | 100   | 75                        | 75    | 60    |

| Flash (ECC) (KB)                        | —                   | 512             | 256   | 512                       | 256   | 256   |

| RAM (ECC) (KB)                          | —                   | 16              | 16    | 16                        | 16    | 16    |

| RAM (Parity) (KB)                       | —                   | 16              | 16    | 16                        | 16    | 16    |

| IPC Message RAM (Parity) (KB)           | —                   | 2               | 2     | 2                         | 2     | 2     |

| Security Zones                          | —                   | 2               | 2     | 2                         | 2     | 2     |

| 10/100 ENET 1588 MII                    | 0                   | Yes             | Yes   | Yes                       | Yes   | No    |

| USB OTG FS                              | 0                   | Yes             | Yes   | Yes                       | Yes   | No    |

| SSI/SPI                                 | 0                   | 4               | 4     | 4                         | 4     | 4     |

| UART                                    | 0                   | 5               | 5     | 5                         | 5     | 5     |

| I2C                                     | 0                   | 2               | 2     | 2                         | 2     | 2     |

| CAN <sup>(3)</sup>                      | 0                   | 2               | 2     | 2                         | 2     | 2     |

| μDMA                                    | 0                   | 32-ch           | 32-ch | 32-ch                     | 32-ch | 32-ch |

| EPI <sup>(4)</sup>                      | 0                   | 1               | 1     | 1                         | 1     | 1     |

| μCRC module                             | 0                   | 1               | 1     | 1                         | 1     | 1     |

| General-Purpose Timers                  | —                   | 4               | 4     | 4                         | 4     | 4     |

| Watchdog Timer modules                  | —                   | 2               | 2     | 2                         | 2     | 2     |

| <b>Control Subsystem — C28x</b>         |                     |                 |       |                           |       |       |

| Speed (MHz) <sup>(2)</sup>              |                     | 150             | 150   | 75                        | 75    | 60    |

| FPU                                     |                     |                 |       | Yes                       |       |       |

| VCU                                     |                     |                 |       | Yes                       |       |       |

| Flash (ECC) (KB)                        |                     | 512             | 256   | 512                       | 256   | 256   |

| RAM (ECC) (KB)                          |                     | 20              | 20    | 20                        | 20    | 20    |

| RAM (Parity) (KB)                       |                     | 16              | 16    | 16                        | 16    | 16    |

| IPC Message RAM (Parity) (KB)           |                     | 2               | 2     | 2                         | 2     | 2     |

| Security Zones                          |                     | 1               | 1     | 1                         | 1     | 1     |

| ePWM modules                            | 2                   |                 |       | 9: 18 outputs             |       |       |

| High-Resolution PWM (HRPWM) outputs     | 2                   |                 |       | 16 outputs                |       |       |

| eCAP modules/PWM outputs                | 0                   |                 |       | 6 (32-bit)                |       |       |

| eQEP modules                            | 0                   |                 |       | 3 (32-bit)                |       |       |

| Fault Trip Zones                        | —                   |                 |       | 12 on any of 64 GPIO pins |       |       |

| McBSP/SPI                               | 1                   | 1               | 1     | 1                         | 1     | 1     |

| SCI                                     | 0                   | 1               | 1     | 1                         | 1     | 1     |

| SPI                                     | 0                   | 1               | 1     | 1                         | 1     | 1     |

| I2C                                     | 0                   | 1               | 1     | 1                         | 1     | 1     |

| DMA                                     | 0                   | 6-ch            | 6-ch  | 6-ch                      | 6-ch  | 6-ch  |

| EPI <sup>(4)</sup>                      | 0                   | 1               | 1     | 1                         | 1     | 1     |

| 32-Bit Timers                           | —                   | 3               | 3     | 3                         | 3     | 3     |

| <b>Shared</b>                           |                     |                 |       |                           |       |       |

| Shared RAM (Parity) (KB)                |                     | 64              | 64    | 64                        | 64    | 0     |

**Table 5-1. Device Comparison (continued)**

| FEATURE                                   |                                  | TYPE <sup>(1)</sup> | H52C<br>H52C-Q1                                                          | H22C   | M52C   | M22C   | E20B   |

|-------------------------------------------|----------------------------------|---------------------|--------------------------------------------------------------------------|--------|--------|--------|--------|

| 12-Bit ADC 1                              | MSPS <sup>(5)</sup>              | 3                   | 2.88                                                                     | 2.88   | 2.88   | 2.88   | 2.31   |

|                                           | Conversion Time <sup>(5)</sup>   |                     | 347 ns                                                                   | 347 ns | 347 ns | 347 ns | 433 ns |

|                                           | Channels                         |                     | 10                                                                       | 10     | 10     | 10     | 10     |

|                                           | Sample-and-Hold                  |                     | 2                                                                        | 2      | 2      | 2      | 2      |

| 12-Bit ADC 2                              | MSPS <sup>(5)</sup>              | 3                   | 2.88                                                                     | 2.88   | 2.88   | 2.88   | 2.31   |

|                                           | Conversion Time <sup>(5)</sup>   |                     | 347 ns                                                                   | 347 ns | 347 ns | 347 ns | 433 ns |

|                                           | Channels                         |                     | 10                                                                       | 10     | 10     | 10     | 10     |

|                                           | Sample-and-Hold                  |                     | 2                                                                        | 2      | 2      | 2      | 2      |

| Comparators with Integrated DACs          | 0                                |                     | 6                                                                        | 6      | 6      | 6      | 6      |

| Voltage Regulator                         |                                  |                     | Yes – Uses 3.3-V Single Supply (3.3-V/1.2-V recommended for 125°C)       |        |        |        |        |

| Clocking                                  |                                  |                     | See <a href="#">Section 8.10</a>                                         |        |        |        |        |

| <b>Additional Safety</b>                  |                                  |                     |                                                                          |        |        |        |        |

| Master Subsystem                          |                                  |                     | 2 Watchdogs, NMI Watchdog: CPU, Memory                                   |        |        |        |        |

| Control Subsystem                         |                                  |                     | NMI Watchdog: CPU, Memory                                                |        |        |        |        |

| Shared                                    |                                  |                     | Critical Register and I/O Function Lock Protection; RAM Fetch Protection |        |        |        |        |

| <b>Packaging</b>                          |                                  |                     |                                                                          |        |        |        |        |

| Package Type                              | 144-Pin RFP PowerPAD<br>HTQFP    |                     | Yes                                                                      | Yes    | Yes    | Yes    | Yes    |

| Junction<br>Temperature (T <sub>J</sub> ) | T: -40°C to 105°C                | –                   | Yes                                                                      | Yes    | Yes    | Yes    | Yes    |

|                                           | S: -40°C to 125°C                | –                   | Yes                                                                      | Yes    | Yes    | Yes    | Yes    |

|                                           | Q: -40°C to 150°C <sup>(6)</sup> | –                   | Yes                                                                      | No     | No     | No     | No     |

| Free-Air<br>Temperature (T <sub>A</sub> ) | Q: -40°C to 125°C <sup>(6)</sup> | –                   | Yes                                                                      | No     | No     | No     | No     |

- (1) A type change represents a major functional feature difference in a peripheral module. Within a peripheral type, there may be minor differences between devices that do not affect the basic functionality of the module. These device-specific differences are listed in the [C2000 Real-Time Control Peripherals Reference Guide](#) and in the peripheral reference guides.

- (2) The maximum frequency at which the Cortex-M3 core can run is 100 MHz. The clock divider before the Cortex-M3 core can only take values of /1, /2, or /4. For this reason, when the C28x is configured to run at the maximum frequency of 150 MHz, the fastest allowable frequency for the Cortex-M3 is 75 MHz. If the Cortex-M3 is configured to run at 100 MHz, the maximum frequency of the C28x is limited to 100 MHz.

- (3) The CAN module uses the popular IP known as D\_CAN. This document uses the names "CAN" and "D\_CAN" interchangeably to reference this peripheral.

- (4) Single EPI arbitrated between masters in Master and Control Subsystems.

- (5) An integer divide ratio must be maintained between the C28x and ADC clock frequencies. All MSPS and Conversion Time values are based on the maximum C28x clock frequency.

- (6) "Q" refers to AEC Q100 qualification for automotive applications.

**Table 5-2. Possible Speed Combinations for Cortex-M3 and C28x Cores**

|           |         |         |        |        |

|-----------|---------|---------|--------|--------|

| Cortex-M3 | 75 MHz  | 100 MHz | 75 MHz | 60 MHz |

| C28x      | 150 MHz | 100 MHz | 75 MHz | 60 MHz |

## 5.1 Related Products

For information about other devices in this family of products, see the following link:

### [F28M36x Concerto™ Microcontrollers](#)

The F28M3x series of microcontrollers brings together connectivity and control by combining an Arm Cortex-M3 core with the C28x core on to one device. With F28M3x, applications such as solar inverters and industrial control can keep the benefits of separating the communication and control portions while maintaining a single-chip solution. In addition, F28M3x microcontrollers enable safety certifications in your system through enhanced hardware and safety features.

The F28M36x family of devices is the second series in the Concerto family.

### [TMS320F2838x Microcontrollers With Connectivity Manager](#)

The TMS320F2838x is a powerful 32-bit floating-point microcontroller unit (MCU) designed for advanced closed-loop control applications. The F2838x supports a dual-core C28x architecture along with a new Connectivity Manager that offloads critical communication tasks, significantly boosting system performance. The integrated analog and control peripherals with advanced connectivity peripherals like EtherCAT and Ethernet also let designers consolidate real-time control and real-time communications architectures, reducing requirements for multicontroller systems.

## 6 Terminal Configuration and Functions

### 6.1 Pin Diagram

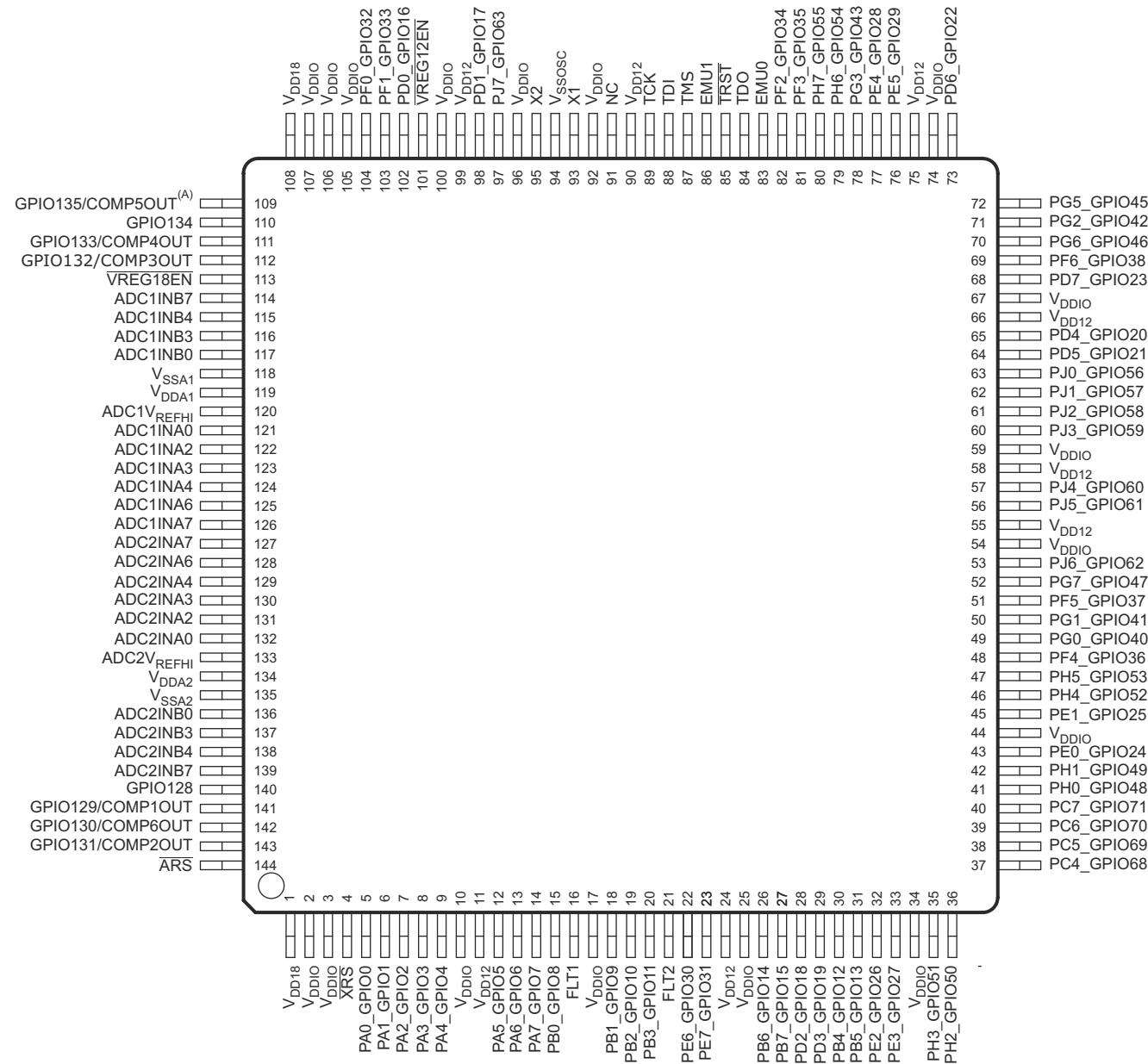

Figure 6-1 shows the 144-pin RFP PowerPAD Thermally Enhanced Thin Quad Flatpack pin assignments.

A. All I/Os, except for GPIO135, are glitch-free during power up and power down. See [Section 8.11](#).

B. See [Section 6.2.1](#), Signal Descriptions, for the complete multiplexed signal names.

**Figure 6-1. 144-Pin RFP PowerPAD Thermally Enhanced Thin Quad Flatpack (Top View)**

---

#### Note

The exposed lead frame die pad of the PowerPAD package serves two functions: to remove heat from the die and to provide ground path for the digital ground (analog ground is provided through dedicated pins). Thus, the PowerPAD should be soldered to the ground (GND) plane of the PCB because this will provide both the digital ground path and good thermal conduction path. To make optimum use of the thermal efficiencies designed into the PowerPAD package, the PCB must be designed with this technology in mind. A thermal land is required on the surface of the PCB directly underneath the body of the PowerPAD. The thermal land should be soldered to the exposed lead frame die pad of the PowerPAD package; the thermal land should be as large as needed to dissipate the required heat. An array of thermal vias should be used to connect the thermal pad to the internal GND plane of the board. See [PowerPAD™ Thermally Enhanced Package](#) for more details on using the PowerPAD package.

---

## 6.2 Signal Descriptions

Section 6.2.1 describes the signals.

### 6.2.1 Signal Descriptions

| TERMINAL <sup>(1)</sup>                                                          |                       | I/O/Z <sup>(2)</sup> | DESCRIPTION                                                                   | PU<br>or<br>PD <sup>(3)</sup> | OUTPUT<br>BUFFER<br>STRENGTH |

|----------------------------------------------------------------------------------|-----------------------|----------------------|-------------------------------------------------------------------------------|-------------------------------|------------------------------|

| NAME                                                                             | RFP<br>PIN NO.        |                      |                                                                               |                               |                              |

| <b>ADC 1 Reference Inputs, Analog Comparator Inputs, DAC Inputs, AIO Group 1</b> |                       |                      |                                                                               |                               |                              |

| ADC1V <sub>REFHI</sub>                                                           | 120                   | I                    | ADC1 External High Reference – used only when in ADC external reference mode. |                               |                              |

| ADC1V <sub>REFLO</sub>                                                           | see V <sub>SSA1</sub> | I                    | ADC1 External Low Reference – used only when in ADC external reference mode.  |                               |                              |

| ADC1INA0                                                                         | 121                   | I                    | ADC1 Group A, Channel 0 input                                                 |                               |                              |

| ADC1INA2                                                                         |                       | I                    | ADC1 Group A, Channel 2 input                                                 |                               |                              |

| COMPA1                                                                           | 122                   | I                    | Comparator Input A1                                                           |                               | 4 mA                         |

| AIO2                                                                             |                       | I/O                  | Digital AIO2                                                                  |                               |                              |

| ADC1INA3                                                                         | 123                   | I                    | ADC1 Group A, Channel 3 input                                                 |                               |                              |

| ADC1INA4                                                                         |                       | I                    | ADC1 Group A, Channel 4 input                                                 |                               |                              |

| COMPA2                                                                           | 124                   | I                    | Comparator Input A2                                                           |                               | 4 mA                         |

| AIO4                                                                             |                       | I/O                  | Digital AIO4                                                                  |                               |                              |

| ADC1INA6                                                                         |                       | I                    | ADC1 Group A, Channel 6 input                                                 |                               |                              |

| COMPA3                                                                           | 125                   | I                    | Comparator Input A3                                                           |                               | 4 mA                         |

| AIO6                                                                             |                       | I/O                  | Digital AIO6                                                                  |                               |                              |

| ADC1INA7                                                                         | 126                   | I                    | ADC1 Group A, Channel 7 input                                                 |                               |                              |

| ADC1INB0                                                                         | 117                   | I                    | ADC1 Group B, Channel 0 input                                                 |                               |                              |

| ADC1INB3                                                                         | 116                   | I                    | ADC1 Group B, Channel 3 input                                                 |                               |                              |

| ADC1INB4                                                                         |                       | I                    | ADC1 Group B, Channel 4 input                                                 |                               |                              |

| COMPB2                                                                           | 115                   | I                    | Comparator Input B2                                                           |                               | 4 mA                         |

| AIO12                                                                            |                       | I/O                  | Digital AIO12                                                                 |                               |                              |

| ADC1INB7                                                                         | 114                   | I                    | ADC1 Group B, Channel 7 input                                                 |                               |                              |

| <b>ADC 2 Reference Inputs, Analog Comparator Inputs, DAC Inputs, AIO Group 2</b> |                       |                      |                                                                               |                               |                              |

| ADC2V <sub>REFHI</sub>                                                           | 133                   | I                    | ADC2 External High Reference – used only when in ADC external reference mode. |                               |                              |

| ADC2V <sub>REFLO</sub>                                                           | see V <sub>SSA2</sub> | I                    | ADC2 External Low Reference – used only when in ADC external reference mode.  |                               |                              |

| ADC2INA0                                                                         | 132                   | I                    | ADC2 Group A, Channel 0 input                                                 |                               |                              |

| ADC2INA2                                                                         |                       | I                    | ADC2 Group A, Channel 2 input                                                 |                               |                              |

| COMPA4                                                                           | 131                   | I                    | Comparator Input A4                                                           |                               | 4 mA                         |

| AIO18                                                                            |                       | I/O                  | Digital AIO18                                                                 |                               |                              |

| ADC2INA3                                                                         | 130                   | I                    | ADC2 Group A, Channel 3 input                                                 |                               |                              |

| ADC2INA4                                                                         |                       | I                    | ADC2 Group A, Channel 4 input                                                 |                               |                              |

| COMPA5                                                                           | 129                   | I                    | Comparator Input A5                                                           |                               | 4 mA                         |

| AIO20                                                                            |                       | I/O                  | Digital AIO20                                                                 |                               |                              |

| ADC2INA6                                                                         |                       | I                    | ADC2 Group A, Channel 6 input                                                 |                               |                              |

| COMPA6                                                                           | 128                   | I                    | Comparator Input A6                                                           |                               | 4 mA                         |

| AIO22                                                                            |                       | I/O                  | Digital AIO22                                                                 |                               |                              |

| ADC2INA7                                                                         | 127                   | I                    | ADC2 Group A, Channel 7 input                                                 |                               |                              |

| ADC2INB0                                                                         | 136                   | I                    | ADC2 Group B, Channel 0 input                                                 |                               |                              |

| ADC2INB3                                                                         | 137                   | I                    | ADC2 Group B, Channel 3 input                                                 |                               |                              |

| TERMINAL <sup>(1)</sup>                                                        |                | I/O/Z <sup>(2)</sup> | DESCRIPTION                                                                                    | PU<br>or<br>PD <sup>(3)</sup> | OUTPUT<br>BUFFER<br>STRENGTH |

|--------------------------------------------------------------------------------|----------------|----------------------|------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|

| NAME                                                                           | RFP<br>PIN NO. |                      |                                                                                                |                               |                              |

| ADC2INB4                                                                       |                | I                    | ADC2 Group B, Channel 4 input                                                                  |                               |                              |

| COMPB5                                                                         | 138            | I                    | Comparator Input B5                                                                            |                               | 4 mA                         |

| AIO28                                                                          |                | I/O                  | Digital AIO28                                                                                  |                               |                              |

| ADC2INB7                                                                       | 139            | I                    | ADC2 Group B, Channel 7 input                                                                  |                               |                              |

| <b>ADC Modules Analog Power and Ground</b>                                     |                |                      |                                                                                                |                               |                              |

| V <sub>DDA1</sub>                                                              | 119            |                      | 3.3-V Analog Module 1 Power Pin. Tie with a 2.2- $\mu$ F capacitor (typical) close to the pin. |                               |                              |

| V <sub>DDA2</sub>                                                              | 134            |                      | 3.3-V Analog Module 2 Power Pin. Tie with a 2.2- $\mu$ F capacitor (typical) close to the pin. |                               |                              |

| V <sub>SSA1</sub>                                                              | 118            |                      | Analog ground for ADC1, ADC1V <sub>REFLO</sub> , COMP1–3, and DAC1–3                           |                               |                              |

| V <sub>SSA2</sub>                                                              | 135            |                      | Analog ground for ADC2, ADC2V <sub>REFLO</sub> , COMP4–6, and DAC4–6                           |                               |                              |

| <b>Analog Comparator Results (Digital) and GPIO Group 2 (C28x Access Only)</b> |                |                      |                                                                                                |                               |                              |

| GPIO128                                                                        | 140            | I/O                  | General-purpose input/output 128                                                               | PU                            | 4 mA                         |

| GPIO129                                                                        |                | I/O                  | General-purpose input/output 129                                                               | PU                            | 4 mA                         |

| COMP1OUT                                                                       | 141            | O                    | Compare result from Analog Comparator 1                                                        | PU                            | 4 mA                         |

| GPIO130                                                                        |                | I/O                  | General-purpose input/output 130                                                               | PU                            | 4 mA                         |

| COMP6OUT                                                                       | 142            | O                    | Compare result from Analog Comparator 6                                                        | PU                            | 4 mA                         |

| GPIO131                                                                        |                | I/O                  | General-purpose input/output 131                                                               | PU                            | 4 mA                         |

| COMP2OUT                                                                       | 143            | O                    | Compare result from Analog Comparator 2                                                        | PU                            | 4 mA                         |

| GPIO132                                                                        |                | I/O                  | General-purpose input/output 132                                                               | PU                            | 8 mA                         |

| COMP3OUT                                                                       | 112            | O                    | Compare result from Analog Comparator 3                                                        | PU                            | 8 mA                         |

| GPIO133                                                                        |                | I/O                  | General-purpose input/output 133                                                               | PU                            | 4 mA                         |

| COMP4OUT                                                                       | 111            | O                    | Compare result from Analog Comparator 4                                                        | PU                            | 4 mA                         |

| GPIO134                                                                        | 110            | I/O                  | General-purpose input/output 134                                                               | PU                            | 4 mA                         |

| GPIO135 <sup>(4)</sup>                                                         |                | I/O                  | General-purpose input/output 135                                                               | PU                            | 8 mA                         |

| COMP5OUT                                                                       | 109            | O                    | Compare result from Analog Comparator 5                                                        | PU                            | 8 mA                         |

| <b>GPIO Group 1 and Peripheral Signals</b>                                     |                |                      |                                                                                                |                               |                              |

| PA0_GPIO0                                                                      |                | I/O/Z                | General-purpose input/output 0                                                                 |                               |                              |

| M_U0RX                                                                         |                | I                    | UART-0 receive data                                                                            |                               |                              |

| M_I2C1SCL                                                                      | 5              | I/OD                 | I2C-1 clock open-drain bidirectional port                                                      | PU                            | 4 mA                         |

| M_U1RX                                                                         |                | I                    | UART-1 receive data                                                                            |                               |                              |

| C_EPWM1A                                                                       |                | O                    | Enhanced PWM-1 output A                                                                        |                               |                              |

| PA1_GPIO1                                                                      |                | I/O/Z                | General-purpose input/output 1                                                                 |                               |                              |

| M_U0TX                                                                         |                | O                    | UART-0 transmit data                                                                           |                               |                              |

| M_I2C1SDA                                                                      | 6              | I/OD                 | I2C-1 data open-drain bidirectional port                                                       | PU                            | 4 mA                         |

| M_U1TX                                                                         |                | O                    | UART-1 data transmit                                                                           |                               |                              |

| M_SSI1FSS                                                                      |                | I/O                  | SSI-1 frame                                                                                    |                               |                              |

| C_EPWM1B                                                                       |                | O                    | Enhanced PWM-1 output B                                                                        |                               |                              |

| C_ECAP6                                                                        |                | I/O                  | Enhanced Capture-6 input/output                                                                |                               |                              |

| PA2_GPIO2                                                                      |                | I/O/Z                | General-purpose input/output 2                                                                 |                               |                              |

| M_SSI0CLK                                                                      | 7              | I/O                  | SSI-0 clock                                                                                    | PU                            | 4 mA                         |

| M_MIITXD2                                                                      |                | O                    | EMAC MII transmit data bit 2                                                                   |                               |                              |

| C_EPWM2A                                                                       |                | O                    | Enhanced PWM-2 output A                                                                        |                               |                              |

| TERMINAL <sup>(1)</sup> |                | I/O/Z <sup>(2)</sup> | DESCRIPTION | PU<br>or<br>PD <sup>(3)</sup> | OUTPUT<br>BUFFER<br>STRENGTH |

|-------------------------|----------------|----------------------|-------------|-------------------------------|------------------------------|

| NAME                    | RFP<br>PIN NO. |                      |             |                               |                              |

| PA3_GPIO3               |                | 8                    | I/O/Z       | PU                            | 4 mA                         |

| M_SSI0FSS               |                |                      | I/O         |                               |                              |

| M_MIITXD1               |                |                      | O           |                               |                              |

| M_SSI1CLK               |                |                      | I/O         |                               |                              |

| C_EPWM2B                |                |                      | O           |                               |                              |

| C_ECAP5                 |                |                      | I/O         |                               |                              |

| PA4_GPIO4               |                | 9                    | I/O/Z       | PU                            | 4 mA                         |

| M_SSI0RX                |                |                      | I           |                               |                              |

| M_MIITXD0               |                |                      | O           |                               |                              |

| M_CAN0RX                |                |                      | I           |                               |                              |

| C_EPWM3A                |                |                      | O           |                               |                              |

| PA5_GPIO5               |                | 12                   | I/O/Z       | PU                            | 4 mA                         |

| M_SSI0TX                |                |                      | O           |                               |                              |

| M_MIIRXDV               |                |                      | I           |                               |                              |

| M_CAN0TX                |                |                      | O           |                               |                              |

| C_EPWM3B                |                |                      | O           |                               |                              |

| C_MFSRA                 |                |                      | I           |                               |                              |

| C_ECAP1                 |                |                      | I/O         |                               |                              |

| PA6_GPIO6               |                | 13                   | I/O/Z       | PU                            | 4 mA                         |

| M_I2C1SCL               |                |                      | I/OD        |                               |                              |

| M_CCP1                  |                |                      | I/O         |                               |                              |

| M_MIIRXCK               |                |                      | I           |                               |                              |

| M_CAN0RX                |                |                      | I           |                               |                              |

| M_USB0EPEN              |                |                      | O           |                               |                              |

| M_MIITXD3               |                |                      | O           |                               |                              |

| C_EPWM4A                |                |                      | O           |                               |                              |

| C_EPWMSYNCO             |                |                      | O           |                               |                              |

| PA7_GPIO7               |                | 14                   | I/O/Z       | PU                            | 4 mA                         |

| M_I2C1SDA               |                |                      | I/OD        |                               |                              |

| M_CCP4                  |                |                      | I/O         |                               |                              |

| M_MIIRXER               |                |                      | I           |                               |                              |

| M_CAN0TX                |                |                      | O           |                               |                              |

| M_CCP3                  |                |                      | I/O         |                               |                              |

| M_USB0PFLT              |                |                      | I           |                               |                              |

| M_MIIRXD1               |                |                      | I           |                               |                              |

| C_EPWM4B                |                |                      | O           |                               |                              |

| C_MCLKRA                |                |                      | I           |                               |                              |

| C_ECAP2                 |                |                      | I/O         |                               |                              |

| TERMINAL <sup>(1)</sup> |                | I/O/Z <sup>(2)</sup> | DESCRIPTION                                                            | PU<br>or<br>PD <sup>(3)</sup> | OUTPUT<br>BUFFER<br>STRENGTH |

|-------------------------|----------------|----------------------|------------------------------------------------------------------------|-------------------------------|------------------------------|

| NAME                    | RFP<br>PIN NO. |                      |                                                                        |                               |                              |

| PB0_GPIO8               | 15             | I/O/Z                | General-purpose input/output 8                                         | PU                            | 4 mA                         |

| M_CCP0                  |                | I/O                  | Capture/Compare/PWM-0<br>(General-purpose Timer)                       |                               |                              |

| M_U1RX                  |                | I                    | UART-1 data receive data                                               |                               |                              |

| M_SSI2TX                |                | O                    | SSI-2 transmit data                                                    |                               |                              |

| M_CAN1TX                |                | O                    | CAN-1 transmit data                                                    |                               |                              |

| M_U4TX                  |                | O                    | UART-4 transmit data                                                   |                               |                              |

| C_EPWM5A                |                | O                    | Enhanced PWM-5 output A                                                |                               |                              |

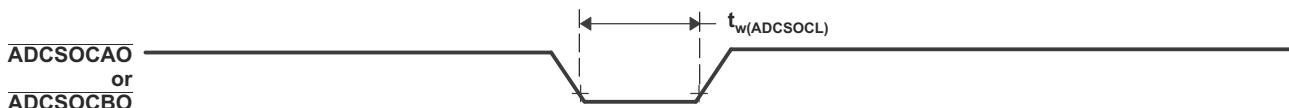

| C_ADCSOCDAO             |                | O                    | ADC start-of-conversion A                                              |                               |                              |

| PB1_GPIO9               | 18             | I/O/Z                | General-purpose input/output 9                                         | PU                            | 4 mA                         |

| M_CCP2                  |                | I/O                  | Capture/Compare/PWM-2<br>(General-purpose Timer)                       |                               |                              |

| M_CCP1                  |                | I/O                  | Capture/Compare/PWM-1<br>(General-purpose Timer)                       |                               |                              |

| M_U1TX                  |                | O                    | UART-1 transmit data                                                   |                               |                              |

| M_SSI2RX                |                | I                    | SSI-2 receive data                                                     |                               |                              |

| C_EPWM5B                |                | O                    | Enhanced PWM-5 output B                                                |                               |                              |

| C_ECAP3                 |                | I/O                  | Enhanced Capture-3 input/output                                        |                               |                              |

| PB2_GPIO10              | 19             | I/O/Z                | General-purpose input/output 10                                        | PU                            | 4 mA                         |

| M_I2C0SCL               |                | I/OD                 | I2C-0 clock open-drain bidirectional port                              |                               |                              |

| M_CCP3                  |                | I/O                  | Capture/Compare/PWM-3<br>(General-purpose Timer)                       |                               |                              |

| M_CCP0                  |                | I/O                  | Capture/Compare/PWM-0<br>(General-purpose Timer)                       |                               |                              |

| M_USB0EPEN              |                | O                    | USB-0 external power enable<br>(optionally used in the host mode)      |                               |                              |

| M_SSI2CLK               |                | I/O                  | SSI-2 clock                                                            |                               |                              |

| M_CAN1RX                |                | I                    | CAN-1 receive data                                                     |                               |                              |

| M_U4RX                  |                | I                    | UART-4 receive data                                                    |                               |                              |

| C_EPWM6A                |                | O                    | Enhanced PWM-6 output A                                                |                               |                              |

| C_ADCSOCBO              |                | O                    | ADC start-of-conversion B                                              |                               |                              |

| PB3_GPIO11              | 20             | I/O/Z                | General-purpose input/output 11                                        | PU                            | 4 mA                         |

| M_I2C0SDA               |                | I/OD                 | I2C-0 data open-drain bidirectional port                               |                               |                              |

| M_USB0PFLT              |                | I                    | USB-0 external power error state<br>(optionally used in the host mode) |                               |                              |

| M_SSI2FSS               |                | I/O                  | SSI-2 frame                                                            |                               |                              |

| M_U1RX                  |                | I                    | UART-1 receive data                                                    |                               |                              |

| C_EPWM6B                |                | O                    | Enhanced PWM-6 output B                                                |                               |                              |

| C_ECAP4                 |                | I/O                  | Enhanced Capture-4 input/output                                        |                               |                              |

| PB4_GPIO12              | 30             | I/O/Z                | General-purpose input/output 12                                        | PU                            | 4 mA                         |

| M_U2RX                  |                | I                    | UART-2 receive data                                                    |                               |                              |

| M_CAN0RX                |                | I                    | CAN-0 receive data                                                     |                               |                              |

| M_U1RX                  |                | I                    | UART-1 receive data                                                    |                               |                              |

| M_EPI0S23               |                | I/O                  | EPI-0 signal 23                                                        |                               |                              |

| M_CAN1TX                |                | O                    | CAN-1 transmit data                                                    |                               |                              |

| M_SSI1TX                |                | O                    | SSI-1 transmit data                                                    |                               |                              |

| C_EPWM7A                |                | O                    | Enhanced PWM-7 output A                                                |                               |                              |

| TERMINAL <sup>(1)</sup>  |                | I/O/Z <sup>(2)</sup> | DESCRIPTION                                      | PU<br>or<br>PD <sup>(3)</sup> | OUTPUT<br>BUFFER<br>STRENGTH |

|--------------------------|----------------|----------------------|--------------------------------------------------|-------------------------------|------------------------------|

| NAME                     | RFP<br>PIN NO. |                      |                                                  |                               |                              |

| PB5_GPIO13               | 31             | I/O/Z                | General-purpose input/output 13                  | PU                            | 4 mA                         |

| M_CCP5                   |                | I/O                  | Capture/Compare/PWM-5<br>(General-purpose Timer) |                               |                              |

| M_CCP6                   |                | I/O                  | Capture/Compare/PWM-6<br>(General-purpose Timer) |                               |                              |

| M_CCP0                   |                | I/O                  | Capture/Compare/PWM-0<br>(General-purpose Timer) |                               |                              |

| M_CAN0TX                 |                | O                    | CAN-0 transmit data                              |                               |                              |

| M_CCP2                   |                | I/O                  | Capture/Compare/PWM-2<br>(General-purpose Timer) |                               |                              |

| M_U1TX                   |                | O                    | UART-1 transmit data                             |                               |                              |

| M_EPI0S22                |                | I/O                  | EPI-0 signal 22                                  |                               |                              |

| M_CAN1RX                 |                | I                    | CAN-1 receive data                               |                               |                              |

| M_SSI1RX                 |                | I                    | SSI-1 receive data                               |                               |                              |

| C_EPWM7B                 |                | O                    | Enhanced PWM-7 output B                          |                               |                              |

| PB6_GPIO14               | 26             | I/O/Z                | General-purpose input/output 14                  | PU                            | 4 mA                         |

| M_CCP1                   |                | I/O                  | Capture/Compare/PWM-1<br>(General-purpose Timer) |                               |                              |

| M_CCP7                   |                | I/O                  | Capture/Compare/PWM-7<br>(General-purpose Timer) |                               |                              |

| M_CCP5                   |                | I/O                  | Capture/Compare/PWM-5<br>(General-purpose Timer) |                               |                              |

| M_EPI0S37 <sup>(5)</sup> |                | I/O                  | EPI-0 signal 37                                  |                               |                              |

| M_MIICRS                 |                | I                    | EMAC MII carrier sense                           |                               |                              |

| M_I2C0SDA                |                | I/OD                 | I2C-0 data open-drain bidirectional port         |                               |                              |

| M_U1TX                   |                | O                    | UART-1 transmit data                             |                               |                              |

| M_SSI1CLK                |                | I/O                  | SSI-1 clock                                      |                               |                              |

| C_EPWM8A                 |                | O                    | Enhanced PWM-8 output A                          |                               |                              |

| PB7_GPIO15               | 27             | I/O/Z                | General-purpose input/output 15                  | PU                            | 4 mA                         |

| M_EXTNMI                 |                | I                    | Cortex-M3 external nonmaskable interrupt         |                               |                              |

| M_MIIRXD1                |                | I                    | EMAC MII receive data 1                          |                               |                              |

| M_EPI0S36 <sup>(5)</sup> |                | I/O                  | EPI-0 signal 36                                  |                               |                              |

| M_I2C0SCL                |                | I/OD                 | I2C-0 clock open-drain bidirectional port        |                               |                              |

| M_U1RX                   |                | I                    | UART-1 receive data                              |                               |                              |

| M_SSI1FSS                |                | I/O                  | SSI-1 frame                                      |                               |                              |

| C_EPWM8B                 |                | O                    | Enhanced PWM-8 output B                          |                               |                              |

| TERMINAL <sup>(1)</sup> |                | I/O/Z <sup>(2)</sup> | DESCRIPTION                                                            | PU<br>or<br>PD <sup>(3)</sup> | OUTPUT<br>BUFFER<br>STRENGTH |

|-------------------------|----------------|----------------------|------------------------------------------------------------------------|-------------------------------|------------------------------|

| NAME                    | RFP<br>PIN NO. |                      |                                                                        |                               |                              |

| PD0_GPIO16              | 102            | I/O/Z                | General-purpose input/output 16                                        | PU                            | 4 mA                         |

| M_CAN0RX                |                | I                    | CAN-0 receive data                                                     |                               |                              |

| M_U2RX                  |                | I                    | UART-2 receive data                                                    |                               |                              |

| M_U1RX                  |                | I                    | UART-1 receive data                                                    |                               |                              |

| M_CCP6                  |                | I/O                  | Capture/Compare/PWM-6<br>(General-purpose Timer)                       |                               |                              |

| M_MIIRXDV               |                | I                    | EMAC MII receive data valid                                            |                               |                              |

| M_MIIRXD2               |                | I                    | EMAC MII receive data 2                                                |                               |                              |

| M_SSI0TX                |                | O                    | SSI-0 transmit data                                                    |                               |                              |

| M_CAN1TX                |                | O                    | CAN-1 transmit data                                                    |                               |                              |

| M_USB0EPEN              |                | O                    | USB-0 external power enable<br>(optionally used in the host mode)      |                               |                              |

| C_SPISIMOA              |                | I/O                  | SPI-A slave in, master out                                             |                               |                              |

| PD1_GPIO17              | 98             | I/O/Z                | General-purpose input/output 17                                        | PU                            | 4 mA                         |

| M_CAN0TX                |                | O                    | CAN-0 transmit data                                                    |                               |                              |

| M_U2TX                  |                | O                    | UART-2 transmit data                                                   |                               |                              |

| M_U1TX                  |                | O                    | UART-1 transmit data                                                   |                               |                              |

| M_CCP7                  |                | I/O                  | Capture/Compare/PWM-7<br>(General-purpose Timer)                       |                               |                              |

| M_MIITXER               |                | O                    | EMAC MII transmit error                                                |                               |                              |

| M_CCP2                  |                | I/O                  | Capture/Compare/PWM-2<br>(General-purpose Timer)                       |                               |                              |

| M_MIICOL                |                | I                    | EMAC MII collision detect                                              |                               |                              |

| M_SSI0RX                |                | I                    | SSI-0 receive data                                                     |                               |                              |

| M_CAN1RX                |                | I                    | CAN-1 receive data                                                     |                               |                              |

| M_USB0PFLT              |                | I                    | USB-0 external power error state<br>(optionally used in the host mode) |                               |                              |

| C_SPISOMIA              |                | I/O                  | SPI-A master in, slave out                                             |                               |                              |

| PD2_GPIO18              | 28             | I/O/Z                | General-purpose input/output 18                                        | PU                            | 4 mA                         |

| M_U1RX                  |                | I                    | UART-1 receive data                                                    |                               |                              |

| M_CCP6                  |                | I/O                  | Capture/Compare/PWM-6<br>(General-purpose Timer)                       |                               |                              |

| M_CCP5                  |                | I/O                  | Capture/Compare/PWM-5<br>(General-purpose Timer)                       |                               |                              |

| M_EPI0S20               |                | I/O                  | EPI-0 signal 20                                                        |                               |                              |

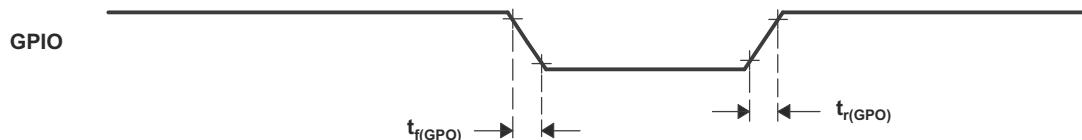

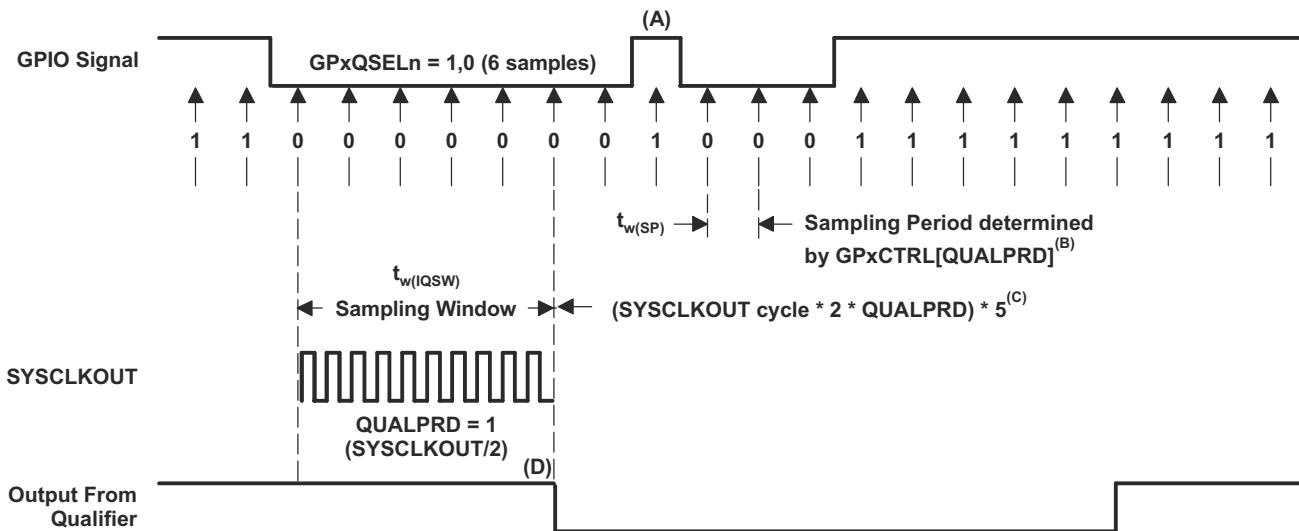

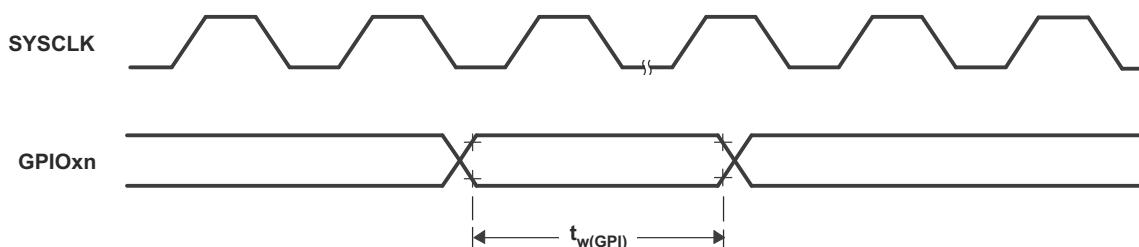

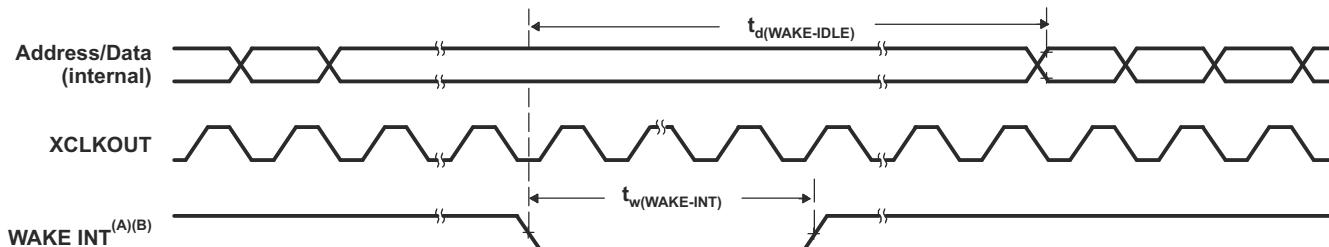

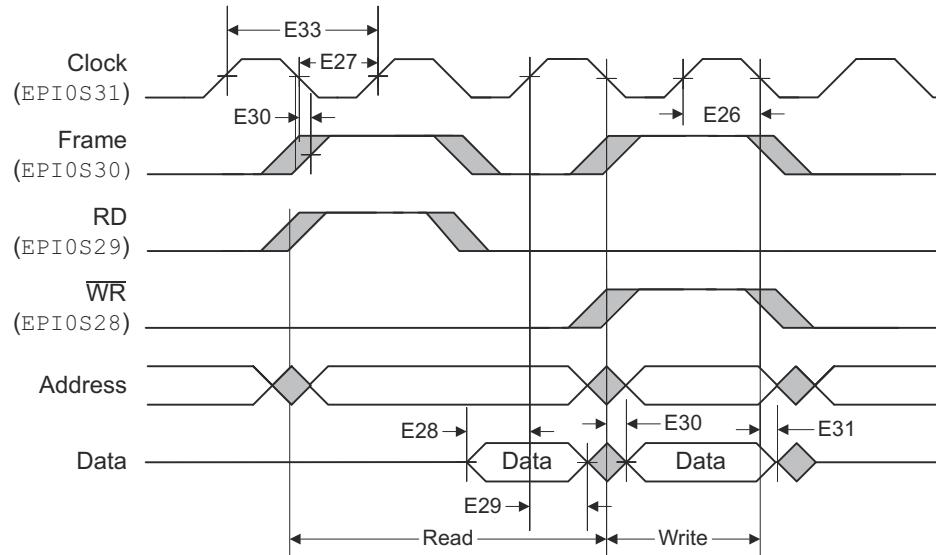

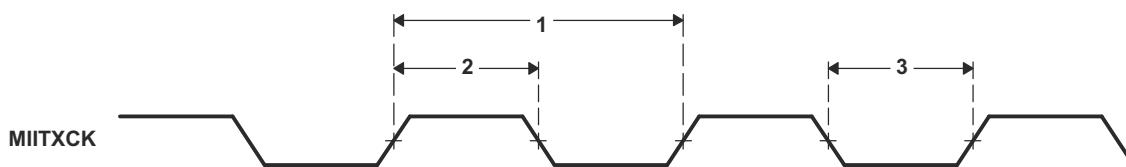

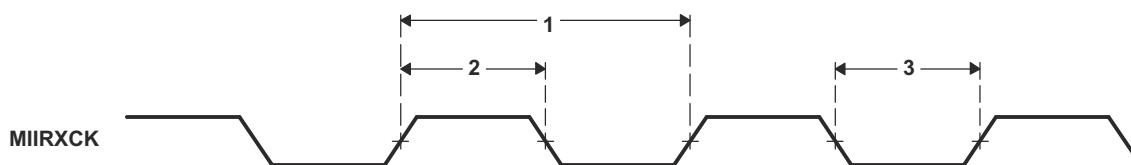

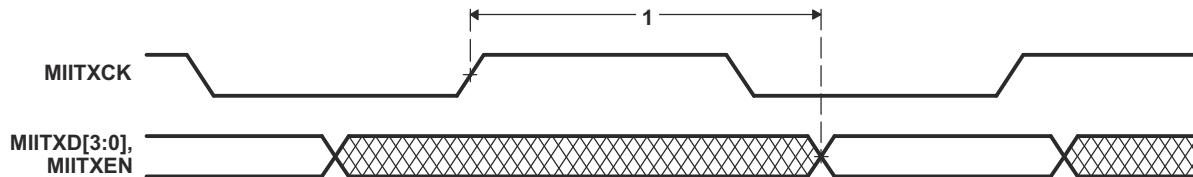

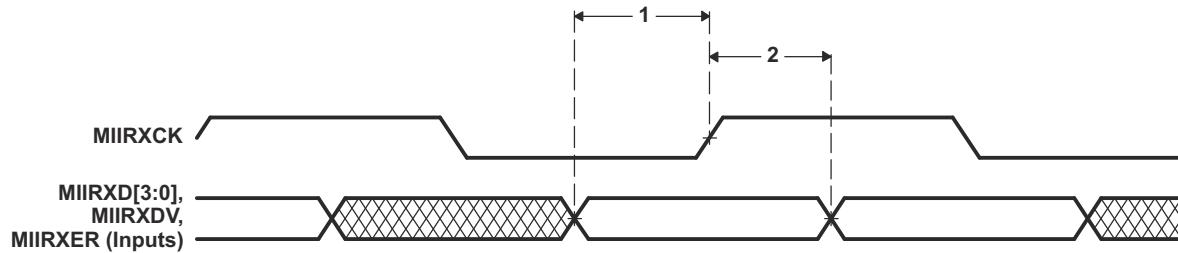

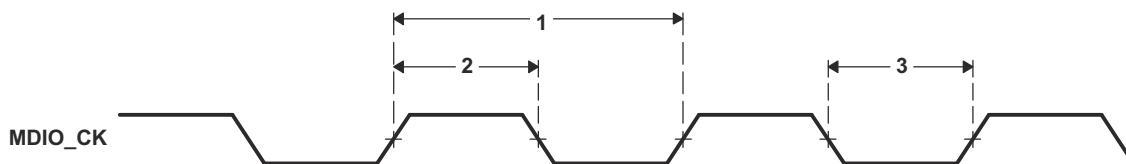

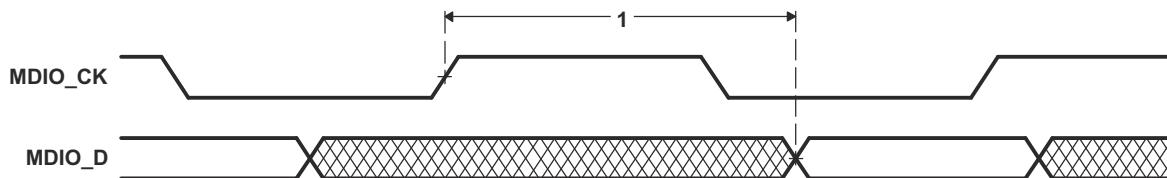

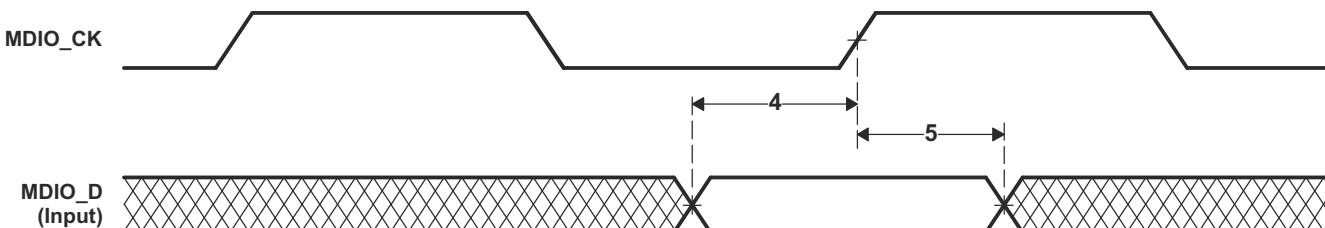

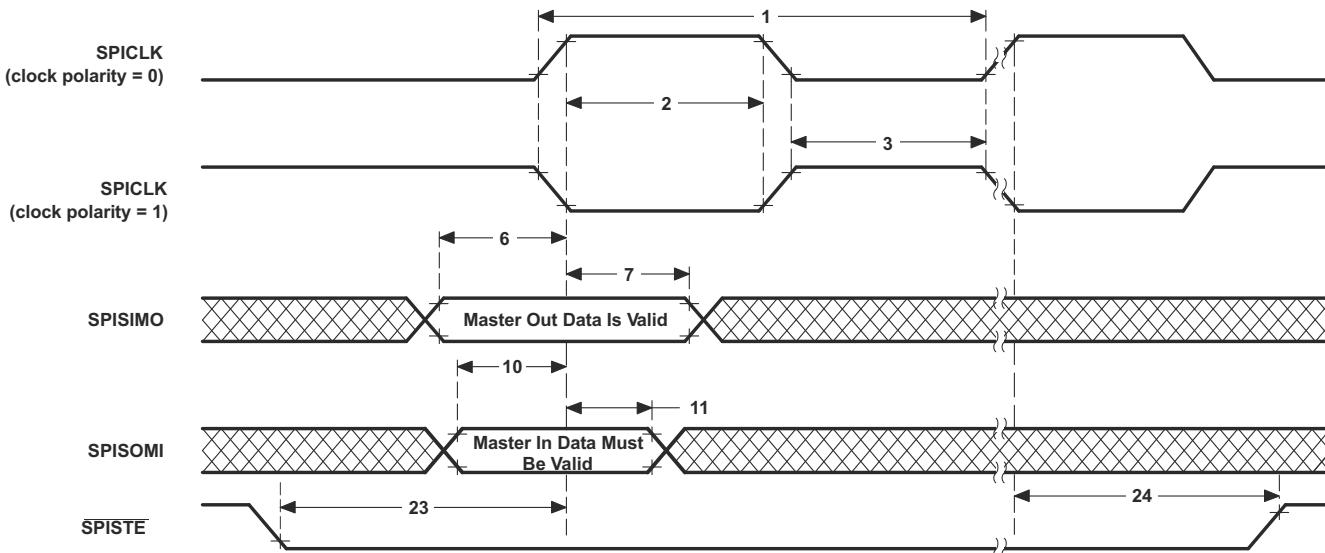

| M_SSI0CLK               |                | I/O                  | SSI-0 clock                                                            |                               |                              |